#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 16K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-UFQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-UQFN (4x4)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11e16a-au |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Processor and Architecture**

| Features                       | Cortex-M23 Configurable<br>Options                             | SAM L10 Implementation | SAM L11 Implementation |

|--------------------------------|----------------------------------------------------------------|------------------------|------------------------|

| Cross Trigger Interface (CTI)  | Present or absent                                              | Absent                 | Absent                 |

| Micro Trace Buffer (MTB)       | Present or absent                                              | Absent                 | Absent                 |

| Embedded Trace Macrocell (ETM) | Present or absent                                              | Absent                 | Absent                 |

| JTAGnSW debug protocol         | Selects between JTAG or Serial-<br>Wire interfaces for the DAP | Serial-Wire            | Serial-Wire            |

| Multi-drop for Serial Wire     | Present or absent                                              | Absent                 | Absent                 |

#### Note:

1. Refer to Table 11-3 for more information.

For more details, refer to the ARM Cortex-M23 Processor Technical Reference Manual (http://www.arm.com).

#### 11.1.2 Cortex-M23 Core Peripherals

The processor has the following core peripheral:

- System Timer (SysTick)

- The System Timer is a 24-bit timer clocked by the core frequency.

**Important:** On SAM L11 devices, there are two System timers, one for Secure state and one for Non-secure state.

- Nested Vectored Interrupt Controller (NVIC)

- The NVIC is an embedded interrupt controller that supports low latency interrupt processing.

**Important:** On SAM L11 devices, there are two Vector tables: the Secure Vector table and the Non-Secure Vector table.

- System Control Block (SCB)

- The System Control Block (SCB) provides system implementation information and system control that includes configuration, control, and reporting of system exceptions

- Memory Protection Unit (MPU)

- The MPU improves system reliability by defining the memory attributes for different memory regions.

| 7 |

|---|

|   |

**Important:** On SAM L11 devices, there are two MPUs: one for the Secure state and one for the Non-secure state. Each MPU can define memory access permissions and attributes independently.

- Security Attribution Unit (SAU)

- The SAU improves system security by defining security attributes for different regions.

#### 14.4.5.9 Boot Interactive Mode Commands Table 14-9. Boot Interactive Mode Commands

| Command Name  | Description                                  | Command prefix | Command |

|---------------|----------------------------------------------|----------------|---------|

| CMD_INIT      | Entering Interactive Mode                    | 0x444247       | 55      |

| CMD_EXIT      | Exit Interactive Mode                        | 0x444247       | AA      |

| CMD_RESET     | System Reset Request                         | 0x444247       | 52      |

| CMD_CE0       | ChipErase_NS for SAM L11                     | 0x444247       | E0      |

| CMD_CE1       | ChipErase_S for SAM L11                      | 0x444247       | E1      |

| CMD_CE2       | ChipErase_ALL for SAM L11                    | 0x444247       | E2      |

| CMD_CHIPERASE | ChipErase for SAM L10                        | 0x444247       | E3      |

| CMD_CRC       | NVM Memory Regions Integrity<br>Checks       | 0x444247       | C0      |

| CMD_DCEK      | Random Session Key Generation<br>for SAM L11 | 0x444247       | 44      |

| CMD_RAUX      | NVM Rows Integrity Checks                    | 0x444247       | 4C      |

# 14.4.5.10 Boot Interactive Mode Status

## Table 14-10. Boot Interactive Mode Status

| Status Name            | Description                          | Status prefix | Status coding |

|------------------------|--------------------------------------|---------------|---------------|

| SIG_NO                 | No Error                             | 0xEC0000      | 00            |

| SIG_SAN_FFF            | Fresh from factory error             | 0xEC0000      | 10            |

| SIG_SAN_UROW           | UROW checksum error                  | 0xEC0000      | 11            |

| SIG_SAN_SECEN          | SECEN parameter error                | 0xEC0000      | 12            |

| SIG_SAN_BOCOR          | BOCOR checksum error                 | 0xEC0000      | 13            |

| SIG_SAN_BOOTPROT       | BOOTPROT parameter error             | 0xEC0000      | 14            |

| SIG_SAN_NOSECREG       | No secure register parameter error   | 0xEC0000      | 15            |

| SIG_COMM               | Debugger start communication command | 0xEC0000      | 20            |

| SIG_CMD_SUCCESS        | Debugger command success             | 0xEC0000      | 21            |

| SIG_CMD_FAIL           | Debugger command fail                | 0xEC0000      | 22            |

| SIG_CMD_BADKEY         | Debugger bad key                     | 0xEC0000      | 23            |

| SIG_CMD_VALID          | Valid command                        | 0xEC0000      | 24            |

| SIG_CMD_INVALID        | Invalid command                      | 0xEC0000      | 25            |

| SIG_ARG_VALID          | Valid argument                       | 0xEC0000      | 26            |

| SIG_ARG_INVALID        | Invalid argument                     | 0xEC0000      | 27            |

| SIG_CE_CVM             | Chip erase error: CVM                | 0xEC0000      | 30            |

| SIG_CE_ARRAY_ERASEFAIL | Chip erase error: array erase fail   | 0xEC0000      | 31            |

| SIG_CE_ARRAY_NVME      | Chip erase error: array NVME         | 0xEC0000      | 32            |

| SIG_CE_DATA_ERASEFAIL  | Chip erase error: data erase fail    | 0xEC0000      | 33            |

| SIG_CE_DATA_NVME       | Chip erase error: data NVME          | 0xEC0000      | 34            |

| SIG_CE_BCUR            | Chip erase error: BOCOR, UROW        | 0xEC0000      | 35            |

| SIG_CE_BC              | Chip erase error: BC check           | 0xEC0000      | 36            |

| SIG_BOOT_OPT           | BOOTOPT parameter error              | 0xEC0000      | 40            |

#### 15.7.10 Peripheral Write Protection Status B

| Name:     | STATUSB    |

|-----------|------------|

| Offset:   | 0x38       |

| Reset:    | 0x000000   |

| Property: | Mix-Secure |

Reading the STATUSB register returns the peripheral write protection status:

| Value | Description                        |

|-------|------------------------------------|

| 0     | Peripheral is not write protected. |

| 1     | Peripheral is write protected.     |

**Important:** For **SAM L11 Non-Secure** accesses, read accesses (R\*) are allowed only if the peripheral security attribution for the corresponding peripheral is set as Non-Secured in the NONSECx register.

| Bit    | 31 | 30 | 29 | 28       | 27     | 26      | 25     | 24     |

|--------|----|----|----|----------|--------|---------|--------|--------|

|        |    |    |    |          |        |         |        |        |

| Access |    |    |    |          |        |         |        |        |

| Reset  |    |    |    |          |        |         |        |        |

|        |    |    |    |          |        |         |        |        |

| Bit    | 23 | 22 | 21 | 20       | 19     | 18      | 17     | 16     |

|        |    |    |    |          |        |         |        |        |

| Access |    |    |    |          |        |         |        |        |

| Reset  |    |    |    |          |        |         |        |        |

|        |    |    |    |          |        |         |        |        |

| Bit    | 15 | 14 | 13 | 12       | 11     | 10      | 9      | 8      |

|        |    |    |    |          |        |         |        |        |

| Access |    |    |    |          |        |         |        |        |

| Reset  |    |    |    |          |        |         |        |        |

|        |    |    |    |          |        |         |        |        |

| Bit    | 7  | 6  | 5  | 4        | 3      | 2       | 1      | 0      |

|        |    |    |    | Reserved | DMAC   | NVMCTRL | DSU    | IDAU   |

| Access |    |    |    | R/R*/R   | R/R*/R | R/R*/R  | R/R*/R | R/R*/R |

| Reset  |    |    |    | 0        | 0      | 0       | 0      | 0      |

|        |    |    |    |          |        |         |        |        |

#### Bit 4 - Reserved Reserved

- Bit 3 DMAC Peripheral DMAC Write Protection Status

- Bit 2 NVMCTRL Peripheral NVMCTRL Write Protection Status

- Bit 1 DSU Peripheral DSU Write Protection Status

- Bit 0 IDAU Peripheral IDAU Write Protection Status

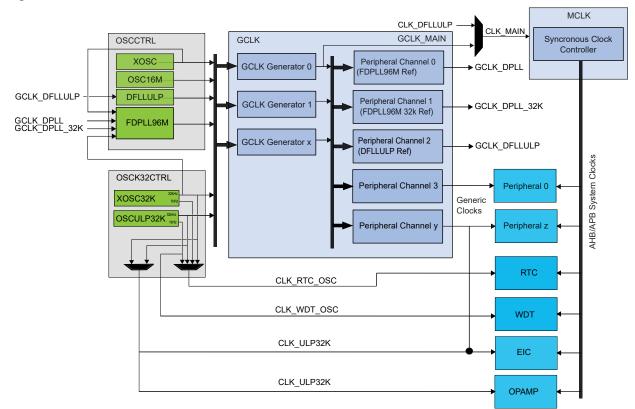

## 17. Clock System

This chapter summarizes the clock distribution and terminology in the SAM L10/L11 device. This document will not explain every detail of its configuration, hence for in-depth details, refer to the respective peripherals descriptions and the *Generic Clock* documentation.

## 17.1 Clock Distribution

Figure 17-1. Clock Distribution

The SAM L10/L11 clock system consists of these features:

- Clock sources, that is oscillators controlled by OSCCTRL and OSC32KCTRL

- A clock source provides a time base that is used by other components, such as Generic Clock Generators. Example clock sources are the internal 16MHz oscillator (OSC16M), external crystal oscillator (XOSC) and the Fractional Digital Phase Locked Loop (FDPLL96M).

- *Generic Clock Controller (GCLK),* which generates, controls and distributes the asynchronous clock consisting of:

- Generic Clock Generators: These are programmable prescalers that can use any of the system clock sources as a time base. The Generic Clock Generator 0 generates the clock signal GCLK\_MAIN, which is used by the Power Manager and the Main Clock (MCLK) module, which in turn generates synchronous clocks.

- Generic Clocks: These are clock signals generated by Generic Clock Generators and output by the Peripheral Channels, and serve as clocks for the peripherals of the system. Multiple instances of a peripheral will typically have a separate Generic Clock for each instance.

#### **Related Links**

19.6.2.6 Peripheral Clock Masking24. OSC32KCTRL – 32KHz Oscillators Controller

#### 18.5.4 DMA

Not applicable.

#### 18.5.5 Interrupts

Not applicable.

#### 18.5.6 Events

Not applicable.

#### 18.5.7 Debug Operation

When the CPU is halted in debug mode the GCLK continues normal operation. If the GCLK is configured in a way that requires it to be periodically serviced by the CPU through interrupts or similar, improper operation or data loss may result during debugging.

#### 18.5.8 Register Access Protection

All registers with write-access can be optionally write-protected by the Peripheral Access Controller (PAC).

**Note:** Optional write-protection is indicated by the "PAC Write-Protection" property in the register description.

Write-protection does not apply for accesses through an external debugger.

#### **Related Links**

15. PAC - Peripheral Access Controller

#### 18.5.9 SAM L11 TrustZone Specific Register Access Protection

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to Peripherals Security Attribution for more information.

#### 18.5.10 Analog Connections

Not applicable.

#### **18.6** Functional Description

#### 18.6.1 Principle of Operation

The GCLK module is comprised of five Generic Clock Generators (Generators) sourcing up to 64 Peripheral Channels and the Main Clock signal CLK\_MAIN.

#### 23.8.19 DPLL Synchronization Busy

| Name:     | DPLLSYNCBUSY |

|-----------|--------------|

| Offset:   | 0x3C         |

| Reset:    | 0x00         |

| Property: | _            |

| Bit    | 7 | 6 | 5 | 4 | 3         | 2         | 1      | 0 |

|--------|---|---|---|---|-----------|-----------|--------|---|

|        |   |   |   |   | DPLLPRESC | DPLLRATIO | ENABLE |   |

| Access |   |   |   |   | R         | R         | R      |   |

| Reset  |   |   |   |   | 0         | 0         | 0      |   |

**Bit 3 – DPLLPRESC** DPLL Prescaler Synchronization Status

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | The DPLLRESC register has been synchronized.                                    |

| 1     | The DPLLRESC register value has changed and its synchronization is in progress. |

#### Bit 2 – DPLLRATIO DPLL Loop Divider Ratio Synchronization Status

| V | alue | Description                                                                      |

|---|------|----------------------------------------------------------------------------------|

| 0 |      | The DPLLRATIO register has been synchronized.                                    |

| 1 |      | The DPLLRATIO register value has changed and its synchronization is in progress. |

#### **Bit 1 – ENABLE** DPLL Enable Synchronization Status

| Value | Description                                                                        |

|-------|------------------------------------------------------------------------------------|

| 0     | The DPLLCTRLA.ENABLE bit has been synchronized.                                    |

| 1     | The DPLLCTRLA.ENABLE bit value has changed and its synchronization is in progress. |

# SAM L10/L11 Family OSC32KCTRL – 32KHz Oscillators Controller

#### 24.8.6 32KHz External Crystal Oscillator (XOSC32K) Control

| Name:     | XOSC32K              |

|-----------|----------------------|

| Offset:   | 0x14                 |

| Reset:    | 0x0000080            |

| Property: | PAC Write-Protection |

| Bit    | 15       | 14       | 13 | 12      | 11    | 10     | 9            | 8   |

|--------|----------|----------|----|---------|-------|--------|--------------|-----|

|        |          |          |    | WRTLOCK |       |        | STARTUP[2:0] |     |

| Access |          |          |    | R/W     |       | R/W    | R/W          | R/W |

| Reset  |          |          |    | 0       |       | 0      | 0            | 0   |

|        |          |          |    |         |       |        |              |     |

| Bit    | 7        | 6        | 5  | 4       | 3     | 2      | 1            | 0   |

|        | ONDEMAND | RUNSTDBY |    | EN1K    | EN32K | XTALEN | ENABLE       |     |

| Access | R/W      | R/W      |    | R/W     | R/W   | R/W    | R/W          |     |

| Reset  | 1        | 0        |    | 0       | 0     | 0      | 0            |     |

#### Bit 12 – WRTLOCK Write Lock

This bit locks the XOSC32K register for future writes, effectively freezing the XOSC32K configuration.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The XOSC32K configuration is not locked. |

| 1     | The XOSC32K configuration is locked.     |

#### Bits 10:8 - STARTUP[2:0] Oscillator Start-Up Time

These bits select the start-up time for the oscillator.

The OSCULP32K oscillator is used to clock the start-up counter.

#### Table 24-2. Start-Up Time for 32KHz External Crystal Oscillator

| STARTUP[2:0] | Number of OSCULP32K<br>Clock Cycles | Number of XOSC32K<br>Clock Cycles | Approximate Equivalent<br>Time<br>[s] |

|--------------|-------------------------------------|-----------------------------------|---------------------------------------|

| 0x0          | 2048                                | 3                                 | 0.06                                  |

| 0x1          | 4096                                | 3                                 | 0.13                                  |

| 0x2          | 16384                               | 3                                 | 0.5                                   |

| 0x3          | 32768                               | 3                                 | 1                                     |

| 0x4          | 65536                               | 3                                 | 2                                     |

| 0x5          | 131072                              | 3                                 | 4                                     |

| 0x6          | 262144                              | 3                                 | 8                                     |

| 0x7          | -                                   | -                                 | Reserved                              |

#### Note:

- 1. Actual Start-Up time is 1 OSCULP32K cycle + 3 XOSC32K cycles.

- 2. The given time assumes an XTAL frequency of 32.768kHz.

#### 25.8.6 Voltage Regulator System (VREG) Control

| Name:     | VREG                 |

|-----------|----------------------|

| Offset:   | 0x18                 |

| Reset:    | 0x0000002            |

| Property: | PAC Write-Protection |

| Bit    | 31  | 30       | 29       | 28   | 27      | 26    | 25      | 24    |

|--------|-----|----------|----------|------|---------|-------|---------|-------|

|        |     |          |          | VSPE | ER[7:0] |       |         |       |

| Access | R/W | R/W      | R/W      | R/W  | R/W     | R/W   | R/W     | R/W   |

| Reset  | 0   | 0        | 0        | 0    | 0       | 0     | 0       | 0     |

|        |     |          |          |      |         |       |         |       |

| Bit    | 23  | 22       | 21       | 20   | 19      | 18    | 17      | 16    |

|        |     |          |          |      |         | VSVST | EP[3:0] |       |

| Access |     | •        |          |      | R/W     | R/W   | R/W     | R/W   |

| Reset  |     |          |          |      | 0       | 0     | 0       | 0     |

|        |     |          |          |      |         |       |         |       |

| Bit    | 15  | 14       | 13       | 12   | 11      | 10    | 9       | 8     |

|        |     |          |          |      |         |       | VREFSEL | LPEFF |

| Access |     | •        |          |      |         |       | R/W     | R/W   |

| Reset  |     |          |          |      |         |       | 0       | 0     |

|        |     |          |          |      |         |       |         |       |

| Bit    | 7   | 6        | 5        | 4    | 3       | 2     | 1       | 0     |

|        |     | RUNSTDBY | STDBYPL0 |      |         | SEL   | ENABLE  |       |

| Access |     | R/W      | R/W      |      |         | R/W   | R/W     |       |

| Reset  |     | 0        | 1        |      |         | 0     | 1       |       |

#### Bits 31:24 – VSPER[7:0] Voltage Scaling Period

This bitfield sets the period between the voltage steps when the VDDCORE voltage is changing in µs.

If VSPER=0, the period between two voltage steps is 1µs.

#### Bits 19:16 – VSVSTEP[3:0] Voltage Scaling Voltage Step

This field sets the voltage step height when the VDDCORE voltage is changing to reach the target VDDCORE voltage.

The voltage step is equal to 2<sup>VSVSTEP\*</sup> min\_step.

See the Electrical Characteristics chapters for the min\_step voltage level.

**Bit 9 – VREFSEL** Voltage Regulator Voltage Reference Selection This bit provides support of using ULPVREF during active function mode.

Selects ULPVREF for the voltage regulator.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Selects VREF for the voltage regulator. |

Bit 8 – LPEFF Low power Mode Efficiency

1

#### 15. PAC - Peripheral Access Controller

#### 27.5.9 SAM L11 TrustZone Specific Register Access Protection

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to *Peripherals Security Attribution* for more information.

#### 27.5.10 Analog Connections

A 32.768kHz crystal can be connected to the XIN32 and XOUT32 pins, along with any required load capacitors. See the Electrical Characteristics Chapters for details on recommended crystal characteristics and load capacitors.

#### 27.6 Functional Description

#### 27.6.1 Principle of Operation

The RTC keeps track of time in the system and enables periodic events, as well as interrupts and events at a specified time. The RTC consists of a 10-bit prescaler that feeds a 32-bit counter. The actual format of the 32-bit counter depends on the RTC operating mode.

The RTC can function in one of these modes:

- Mode 0 COUNT32: RTC serves as 32-bit counter

- Mode 1 COUNT16: RTC serves as 16-bit counter

- Mode 2 CLOCK: RTC serves as clock/calendar with alarm functionality

#### 27.6.2 Basic Operation

#### 27.6.2.1 Initialization

The following bits are enable-protected, meaning that they can only be written when the RTC is disabled (CTRLA.ENABLE=0):

- Operating Mode bits in the Control A register (CTRLA.MODE)

- Prescaler bits in the Control A register (CTRLA.PRESCALER)

- Clear on Match bit in the Control A register (CTRLA.MATCHCLR)

- Clock Representation bit in the Control A register (CTRLA.CLKREP)

The following registers are enable-protected:

- Control B register (CTRLB)

- Event Control register (EVCTRL)

- Tamper Control register (TAMPCTRL)

- Tamper Control B register (TAMPCTRLB)

Enable-protected bits and registers can be changed only when the RTC is disabled (CTRLA.ENABLE=0). If the RTC is enabled (CTRLA.ENABLE=1), these operations are necessary: first write

## 30.7 Register Summary

#### Important:

For SAM L11, the NVMCTRL register map is automatically duplicated in a Secure and Non-Secure alias:

- The Non-Secure alias is at the peripheral base address

- The Secure alias is located at the peripheral base address + 0x1000

Refer to *Mix-Secure Peripherals* for more information on register access rights

| Offset | Name     | Bit Pos. |      |        |       |       |          |          |          |          |

|--------|----------|----------|------|--------|-------|-------|----------|----------|----------|----------|

|        |          | 7:0      |      |        |       |       | CMD[6:0] |          |          |          |

| 0x00   | CTRLA    | 15:8     |      |        |       | CMD   | EX[7:0]  |          |          |          |

| 0x02   |          |          |      |        |       |       |          |          |          |          |

|        | Reserved |          |      |        |       |       |          |          |          |          |

| 0x03   |          |          |      |        |       |       |          |          |          |          |

|        |          | 7:0      |      |        |       |       | RW       | S[3:0]   | 1        |          |

|        |          | 15:8     |      |        |       |       | FWUP     |          | SLEEPF   | PRM[1:0] |

| 0x04   | CTRLB    | 23:16    |      |        |       |       |          | CACHEDIS | READM    | ODE[1:0] |

|        |          | 31:24    |      |        |       |       |          |          |          |          |

| 0x08   | CTRLC    | 7:0      |      |        |       |       |          |          |          | MANW     |

| 0x09   | Reserved |          |      |        |       |       |          |          |          |          |

| 0x0A   | EVCTRL   | 7:0      |      |        |       |       |          |          | AUTOWINV | AUTOWEI  |

| 0x0B   | Reserved |          |      |        |       |       |          |          |          |          |

| 0x0C   | INTENCLR | 7:0      |      |        | NSCHK | KEYE  | NVME     | LOCKE    | PROGE    | DONE     |

| 0x0D   |          |          |      |        |       |       |          |          |          |          |

|        | Reserved |          |      |        |       |       |          |          |          |          |

| 0x0F   |          |          |      |        |       |       |          |          |          |          |

| 0x10   | INTENSET | 7:0      |      |        | NSCHK | KEYE  | NVME     | LOCKE    | PROGE    | DONE     |

| 0x11   |          |          |      |        |       |       |          |          |          |          |

|        | Reserved |          |      |        |       |       |          |          |          |          |

| 0x13   |          |          |      |        |       |       |          |          |          |          |

| 0x14   | INTFLAG  | 7:0      |      |        | NSCHK | KEYE  | NVME     | LOCKE    | PROGE    | DONE     |

| 0x15   |          |          |      |        |       |       |          |          |          |          |

|        | Reserved |          |      |        |       |       |          |          |          |          |

| 0x17   |          |          |      |        |       |       |          |          |          |          |

| 0x18   | STATUS   | 7:0      |      |        |       | DALFU | JSE[1:0] | READY    | LOAD     | PRM      |

| 0210   | 31A103   | 15:8     |      |        |       |       |          |          |          |          |

| 0x1A   |          |          |      |        |       |       |          |          |          |          |

|        | Reserved |          |      |        |       |       |          |          |          |          |

| 0x1B   |          |          |      |        |       |       |          |          |          |          |

|        |          | 7:0      |      |        |       | AOFFS | SET[7:0] |          |          |          |

| 0x1C   | ADDR     | 15:8     |      |        |       | AOFFS | ET[15:8] |          |          |          |

| UXIC   | ADDK     | 23:16    | ARRA | Y[1:0] |       |       |          |          |          |          |

|        |          | 31:24    |      |        |       |       |          |          |          |          |

| 0x20   | SULCK    | 7:0      |      |        |       |       |          | DS       | AS       | BS       |

# EVSYS – Event System

| Value     | Event Generator | Description           |

|-----------|-----------------|-----------------------|

| 0x19-0x1C | DMAC_CH         | DMAC channel          |

| 0x1D      | TC0_OVF         | TC0 overflow          |

| 0x1E-0x1F | TC0_MCX         | TC0 match/compare     |

| 0x20      | TC1_OVF         | TC1 overflow          |

| 0x21-0x22 | TC1_MCX         | TC1 match/compare     |

| 0x23      | TC2_OVF         | TC2 overflow          |

| 0x24-0x25 | TC2_MCX         | TC2 match/compare     |

| 0x26      | ADC_RESRDY      | ADC resolution ready  |

| 0x27      | ADC_WINMON      | ADC window monitor    |

| 0x28-0x29 | AC_COMP         | AC comparator         |

| 0x2A      | AC_WIN          | AC window             |

| 0x2B      | DAC_EMPTY       | DAC empty             |

| 0x2C      | PTC_EOC         | PTC end of conversion |

| 0x2D      | PTC_WCOMP       | PTC window comparator |

| 0x2E      | TRNG_READY      | Data ready            |

| 0x2F-0x30 | CCL_LUTOUT      | CCL output            |

| 0x31      | PAC_ERR         | PAC access error      |

#### 33.7.17 Channel Security Attribution

| Name:     | NONSECCHAN                         |

|-----------|------------------------------------|

| Offset:   | 0x1D8                              |

| Reset:    | 0x0000000                          |

| Property: | PAC Write-Protection, Write-Secure |

This register allows the user to configure one or more channels as secured or non-secured.

|                 | <b>&gt;</b> | Important: | portant: This register is only available for SAM L11 and has no effect for SAM L10. |         |          |         |         |         |  |  |

|-----------------|-------------|------------|-------------------------------------------------------------------------------------|---------|----------|---------|---------|---------|--|--|

| Bit             | 31          | 30         | 29                                                                                  | 28      | 27       | 26      | 25      | 24      |  |  |

| [               |             |            |                                                                                     |         |          |         |         |         |  |  |

| Access<br>Reset |             |            |                                                                                     | 1       |          | 1       |         |         |  |  |

| Bit             | 23          | 22         | 21                                                                                  | 20      | 19       | 18      | 17      | 16      |  |  |

| [               |             |            |                                                                                     |         |          |         |         |         |  |  |

| Access<br>Reset |             |            |                                                                                     |         |          |         |         |         |  |  |

| Bit             | 15          | 14         | 13                                                                                  | 12      | 11       | 10      | 9       | 8       |  |  |

|                 |             |            |                                                                                     |         |          |         |         |         |  |  |

| Access          |             |            |                                                                                     |         |          |         |         |         |  |  |

| Reset           |             |            |                                                                                     |         |          |         |         |         |  |  |

| Bit             | 7           | 6          | 5                                                                                   | 4       | 3        | 2       | 1       | 0       |  |  |

|                 |             |            |                                                                                     |         | ELn[7:0] |         |         |         |  |  |

| Access          | RW/R/RW     | RW/R/RW    | RW/R/RW                                                                             | RW/R/RW | RW/R/RW  | RW/R/RW | RW/R/RW | RW/R/RW |  |  |

| Reset           | 0           | 0          | 0                                                                                   | 0       | 0        | 0       | 0       | 0       |  |  |

**Bits 7:0 – CHANNELn[7:0]** Channel n Security Attribution [n=7..0]The bit n of CHANNEL enables the non-secure mode of CHANNELn. The registers whose CHANNEL bit or bitfield n is set in non-secure mode by NONSECCHAN.CHANNELn are CHANNELn, CHINTENCLRn, CHINTENSETn, CHINTFLAGn and CHSTATUSx registers.

These bits set the security attribution for the individual channels.

| Value | Description                                                                                                                                                                                                                                                                                       |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The corresponding channel is secured. When the module is PAC secured, the configuration and status bits for this channel are only available through the secure alias. Attempts to change the channel configuration through the non-secure alias will be silently ignored and reads will return 0. |

| 1     | The corresponding channel is non-secured. The configuration and status bits for this channel are available through the non-secure alias.                                                                                                                                                          |

SERCOM USART - SERCOM Synchronous and Asyn...

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |

#### 36.8.4 Interrupt Enable Clear

Name:INTENCLROffset:0x14Reset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 7     | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|--------|-------|---|---|---|-----|-----|-----|-----|

|        | ERROR |   |   |   | SSL | RXC | TXC | DRE |

| Access | R/W   |   |   |   | R/W | R/W | R/W | R/W |

| Reset  | 0     |   |   |   | 0   | 0   | 0   | 0   |

#### **Bit 7 – ERROR** Error Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Error Interrupt Enable bit, which disables the Error interrupt.

| Value | Description                  |

|-------|------------------------------|

| 0     | Error interrupt is disabled. |

| 1     | Error interrupt is enabled.  |

#### Bit 3 – SSL Slave Select Low Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Slave Select Low Interrupt Enable bit, which disables the Slave Select Low interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Slave Select Low interrupt is disabled. |

| 1     | Slave Select Low interrupt is enabled.  |

**Bit 2 – RXC** Receive Complete Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Receive Complete Interrupt Enable bit, which disables the Receive Complete interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Receive Complete interrupt is disabled. |

| 1     | Receive Complete interrupt is enabled.  |

Bit 1 – TXC Transmit Complete Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Transmit Complete Interrupt Enable bit, which disable the Transmit Complete interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | Transmit Complete interrupt is disabled. |

| 1     | Transmit Complete interrupt is enabled.  |

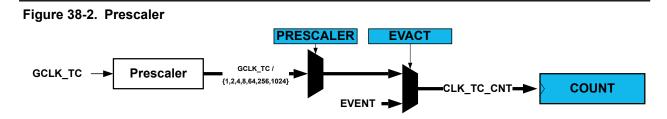

TC – Timer/Counter

#### 38.6.2.4 Counter Mode

The counter mode is selected by the Mode bit group in the Control A register (CTRLA.MODE). By default, the counter is enabled in the 16-bit counter resolution. Three counter resolutions are available:

- COUNT8: The 8-bit TC has its own Period Value and Period Buffer Value registers (PER and PERBUF).

- COUNT16: 16-bit is the default counter mode. There is no dedicated period register in this mode.

- COUNT32: This mode is achieved by pairing two 16-bit TC peripherals. TCn is paired with TCn+1. TC2 does not support 32-bit resolution.

When paired, the TC peripherals are configured using the registers of the even-numbered TC. The odd-numbered partner will act as a slave, and the Slave bit in the Status register (STATUS.SLAVE) will be set. The register values of a slave will not reflect the registers of the 32-bit counter. Writing to any of the slave registers will not affect the 32-bit counter. Normal access to the slave COUNT and CCx registers is not allowed.

#### 38.6.2.5 Counter Operations

Depending on the mode of operation, the counter is cleared, reloaded, incremented, or decremented at each TC clock input (CLK\_TC\_CNT). A counter clear or reload marks the end of the current counter cycle and the start of a new one.

The counting direction is set by the Direction bit in the Control B register (CTRLB.DIR). If this bit is zero the counter is counting up, and counting down if CTRLB.DIR=1. The counter will count up or down for each tick (clock or event) until it reaches TOP or ZERO. When it is counting up and TOP is reached, the counter will be set to zero at the next tick (overflow) and the Overflow Interrupt Flag in the Interrupt Flag Status and Clear register (INTFLAG.OVF) will be set. When it is counting down, the counter is reloaded with the TOP value when ZERO is reached (underflow), and INTFLAG.OVF is set.

INTFLAG.OVF can be used to trigger an interrupt, a DMA request, or an event. An overflow/underflow occurrence (i.e., a compare match with TOP/ZERO) will stop counting if the One-Shot bit in the Control B register is set (CTRLBSET.ONESHOT).

It is possible to change the counter value (by writing directly in the COUNT register) even when the counter is running. When starting the TC, the COUNT value will be either ZERO or TOP (depending on the counting direction set by CTRLBSET.DIR or CTRLBCLR.DIR), unless a different value has been written to it, or the TC has been stopped at a value other than ZERO. The write access has higher priority than count, clear, or reload. The direction of the counter can also be changed when the counter is running. See also the following figure.

Some registers are synchronized when read and/or written. Synchronization is denoted by the "Write-Synchronized" or the "Read-Synchronized" property in each individual register description. For details, refer to Synchronization.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

On **SAM L11** devices, this peripheral has different access permissions depending on PAC Security Attribution (Secure or Non-Secure):

- If the peripheral is configured as Non-Secure in the PAC:

- Secure access and Non-Secure access are granted

- If the peripheral is configured as Secure in the PAC:

- Secure access is granted

- Non-Secure access is discarded (Write is ignored, read 0x0) and a PAC error is triggered

Refer to *Peripherals Security Attribution* for more information.

#### 43.8.5 Interrupt Enable Set

Name:INTENSETOffset:0x05Reset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1     | 0        |

|--------|---|---|---|---|---|---|-------|----------|

|        |   |   |   |   |   |   | EMPTY | UNDERRUN |

| Access |   |   |   |   |   |   | R/W   | R/W      |

| Reset  |   |   |   |   |   |   | 0     | 0        |

**Bit 1 – EMPTY** Data Buffer Empty Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Data Buffer Empty Interrupt Enable bit, which enables the Data Buffer Empty interrupt.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | The Data Buffer Empty interrupt is disabled. |

| 1     | The Data Buffer Empty interrupt is enabled.  |

#### Bit 0 – UNDERRUN Underrun Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Data Buffer Underrun Interrupt Enable bit, which enables the Data Buffer Underrun interrupt.

|   | Value | Description                                     |

|---|-------|-------------------------------------------------|

| [ | 0     | The Data Buffer Underrun interrupt is disabled. |

|   | 1     | The Data Buffer Underrun interrupt is enabled.  |

## **Electrical Characteristics**

#### 46.11.7 DETREF Characteristics

Table 46-31. Reference Voltage Characteristics

| Symbol      | Parameter                   | Conditions                                    | Min.  | Тур.          | Max.  | Units |

|-------------|-----------------------------|-----------------------------------------------|-------|---------------|-------|-------|

| ADC/DAC Ref | ADC/DAC internal reference  | nom. 1.0V, V <sub>CC</sub> =3.0V, T= 25°C     | 0.976 | 1.0           | 1.022 | V     |

|             |                             | nom. 1.1V, V <sub>CC</sub> =3.0V, T= 25°C     | 1.077 | 1.1           | 1.127 |       |

|             |                             | nom. 1.2V, V <sub>CC</sub> =3.0V, T= 25°C     | 1.174 | 1.2           | 1.234 |       |

|             |                             | nom. 1.25V, V <sub>CC</sub> =3.0V, T=<br>25°C | 1.221 | 1.25          | 1.287 |       |

|             |                             | nom. 2.0V, V <sub>CC</sub> =3.0V, T= 25°C     | 1.945 | 2.0           | 2.030 |       |

|             |                             | nom. 2.2V, V <sub>CC</sub> =3.0V, T= 25°C     | 2.143 | 2.2           | 2.242 |       |

|             |                             | nom. 2.4V, $V_{CC}$ =3.0V, T= 25°C            | 2.335 | 2.4           | 2.457 |       |

|             |                             | nom. 2.5V, V <sub>CC</sub> =3.0V, T= 25°C     | 2.428 | 2.5           | 2.563 |       |

|             | Ref Temperature coefficient | drift over [-40, +25]°C                       | -     | -0.01/+0.015  | -     | %/°C  |

|             |                             | drift over [+25, +85]°C                       | -     | -0.01/+0.005  | -     |       |

|             | Ref Supply coefficient      | drift over [1.6, 3.63]V                       | -     | +/-0.35       | -     | %/V   |

| AC Ref      | AC Ref Accuracy             | V <sub>CC</sub> =3.0V, T=25°C                 | 1.086 | 1.1           | 1.128 | V     |

|             | Ref Temperature coefficient | drift over [-40, +25]°C                       | -     | +/-0.01       | -     | %/°C  |

|             |                             | drift over [+25, +85]°C                       | -     | -0.005/+0.001 | -     | %/°C  |

|             | Ref Supply coefficient      | drift over [1.6, 3.63]V                       | -     | -0.35/+0.35   | -     | %/V   |

### 46.11.8 OPAMP Characteristics Table 46-32. Operating Conditions

| Symbol                | Parameters               | Conditions                    | Min. | Тур. | Max.     | Unit |

|-----------------------|--------------------------|-------------------------------|------|------|----------|------|

| VCC                   | Power Supply             | All power modes               | 1.6  | 3    | 3.63     | V    |

| Vin                   | Input voltage range      |                               | 0    | -    | Vcc      | V    |

| Vout                  | Output voltage range     |                               | 0.15 | -    | Vcc-0.15 | V    |

| Cload                 | Maximum capacitance load |                               | -    | -    | 50       | pF   |

| Rload <sup>(1)</sup>  | Minimum resistive load   | Output Range[0.15V;Vcc-0.15V] | 3.5  | -    | -        | kΩ   |

|                       |                          | Output Range[0.3V;Vcc-0.3V]   | 0.5  | -    | -        |      |

| I <sub>load</sub> (1) | DC output current load   | Output Range[0.15V;Vcc-0.15V] | -    | -    | 1        | mA   |

|                       |                          | Output Range[0.3V;Vcc-0.3V]   | -    | -    | 6.9      |      |

**Note:** 1. These values are based on simulation. They are not covered by production test limits or characterization.

## 125°C Electrical Characteristics

| Symbol                              | Parameter                                     | Conditions                                                                               | Min.  | Тур.  | Max.  | Units |  |  |  |

|-------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------|-------|-------|-------|-------|--|--|--|

|                                     |                                               | Calibrated against a 4/8/12/16 MHz                                                       | 7.92  | 8.00  | 8.08  |       |  |  |  |

|                                     |                                               | reference                                                                                | 11.88 | 12.00 | 12.12 |       |  |  |  |

|                                     |                                               |                                                                                          | 15.84 | 16.00 | 16.16 |       |  |  |  |

| TempDrift                           | Freq vs. temperature drift                    | VDD=3.3V over temperature<br>[-40°C-125°C], versus calibration<br>reference at 25°C      | -5    |       | 5     | %     |  |  |  |

| SupplyDrift                         | Freq vs. supply drift                         | Temperature =25°C over voltage<br>[1.62V-3.63V], versus calibration<br>reference at 3.3V | -1.5  |       | 1.5   |       |  |  |  |

| T <sub>WUP</sub> <sup>(2)</sup>     | Wake up time - 1st clock edge<br>after enable | F <sub>OUT</sub> = 4MHz                                                                  | -     | 0.13  | 0.32  | 1     |  |  |  |

|                                     |                                               | F <sub>OUT</sub> = 8MHz                                                                  | -     | 0.13  | 0.31  |       |  |  |  |

|                                     |                                               | F <sub>OUT</sub> = 12MHz                                                                 | -     | 0.13  | 0.31  |       |  |  |  |

|                                     |                                               | F <sub>OUT</sub> = 16MHz                                                                 | -     | 0.13  | 0.31  |       |  |  |  |

| T <sub>STARTUP</sub> <sup>(2)</sup> | Startup time                                  | F <sub>OUT</sub> = 4MHz                                                                  | -     | 1.16  | 2.96  | 96 µs |  |  |  |

|                                     |                                               | F <sub>OUT</sub> = 8MHz                                                                  | -     | 1.29  | 2.74  |       |  |  |  |

|                                     |                                               | F <sub>OUT</sub> = 12MHz                                                                 | -     | 1.34  | 2.95  |       |  |  |  |

|                                     |                                               | F <sub>OUT</sub> = 16MHz                                                                 | -     | 1.39  | 3.11  |       |  |  |  |

| Duty <sup>(1)</sup>                 | Duty Cycle                                    | -                                                                                        | 45    | 50    | 55    | %     |  |  |  |

#### Note:

- 1. These values are based on simulation. They are not covered by production test limits or characterization.

- 2. These values are based on characterization. These values are not covered in test limits in production.

#### Table 47-22. Power Consumption

| Symbol          | Parameter              | Conditions                                        | Та                    | Min. | Тур. | Max. | Units |

|-----------------|------------------------|---------------------------------------------------|-----------------------|------|------|------|-------|

| I <sub>DD</sub> | Current<br>consumption | F <sub>out</sub> =4MHz,<br>V <sub>CC</sub> =3.3V  | Max.125°C<br>Typ.25°C | -    | 73   | 370  | μΑ    |

|                 |                        | F <sub>out</sub> =8MHz,<br>V <sub>CC</sub> =3.3V  |                       | -    | 106  | 400  |       |

|                 |                        | F <sub>out</sub> =12MHz,<br>V <sub>CC</sub> =3.3V |                       | -    | 135  | 425  |       |

|                 |                        | F <sub>out</sub> =16MHz,<br>V <sub>CC</sub> =3.3V |                       | -    | 166  | 455  |       |

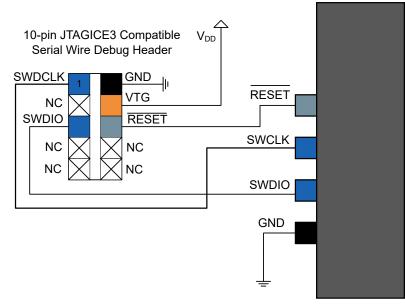

JTAGICE3 and SAM L10/L11. The following figure describes how to connect a 10-pin header that support connecting the JTAGICE3 directly to the SAM L10/L11 without the need for a squid cable. This can also be used for the Atmel-ICE AVR connector port.

The JTAGICE3 squid cable or the JTACICE3 50mil cable can be used to connect the JTAGICE3 programmer and debugger to the SAM L10/L11. The figure illustrates the correct pinout for the JTAGICE3 50 mil, and details are given in the following table.

#### Table 50-8. 10-pin JTAGICE3 Compatible Serial Wire Debug Interface

| Header Signal Name | Description                                                      |

|--------------------|------------------------------------------------------------------|

| SWDCLK             | Serial wire clock pin                                            |

| SWDIO              | Serial wire bidirectional data pin                               |

| RESET              | Target device reset pin, active low                              |

| VTG                | Target voltage sense, should be connected to the device $V_{DD}$ |

| GND                | Ground                                                           |

#### 50.7.3 20-pin IDC JTAG Connector

For debuggers and/or programmers that support the 20-pin IDC JTAG Connector, e.g., the SAM-ICE, the signals should be connected, as shown in the following figure, with details described in the following table.