# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M23                                                          |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 25                                                                        |

| Program Memory Size        | 64KB (64K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 16K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.63V                                                             |

| Data Converters            | A/D 10x12b; D/A 1x10b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-VQFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsaml11e16a-mu |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## SAM L10/L11 Family

### **Signal Descriptions List**

| Signal Name                                             | Function                               | Туре          |  |  |

|---------------------------------------------------------|----------------------------------------|---------------|--|--|

| External Interrupt Controller - EIC                     |                                        |               |  |  |

| EXTINT[7:0]                                             | External Interrupts Pins               | Digital Input |  |  |

| NMI                                                     | Non-Maskable Interrupt Pin             | Digital Input |  |  |

| General Purpose I/O - PORT                              |                                        |               |  |  |

| PA11-PA00 / PA19-PA14 / PA25-PA22 /<br>PA27 / PA31-PA30 | General Purpose I/O Pin in Port A      | Digital I/O   |  |  |

| Reset Controller - RSTC                                 |                                        |               |  |  |

| RESET                                                   | External Reset Pin (Active Level: LOW) | Digital Input |  |  |

| Debug Service Unit - DSU                                |                                        |               |  |  |

| SWCLK                                                   | Serial Wire Clock                      | Digital Input |  |  |

| SWDIO                                                   | Serial Wire Bidirectional Data Pin     | Digital I/O   |  |  |

1. VREFA is shared between the ADC and DAC peripherals.

## SAM L10/L11 Family

### Memories

| Bit Pos. | Name                      | Usage                                                  | Factory Setting | Related Peripheral Register |

|----------|---------------------------|--------------------------------------------------------|-----------------|-----------------------------|

| 25       | WDT_RUNSTDBY              | WDT Runstdby at power-on                               | 0x0             | WDT.CTRLA                   |

| 26       | WDT_ENABLE                | WDT Enable at power-on                                 | 0x0             | WDT.CTRLA                   |

| 27       | WDT_ALWAYSON              | WDT Always-On at power-on                              | 0x0             | WDT.CTRLA                   |

| 31:28    | WDT_PER                   | WDT Period at power-on                                 | 0xB             | WDT.CONFIG                  |

| 35:32    | WDT_WINDOW                | WDT Window mode time-out at power-on                   | 0xB             | WDT.CONFIG                  |

| 39:36    | WDT_EWOFFSET              | WDT Early Warning Interrupt Time Offset at power-on    | 0xB             | WDT.EWCTRL                  |

| 40       | WDT_WEN                   | WDT Timer Window Mode Enable at power-on               | 0x0             | WDT.CTRLA                   |

| 41       | BOD33_HYST                | BOD33 Hysteresis configuration at power-on             | 0x0             | SUPC.BOD33                  |

| 42       | Reserved                  | Reserved                                               | Reserved        | Reserved                    |

| 43       | RXN                       | RAM is eXecute Never                                   | 0x1             | IDAU.SECCTRL                |

| 44       | DXN                       | Data Flash is eXecute Never                            | 0x1             | NVMCTRL.SECCTRL             |

| 63:45    | Reserved                  | Reserved                                               | Reserved        | Reserved                    |

| 71:64    | AS                        | Flash Application Secure Size = AS*0x100               | 0xFF            | IDAU.SCFGA                  |

| 77:72    | ANSC                      | Flash Application Non-Secure Callable Size = ANSC*0x20 | 0x0             | IDAU.SCFGA                  |

| 79:78    | Reserved                  | Reserved Reserved                                      |                 | Reserved                    |

| 83:80    | DS                        | Data Flash Secure Size = DS*0x100 0x8 IDAU.SCFG/       |                 | IDAU.SCFGA                  |

| 87:84    | Reserved                  | Reserved Reserved Reserved                             |                 | Reserved                    |

| 94:88    | RS                        | RAM Secure Size = RS*0x80                              | 0x7F            | IDAU.SCFGR                  |

| 95       | Reserved                  | Reserved                                               | Reserved        | Reserved                    |

| 96       | URWEN                     | User Row Write Enable 0x1 NVMCTR                       |                 | NVMCTRL.SCFGAD              |

| 127:97   | Reserved                  | Reserved Reserved Reserved                             |                 | Reserved                    |

| 159:128  | NONSECA <sup>(1)</sup>    | Peripherals Non-Secure Status Fuses for Bridge A       | 0x0000_0000     | PAC.NONSECA                 |

| 191:160  | NONSECB <sup>(2, 3)</sup> | Peripherals Non-Secure Status Fuses for Bridge B       | 0x0000_0000     | PAC.NONSECB                 |

| 223:192  | NONSECC                   | Peripherals Non-Secure Status Fuses for Bridge C       | 0x0000_0000     | PAC.NONSECC                 |

| 255:224  | USERCRC                   | CRC of NVM User Row bits 223:64                        | 0x8433651E      | Boot ROM                    |

#### Note:

- 1. The PAC Peripheral is always secured regardless of its bit value

- 2. The IDAU and NVMCTRL peripherals are always secured regardless of their bit values.

- 3. The DSU peripheral is always non-secured regardless of its bit value.

###

1. BOD12 is calibrated in production and its calibration parameters must not be changed to ensure the correct device behavior.

| Table 10-11. | SAM L11 | UROW | Mapping |

|--------------|---------|------|---------|

|--------------|---------|------|---------|

| Offset | Bit<br>Pos. |                              | Name                 |               |  |             |  |  |

|--------|-------------|------------------------------|----------------------|---------------|--|-------------|--|--|

| 0x00   | 7:0         | BOD33 Level                  | Level - NSULCK SULCK |               |  |             |  |  |

| 0x01   | 15:8        | BOD33                        | Action               | BOD33 Disable |  | BOD33 Level |  |  |

| 0x02   | 23:16       | BOD12 Calibration Parameters |                      |               |  |             |  |  |

20.8.9 Value

|        | Name:<br>Offset:<br>Reset:<br>Property: | VALUE<br>0x10<br>0x00000000<br>- |    |       |         |    |    |    |

|--------|-----------------------------------------|----------------------------------|----|-------|---------|----|----|----|

| Bit    | 31                                      | 30                               | 29 | 28    | 27      | 26 | 25 | 24 |

|        |                                         |                                  |    |       |         |    |    |    |

| Access |                                         |                                  |    |       |         |    |    |    |

| Reset  |                                         |                                  |    |       |         |    |    |    |

| Bit    | 23                                      | 22                               | 21 | 20    | 19      | 18 | 17 | 16 |

|        |                                         |                                  |    | VALUE | [23:16] |    |    |    |

| Access | R                                       | R                                | R  | R     | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                | 0  | 0     | 0       | 0  | 0  | 0  |

| Bit    | 15                                      | 14                               | 13 | 12    | 11      | 10 | 9  | 8  |

|        |                                         |                                  |    | VALUE | E[15:8] |    |    |    |

| Access | R                                       | R                                | R  | R     | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                | 0  | 0     | 0       | 0  | 0  | 0  |

|        |                                         |                                  |    |       |         |    |    |    |

| Bit    | 7                                       | 6                                | 5  | 4     | 3       | 2  | 1  | 0  |

|        |                                         |                                  |    |       | E[7:0]  |    |    |    |

| Access | R                                       | R                                | R  | R     | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                | 0  | 0     | 0       | 0  | 0  | 0  |

**Bits 23:0 – VALUE[23:0]** Measurement Value Result from measurement.

#### 23.8.1 Event Control

| Name:     | EVCTRL               |

|-----------|----------------------|

| Offset:   | 0x00                 |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2       | 1      | 0     |

|--------|---|---|---|---|---|---------|--------|-------|

|        |   |   |   |   |   | TUNEINV | TUNEEI | CFDEO |

| Access |   |   |   |   |   | R/W     | R/W    | R/W   |

| Reset  |   |   |   |   |   | 0       | 0      | 0     |

#### Bit 2 – TUNEINV Tune Event Input Invert

This bit is used to invert the input event of the DFLLULP tuner.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | Tune event input source is not inverted. |

| 1     | Tune event input source is inverted.     |

#### Bit 1 – TUNEEI Tune Event Input Enable

This bit is used to enable the input event of the DFLLULP tuner.

| Value | Description                                                           |

|-------|-----------------------------------------------------------------------|

| 0     | A new closed loop tuning will not be triggered on any incoming event. |

| 1     | A new closed loop tuning will be triggered on any incoming event.     |

#### Bit 0 – CFDEO Clock Failure Detector Event Output Enable

This bit indicates whether the Clock Failure detector event output is enabled or not and an output event will be generated when the Clock Failure detector detects a clock failure

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | Clock Failure detector event output is disabled and no event will be generated. |

| 1     | Clock Failure detector event output is enabled and an event will be generated.  |

## SAM L10/L11 Family OSC32KCTRL – 32KHz Oscillators Controller

#### Name: OSCULP32K Offset: 0x1C Reset: 0x0000XX06 Property: **PAC Write-Protection** Bit 31 30 29 28 27 26 25 24 Access Reset Bit 23 22 21 20 19 18 17 16 Access Reset 15 Bit 14 13 12 11 10 9 8 WRTLOCK CALIB[4:0] R/W R/W R/W R/W R/W R/W Access 0 Reset х х х х х Bit 7 6 5 4 3 2 0 1 ULP32KSW R/W Access 0 Reset

#### 24.8.9 32KHz Ultra Low-Power Internal Oscillator (OSCULP32K) Control

#### Bit 15 – WRTLOCK Write Lock

This bit locks the OSCULP32K register for future writes to fix the OSCULP32K configuration.

| Val | lue | Description                                |

|-----|-----|--------------------------------------------|

| 0   |     | The OSCULP32K configuration is not locked. |

| 1   |     | The OSCULP32K configuration is locked.     |

#### Bits 12:8 - CALIB[4:0] Oscillator Calibration

These bits control the oscillator calibration.

These bits are loaded from Flash Calibration at startup.

#### Bit 5 – ULP32KSW OSCULP32K Clock Switch Enable

| Value | е | Description                                                      |

|-------|---|------------------------------------------------------------------|

| 0     |   | OSCULP32K is not switched and provided by the ULP32K oscillator. |

| 1     |   | OSCULP32K is switched to be provided by the XOSC32K oscillator.  |

#### 25.8.2 Interrupt Enable Set

| Name:     | INTENSET             |

|-----------|----------------------|

| Offset:   | 0x04                 |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

| Bit    | 31 | 30 | 29 | 28 | 27         | 26       | 25       | 24       |

|--------|----|----|----|----|------------|----------|----------|----------|

|        |    |    |    |    |            |          |          |          |

| Access |    |    |    |    |            |          |          |          |

| Reset  |    |    |    |    |            |          |          |          |

|        |    |    |    |    |            |          |          |          |

| Bit    | 23 | 22 | 21 | 20 | 19         | 18       | 17       | 16       |

|        |    |    |    |    |            |          |          |          |

| Access |    |    |    |    |            |          |          |          |

| Reset  |    |    |    |    |            |          |          |          |

|        |    |    |    |    |            |          |          |          |

| Bit    | 15 | 14 | 13 | 12 | 11         | 10       | 9        | 8        |

|        |    |    |    |    | ULPVREFRDY | VCORERDY |          | VREGRDY  |

| Access |    |    |    |    | R/W        | R/W      |          | R/W      |

| Reset  |    |    |    |    | 0          | 0        |          | 0        |

|        |    |    |    |    |            |          |          |          |

| Bit    | 7  | 6  | 5  | 4  | 3          | 2        | 1        | 0        |

|        |    |    |    |    |            | B33SRDY  | BOD33DET | BOD33RDY |

| Access |    |    |    |    |            | R/W      | R/W      | R/W      |

| Reset  |    |    |    |    |            | 0        | 0        | 0        |

**Bit 11 – ULPVREFRDY** Low Power Voltage Reference Ready Interrupt Enable Writing a '0' to this bit has no effect.

The ULPVREFRDY bit is set on a zero-to-one transition of the Low Power Voltage Reference Ready bit in the Status register (STATUS.ULPVREFRDY).

| Value | Description                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------|

| 0     | The Low Power Ready interrupt is disabled.                                                                                     |

| 1     | The Low Power Ready interrupt is enabled and an interrupt request will be generated when the ULPVREFRDY Interrupt Flag is set. |

Bit 10 – VCORERDY VDDCORE Voltage Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the VDDCORE Ready Interrupt Enable bit, which enables the VDDCORE Ready interrupt.

| Value | Description                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------------------|

| 0     | The VDDCORE Ready interrupt is disabled.                                                                                   |

| 1     | The VDDCORE Ready interrupt is enabled and an interrupt request will be generated when the VCORERDY Interrupt Flag is set. |

If the CPU accesses the registers which are source for DMA request set/clear condition, the DMA request can be lost or the DMA transfer can be corrupted, if enabled.

#### 27.6.4 Interrupts

The RTC has the following interrupt sources:

- Overflow (OVF): Indicates that the counter has reached its top value and wrapped to zero.

- Tamper (TAMPER): Indicates detection of valid signal on a tamper input pin or tamper event input.

- Compare (CMPn): Indicates a match between the counter value and the compare register.

- Alarm (ALARMn): Indicates a match between the clock value and the alarm register.

- Period n (PERn): The corresponding bit in the prescaler has toggled. Refer to 27.6.8.1 Periodic Intervals for details.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs. Each interrupt can be individually enabled by setting the corresponding bit in the Interrupt Enable Set register (INTENSET=1), and disabled by setting the corresponding bit in the Interrupt Enable Clear register (INTENCLR=1).

An interrupt request is generated when the interrupt flag is raised and the corresponding interrupt is enabled. The interrupt request remains active until either the interrupt flag is cleared, the interrupt is disabled or the RTC is reset. See the description of the INTFLAG registers for details on how to clear interrupt flags.

All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. Refer to the Nested Vector Interrupt Controller for details. The user must read the INTFLAG register to determine which interrupt condition is present.

**Note:** Interrupts must be globally enabled for interrupt requests to be generated. Refer to the Nested Vector Interrupt Controller for details.

#### 27.6.5 Events

The RTC can generate the following output events:

- Overflow (OVF): Generated when the counter has reached its top value and wrapped to zero.

- Tamper (TAMPER): Generated on detection of valid signal on a tamper input pin or tamper event input.

- Compare (CMPn): Indicates a match between the counter value and the compare register.

- Alarm (ALARM): Indicates a match between the clock value and the alarm register.

- Period n (PERn): The corresponding bit in the prescaler has toggled. Refer to 27.6.8.1 Periodic Intervals for details.

- Periodic Daily (PERD): Generated when the COUNT/CLOCK has incremented at a fixed period of time.

Setting the Event Output bit in the Event Control Register (EVCTRL.xxxEO=1) enables the corresponding output event. Writing a zero to this bit disables the corresponding output event. Refer to the EVSYS - Event System for details on configuring the event system.

The RTC can take the following actions on an input event:

• Tamper (TAMPEVT): Capture the RTC counter to the timestamp register. See *Tamper Detection*.

Writing a one to an Event Input bit into the Event Control register (EVCTRL.xxxEI) enables the corresponding action on input event. Writing a zero to this bit disables the corresponding action on input event.

#### 27.6.8 Additional Features

#### 27.6.8.1 Periodic Intervals

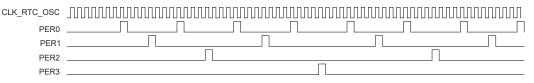

The RTC prescaler can generate interrupts and events at periodic intervals, allowing flexible system tick creation. Any of the upper eight bits of the prescaler (bits 2 to 9) can be the source of an interrupt/event. When one of the eight Periodic Event Output bits in the Event Control register (EVCTRL.PEREO[n=0..7]) is '1', an event is generated on the 0-to-1 transition of the related bit in the prescaler, resulting in a periodic event frequency of:

$$f_{\text{PERIODIC}(n)} = \frac{f_{\text{CLK}_{\text{RTC}_{\text{OSC}}}}}{2^{n+3}}$$

$f_{CLK\_RTC\_OSC}$  is the frequency of the internal prescaler clock CLK\_RTC\_OSC, and n is the position of the EVCTRL.PEREOn bit. For example, PER0 will generate an event every eight CLK\_RTC\_OSC cycles, PER1 every 16 cycles, etc. This is shown in the figure below.

Periodic events are independent of the prescaler setting used by the RTC counter, except if CTRLA.PRESCALER is zero. Then, no periodic events will be generated.

#### Figure 27-5. Example Periodic Events

#### 27.6.8.2 Frequency Correction

The RTC Frequency Correction module employs periodic counter corrections to compensate for a tooslow or too-fast oscillator. Frequency correction requires that CTRLA.PRESCALER is greater than 1.

The digital correction circuit adds or subtracts cycles from the RTC prescaler to adjust the frequency in approximately 1ppm steps. Digital correction is achieved by adding or skipping a single count in the prescaler once every 8192 CLK\_RTC\_OSC cycles. The Value bit group in the Frequency Correction register (FREQCORR.VALUE) determines the number of times the adjustment is applied over 128 of these periods. The resulting correction is as follows:

Correction in ppm  $= \frac{\text{FREQCORR.VALUE}}{8192 \cdot 128} \cdot 10^6 \text{ppm}$

This results in a resolution of 0.95367ppm.

The Sign bit in the Frequency Correction register (FREQCORR.SIGN) determines the direction of the correction. A positive value will add counts and increase the period (reducing the frequency), and a negative value will reduce counts per period (speeding up the frequency).

Digital correction also affects the generation of the periodic events from the prescaler. When the correction is applied at the end of the correction cycle period, the interval between the previous periodic event and the next occurrence may also be shortened or lengthened depending on the correction value.

#### 27.6.8.3 General Purpose Registers

The RTC includes four General Purpose registers (GPn). These registers are reset only when the RTC is reset or when tamper detection occurs while CTRLA.GPTRST=1, and remain powered while the RTC is powered. They can be used to store user-defined values while other parts of the system are powered off.

The general purpose registers 2\*n and 2\*n+1 are enabled by writing a '1' to the General Purpose Enable bit n in the Control B register (CTRLB.GPnEN).

© 2018 Microchip Technology Inc.

RTC – Real-Time Counter

| Name:<br>Offset:<br>Reset:<br>Property: |           | SYNCBUSY<br>0x10<br>0x00000000<br>- |       |    |       |          |        |       |

|-----------------------------------------|-----------|-------------------------------------|-------|----|-------|----------|--------|-------|

| Bit                                     | 31        | 30                                  | 29    | 28 | 27    | 26       | 25     | 24    |

|                                         |           |                                     |       |    |       |          |        |       |

| Access                                  |           |                                     |       |    |       |          |        |       |

| Reset                                   |           |                                     |       |    |       |          |        |       |

| 5.1                                     | 22        | 22                                  | 0.4   | 00 | 10    | 10       | 47     | 40    |

| Bit                                     | 23        | 22                                  | 21    | 20 | 19    | 18       | 17     | 16    |

|                                         |           |                                     |       |    |       |          |        | [1:0] |

| Access                                  |           |                                     |       |    |       |          | R      | R     |

| Reset                                   |           |                                     |       |    |       |          | 0      | 0     |

|                                         |           |                                     |       |    |       |          |        |       |

| Bit                                     |           | 14                                  | 13    | 12 | 11    | 10       | 9      | 8     |

|                                         | COUNTSYNC |                                     |       |    |       |          |        |       |

| Access                                  | R         |                                     |       |    |       |          |        |       |

| Reset                                   | 0         |                                     |       |    |       |          |        |       |

|                                         |           |                                     |       |    |       |          |        |       |

| Bit                                     | 7         | 6                                   | 5     | 4  | 3     | 2        | 1      | 0     |

|                                         |           |                                     | COMP0 |    | COUNT | FREQCORR | ENABLE | SWRST |

| Access                                  |           |                                     | R     |    | R     | R        | R      | R     |

| Reset                                   |           |                                     | 0     |    | 0     | 0        | 0      | 0     |

#### 27.8.8 Synchronization Busy in COUNT32 mode (CTRLA.MODE=0)

Bits 17:16 - GPn[1:0] General Purpose n Synchronization Busy Status

| Ν | /alue | Description                                         |

|---|-------|-----------------------------------------------------|

| 0 | )     | Write synchronization for GPn register is complete. |

| 1 | -     | Write synchronization for GPn register is ongoing.  |

Bit 15 – COUNTSYNC Count Read Sync Enable Synchronization Busy Status

| Value | Description                                                |

|-------|------------------------------------------------------------|

| 0     | Write synchronization for CTRLA.COUNTSYNC bit is complete. |

| 1     | Write synchronization for CTRLA.COUNTSYNC bit is ongoing.  |

#### Bit 5 – COMP0 Compare 0 Synchronization Busy Status

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | Write synchronization for COMP0 register is complete. |

| 1     | Write synchronization for COMP0 register is ongoing.  |

#### **Bit 3 – COUNT** Count Value Synchronization Busy Status

| Value | Description                                                |

|-------|------------------------------------------------------------|

| 0     | Read/write synchronization for COUNT register is complete. |

| 1     | Read/write synchronization for COUNT register is ongoing.  |

#### 27.10.4 Interrupt Enable Clear in COUNT16 mode (CTRLA.MODE=1)

Name:INTENCLROffset:0x08Reset:0x0000Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set (INTENSET) register.

| Bit    | 15          | 14          | 13          | 12          | 11          | 10          | 9           | 8           |

|--------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

|        | OVF         | TAMPER      |             |             |             |             |             |             |

| Access | R/W         | R/W         |             |             |             |             |             |             |

| Reset  | 0           | 0           |             |             |             |             |             |             |

|        |             |             |             |             |             |             |             |             |

| Bit    | 7           | 6           | 5           | 4           | 3           | 2           | 1           | 0           |

|        |             |             |             |             |             |             |             |             |

|        | PER7        | PER6        | PER5        | PER4        | PER3        | PER2        | CMP1        | CMP0        |

| Access | PER7<br>R/W | PER6<br>R/W | PER5<br>R/W | PER4<br>R/W | PER3<br>R/W | PER2<br>R/W | CMP1<br>R/W | CMP0<br>R/W |

#### Bit 15 – OVF Overflow Interrupt Enable

Writing a '0' to this bit has no effect. Writing a '1' to this bit will clear the Overflow Interrupt Enable bit, which disables the Overflow interrupt.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Overflow interrupt is disabled. |

| 1     | The Overflow interrupt is enabled.  |

#### **Bit 14 – TAMPER** Tamper Interrupt Enable

Writing a '0' to this bit has no effect. Writing a '1' to this bit will clear the Tamper Interrupt Enable bit, which disables the Tamper interrupt.

| Value | Description                       |

|-------|-----------------------------------|

| 0     | The Tamper interrupt is disabled. |

| 1     | The Tamper interrupt is enabled.  |

#### Bits 0, 1 – CMPn Compare n Interrupt Enable [n = 1..0]

Writing a '0' to this bit has no effect. Writing a '1' to this bit will clear the Compare n Interrupt Enable bit, which disables the Compare n interrupt.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | The Compare n interrupt is disabled. |

| 1     | The Compare n interrupt is enabled.  |

#### Bits 0, 1, 2, 3, 4, 5, 6, 7 – PERn Periodic Interval n Interrupt Enable [n = 7..0]

Writing a '0' to this bit has no effect. Writing a '1' to this bit will clear the Periodic Interval n Interrupt Enable bit, which disables the Periodic Interval n interrupt.

| Va | lue | Description                                |

|----|-----|--------------------------------------------|

| 0  |     | Periodic Interval n interrupt is disabled. |

| 1  |     | Periodic Interval n interrupt is enabled.  |

#### 28.10.5 Next Descriptor Address

Reset

Name:DESCADDROffset:0x0CProperty:-

The DESCADDR register offset is relative to (BASEADDR or WRBADDR) + Channel Number \* 0x10

| Bit    | 31 | 30 | 29 | 28     | 27        | 26 | 25 | 24 |

|--------|----|----|----|--------|-----------|----|----|----|

|        |    |    |    | DESCAD | DR[31:24] |    |    |    |

| Access |    |    |    |        |           |    |    |    |

| Reset  |    |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

| Bit    | 23 | 22 | 21 | 20     | 19        | 18 | 17 | 16 |

|        |    |    |    | DESCAD | DR[23:16] |    |    |    |

| Access |    |    |    |        |           |    |    |    |

| Reset  |    |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

| Bit    | 15 | 14 | 13 | 12     | 11        | 10 | 9  | 8  |

|        |    |    |    | DESCAL | DDR[15:8] |    |    |    |

| Access | L  |    |    |        |           |    |    |    |

| Reset  |    |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

| Bit    | 7  | 6  | 5  | 4      | 3         | 2  | 1  | 0  |

|        |    |    |    | DESCA  | DDR[7:0]  |    |    |    |

| Access | L  |    |    |        |           |    |    |    |

|        |    |    |    |        |           |    |    |    |

Bits 31:0 – DESCADDR[31:0] Next Descriptor Address

This bit group holds the SRAM address of the next descriptor. The value must be 128-bit aligned. If the value of this SRAM register is 0x00000000, the transaction will be terminated when the DMAC tries to load the next transfer descriptor.

To issue a command, the CTRLA.CMD bits must be written along with the CTRLA.CMDEX value. When a command is issued, STATUS.READY is cleared and rises again when the command has completed. INTFLAG.DONE is also set when a command completes. Any commands written while INTFLAG.READY is low will be ignored.

The CTRLB and CTRLC registers must be used to control the power reduction mode, read wait states, and the write mode.

#### 30.6.4.1 NVM Read

Reading from the FLASH is performed via the AHB bus. Read data is available after the configured number of read wait states (CTRLB.RWS) set in the NVM Controller.

The number of cycles data are delayed to the AHB bus is determined by the read wait states.

Reading the NVM main address space while a programming or erase operation is ongoing on the NVM main array results in an AHB bus stall until the end of the operation. Reading the NVM main array does not stall the bus when the Data FLASH is being programmed or erased.

#### 30.6.4.2 DATA FLASH Read

Reading from the Data FLASH is performed via the AHB bus by addressing the Data FLASH address space directly.

Read timings are increased by one cycle compared to regular FLASH read timings when access size is Byte or half-Word. The AHB data phase is twice as long in case of full-Word-size access.

It is not possible to read the Data FLASH while the NVM main array is being written or erased (the read is stalled), whereas the Data FLASH can be written or erased while the main array is being read.

The Data FLASH address space is not cached, therefore it is recommended to limit access to this area for performance and power consumption considerations.

#### 30.6.4.3 NVM Write

Data to be written to the NVM block are first written to and stored in an internal buffer called the page buffer. The page buffer contains the same number of bytes as an NVM page. Writes to the page buffer must be 16 or 32 bits. 8-bit writes to the page buffer are not allowed and will cause a bus error.

Both FLASH and DATA FLASH share the same page buffer. Writing to the NVM block via the AHB bus is performed by a load operation to the page buffer. For each AHB bus write, the address is stored in the ADDR register. After the page buffer has been loaded with the required number of bytes, the page can be written to the array pointed by ADDR by setting CTRLA.CMD to 'Write Page' and setting the key value to CMDEX. The LOAD bit in the STATUS register indicates whether the page buffer has been loaded or not.

If the NVMCTRL is busy processing a write command (STATUS.READY=0), then the AHB bus is stalled upon AHB write until the ongoing command completes.

The NVM Controller requires that an erase must be done before programming. Rows can be individually erased by the Erase Row command to erase a row.

Automatic page writes are enabled by writing the manual write bit to zero (CTRLB.MANW=0). This will trigger a write operation to the page addressed by ADDR when the last location of the page is written.

Because the address is automatically stored in ADDR during the APB bus write operation, the last given address will be present in the ADDR register. There is no need to load the ADDR register manually, unless a different page in memory is to be written. The page buffer is automatically cleared upon a 'Write Page' command completion.

## SAM L10/L11 Family PORT - I/O Pin Controller

Writing a '1' to a bit will clear the corresponding bit in the DIR register, which configures the I/O pin as an input.

| Value | Description                                                              |

|-------|--------------------------------------------------------------------------|

| 0     | The corresponding I/O pin in the PORT group will keep its configuration. |

| 1     | The corresponding I/O pin in the PORT group is configured as input.      |

### Bit 2 – RXC Receive Complete Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Receive Complete Interrupt Enable bit, which disables the Receive Complete interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Receive Complete interrupt is disabled. |

| 1     | Receive Complete interrupt is enabled.  |

**Bit 1 – TXC** Transmit Complete Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Transmit Complete Interrupt Enable bit, which disables the Receive Complete interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | Transmit Complete interrupt is disabled. |

| 1     | Transmit Complete interrupt is enabled.  |

**Bit 0 – DRE** Data Register Empty Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Data Register Empty Interrupt Enable bit, which disables the Data Register Empty interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | Data Register Empty interrupt is disabled. |

| 1     | Data Register Empty interrupt is enabled.  |

#### Bit 0 – DRE Data Register Empty

This flag is cleared by writing new data to DATA.

This flag is set when DATA is empty and ready for new data to transmit.

Writing '0' to this bit has no effect.

Writing '1' to this bit has no effect.

The missing ACK response can indicate that the  $I^2C$  slave is busy with other tasks or sleeping. Therefore, it is not able to respond. In this event, the next step can be either issuing a stop condition (recommended) or resending the address packet by a repeated start condition. When using SMBus logic, the slave must ACK the address. If there is no response, it means that the slave is not available on the bus.

#### Case 3: Address packet transmit complete - Write packet, Master on Bus set

If the I<sup>2</sup>C master receives an acknowledge response from the I<sup>2</sup>C slave, INTFLAG.MB will be set and STATUS.RXNACK will be cleared. The clock hold is active at this point, preventing further activity on the bus.

In this case, the software implementation becomes highly protocol dependent. Three possible actions can enable the I<sup>2</sup>C operation to continue:

- Initiate a data transmit operation by writing the data byte to be transmitted into DATA.DATA.

- Transmit a new address packet by writing ADDR.ADDR. A repeated start condition will automatically be inserted before the address packet.

- Issue a stop condition, consequently terminating the transaction.

#### Case 4: Address packet transmit complete – Read packet, Slave on Bus set

If the I<sup>2</sup>C master receives an ACK from the I<sup>2</sup>C slave, the I<sup>2</sup>C master proceeds to receive the next byte of data from the I<sup>2</sup>C slave. When the first data byte is received, the Slave on Bus bit in the Interrupt Flag register (INTFLAG.SB) will be set and STATUS.RXNACK will be cleared. The clock hold is active at this point, preventing further activity on the bus.

In this case, the software implementation becomes highly protocol dependent. Three possible actions can enable the I<sup>2</sup>C operation to continue:

- Let the I<sup>2</sup>C master continue to read data by acknowledging the data received. ACK can be sent by software, or automatically in smart mode.

- Transmit a new address packet.

- Terminate the transaction by issuing a stop condition.

**Note:** An ACK or NACK will be automatically transmitted if smart mode is enabled. The Acknowledge Action bit in the Control B register (CTRLB.ACKACT) determines whether ACK or NACK should be sent.

#### 37.6.2.4.3 Transmitting Data Packets

When an address packet with direction Master Write (see Figure 37-3) was transmitted successfully, INTFLAG.MB will be set. The I<sup>2</sup>C master will start transmitting data via the I<sup>2</sup>C bus by writing to DATA.DATA, and monitor continuously for packet collisions. I

If a collision is detected, the I<sup>2</sup>C master will lose arbitration and STATUS.ARBLOST will be set. If the transmit was successful, the I<sup>2</sup>C master will receive an ACK bit from the I<sup>2</sup>C slave, and STATUS.RXNACK will be cleared. INTFLAG.MB will be set in both cases, regardless of arbitration outcome.

It is recommended to read STATUS.ARBLOST and handle the arbitration lost condition in the beginning of the I<sup>2</sup>C Master on Bus interrupt. This can be done as there is no difference between handling address and data packet arbitration.

STATUS.RXNACK must be checked for each data packet transmitted before the next data packet transmission can commence. The I<sup>2</sup>C master is not allowed to continue transmitting data packets if a NACK is received from the I<sup>2</sup>C slave.

## 37.9 Register Summary - I2C Master

| Offset | Name     | Bit Pos. |          |          |        |          |           |        |            |         |

|--------|----------|----------|----------|----------|--------|----------|-----------|--------|------------|---------|

|        |          | 7:0      | RUNSTDBY |          |        |          | MODE[2:0] |        | ENABLE     | SWRST   |

| 0x00   |          | 15:8     |          |          |        |          |           |        |            |         |

|        | CTRLA    | 23:16    | SEXTTOEN | MEXTTOEN | SDAHC  | LD[1:0]  |           |        |            | PINOUT  |

|        |          | 31:24    |          | LOWTOUT  | INACTO | UT[1:0]  | SCLSM     |        | SPEE       | D[1:0]  |

|        |          | 7:0      |          |          |        |          |           |        |            |         |

| 004    |          | 15:8     |          |          |        |          |           |        | QCEN       | SMEN    |

| 0x04   | CTRLB    | 23:16    |          |          |        |          |           | ACKACT | CME        | D[1:0]  |

|        |          | 31:24    |          |          |        |          |           |        |            |         |

| 0x08   |          |          |          |          |        |          |           |        |            |         |

|        | Reserved |          |          |          |        |          |           |        |            |         |

| 0x0B   |          |          |          |          |        |          |           |        |            |         |

|        |          | 7:0      |          |          |        | BAL      | JD[7:0]   |        |            |         |

| 0.000  | BAUD     | 15:8     |          |          |        | BAUD     | LOW[7:0]  |        |            |         |

| 0x0C   | BAUD     | 23:16    |          |          |        | HSBA     | AUD[7:0]  |        |            |         |

|        |          | 31:24    |          |          |        | HSBAU    | DLOW[7:0] |        |            |         |

| 0x10   |          |          |          |          |        |          |           |        |            |         |

|        | Reserved |          |          |          |        |          |           |        |            |         |

| 0x13   |          |          |          |          |        |          |           |        |            |         |

| 0x14   | INTENCLR | 7:0      | ERROR    |          |        |          |           |        | SB         | MB      |

| 0x15   | Reserved |          |          |          |        |          |           |        |            |         |

| 0x16   | INTENSET | 7:0      | ERROR    |          |        |          |           |        | SB         | MB      |

| 0x17   | Reserved |          |          |          |        |          |           |        |            |         |

| 0x18   | INTFLAG  | 7:0      | ERROR    |          |        |          |           |        | SB         | MB      |

| 0x19   | Reserved |          |          |          |        |          |           |        |            |         |

| 0.44   | 0747110  | 7:0      | CLKHOLD  | LOWTOUT  | BUSSTA | ATE[1:0] |           | RXNACK | ARBLOST    | BUSERF  |

| 0x1A   | STATUS   | 15:8     |          |          |        |          |           | LENERR | SEXTTOUT   | MEXTTOL |

|        |          | 7:0      |          |          |        |          |           | SYSOP  | ENABLE     | SWRST   |

|        |          | 15:8     |          |          |        |          |           |        |            |         |

| 0x1C   | SYNCBUSY | 23:16    |          |          |        |          |           |        |            |         |

|        |          | 31:24    |          |          |        |          |           |        |            |         |

| 0x20   |          |          |          |          |        |          |           |        |            |         |

|        | Reserved |          |          |          |        |          |           |        |            |         |

| 0x23   |          |          |          |          |        |          |           |        |            |         |

|        |          | 7:0      |          |          |        | ADI      | DR[7:0]   |        |            | 1       |

| 0.04   | 4000     | 15:8     | TENBITEN | HS       | LENEN  |          |           |        | ADDR[10:8] |         |

| 0x24   | ADDR     | 23:16    |          |          |        | LE       | N[7:0]    |        |            |         |

|        |          | 31:24    |          |          |        |          |           |        |            |         |

| 0.00   | D        | 7:0      |          |          |        | DA       | FA[7:0]   |        |            |         |

| 0x28   | DATA     | 15:8     |          |          |        |          |           |        |            |         |

| 0x2A   |          |          |          |          |        |          |           |        |            |         |

|        | Reserved |          |          |          |        |          |           |        |            |         |

| 0x2F   |          |          |          |          |        |          |           |        |            |         |

| 0x30   | DBGCTRL  | 7:0      |          |          |        |          |           |        |            | DBGSTO  |

#### 37.10.6 Interrupt Flag Status and Clear

| Name:<br>Offset:<br>Reset:<br>Property: |       | INTFLAG<br>0x18<br>0x00<br>- |   |   |   |   |     |     |

|-----------------------------------------|-------|------------------------------|---|---|---|---|-----|-----|

| Bit                                     | 7     | 6                            | 5 | 4 | 3 | 2 | 1   | 0   |

|                                         | ERROR |                              |   |   |   |   | SB  | MB  |

| Access                                  | R/W   | ŀ                            |   |   |   |   | R/W | R/W |

| Reset                                   | 0     |                              |   |   |   |   | 0   | 0   |

#### Bit 7 – ERROR Error

This flag is cleared by writing '1' to it.

This bit is set when any error is detected. Errors that will set this flag have corresponding status bits in the STATUS register. These status bits are LENERR, SEXTTOUT, MEXTTOUT, LOWTOUT, ARBLOST, and BUSERR.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the flag.

#### Bit 1 – SB Slave on Bus

The Slave on Bus flag (SB) is set when a byte is successfully received in master read mode, i.e., no arbitration lost or bus error occurred during the operation. When this flag is set, the master forces the SCL line low, stretching the I<sup>2</sup>C clock period. The SCL line will be released and SB will be cleared on one of the following actions:

- Writing to ADDR.ADDR

- Writing to DATA.DATA

- Reading DATA.DATA when smart mode is enabled (CTRLB.SMEN)

- Writing a valid command to CTRLB.CMD

Writing '1' to this bit location will clear the SB flag. The transaction will not continue or be terminated until one of the above actions is performed.

Writing '0' to this bit has no effect.

#### Bit 0 – MB Master on Bus

This flag is set when a byte is transmitted in master write mode. The flag is set regardless of the occurrence of a bus error or an arbitration lost condition. MB is also set when arbitration is lost during sending of NACK in master read mode, or when issuing a start condition if the bus state is unknown. When this flag is set and arbitration is not lost, the master forces the SCL line low, stretching the I<sup>2</sup>C clock period. The SCL line will be released and MB will be cleared on one of the following actions:

- Writing to ADDR.ADDR

- Writing to DATA.DATA

- Reading DATA.DATA when smart mode is enabled (CTRLB.SMEN)

- Writing a valid command to CTRLB.CMD

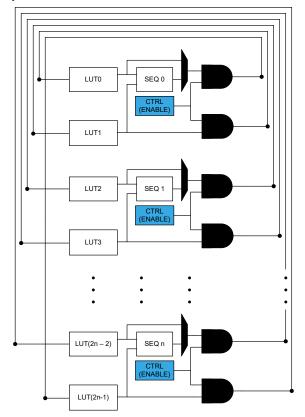

#### Figure 40-5. Linked LUT Input Selection

#### Internal Events Inputs Selection (EVENT)

Asynchronous events from the Event System can be used as input selection, as shown in Figure 40-6. For each LUT, one event input line is available and can be selected on each LUT input. Before enabling the event selection by writing LUTCTRLx.INSELy=EVENT, the Event System must be configured first.

By default CCL includes an edge detector. When the event is received, an internal strobe is generated when a rising edge is detected. The pulse duration is one GCLK\_CCL clock cycle. Writing the LUTCTRLx.INSELy=ASYNCEVENT will disable the edge detector. In this case, it is possible to combine an asynchronous event input with any other input source. This is typically useful with event levels inputs (external IO pin events, as example). The following steps ensure proper operation:

- 1. Enable the GCLK\_CCL clock.

- 2. Configure the Event System to route the event asynchronously.

- 3. Select the event input type (LUTCTRLx.INSEL).

- 4. If a strobe must be generated on the event input falling edge, write a '1' to the Inverted Event Input Enable bit in LUT Control register (LUTCTRLx.INVEI).

- 5. Enable the event input by writing the Event Input Enable bit in LUT Control register (LUTCTRLx.LUTEI) to '1'.

#### Bit 0 – SWRST Software Reset

Writing a '0' to this bit has no effect.

Writing a '1' to this bit resets all registers in the ADC, except DBGCTRL, to their initial state, and the ADC will be disabled.

Writing a '1' to CTRL.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded.

Due to synchronization there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | There is no reset operation ongoing. |

| 1     | The reset operation is ongoing.      |