Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 40MHz                                                                    |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                               |

| Number of I/O              | 52                                                                       |

| Program Memory Size        | 64KB (32K x 16)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 1K x 8                                                                   |

| RAM Size                   | 3.25K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 4.2V ~ 5.5V                                                              |

| Data Converters            | A/D 16x10b                                                               |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 68-LCC (J-Lead)                                                          |

| Supplier Device Package    | 68-PLCC (24.23x24.23)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f6680-e-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 OSCILLATOR CONFIGURATIONS

# 2.1 Oscillator Types

The PIC18F6585/8585/6680/8680 devices can be operated in eleven different oscillator modes. The user can program four configuration bits (FOSC3, FOSC2, FOSC1 and FOSC0) to select one of these eleven modes:

- 1. LP Low-Power Crystal 2. XT Crvstal/Resonator 3. HS High-Speed Crystal/Resonator 4. RC External Resistor/Capacitor EC 5. External Clock ECIO External Clock with I/O 6. pin enabled

- 7. HS+PLL High-Speed Crystal/Resonator with PLL enabled

- 8. RCIO External Resistor/Capacitor with I/O pin enabled

- 9. ECIO+SPLL External Clock with software controlled PLL

- 10. ECIO+PLL External Clock with PLL and I/O pin enabled

- 11. HS+SPLL High-Speed Crystal/Resonator with software control

## 2.2 Crystal Oscillator/Ceramic Resonators

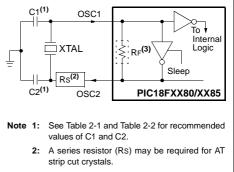

In XT, LP, HS, HS+PLL or HS+SPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 2-1 shows the pin connections.

The PIC18F6585/8585/6680/8680 oscillator design requires the use of a parallel cut crystal.

| Note: | Use of a series cut crystal may give a fre- |

|-------|---------------------------------------------|

|       | quency out of the crystal manufacturers     |

|       | specifications.                             |

FIGURE 2-1:

## CRYSTAL/CERAMIC RESONATOR OPERATION (HS, XT OR LP CONFIGURATION)

3: RF varies with the oscillator mode chosen.

# TABLE 2-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS

|      | Ranges Tested: |           |           |  |  |  |  |  |  |  |

|------|----------------|-----------|-----------|--|--|--|--|--|--|--|

| Mode | Freq           | C1        | C2        |  |  |  |  |  |  |  |

| ХТ   | 455 kHz        | 68-100 pF | 68-100 pF |  |  |  |  |  |  |  |

|      | 2.0 MHz        | 15-68 pF  | 15-68 pF  |  |  |  |  |  |  |  |

|      | 4.0 MHz        | 15-68 pF  | 15-68 pF  |  |  |  |  |  |  |  |

| HS   | 8.0 MHz        | 10-68 pF  | 10-68 pF  |  |  |  |  |  |  |  |

|      | 16.0 MHz       | 10-22 pF  | 10-22 pF  |  |  |  |  |  |  |  |

#### **These values are for design guidance only.** See notes following this table.

| Resonators Used:                                      |                       |             |  |  |  |  |  |

|-------------------------------------------------------|-----------------------|-------------|--|--|--|--|--|

| 2.0 MHz                                               | Murata Erie CSA2.00MG | $\pm 0.5\%$ |  |  |  |  |  |

| 4.0 MHz                                               | Murata Erie CSA4.00MG | $\pm 0.5\%$ |  |  |  |  |  |

| 8.0 MHz Murata Erie CSA8.00MT ± 0.5%                  |                       |             |  |  |  |  |  |

| 16.0 MHz Murata Erie CSA16.00MX ± 0.5%                |                       |             |  |  |  |  |  |

| All resonators used did not have built-in capacitors. |                       |             |  |  |  |  |  |

Note 1: Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- 2: When operating below 3V VDD, or when using certain ceramic resonators at any voltage, it may be necessary to use high gain HS mode, try a lower frequency resonator, or switch to a crystal oscillator.

- Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components, or verify oscillator performance.

| TABLE 3-1: TIME-OUT IN VARIOUS SITUATIO | NS |

|-----------------------------------------|----|

|-----------------------------------------|----|

| Oscillator                         | Power-up <sup>(;</sup>  | 2)               | _                | Wake-up from                  |  |

|------------------------------------|-------------------------|------------------|------------------|-------------------------------|--|

| Configuration                      | PWRTE = 0PWRTE = 1      |                  | Brown-out        | Sleep or<br>Oscillator Switch |  |

| HS with PLL enabled <sup>(1)</sup> | 72 ms + 1024 Tosc + 2ms | 1024 Tosc + 2 ms | 1024 Tosc + 2 ms | 1024 Tosc + 2 ms              |  |

| EC with PLL enabled <sup>(1)</sup> | 72 ms + 2ms             | 1.5 μs + 2 ms    | 2 ms             | 1.5 μs + 2 ms                 |  |

| HS, XT, LP                         | 72 ms + 1024 Tosc       | 1024 Tosc        | 1024 Tosc        | 1024 Tosc                     |  |

| EC                                 | 72 ms                   | 1.5 μs           | 1.5 μs           | 1.5 μs <sup>(3)</sup>         |  |

| External RC                        | 72 ms                   | 1.5 μs           | 1.5 μs           | 1.5 μs                        |  |

Note 1: 2 ms is the nominal time required for the 4x PLL to lock.

2: 72 ms is the nominal power-up timer delay if implemented.

3: 1.5 µs is the recovery time from Sleep. There is no recovery time from oscillator switch.

| REGISTER 5-1. REGISTER BITS AND I OSTITIONS | REGISTER 3-1: | RCON REGISTER BITS AND POSITIONS |

|---------------------------------------------|---------------|----------------------------------|

|---------------------------------------------|---------------|----------------------------------|

| R/W   | -0 | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-0 |

|-------|----|-----|-----|-------|-------|-------|-------|-------|

| IPE   | Ν  | —   | —   | RI    | TO    | PD    | POR   | BOR   |

| bit 7 |    |     |     |       |       |       |       | bit 0 |

Note: Refer to Section 4.14 "RCON Register" for bit definitions.

## TABLE 3-2: STATUS BITS, THEIR SIGNIFICANCE AND THE INITIALIZATION CONDITION FOR RCON REGISTER

| Condition                                        | Program<br>Counter    | RCON<br>Register | RI | то | PD | POR | BOR | STKFUL | STKUNF |

|--------------------------------------------------|-----------------------|------------------|----|----|----|-----|-----|--------|--------|

| Power-on Reset                                   | 0000h                 | 01 1100          | 1  | 1  | 1  | 0   | 0   | u      | u      |

| MCLR Reset during normal operation               | 0000h                 | 0u uuuu          | u  | u  | u  | u   | u   | u      | u      |

| Software Reset during normal operation           | 0000h                 | 00 uuuu          | 0  | u  | u  | u   | u   | u      | u      |

| Stack Full Reset during normal operation         | 0000h                 | 0u uull          | u  | u  | u  | u   | u   | u      | 1      |

| Stack Underflow Reset during<br>normal operation | 0000h                 | 0u uull          | u  | u  | u  | u   | u   | 1      | u      |

| MCLR Reset during Sleep                          | 0000h                 | 0u 10uu          | u  | 1  | 0  | u   | u   | u      | u      |

| WDT Reset                                        | 0000h                 | 0u 01uu          | 1  | 0  | 1  | u   | u   | u      | u      |

| WDT Wake-up                                      | PC + 2                | uu 00uu          | u  | 0  | 0  | u   | u   | u      | u      |

| Brown-out Reset                                  | 0000h                 | 01 11u0          | 1  | 1  | 1  | 1   | 0   | u      | u      |

| Interrupt wake-up from Sleep                     | PC + 2 <sup>(1)</sup> | uu 00uu          | u  | 1  | 0  | u   | u   | u      | u      |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0'

**Note 1:** When the wake-up is due to an interrupt and the GIEH or GIEL bits are set, the PC is loaded with the interrupt vector (000008h or 000018h).

| TABLE 3-3:            | INITIALIZA         | TION CONDI | HUNS FUR ALL REC                                      | GISTERS (CONTINU |                                 |  |

|-----------------------|--------------------|------------|-------------------------------------------------------|------------------|---------------------------------|--|

| Register              | Applicable Devices |            | Applicable Devices Power-on Reset,<br>Brown-out Reset |                  | Wake-up via WDT<br>or Interrupt |  |

| B5D7 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | xxxx xxxx                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B5D6 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B5D5 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B5D4 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B5D3 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B5D2 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B5D1 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B5D0 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B5DLC <sup>(7)</sup>  | PIC18F6X8X         | PIC18F8X8X | -xxx xxxx                                             | -uuu uuuu        | -uuu uuuu                       |  |

| B5EIDL <sup>(7)</sup> | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B5EIDH <sup>(7)</sup> | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B5SIDL <sup>(7)</sup> | PIC18F6X8X         | PIC18F8X8X | xxxx x-xx                                             | uuuu u-uu        | uuuu u-uu                       |  |

| B5SIDH <sup>(7)</sup> | PIC18F6X8X         | PIC18F8X8X | xxxx x-xx                                             | uuuu u-uu        | uuuu u-uu                       |  |

| B5CON <sup>(7)</sup>  | PIC18F6X8X         | PIC18F8X8X | 0000 0000                                             | 0000 0000        | uuuu uuuu                       |  |

| B4D7 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B4D6 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B4D5 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B4D4 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B4D3 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B4D2 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B4D1 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B4D0 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B4DLC <sup>(7)</sup>  | PIC18F6X8X         | PIC18F8X8X | -xxx xxxx                                             | -uuu uuuu        | -uuu uuuu                       |  |

| B4EIDL <sup>(7)</sup> | PIC18F6X8X         | PIC18F8X8X | xxxx xxxx                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B4EIDH <sup>(7)</sup> | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B4SIDL <sup>(7)</sup> | PIC18F6X8X         | PIC18F8X8X | xxxx x-xx                                             | uuuu u-uu        | uuuu u-uu                       |  |

| B4SIDH <sup>(7)</sup> | PIC18F6X8X         | PIC18F8X8X | xxxx xxxx                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B4CON <sup>(7)</sup>  | PIC18F6X8X         | PIC18F8X8X | 0000 0000                                             | 0000 0000        | uuuu uuuu                       |  |

| B3D7 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B3D6 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | XXXX XXXX                                             | uuuu uuuu        | uuuu uuuu                       |  |

| B3D5 <sup>(7)</sup>   | PIC18F6X8X         | PIC18F8X8X | xxxx xxxx                                             | uuuu uuuu        | uuuu uuuu                       |  |

|                       | *                  |            |                                                       |                  |                                 |  |

# TABLE 3-3: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

Note 1: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 4: See Table 3-2 for Reset value for specific condition.

- 5: Bit 6 of PORTA, LATA, and TRISA are enabled in ECIO and RCIO Oscillator modes only. In all other oscillator modes, they are disabled and read '0'.

- 6: Bit 6 of PORTA, LATA and TRISA are not available on all devices. When unimplemented, they read '0'.

- 7: This register reads all '0's until ECAN is set up in Mode 1 or Mode 2.

# 5.5.2 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

# 5.5.3 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed if needed. The WRERR bit is set when a write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation. In these situations, users can check the WRERR bit and rewrite the location.

# 5.5.4 PROTECTION AGAINST SPURIOUS WRITES

To protect against spurious writes to Flash program memory, the write initiate sequence must also be followed. See Section 24.0 "Special Features of the CPU" for more detail.

# 5.6 Flash Program Operation During Code Protection

See Section 24.0 "Special Features of the CPU" for details on code protection of Flash program memory.

| Name    | Bit 7                                                | Bit 6                                                 | Bit 5  | Bit 4              | Bit 3 | Bit 2       | Bit 1      | Bit 0  | Value on:<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------------------------------------------------------|-------------------------------------------------------|--------|--------------------|-------|-------------|------------|--------|-----------------------|---------------------------------|

| TBLPTRU | _                                                    |                                                       | bit 21 | Program<br>(TBLPTR |       | ble Pointer | Upper Byte |        | 00 0000               | 00 0000                         |

| TBPLTRH | Program N                                            | Program Memory Table Pointer High Byte (TBLPTR<15:8>) |        |                    |       |             |            |        | 0000 0000             | 0000 0000                       |

| TBLPTRL | Program Memory Table Pointer High Byte (TBLPTR<7:0>) |                                                       |        |                    |       |             |            |        | 0000 0000             | 0000 0000                       |

| TABLAT  | Program Memory Table Latch                           |                                                       |        |                    |       |             |            |        | 0000 0000             | 0000 0000                       |

| INTCON  | GIE/GIEH                                             | PEIE/GIEL                                             | TMR0IE | INTE               | RBIE  | TMR0IF      | INTF       | RBIF   | 0000 0000             | 0000 0000                       |

| EECON2  | EEPROM                                               | EEPROM Control Register 2 (not a physical register)   |        |                    |       |             |            |        | —                     | —                               |

| EECON1  | EEPGD                                                | CFGS                                                  |        | FREE               | WRERR | WREN        | WR         | RD     | xx-0 x000             | uu-0 u000                       |

| IPR2    | —                                                    | CMIP                                                  | —      | EEIP               | BCLIP | LVDIP       | TMR3IP     | CCP2IP | -1-1 1111             | -1-1 1111                       |

| PIR2    | _                                                    | CMIF                                                  |        | EEIF               | BCLIF | LVDIF       | TMR3IF     | CCP2IF | -0-0 0000             | -0-0 0000                       |

| PIE2    | _                                                    | CMIE                                                  | —      | EEIE               | BCLIE | LVDIE       | TMR3IE     | CCP2IE | -0-0 0000             | -0-0 0000                       |

# TABLE 5-2: REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

$\label{eq:Legend: Legend: Legend: Legend: r = normalized are not used during Flash/EEPROM access.}$

# 8.0 8 x 8 HARDWARE MULTIPLIER

## 8.1 Introduction

An 8 x 8 hardware multiplier is included in the ALU of the PIC18F6585/8585/6680/8680 devices. By making the multiply a hardware operation, it completes in a single instruction cycle. This is an unsigned multiply that gives a 16-bit result. The result is stored in the 16-bit product register pair (PRODH:PRODL). The multiplier does not affect any flags in the ALUSTA register.

Making the 8 x 8 multiplier execute in a single cycle gives the following advantages:

- · Higher computational throughput

- Reduces code size requirements for multiply algorithms

The performance increase allows the device to be used in applications previously reserved for Digital Signal Processors.

Table 8-1 shows a performance comparison between enhanced devices using the single-cycle hardware multiply and performing the same function without the hardware multiply.

# 8.2 Operation

Example 8-1 shows the sequence to do an 8 x 8 unsigned multiply. Only one instruction is required when one argument of the multiply is already loaded in the WREG register.

Example 8-2 shows the sequence to do an 8 x 8 signed multiply. To account for the sign bits of the arguments, each argument's Most Significant bit (MSb) is tested and the appropriate subtractions are done.

# EXAMPLE 8-1: 8 x 8 UNSIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, | W | ;                |

|-------|-------|---|------------------|

| MULWF | ARG2  |   | ; ARG1 * ARG2 -> |

|       |       |   | ; PRODH:PRODL    |

|       |       |   |                  |

#### EXAMPLE 8-2: 8 x 8 SIGNED MULTIPLY ROUTINE

| MOVF  | ARG1, | W  | ;                |

|-------|-------|----|------------------|

| MULWF | ARG2  |    | ; ARG1 * ARG2 -> |

|       |       |    | ; PRODH:PRODL    |

| BTFSC | ARG2, | SB | ; Test Sign Bit  |

| SUBWF | PRODH |    | ; PRODH = PRODH  |

|       |       |    | ; - ARG1         |

| MOVF  | ARG2, | W  | ;                |

| BTFSC | ARG1, | SB | ; Test Sign Bit  |

| SUBWF | PRODH |    | ; PRODH = PRODH  |

|       |       |    | ; – ARG2         |

|                  |                           | Program           | Cycles |          | Time     |         |

|------------------|---------------------------|-------------------|--------|----------|----------|---------|

| Routine          | Multiply Method           | Memory<br>(Words) | (Max)  | @ 40 MHz | @ 10 MHz | @ 4 MHz |

| 9 x 9 uppigpod   | Without hardware multiply | 13                | 69     | 6.9 μs   | 27.6 μs  | 69 μs   |

| 8 x 8 unsigned   | Hardware multiply         | 1                 | 1      | 100 ns   | 400 ns   | 1 μs    |

| 8 x 8 signed     | Without hardware multiply | 33                | 91     | 9.1 μs   | 36.4 μs  | 91 μs   |

| o x o signed     | Hardware multiply         | 6                 | 6      | 600 ns   | 2.4 μs   | 6 μs    |

| 16 x 16 unsigned | Without hardware multiply | 21                | 242    | 24.2 μs  | 96.8 μs  | 242 μs  |

| 16 x 16 unsigned | Hardware multiply         | 24                | 24     | 2.4 μs   | 9.6 μs   | 24 μs   |

| 16 x 16 signed   | Without hardware multiply | 52                | 254    | 25.4 μs  | 102.6 μs | 254 μs  |

| TO X TO SIGNED   | Hardware multiply         | 36                | 36     | 3.6 μs   | 14.4 μs  | 36 µs   |

# TABLE 8-1: PERFORMANCE COMPARISON

# 14.0 TIMER3 MODULE

The Timer3 module timer/counter has the following features:

- 16-bit timer/counter (two 8-bit registers; TMR3H and TMR3L)

- Readable and writable (both registers)

- Internal or external clock select

- Interrupt on overflow from FFFFh to 0000h

- Reset from CCP module trigger

Figure 14-1 is a simplified block diagram of the Timer3 module.

Register 14-1 shows the Timer3 Control register. This register controls the operating mode of the Timer3 module and sets the Enhanced CCP1 and CCP2 clock source.

Register 12-1 shows the Timer1 Control register. This register controls the operating mode of the Timer1 module, as well as containing the Timer1 oscillator enable bit (T1OSCEN) which can be a clock source for Timer3.

## REGISTER 14-1: T3CON: TIMER3 CONTROL REGISTER

- n = Value at POR

|          | R/W-0                         | R/W-0                                                                                                                                                                                                                                                                                                                               | R/W-0           | R/W-0                            | R/W-0         | R/W-0      | R/W-0        | R/W-0  |  |  |  |  |

|----------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------------|---------------|------------|--------------|--------|--|--|--|--|

|          | RD16                          | T3CCP2                                                                                                                                                                                                                                                                                                                              | T3CKPS1         | T3CKPS0                          | T3CCP1        | T3SYNC     | TMR3CS       | TMR3ON |  |  |  |  |

|          | bit 7                         |                                                                                                                                                                                                                                                                                                                                     |                 |                                  |               |            |              | bit 0  |  |  |  |  |

| bit 7    |                               |                                                                                                                                                                                                                                                                                                                                     | ite Mode En     | able bit<br>Timer3 in one        | a 16-bit oper | ation      |              |        |  |  |  |  |

|          |                               | 0                                                                                                                                                                                                                                                                                                                                   |                 | Timer3 in two                    |               |            |              |        |  |  |  |  |

| bit 6, 3 | T3CCP2:T                      | 3CCP1: Tir                                                                                                                                                                                                                                                                                                                          | ner3 and Tim    | ner1 to CCP                      | Enable bits   |            |              |        |  |  |  |  |

|          | 01 = Timer<br>Timer           | <ul> <li>1x = Timer3 is the clock source for compare/capture of CCP1 and CCP2 modules</li> <li>1 = Timer3 is the clock source for compare/capture of CCP2 module,<br/>Timer1 is the clock source for compare/capture of CCP1 module</li> <li>0 = Timer1 is the clock source for compare/capture of CCP1 and CCP2 modules</li> </ul> |                 |                                  |               |            |              |        |  |  |  |  |

| bit 5-4  | T3CKPS1:                      | T3CKPS0:                                                                                                                                                                                                                                                                                                                            | Timer3 Inpu     | t Clock Prese                    | cale Select b | oits       |              |        |  |  |  |  |

|          | •                             | rescale valu                                                                                                                                                                                                                                                                                                                        |                 |                                  |               |            |              |        |  |  |  |  |

|          | •                             | rescale valu<br>rescale valu                                                                                                                                                                                                                                                                                                        |                 |                                  |               |            |              |        |  |  |  |  |

|          |                               | rescale valu                                                                                                                                                                                                                                                                                                                        |                 |                                  |               |            |              |        |  |  |  |  |

| bit 2    | T3SYNC:                       | Timer3 Exte                                                                                                                                                                                                                                                                                                                         | rnal Clock Ir   | nput Synchro                     | nization Cor  | ntrol bit  |              |        |  |  |  |  |

|          |                               |                                                                                                                                                                                                                                                                                                                                     | em clock cor    | nes from Tim                     | er1/Timer3.   | )          |              |        |  |  |  |  |

|          | <u>When TMF</u><br>1 = Do not |                                                                                                                                                                                                                                                                                                                                     | e external cl   | ock input                        |               |            |              |        |  |  |  |  |

|          |                               |                                                                                                                                                                                                                                                                                                                                     | nal clock inp   | •                                |               |            |              |        |  |  |  |  |

|          | When TMF                      |                                                                                                                                                                                                                                                                                                                                     |                 |                                  |               |            |              |        |  |  |  |  |

|          |                               | 0                                                                                                                                                                                                                                                                                                                                   |                 | e internal clo                   | ck when TM    | R3CS = 0.  |              |        |  |  |  |  |

| bit 1    |                               |                                                                                                                                                                                                                                                                                                                                     | ck Source Se    |                                  |               |            |              |        |  |  |  |  |

|          | (on the                       |                                                                                                                                                                                                                                                                                                                                     | e after the fir | er1 oscillator<br>st falling edg |               |            |              |        |  |  |  |  |

| bit 0    | TMR3ON:                       | Timer3 On                                                                                                                                                                                                                                                                                                                           | bit             |                                  |               |            |              |        |  |  |  |  |

|          | 1 = Enable<br>0 = Stops       |                                                                                                                                                                                                                                                                                                                                     |                 |                                  |               |            |              |        |  |  |  |  |

|          | Legend:                       |                                                                                                                                                                                                                                                                                                                                     |                 |                                  |               |            |              |        |  |  |  |  |

|          | R = Reada                     | able bit                                                                                                                                                                                                                                                                                                                            | W = W           | /ritable bit                     | U = Unin      | nplemented | bit, read as | '0'    |  |  |  |  |

'1' = Bit is set

x = Bit is unknown

'0' = Bit is cleared

|         |                  |                                                                          |                              |                 |                | /             |               |              |

|---------|------------------|--------------------------------------------------------------------------|------------------------------|-----------------|----------------|---------------|---------------|--------------|

|         | R/W-0            | R/W-0                                                                    | R/W-0                        | R/W-0           | R/W-0          | R/W-0         | R/W-0         | R/W-0        |

|         | WCOL             | SSPOV                                                                    | SSPEN                        | СКР             | SSPM3          | SSPM2         | SSPM1         | SSPM0        |

|         | bit 7            |                                                                          |                              |                 |                |               |               | bit 0        |

| bit 7   | WCOL: Wr         | ite Collision                                                            | Detect bit (T                | ransmit mo      | de only)       |               |               |              |

|         | cleare           | SPBUF regi<br>d in software                                              |                              | en while it is  | s still transm | nitting the p | revious wor   | d (must be   |

|         | 0 = No col       |                                                                          |                              |                 |                |               |               |              |

| bit 6   |                  | eceive Overf                                                             | low Indicato                 | r bit           |                |               |               |              |

|         | SPI Slave        |                                                                          |                              |                 |                |               |               |              |

|         | of ove<br>must r | byte is recei<br>rflow, the da<br>ead the SSF<br>d in software<br>erflow | ta in SSPSF<br>PBUF, even i  | R is lost. Ov   | erflow can o   | only occur in | Slave mod     | le.The user  |

|         | Note:            |                                                                          | mode, the<br>n) is initiated |                 |                |               |               | eption (and  |

| bit 5   | SSPEN: S         | ynchronous                                                               | Serial Port E                | nable bit       |                |               |               |              |

|         |                  | s serial port<br>es serial port                                          | 0                            | ,               | , ,            |               | ial port pins |              |

|         | Note:            | When enab                                                                | led, these p                 | ins must be     | properly cor   | nfigured as i | nput or outp  | out.         |

| bit 4   | CKP: Cloc        | k Polarity Se                                                            | lect bit                     |                 |                |               |               |              |

|         | 1 = Idle sta     | te for clock i                                                           | s a high leve                | el              |                |               |               |              |

|         | 0 = Idle sta     | te for clock i                                                           | s a low leve                 | l               |                |               |               |              |

| bit 3-0 | SSPM3:SS         | SPM0: Synch                                                              | nronous Seri                 | al Port Mod     | e Select bits  |               |               |              |

|         | 0100 = SP        | I Slave mod<br>I Slave mod<br>I Master mod                               | e, clock = S                 | CK pin, SS p    | oin control e  |               | can be used   | d as I/O pin |

|         |                  | I Master mo                                                              | ,                            |                 |                |               |               |              |

|         |                  | I Master mo                                                              |                              |                 |                |               |               |              |

|         |                  | I Master mo                                                              |                              |                 |                |               |               |              |

|         | Note:            | Bit combina<br>I <sup>2</sup> C mode o                                   | ations not sp<br>nly.        | ecifically list | ed here are    | either rese   | rved or impl  | emented in   |

|         |                  |                                                                          |                              |                 |                |               |               |              |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# REGISTER 17-2: SSPCON1: MSSP CONTROL REGISTER 1 (SPI MODE)

# 22.1 Control Register

bit 5

The Low-Voltage Detect Control register controls the operation of the Low-Voltage Detect circuitry.

## REGISTER 22-1: LVDCON REGISTER

| U-0   | U-0 | R-0   | R/W-0 | R/W-0 | R/W-1 | R/W-0 | R/W-1 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | IRVST | LVDEN | LVDL3 | LVDL2 | LVDL1 | LVDL0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

bit 7-6 Unimplemented: Read as '0'

IRVST: Internal Reference Voltage Stable Flag bit

- 1 = Indicates that the Low-Voltage Detect logic will generate the interrupt flag at the specified voltage range

- 0 = Indicates that the Low-Voltage Detect logic will not generate the interrupt flag at the specified voltage range and the LVD interrupt should not be enabled

- bit 4 LVDEN: Low-Voltage Detect Power Enable bit

1 = Enables LVD, powers up LVD circuit

0 = Disables LVD, powers down LVD circuit

#### bit 3-0 LVDL3:LVDL0: Low-Voltage Detection Limit bits

1111 = External analog input is used (input comes from the LVDIN pin)

| 1110 = 4.5V-4.77V     |

|-----------------------|

| 1101 = 4.2V-4.45V     |

| 1100 = 4.0V-4.24V     |

| 1011 = 3.8V-4.03V     |

| 1010 = 3.6V-3.82V     |

| 1001 = 3.5V-3.71V     |

| 1000 = 3.3 V - 3.50 V |

| 0111 = 3.0V-3.18V     |

| 0110 = 2.8V-2.97V     |

| 0101 = 2.7V-2.86V     |

| 0100 = 2.5V-2.65V     |

| 0011 = 2.4 V - 2.54 V |

| 0010 = 2.2V-2.33V     |

| 0001 = 2.0V-2.12V     |

| 0000 = Reserved       |

|                       |

**Note:** LVDL3:LVDL0 modes which result in a trip point below the valid operating voltage of the device are not tested.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

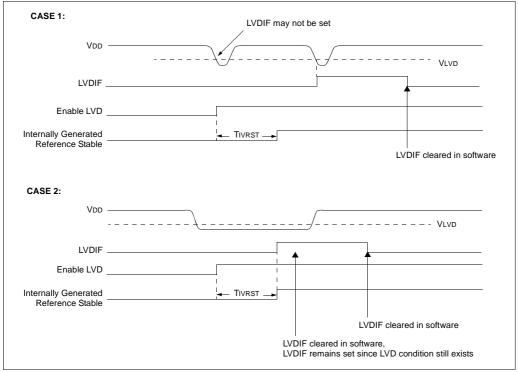

# 22.2 Operation

Depending on the power source for the device voltage, the voltage normally decreases relatively slowly. This means that the LVD module does not need to be constantly operating. To decrease the current requirements, the LVD circuitry only needs to be enabled for short periods where the voltage is checked. After doing the check, the LVD module may be disabled.

Each time that the LVD module is enabled, the circuitry requires some time to stabilize. After the circuitry has stabilized, all status flags may be cleared. The module will then indicate the proper state of the system.

The following steps are needed to set up the LVD module:

- Write the value to the LVDL3:LVDL0 bits (LVDCON register) which selects the desired LVD trip point.

- 2. Ensure that LVD interrupts are disabled (the LVDIE bit is cleared or the GIE bit is cleared).

- 3. Enable the LVD module (set the LVDEN bit in the LVDCON register).

- 4. Wait for the LVD module to stabilize (the IRVST bit to become set).

- Clear the LVD interrupt flag which may have falsely become set until the LVD module has stabilized (clear the LVDIF bit).

- 6. Enable the LVD interrupt (set the LVDIE and the GIE bits).

Figure 22-4 shows typical waveforms that the LVD module may be used to detect.

# FIGURE 22-4: LOW-VOLTAGE DETECT WAVEFORMS

| FER 23-49: | MSEL1: M                                                   | ASK SELE | CT REGIS     | TER 1''' |            |        |        |        |

|------------|------------------------------------------------------------|----------|--------------|----------|------------|--------|--------|--------|

|            | R/W-0                                                      | R/W-0    | R/W-0        | R/W-0    | R/W-0      | R/W-1  | R/W-0  | R/W-1  |

|            | FIL7_1                                                     | FIL7_0   | FIL6_1       | FIL6_0   | FIL5_1     | FIL5_0 | FIL4_1 | FIL4_0 |

|            | bit 7                                                      |          |              |          |            |        |        | bit 0  |

| bit 7-6    | 11 = No mas<br>10 = Filter 1<br>01 = Accept                |          | elect bits 1 | and 0    |            |        |        |        |

| bit 5-4    | •                                                          |          |              |          |            |        |        |        |

| bit 3-2    | 11 = No mas<br>10 = Filter 1<br>01 = Accept                |          | elect bits 1 | and 0    |            |        |        |        |

| bit 1-0    | 11 = No mas<br>10 = Filter 1<br>01 = Accept<br>00 = Accept |          |              |          | nd 2 only. |        |        |        |

|            |                                                            |          |              |          |            |        |        |        |

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# REGISTER 23-49: MSEL1: MASK SELECT REGISTER 1<sup>(1)</sup>

- n = Value at POR

| LIX 20 00. | BROOONL                                                                    | DAOD IN                                                                    |              |              |               |              |                |            |  |  |  |

|------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------|--------------|---------------|--------------|----------------|------------|--|--|--|

|            | R/W-0                                                                      | R/W-0                                                                      | R/W-0        | R/W-0        | R/W-0         | R/W-0        | R/W-0          | R/W-0      |  |  |  |

|            | SEG2PHTS                                                                   | SAM                                                                        | SEG1PH2      | SEG1PH1      | SEG1PH0       | PRSEG2       | PRSEG1         | PRSEG0     |  |  |  |

|            | bit 7                                                                      |                                                                            |              |              |               |              |                | bit 0      |  |  |  |

|            |                                                                            |                                                                            |              |              |               |              |                |            |  |  |  |

| bit 7      | SEG2PHTS:                                                                  | Phase Se                                                                   | gment 2 Tim  | e Select bit |               |              |                |            |  |  |  |

|            | 1 = Freely pr                                                              | 0                                                                          |              |              |               |              |                |            |  |  |  |

|            | 0 = Maximur                                                                | n of PHEG                                                                  | 1 or Informa | tion Process | sing Time (IF | PT), whichev | er is greate   | r          |  |  |  |

| bit 6      | SAM: Sampl                                                                 | e of the CA                                                                | N bus Line   | bit          |               |              |                |            |  |  |  |

|            | 1 = Bus line is sampled three times prior to the sample point              |                                                                            |              |              |               |              |                |            |  |  |  |

|            | 0 = Bus line                                                               | is sampled                                                                 | once at the  | sample poir  | nt            |              |                |            |  |  |  |

| bit 5-3    | SEG1PH2:S                                                                  | EG1PH0:                                                                    | Phase Segm   | ent 1 bits   |               |              |                |            |  |  |  |

|            | 111 = Phase                                                                | •                                                                          |              |              |               |              |                |            |  |  |  |

|            |                                                                            | 110 = Phase Segment 1 time = $7 \times TQ$                                 |              |              |               |              |                |            |  |  |  |

|            | 101 = Phase Segment 1 time = 6 x TQ                                        |                                                                            |              |              |               |              |                |            |  |  |  |

|            |                                                                            | 100 = Phase Segment 1 time = 5 x TQ<br>011 = Phase Segment 1 time = 4 x TQ |              |              |               |              |                |            |  |  |  |

|            | 011 = Phase Segment 1 time = 4 x TQ<br>010 = Phase Segment 1 time = 3 x TQ |                                                                            |              |              |               |              |                |            |  |  |  |

|            | 001 = Phase Segment 1 time = 2 x TQ                                        |                                                                            |              |              |               |              |                |            |  |  |  |

|            | 000 = Phase                                                                | e Segment                                                                  | 1 time = 1 x | ΤQ           |               |              |                |            |  |  |  |

| bit 2-0    | PRSEG2:PRSEG0: Propagation Time Select bits                                |                                                                            |              |              |               |              |                |            |  |  |  |

|            | 111 = Propa                                                                | gation time                                                                | = 8 x TQ     |              |               |              |                |            |  |  |  |

|            | 110 = Propagation time = $7 \times TQ$                                     |                                                                            |              |              |               |              |                |            |  |  |  |

|            | $101 = Propagation time = 6 \times TQ$                                     |                                                                            |              |              |               |              |                |            |  |  |  |

|            | $100 = Propagation time = 5 \times TQ$                                     |                                                                            |              |              |               |              |                |            |  |  |  |

|            | 011 = Propagation time = 4 x TQ<br>010 = Propagation time = 3 x TQ         |                                                                            |              |              |               |              |                |            |  |  |  |

|            | $0.01 = \text{Propagation time} = 2 \times \text{TQ}$                      |                                                                            |              |              |               |              |                |            |  |  |  |

|            | 000 = Propa                                                                | gation time                                                                | = 1 x TQ     |              |               |              |                |            |  |  |  |

|            | Legend:                                                                    |                                                                            |              |              |               |              |                | ,          |  |  |  |

|            | R = Readabl                                                                | o hit                                                                      | W = Writab   | la hit       | II – I Inim   | nlamanted    | oit, read as ' | <u></u> 0' |  |  |  |

|            | IX - IXeauabl                                                              | e Dir                                                                      |              |              | 0 = 01111     | piementeur   | n, ieau as     | 0          |  |  |  |

'0' = Bit is cleared

'1' = Bit is set

# REGISTER 23-53: BRGCON2: BAUD RATE CONTROL REGISTER 2

x = Bit is unknown

## TABLE 23-1: CAN CONTROLLER REGISTER MAP

| Address <sup>(1)</sup> | Name                    | Address | Name                       | Address | Name                       | Address | Name     |

|------------------------|-------------------------|---------|----------------------------|---------|----------------------------|---------|----------|

| F7Fh                   | SPBRGH <sup>(3)</sup>   | F5Fh    | CANCON_RO0                 | F3Fh    | CANCON_RO2                 | F1Fh    | RXM1EIDL |

| F7Eh                   | BAUDCON <sup>(3)</sup>  | F5Eh    | CANSTAT_RO0                | F3Eh    | CANSTAT_RO2                | F1Eh    | RXM1EIDH |

| F7Dh                   | (4)                     | F5Dh    | RXB1D7                     | F3Dh    | TXB1D7                     | F1Dh    | RXM1SIDL |

| F7Ch                   | (4)                     | F5Ch    | RXB1D6                     | F3Ch    | TXB1D6                     | F1Ch    | RXM1SIDH |

| F7Bh                   | (4)                     | F5Bh    | RXB1D5                     | F3Bh    | TXB1D5                     | F1Bh    | RXM0EIDL |

| F7Ah                   | (4)                     | F5Ah    | RXB1D4                     | F3Ah    | TXB1D4                     | F1Ah    | RXM0EIDH |

| F79h                   | ECCP1DEL <sup>(3)</sup> | F59h    | RXB1D3                     | F39h    | TXB1D3                     | F19h    | RXM0SIDL |

| F78h                   | (4)                     | F58h    | RXB1D2                     | F38h    | TXB1D2                     | F18h    | RXM0SIDH |

| F77h                   | ECANCON                 | F57h    | RXB1D1                     | F37h    | TXB1D1                     | F17h    | RXF5EIDL |

| F76h                   | TXERRCNT                | F56h    | RXB1D0                     | F36h    | TXB1D0                     | F16h    | RXF5EIDH |

| F75h                   | RXERRCNT                | F55h    | RXB1DLC                    | F35h    | TXB1DLC                    | F15h    | RXF5SIDL |

| F74h                   | COMSTAT                 | F54h    | RXB1EIDL                   | F34h    | TXB1EIDL                   | F14h    | RXF5SIDH |

| F73h                   | CIOCON                  | F53h    | RXB1EIDH                   | F33h    | TXB1EIDH                   | F13h    | RXF4EIDL |

| F72h                   | BRGCON3                 | F52h    | RXB1SIDL                   | F32h    | TXB1SIDL                   | F12h    | RXF4EIDH |

| F71h                   | BRGCON2                 | F51h    | RXB1SIDH                   | F31h    | TXB1SIDH                   | F11h    | RXF4SIDL |

| F70h                   | BRGCON1                 | F50h    | RXB1CON                    | F30h    | TXB1CON                    | F10h    | RXF4SIDH |

| F6Fh                   | CANCON                  | F4Fh    | CANCON_RO1 <sup>(2)</sup>  | F2Fh    | CANCON_RO3(2)              | F0Fh    | RXF3EIDL |

| F6Eh                   | CANSTAT                 | F4Eh    | CANSTAT_RO1 <sup>(2)</sup> | F2Eh    | CANSTAT_RO3 <sup>(2)</sup> | F0Eh    | RXF3EIDH |

| F6Dh                   | RXB0D7                  | F4Dh    | TXB0D7                     | F2Dh    | TXB2D7                     | F0Dh    | RXF3SIDL |

| F6Ch                   | RXB0D6                  | F4Ch    | TXB0D6                     | F2Ch    | TXB2D6                     | F0Ch    | RXF3SIDH |

| F6Bh                   | RXB0D5                  | F4Bh    | TXB0D5                     | F2Bh    | TXB2D5                     | F0Bh    | RXF2EIDL |

| F6Ah                   | RXB0D4                  | F4Ah    | TXB0D4                     | F2Ah    | TXB2D4                     | F0Ah    | RXF2EIDH |

| F69h                   | RXB0D3                  | F49h    | TXB0D3                     | F29h    | TXB2D3                     | F09h    | RXF2SIDL |

| F68h                   | RXB0D2                  | F48h    | TXB0D2                     | F28h    | TXB2D2                     | F08h    | RXF2SIDH |

| F67h                   | RXB0D1                  | F47h    | TXB0D1                     | F27h    | TXB2D1                     | F07h    | RXF1EIDL |

| F66h                   | RXB0D0                  | F46h    | TXB0D0                     | F26h    | TXB2D0                     | F06h    | RXF1EIDH |

| F65h                   | RXB0DLC                 | F45h    | TXB0DLC                    | F25h    | TXB2DLC                    | F05h    | RXF1SIDL |

| F64h                   | RXB0EIDL                | F44h    | TXB0EIDL                   | F24h    | TXB2EIDL                   | F04h    | RXF1SIDH |

| F63h                   | RXB0EIDH                | F43h    | TXB0EIDH                   | F23h    | TXB2EIDH                   | F03h    | RXF0EIDL |

| F62h                   | RXB0SIDL                | F42h    | TXB0SIDL                   | F22h    | TXB2SIDL                   | F02h    | RXF0EIDH |

| F61h                   | RXB0SIDH                | F41h    | TXB0SIDH                   | F21h    | TXB2SIDH                   | F01h    | RXF0SIDL |

| F60h                   | RXB0CON                 | F40h    | TXB0CON                    | F20h    | TXB2CON                    | F00h    | RXF0SIDH |

Note 1: Shaded registers are available in Access Bank low area while the rest are available in Bank 15.

2: CANSTAT register is repeated in these locations to simplify application firmware. Unique names are given for each instance of the controller register due to the Microchip header file requirement.

3: These registers are not CAN registers.

4: Unimplemented registers are read as '0'.

### 23.5.3 PROGRAMMABLE TRANSMIT/ RECEIVE BUFFERS

The ECAN module implements six new buffers: B0-B5. These buffers are individually programmable as either transmit or receive buffers. These buffers are available only in Mode 1 and 2. As with dedicated transmit and receive buffers, each of these programmable buffers occupies 14 bytes of SRAM and are mapped into SFR memory map.

Each buffer contains one Control register (BnCON), four Identifier registers (BnSIDL, BnSIDH, BnEIDL, BnEIDH), one Data Length Count register (BnDLC) and eight Data Byte registers (BnDm). Each of these registers contains two sets of control bits. Depending on whether the buffer is configured as transmit or receive, one would use the corresponding control bit set. By default, all buffers are configured as receive buffers. Each buffer can be individually configured as transmit or receive buffers by setting the corresponding TXENn bit in the BSEL0 register.

When configured as transmit buffers, user firmware may access transmit buffers in any order similar to accessing dedicated transmit buffers. In receive configuration, with Mode 1 enabled, user firmware may also access receive buffers in any order required. But in Mode 2, all receive buffers are combined to form a single FIFO. Actual FIFO length is programmable by user firmware. Access to FIFO must be done through the FIFO pointer bits (FP<4:0>) in the CANCON register. It must be noted that there is no hardware protection against out of order FIFO reads.

## 23.5.4 PROGRAMMABLE AUTO-RTR BUFFERS

In Mode 1 and 2, any of six programmable transmit/ receive buffers may be programmed to automatically respond to predefined RTR messages without user firmware intervention. Automatic RTR handling is enabled by setting the TXnEN bit in the BSEL0 register and the RTREN bit in the BnCON register. After this setup, when an RTR request is received, the TXREQ bit is automatically set and current buffer content is automatically queued for transmission as a RTR response. As with all transmit buffers, once the TXREQ bit is set, buffer registers become read-only and any writes to them will be ignored. The following outlines the steps required to automatically handle RTR messages:

- 1. Set buffer to Transmit mode by setting TXnEN bit to '1' in BSEL0 register.

- At least one acceptance filter must be associated with this buffer and preloaded with expected RTR identifier.

- 3. Bit RTREN in BnCON register must be set to '1'.

- 4. Buffer must be preloaded with the data to be sent as a RTR response.

Normally, user firmware will keep Buffer Data registers up to date. If firmware attempts to update buffer while an automatic RTR response is in process of transmission, all writes to buffers are ignored.

# 23.6 CAN Message Transmission

## 23.6.1 INITIATING TRANSMISSION

For the MCU to have write access to the message buffer, the TXREQ bit must be clear, indicating that the message buffer is clear of any pending message to be transmitted. At a minimum, the SIDH, SIDL, and DLC registers must be loaded. If data bytes are present in the message, the data registers must also be loaded. If the message is to use extended identifiers, the EIDH:EIDL registers must also be loaded and the EXIDE bit set.

To initiate message transmission, the TXREQ bit must be set for each buffer to be transmitted. When TXREQ is set, the TXABT, TXLARB and TXERR bits will be cleared. To successfully complete the transmission, there must be at least one node with matching baud rate on the network.

Setting the TXREQ bit does not initiate a message transmission, it merely flags a message buffer as ready for transmission. Transmission will start when the device detects that the bus is available. The device will then begin transmission of the highest priority message that is ready.

When the transmission has completed successfully, the TXREQ bit will be cleared, the TXBnIF bit will be set, and an interrupt will be generated if the TXBnIE bit is set.

If the message transmission fails, the TXREQ will remain set, indicating that the message is still pending for transmission and one of the following condition flags will be set. If the message started to transmit but encountered an error condition, the TXERR and the IRXIF bits will be set and an interrupt will be generated. If the message lost arbitration, the TXLARB bit will be set.

## REGISTER 24-2: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

|   | U-0   | U-0 | U-0 | U-0 | R/P-1 | R/P-1 | R/P-1 | R/P-1  |

|---|-------|-----|-----|-----|-------|-------|-------|--------|

|   | _     | —   | —   | —   | BORV1 | BORV0 | BOREN | PWRTEN |

| k | oit 7 |     |     |     |       |       |       | bit 0  |

#### bit 7-4 Unimplemented: Read as '0'

- bit 3-2 BORV1:BORV0: Brown-out Reset Voltage bits

- 11 = VBOR set to 2.0V

- 10 = VBOR set to 2.7V

- 01 = VBOR set to 4.2V

- 00 = VBOR set to 4.5V

#### bit 1 BOREN: Brown-out Reset Enable bit

- 1 = Brown-out Reset enabled

- 0 = Brown-out Reset disabled

#### bit 0 **PWRTEN:** Power-up Timer Enable bit

- 1 = PWRT disabled

- 0 = PWRT enabled

### Legend:

| R = Readable bit                                          | P = Programmable bit | U = Unimplemented bit, read as '0'  |

|-----------------------------------------------------------|----------------------|-------------------------------------|

| <ul> <li>n = Value when device is unprogrammed</li> </ul> |                      | u = Unchanged from programmed state |

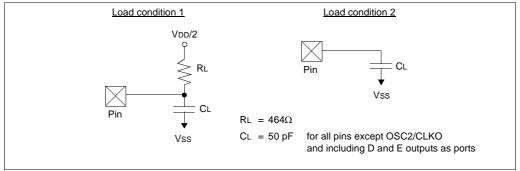

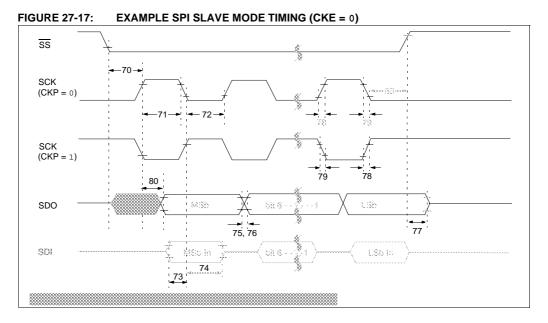

## 27.4.2 TIMING CONDITIONS

The temperature and voltages specified in Table 27-5 apply to all timing specifications unless otherwise noted. Figure 27-5 specifies the load conditions for the timing specifications.

# TABLE 27-5: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions (unless otherwise stated)                                                                                  |  |  |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                    | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for extended      |  |  |  |  |

| AC CHARACTERISTICS | Operating voltage VDD range as described in DC spec Section 27.1 and Section 27.3.<br>LC parts operate for industrial temperatures only. |  |  |  |  |

## FIGURE 27-5: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

| Param.<br>No.               | Symbol                            | Characteristic                                                               | Min              | Max           | Units | Conditions |          |

|-----------------------------|-----------------------------------|------------------------------------------------------------------------------|------------------|---------------|-------|------------|----------|

| 70                          | TssL2scH,<br>TssL2scL             | $\overline{\text{SS}}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ Input | Тсү              |               | ns    |            |          |

| 71                          | TscH                              | SCK Input High Time (Slave mode)                                             | Continuous       | 1.25 TCY + 30 |       | ns         |          |

| 71A                         |                                   |                                                                              | Single Byte      | 40            |       | ns         | (Note 1) |

| 72                          | TscL                              | SCK Input Low Time (Slave mode)                                              | Continuous       | 1.25 TCY + 30 | -     | ns         |          |

| 72A                         |                                   |                                                                              | Single Byte      | 40            |       | ns         | (Note 1) |

| 73                          | TDIV2SCH,<br>TDIV2SCL             | Setup Time of SDI Data Input to SCK E                                        | 100              |               | ns    |            |          |

| 73A                         | Тв2в                              | Last Clock Edge of Byte 1 to the First Cloc                                  | k Edge of Byte 2 | 1.5 TCY + 40  |       | ns         | (Note 2) |

| 74                          | TscH2diL,<br>TscL2diL             | Hold Time of SDI Data Input to SCK Edg                                       | 100              |               | ns    |            |          |

| 75                          | 75 TDOR SDO Data Output Rise Time |                                                                              | PIC18FXX8X       | _             | 25    | ns         |          |

|                             |                                   |                                                                              | PIC18LFXX8X      |               | 45    | ns         |          |

| 76                          | TDOF                              | SDO Data Output Fall Time                                                    |                  | —             | 25    | ns         |          |

| 77                          | TssH2doZ                          | SS ↑ to SDO Output High-Impedance                                            |                  | 10            | 50    | ns         |          |

| 78 TSCR SCK oUtput Rise Tim |                                   | SCK oUtput Rise Time (Master mode)                                           | PIC18FXX8X       | _             | 25    | ns         |          |

|                             |                                   |                                                                              | PIC18LFXX8X      |               | 45    | ns         |          |

| 79                          | TSCF                              | SCK Output Fall Time (Master mode)                                           |                  | —             | 25    | ns         |          |

| 80                          | TSCH2DOV,                         | SDO Data Output Valid after SCK Edge                                         | PIC18FXX8X       | —             | 50    | ns         |          |

|                             | TSCL2DOV                          |                                                                              | PIC18LFXX8X      |               | 100   | ns         | 1        |

| 83                          | TSCH2SSH,<br>TSCL2SSH             | SS ↑ after SCK Edge                                                          |                  | 1.5 TCY + 40  |       | ns         |          |

Note 1: Requires the use of Parameter #73A.

2: Only if Parameter #71A and #72A are used.

## TABLE 27-25: A/D CONVERTER CHARACTERISTICS: PIC18F6585/8585/6680/8680 (INDUSTRIAL, EXTENDED) PIC18LF6585/8585/6680/8680 (INDUSTRIAL)

| Param<br>No. | Symbol                           | Charact                                           | eristic                   | Min       | Тур        | Max         | Units                                                                                    | Conditions                                    |

|--------------|----------------------------------|---------------------------------------------------|---------------------------|-----------|------------|-------------|------------------------------------------------------------------------------------------|-----------------------------------------------|

| A01          | NR                               | Resolution                                        |                           |           | 10<br>TBD  | bit<br>bit  | $\label{eq:VREF} \begin{array}{l} VREF = VDD \geq 3.0V \\ VREF = VDD < 3.0V \end{array}$ |                                               |

| A03          | EIL                              | Integral Linearity                                | _                         |           | <±1<br>TBD | LSb<br>LSb  | $\begin{array}{l} VREF = VDD \geq 3.0V \\ VREF = VDD < 3.0V \end{array}$                 |                                               |

| A04          | EDL                              | Differential Linea                                | _                         |           | <±1<br>TBD | LSb<br>LSb  | $\label{eq:VREF} \begin{array}{l} VREF = VDD \geq 3.0V \\ VREF = VDD < 3.0V \end{array}$ |                                               |

| A05          | Efs                              | Full-Scale Error                                  | _                         |           | <±1<br>TBD | LSb<br>LSb  | $\label{eq:VREF} \begin{array}{l} VREF = VDD \geq 3.0V \\ VREF = VDD < 3.0V \end{array}$ |                                               |

| A06          | EOFF                             | Offset Error                                      | _                         |           | <±1<br>TBD | LSb<br>LSb  | $\label{eq:VREF} \begin{array}{l} VREF = VDD \geq 3.0V \\ VREF = VDD < 3.0V \end{array}$ |                                               |

| A10          | —                                | Monotonicity                                      | guaranteed <sup>(3)</sup> |           |            | —           | $VSS \leq VAIN \leq VREF$                                                                |                                               |

| A20<br>A20A  | VREF                             | Reference Voltage<br>(VREFH – VREFL)              |                           | 0V<br>3V  |            | _           | V<br>V                                                                                   | For 10-bit resolution                         |