Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 52                                                                        |

| Program Memory Size        | 48KB (24K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 68-LCC (J-Lead)                                                           |

| Supplier Device Package    | 68-PLCC (24.23x24.23)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf6585-i-l |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

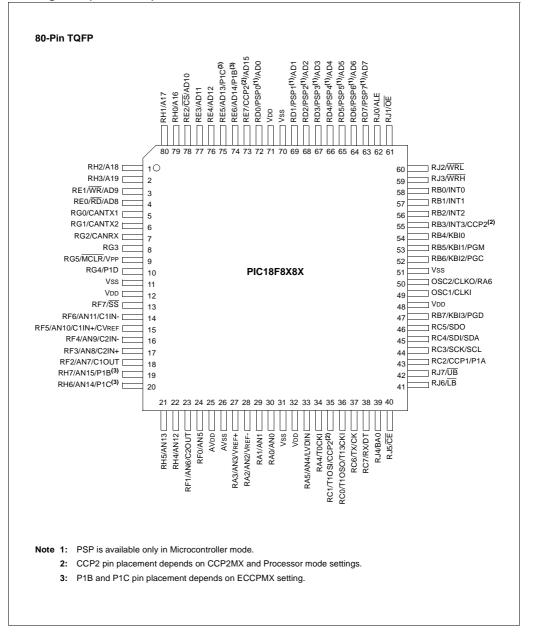

## **Pin Diagrams (Continued)**

## **Table of Contents**

| 1.0   | Device Overview                                                          | 9     |

|-------|--------------------------------------------------------------------------|-------|

| 2.0   | Oscillator Configurations                                                | 23    |

| 3.0   | Reset                                                                    | 33    |

| 4.0   | Memory Organization                                                      | 51    |

| 5.0   | Flash Program Memory                                                     | 83    |

| 6.0   | External Memory Interface                                                | 93    |

| 7.0   | Data EEPROM Memory                                                       | 101   |

| 8.0   | 8 x 8 Hardware Multiplier                                                | . 107 |

| 9.0   | Interrupts                                                               | . 109 |

| 10.0  | I/O Ports                                                                | . 125 |

| 11.0  | Timer0 Module                                                            | . 155 |

| 12.0  | Timer1 Module                                                            | . 159 |

| 13.0  | Timer2 Module                                                            | . 162 |

|       | Timer3 Module                                                            |       |

| 15.0  | Capture/Compare/PWM (CCP) Modules                                        | . 167 |

| 16.0  | Enhanced Capture/Compare/PWM (ECCP) Module                               |       |

| 17.0  | Master Synchronous Serial Port (MSSP) Module                             |       |

| 18.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (USART) | . 229 |

| 19.0  | 10-bit Analog-to-Digital Converter (A/D) Module                          | . 249 |

|       | Comparator Module                                                        |       |

|       | Comparator Voltage Reference Module                                      |       |

| 22.0  | Low-Voltage Detect                                                       | . 269 |

| 23.0  | ECAN Module                                                              | . 275 |

| 24.0  | Special Features of the CPU                                              | . 345 |

| 25.0  | Instruction Set Summary                                                  | . 365 |

| 26.0  | Development Support                                                      | . 407 |

| 27.0  | Electrical Characteristics                                               | . 413 |

|       | DC and AC Characteristics Graphs and Tables                              |       |

|       | Packaging Information                                                    |       |

| Appe  | ndix A: Revision History                                                 | 469   |

|       | ndix B: Device Differences                                               |       |

| Appe  | ndix C: Conversion Considerations                                        | . 470 |

| Appe  | ndix D: Migration from Mid-Range to Enhanced Devices                     | . 470 |

| Appe  | ndix E: Migration from High-End to Enhanced Devices                      | . 471 |

| Index | ۲                                                                        | . 473 |

| On-L  | ine Support                                                              | . 487 |

| Syste | ems Information and Upgrade Hot Line                                     | . 487 |

| Read  | er Response                                                              | . 488 |

| PIC1  | 8F6585/8585/6680/8680 Product Identification System                      | . 489 |

# 5.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation cannot be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

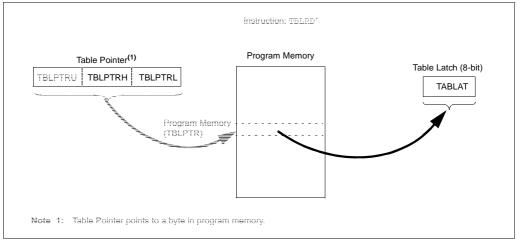

### 5.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8-bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and places it into the data RAM space. Figure 5-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 5.5 "Writing to Flash Program Memory"**. Figure 5-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

FIGURE 5-1: TABLE READ OPERATION

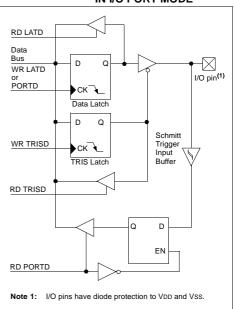

## 10.4 PORTD, TRISD and LATD Registers

PORTD is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISD. Setting a TRISD bit (= 1) will make the corresponding PORTD pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISD bit (= 0) will make the corresponding PORTD pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATD) is also memory mapped. Read-modify-write operations on the LATD register read and write the latched output value for PORTD.

PORTD is an 8-bit port with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

| Note: | On a Power-on Reset, these pins a | re |  |  |  |  |

|-------|-----------------------------------|----|--|--|--|--|

|       | configured as digital inputs.     |    |  |  |  |  |

On PIC18F8X8X devices, PORTD is multiplexed with the system bus as the external memory interface; I/O port functions are only available when the system bus is disabled by setting the EBDIS bit in the MEMCOM register (MEMCON<7>). When operating as the external memory interface, PORTD is the low-order byte of the multiplexed address/data bus (AD7:AD0).

PORTD can also be configured as an 8-bit wide microprocessor port (Parallel Slave Port) by setting control bit, PSPMODE (TRISE<4>). In this mode, the input buffers are TTL. See Section 10.10 "Parallel Slave Port (PSP)" for additional information.

#### EXAMPLE 10-4: INITIALIZING PORTD

| CLRF  | PORTD | ; Initialize PORTD by ; clearing output |

|-------|-------|-----------------------------------------|

|       |       | ; data latches                          |

| CLRF  | LATD  | ; Alternate method                      |

|       |       | ; to clear output                       |

|       |       | ; data latches                          |

| MOVLW | 0CFh  | ; Value used to                         |

|       |       | ; initialize data                       |

|       |       | ; direction                             |

| MOVWF | TRISD | ; Set RD<3:0> as inputs                 |

|       |       | ; RD<5:4> as outputs                    |

|       |       | ; RD<7:6> as inputs                     |

|       |       |                                         |

#### FIGURE 10-9: PORTD BLOCK DIAGRAM IN I/O PORT MODE

#### REGISTER 15-2: CCP2CON REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

|       | —   | DC2B1 | DC2B0 | CCP2M3 | CCP2M2 | CCP2M1 | CCP2M0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-4 DC2B1:DC2B0: PWM Duty Cycle bit 1 and bit 0

Capture mode: Unused. Compare mode:

Unused. PWM mode:

These bits are the two LSbs of the 10-bit PWM duty cycle. The eight MSbs of the duty cycle are found in CCPR2L.

#### bit 3-0 CCP2M3:CCP2M0: CCP2 Mode Select bits

- 0000 = Capture/Compare/PWM off (resets CCP2 module)

- 0001 = Reserved

- 0010 = Compare mode, toggle output on match

- 0011 = Reserved

- 0100 = Capture mode, every falling edge

- 0101 = Capture mode, every rising edge

- 0110 = Capture mode, every 4th rising edge

- 0111 = Capture mode, every 16th rising edge

- 1000 = Compare mode, initialize CCP pin low, on compare match force CCP pin high

- ${\tt 1001}$  = Compare mode, initialize CCP pin high, on compare match force CCP pin low

- ${\tt 1010}$  = Compare mode, generate software interrupt only, CCP pin is unaffected

- 1011 = Compare mode, trigger special event, resets TMR1 or TMR3 and starts A/D conversion if A/D module is enabled

- 11xx = PWM mode

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

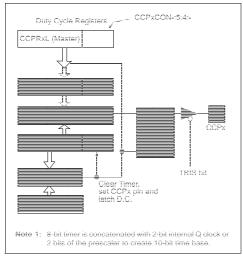

## 15.4 PWM Mode

In Pulse Width Modulation (PWM) mode, the CCPx pin produces up to a 10-bit resolution PWM output. For PWM mode to function properly, the TRIS bit for the CCPx pin must be cleared to make it an output.

| Note: | Clearing the CCPxCON register will force    |

|-------|---------------------------------------------|

|       | the CCPx PWM output latch to the default    |

|       | low level. This is not the port data latch. |

Figure 15-3 shows a simplified block diagram of the CCP module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see Section 15.4.3 "Setup for PWM Operation".

#### FIGURE 15-3: SIMPLIFIED PWM BLOCK DIAGRAM

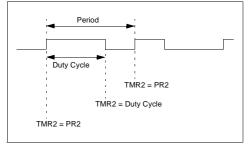

A PWM output (Figure 15-4) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

### 15.4.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula.

### EQUATION 15-1:

$PWM Period = [(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 Prescale Value)$

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (exception: if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is latched from CCPR1L into CCPR1H

## 15.4.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPRxL register and to the CCPxCON<5:4> bits. Up to 10-bit resolution is available. The CCPRxL contains the eight MSbs and the CCPxCON<5:4> contain the two LSbs. This 10-bit value is represented by CCPRxL:CCPxCON<5:4>. The following equation is used to calculate the PWM duty cycle in time.

### **EQUATION 15-2:**

```

PWM Duty Cycle = (CCPRxL:CCPxCON<5:4>) •

Tosc • (TMR2 Prescale Value)

```

CCPRxL and CCPxCON<5:4> can be written to at any time but the duty cycle value is not latched into CCPRxH until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPRxH is a read-only register.

The CCPRxH register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation.

When the CCPRxH and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCPx pin is cleared.

## 16.2 Enhanced PWM Mode

The Enhanced PWM mode provides additional PWM output options for a broader range of control applications. The module is a backward compatible version of the standard CCP module and offers up to four outputs, designated P1A through P1D. Users are also able to select the polarity of the signal (either active-high or active-low). The module's output mode and polarity are configured by setting the P1M1:P1M0 and CCP1M3:CCP1M0 bits of the CCP1CON register (CCP1CON<7:6> and CCP1CON<3:0>, respectively).

Figure 16-2 shows a simplified block diagram of PWM operation. All control registers are double-buffered and are loaded at the beginning of a new PWM cycle (the period boundary when Timer2 resets) in order to prevent glitches on any of the outputs. The exception is the PWM Delay register, ECCP1DEL, which is loaded at either the duty cycle boundary or the boundary period (whichever comes first). Because of the buffering, the module waits until the assigned timer resets instead of starting immediately. This means that enhanced PWM waveforms do not exactly match the standard PWM waveforms, but are instead offset by one full instruction cycle (4 Tosc).

As before, the user must manually configure the appropriate TRIS bits for output.

#### 16.2.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following equation.

### EQUATION 16-1:

$PWM Period = [(PR2) + 1] \cdot 4 \cdot TOSC \cdot (TMR2 Prescale Value)$

PWM frequency is defined as 1/[PWM period]. When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set (if PWM duty cycle = 0%, the CCP1 pin will not be set)

- The PWM duty cycle is copied from CCPR1L into CCPR1H

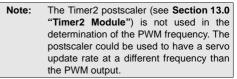

- Note: The Timer2 postscaler (see Section 13.0 "Timer2 Module") is not used in the determination of the PWM frequency. The postscaler could be used to have a servo update rate at a different frequency than the PWM output.

### 16.2.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR1L register and to the CCP1CON<5:4> bits. Up to 10-bit resolution is available. The CCPR1L contains the eight MSbs and the CCP1CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR1L:CCP1CON<5:4>. The PWM duty cycle is calculated by the following equation.

#### EQUATION 16-2:

```

PWM Duty Cycle = (CCPR1L:CCP1CON<5:4>) •

Tosc • (TMR2 Prescale Value)

```

CCPR1L and CCP1CON<5:4> can be written to at any time, but the duty cycle value is not copied into CCPR1H until a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR1H is a read-only register.

The CCPR1H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation. When the CCPR1H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or two bits of the TMR2 prescaler, the CCP1 pin is cleared. The maximum PWM resolution (bits) for a given PWM frequency is given by the following equation:

### EQUATION 16-3:

PWM Resolution (max) =

$$\frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)}$$

bits

Note: If the PWM duty cycle value is longer than the PWM period, the CCP1 pin will not be cleared.

### 16.2.3 PWM OUTPUT CONFIGURATIONS

The P1M1:P1M0 bits in the CCP1CON register allow one of four configurations:

- Single Output

- Half-Bridge Output

- Full-Bridge Output, Forward mode

- Full-Bridge Output, Reverse mode

The Single Output mode is the standard PWM mode discussed in **Section 16.2 "Enhanced PWM Mode"**. The Half-Bridge and Full-Bridge Output modes are covered in detail in the sections that follow.

The general relationship of the outputs in all configurations is summarized in Figure 16-3.

### 17.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 17-18).

NOTES:

| FER 23-51: | MSEL3: M                     | ASK SELE                   | CT REGIS      | TER 3(1)    |            |         |         |         |

|------------|------------------------------|----------------------------|---------------|-------------|------------|---------|---------|---------|

|            | R/W-0                        | R/W-0                      | R/W-0         | R/W-0       | R/W-0      | R/W-0   | R/W-0   | R/W-0   |

|            | FIL15_1                      | FIL15_0                    | FIL14_1       | FIL14_0     | FIL13_1    | FIL13_0 | FIL12_1 | FIL12_0 |

|            | bit 7                        |                            |               |             |            |         |         | bit 0   |

|            |                              |                            |               |             |            |         |         |         |

| bit 7-6    | _                            | 15_0: Filter 1             | 5 Select bit  | s 1 and 0   |            |         |         |         |

|            | 11 = No mas                  |                            |               |             |            |         |         |         |

|            | 10 = Filter 1<br>01 = Accept |                            |               |             |            |         |         |         |

|            |                              | ance Mask 0                |               |             |            |         |         |         |

| bit 5-4    | FIL14_1:FIL                  | 14_0: Filter 1             | 4 Select bit  | s 1 and 0   |            |         |         |         |

|            | 11 = No mas                  | sk                         |               |             |            |         |         |         |

|            | 10 = Filter 1                |                            |               |             |            |         |         |         |

|            | 01 = Accept                  | ance Mask 1<br>ance Mask 0 |               |             |            |         |         |         |

| bit 3-2    |                              | .13_0: Filter 1            | 3 Select hit  | s 1 and 0   |            |         |         |         |

| DIT O L    | 11 = No mas                  | _                          | 0 001001 511  |             |            |         |         |         |

|            | 10 = Filter 1                |                            |               |             |            |         |         |         |

|            | 01 = Accept                  |                            |               |             |            |         |         |         |

|            | •                            | ance Mask 0                |               |             |            |         |         |         |

| bit 1-0    | —                            | .12_0: Filter 1            | 2 Select bit  | s 1 and 0   |            |         |         |         |

|            | 11 = No mas<br>10 = Filter 1 |                            |               |             |            |         |         |         |

|            | 01 = Accept                  |                            |               |             |            |         |         |         |

|            |                              | ance Mask 0                |               |             |            |         |         |         |

|            | Note 1:                      | This register is           | s available i | n Mode 1 ar | nd 2 only. |         |         |         |

|            |                              |                            |               |             |            |         |         |         |

| REGISTER 23-51: N | MSEL3: MASK SELECT REGISTER 3 <sup>(1)</sup> |

|-------------------|----------------------------------------------|

|-------------------|----------------------------------------------|

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

- n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

| File                   | Name     | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3                | Bit 2  | Bit 1                 | Bit 0  | Default/<br>Unprogrammed<br>Value |

|------------------------|----------|-------|-------|--------|--------|----------------------|--------|-----------------------|--------|-----------------------------------|

| 300001h                | CONFIG1H |       |       | OSCSEN |        | FOSC3                | FOSC2  | FOSC1                 | FOSC0  | 1- 1111                           |

| 300002h                | CONFIG2L | _     | _     | _      | _      | BORV1                | BORV0  | BODEN                 | PWRTEN | 1111                              |

| 300003h                | CONFIG2H | _     | _     | _      | WDTPS3 | WDTPS2               | WDTPS1 | WDTPS0                | WDTEN  | 1 1111                            |

| 300004h <sup>(1)</sup> | CONFIG3L | WAIT  | _     | _      | _      | _                    | _      | PM1                   | PM0    | 111                               |

| 300005h                | CONFIG3H | MCLRE | -     | —      |        | —                    | —      | ECCPMX <sup>(4)</sup> | CCP2MX | 111                               |

| 300006h                | CONFIG4L | DEBUG |       | —      |        | —                    | LVP    | _                     | STVREN | 11-1                              |

| 300008h                | CONFIG5L | _     | _     | _      | _      | CP3 <sup>(2)</sup>   | CP2    | CP1                   | CP0    | 1111                              |

| 300009h                | CONFIG5H | CPD   | CPB   | _      | _      | _                    | _      | _                     | _      | 11                                |

| 30000Ah                | CONFIG6L |       | -     | —      |        | WRT3 <sup>(2)</sup>  | WRT2   | WRT1                  | WRT0   | 1111                              |

| 30000Bh                | CONFIG6H | WRTD  | WRTB  | WRTC   | _      | _                    | _      | _                     | _      | 111                               |

| 30000Ch                | CONFIG7L |       |       | —      |        | EBTR3 <sup>(2)</sup> | EBTR2  | EBTR1                 | EBTR0  | 1111                              |

| 30000Dh                | CONFIG7H |       | EBTRB | —      |        | —                    | —      | —                     |        | -1                                |

| 3FFFFEh                | DEVID1   | DEV2  | DEV1  | DEV0   | REV4   | REV3                 | REV2   | REV1                  | REV0   | (Note 3)                          |

| 3FFFFFh                | DEVID2   | DEV10 | DEV9  | DEV8   | DEV7   | DEV6                 | DEV5   | DEV4                  | DEV3   | 0000 1010                         |

## TABLE 24-1: CONFIGURATION BITS AND DEVICE IDS

$\label{eq:legend: Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition. Shaded cells are unimplemented, read as '0'.$

Note 1: Unimplemented in PIC18F6X8X devices; maintain this bit set.

2: Unimplemented in PIC18FX585 devices; maintain this bit set.

3: See Register 24-13 for DEVID1 values.

4: Reserved in PIC18F6X8X devices; maintain this bit set.

#### REGISTER 24-13: DEVICE ID REGISTER 1 FOR PIC18FXX8X DEVICES (ADDRESS 3FFFFEh)

| R     | R    | R    | R    | R    | R    | R    | R     |

|-------|------|------|------|------|------|------|-------|

| DEV2  | DEV1 | DEV0 | REV4 | REV3 | REV2 | REV1 | REV0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

bit 7-5 DEV2:DEV0: Device ID bits

000 = PIC18F8680

001 = PIC18F6680

010 = PIC18F8585

011 = PIC18F6585

### bit 4-0 REV4:REV0: Revision ID bits

These bits are used to indicate the device revision.

| Legend:                 |                      |                                     |

|-------------------------|----------------------|-------------------------------------|

| R = Readable bit        | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when device | e is unprogrammed    | u = Unchanged from programmed state |

#### REGISTER 24-14: DEVICE ID REGISTER 2 FOR PIC18FXX8X DEVICES (ADDRESS 3FFFFFh)

| R-0   | R-0  | R-0  | R-0  | R-1  | R-0  | R-1  | R-0   |

|-------|------|------|------|------|------|------|-------|

| DEV10 | DEV9 | DEV8 | DEV7 | DEV6 | DEV5 | DEV4 | DEV3  |

| bit 7 |      |      |      |      |      |      | bit 0 |

#### bit 7-0 DEV10:DEV3: Device ID bits

These bits are used with the DEV2:DEV0 bits in the Device ID Register 1 to identify the part number.

0000 1010 = PIC18F6585/8585/6680/8680

| Legend:                |                      |                                     |

|------------------------|----------------------|-------------------------------------|

| R = Readable bit       | P = Programmable bit | U = Unimplemented bit, read as '0'  |

| - n = Value when devic | e is unprogrammed    | u = Unchanged from programmed state |

# 24.2 Watchdog Timer (WDT)

The Watchdog Timer is a free-running, on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKI pin. That means that the WDT will run even if the clock on the OSC1/CLKI and OSC2/CLKO/RA6 pins of the device has been stopped, for example, by execution of a SLEEP instruction.

During normal operation, a WDT time-out generates a device Reset (Watchdog Timer Reset). If the device is in Sleep mode, a WDT time-out causes the device to wake-up and continue with normal operation (Watchdog Timer wake-up). The  $\overline{\text{TO}}$  bit in the RCON register will be cleared upon a WDT time-out.

The Watchdog Timer is enabled/disabled by a device configuration bit. If the WDT is enabled, software execution may not disable this function. When the WDTEN configuration bit is cleared, the SWDTEN bit enables/disables the operation of the WDT. The WDT time-out period values may be found in **Section 27.0** "**Electrical Characteristics**" under parameter #31. Values for the WDT postscaler may be assigned using the configuration bits.

- Note 1: The CLRWDT and SLEEP instructions clear the WDT and the postscaler if assigned to the WDT and prevent it from timing out and generating a device Reset condition.

- When a CLRWDT instruction is executed and the postscaler is assigned to the WDT, the postscaler count will be cleared but the postscaler assignment is not changed.

## 24.2.1 CONTROL REGISTER

Register 24-15 shows the WDTCON register. This is a readable and writable register which contains a control bit that allows software to override the WDT enable configuration bit, only when the configuration bit has disabled the WDT.

## REGISTER 24-15: WDTCON REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  |

|-------|-----|-----|-----|-----|-----|-----|--------|

| —     |     | —   | —   | —   | —   | —   | SWDTEN |

| bit 7 |     |     |     |     |     |     | bit 0  |

#### bit 7-1 Unimplemented: Read as '0'

bit 0 SWDTEN: Software Controlled Watchdog Timer Enable bit

- 1 = Watchdog Timer is on

- 0 = Watchdog Timer is turned off if the WDTEN configuration bit in the Configuration register = 0

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | d bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 24.4.2 DATA EEPROM CODE PROTECTION

The entire data EEPROM is protected from external reads and writes by two bits: CPD and WRTD. CPD inhibits external reads and writes of data EEPROM. WRTD inhibits external writes to data EEPROM. The CPU can continue to read and write data EEPROM readralless of the protection bit settings.

#### 24.4.3 CONFIGURATION REGISTER PROTECTION

The Configuration registers can be write-protected. The WRTC bit controls protection of the Configuration registers. In User mode, the WRTC bit is readable only. WRTC can only be written via ICSP or an external programmer.

## 24.5 ID Locations

Eight memory locations (200000h-200007h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are accessible during normal execution through the TBLRD and TBLWT instructions or during program/verify. The ID locations can be read when the device is code-protected.

## 24.6 In-Circuit Serial Programming

PIC18FXX80/XX85 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

## 24.7 In-Circuit Debugger

When the DEBUG bit in Configuration register, CONFIG4L, is programmed to a '0', the in-circuit debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 24-4 shows which features are consumed by the background debugger.

| <b>TABLE 24-4:</b> | DEBUGGER RESOURCES |

|--------------------|--------------------|

|--------------------|--------------------|

| I/O pins       | RB6, RB7  |  |  |  |  |

|----------------|-----------|--|--|--|--|

| Stack          | 2 levels  |  |  |  |  |

| Program Memory | 512 bytes |  |  |  |  |

| Data Memory    | 10 bytes  |  |  |  |  |

To use the in-circuit debugger function of the microcontroller, the design must implement In-Circuit Serial Programming connections to MCLR/VPP, VDD, GND, RB7 and RB6. This will interface to the in-circuit debugger module available from Microchip or one of the third party development tool companies.

| GOT                                                                                                                                                                                                | о                                       | Uncondi                   | tional B                    | ranch                    | ı    |                                        |           | INC   | =                           |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------|-----------------------------|--------------------------|------|----------------------------------------|-----------|-------|-----------------------------|----|

| Synta                                                                                                                                                                                              | ax:                                     | [ label ]                 | GOTO                        | k                        |      |                                        | •         | Synt  | ax:                         |    |

| Oper                                                                                                                                                                                               | rands:                                  | $0 \le k \le 10$          | )48575                      |                          |      |                                        |           | Ope   | rands:                      |    |

| Oper                                                                                                                                                                                               | ration:                                 | $k \rightarrow PC < 2$    | 20:1>                       |                          |      |                                        |           |       |                             |    |

| Statu                                                                                                                                                                                              | us Affected:                            | None                      |                             |                          |      |                                        |           | 000   | ration:                     |    |

| 1st w                                                                                                                                                                                              | oding:<br>vord (k<7:0>)<br>word(k<19:8> | 1110<br>) 1111            | 1111<br>k <sub>19</sub> kkk | k <sub>7</sub> kl<br>kkk |      | kkkk <sub>0</sub><br>kkkk <sub>8</sub> |           | Statu | us Affected:<br>oding:      |    |

| Description: GOTO allows an unconditional<br>branch anywhere within entire<br>2-Mbyte memory range. The 20-bit<br>value 'k' is loaded into PC<20:1>.<br>GOTO is always a two-cycle<br>instruction. |                                         |                           |                             |                          |      | Desc                                   | cription: |       |                             |    |

| Word                                                                                                                                                                                               | ds:                                     | 2                         |                             |                          |      |                                        |           |       |                             |    |

| Cycle                                                                                                                                                                                              | es:                                     | 2                         |                             |                          |      |                                        |           |       |                             |    |

| QC                                                                                                                                                                                                 | ycle Activity:                          |                           |                             |                          |      |                                        |           | Wor   | ds:                         |    |

|                                                                                                                                                                                                    | Q1                                      | Q2                        | Q                           | 3                        |      | Q4                                     | -         | Cvcl  | es:                         |    |

|                                                                                                                                                                                                    | Decode                                  | Read literal<br>'k'<7:0>, | No<br>operat                |                          | 'k'• | ad literal<br><19:8>,<br>te to PC      |           |       | co.<br>Sycle Activity<br>Q1 | y: |

|                                                                                                                                                                                                    | No<br>operation                         | No<br>operation           | No<br>operat                |                          | ор   | No<br>eration                          |           |       | Decode                      | 1  |

Example: GOTO THERE

After Instruction

PC = Address (THERE)

| INCF                   | Incremen                                                               | t f                                                                                                                                                                                                                                                                                                   |           |                               |  |  |  |

|------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------|--|--|--|

| Syntax:                | [ label ]                                                              | INCF                                                                                                                                                                                                                                                                                                  | f [,d [,a | ]]                            |  |  |  |

| Operands:              | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                  |                                                                                                                                                                                                                                                                                                       |           |                               |  |  |  |

| Operation:             | (f) + 1 $\rightarrow$ 0                                                | dest                                                                                                                                                                                                                                                                                                  |           |                               |  |  |  |

| Status Affected:       | C, DC, N                                                               | , OV, Z                                                                                                                                                                                                                                                                                               |           |                               |  |  |  |

| Encoding:              | 0010                                                                   | 10da                                                                                                                                                                                                                                                                                                  | ffff      | ffff                          |  |  |  |

|                        | is placed i<br>is placed l<br>(default). I<br>Bank will l<br>the BSR v | incremented. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result<br>is placed back in register 'f'<br>(default). If 'a' is '0', the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' = 1, then the<br>bank will be selected as per the<br>BSR using (default). |           |                               |  |  |  |

| Words:                 | 1                                                                      |                                                                                                                                                                                                                                                                                                       |           |                               |  |  |  |

| Cycles:                | 1                                                                      |                                                                                                                                                                                                                                                                                                       |           |                               |  |  |  |

|                        |                                                                        |                                                                                                                                                                                                                                                                                                       |           |                               |  |  |  |

| Q Cycle Activity       | •                                                                      |                                                                                                                                                                                                                                                                                                       |           |                               |  |  |  |

| Q Cycle Activity<br>Q1 | Q2                                                                     | Q3                                                                                                                                                                                                                                                                                                    | 8         | Q4                            |  |  |  |

|                        |                                                                        | Q3<br>Proce<br>Data                                                                                                                                                                                                                                                                                   | SS        | Q4<br>Write to<br>destination |  |  |  |

| Q1                     | Q2<br>Read                                                             | Proce<br>Data                                                                                                                                                                                                                                                                                         | SS        | Write to                      |  |  |  |

| RLNCF                     | Rotate Left f (no carry)                                                                                                                                                                                                                                                           | RRCF                                          | Rotate Right f through Carry                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                   | [ <i>label</i> ] RLNCF f [,d [,a]]                                                                                                                                                                                                                                                 | Syntax:                                       | [ <i>label</i> ] RRCF f [,d [,a]]                                                                                                                                                                                                                                                                                                                                                |

| Operands:                 | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                 | Operands:                                     | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                                               |

| Operation:                | $(f < n >) \rightarrow dest < n + 1 >,$<br>$(f < 7 >) \rightarrow dest < 0 >$                                                                                                                                                                                                      | Operation:                                    | $(f < n >) \rightarrow dest < n - 1 >,$<br>$(f < 0 >) \rightarrow C,$<br>$(C) \rightarrow dest < 7 >$                                                                                                                                                                                                                                                                            |

| Status Affected:          | N, Z                                                                                                                                                                                                                                                                               | Status Affected                               | ( )                                                                                                                                                                                                                                                                                                                                                                              |

| Encoding:<br>Description: | 0100 01da ffff<br>The contents of register 'f' ar                                                                                                                                                                                                                                  | <u>Encoding</u>                               | 0011 00da ffff fff                                                                                                                                                                                                                                                                                                                                                               |

|                           | rotated one bit to the left. If 'd<br>the result is placed in W. If 'd<br>the result is stored back in re<br>'f' (default). If 'a' is '0', the Ac<br>Bank will be selected, overric<br>the BSR value. If 'a' is '1', the<br>bank will be selected as per t<br>BSR value (default). | ' is '1',<br>gister<br>cess<br>ling<br>en the | The contents of register 'f' are<br>rotated one bit to the right throug<br>the Carry flag. If 'd' is '0', the res<br>is placed in W. If 'd' is '1', the res<br>is placed back in register 'f'<br>(default). If 'a' is '0', the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' is '1', then the<br>bank will be selected as per the<br>BSR value (default). |

| Words:                    | 1                                                                                                                                                                                                                                                                                  |                                               | C register f                                                                                                                                                                                                                                                                                                                                                                     |

| Cycles:                   | 1                                                                                                                                                                                                                                                                                  | Words:                                        | 1                                                                                                                                                                                                                                                                                                                                                                                |

| Q Cycle Activity<br>Q1    | :<br>Q2 Q3 Q4                                                                                                                                                                                                                                                                      | Cycles:                                       | 1                                                                                                                                                                                                                                                                                                                                                                                |

| Decode                    | Read Process Write<br>register 'f' Data destina                                                                                                                                                                                                                                    | to Q Cycle Activi                             | ty:<br>Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                  |

| Example:                  | RLNCF REG, 1, 0                                                                                                                                                                                                                                                                    | Decode                                        | Read         Process         Write tr           register 'f'         Data         destination                                                                                                                                                                                                                                                                                    |

| Before Instru             | uction                                                                                                                                                                                                                                                                             | <b>_</b> .                                    |                                                                                                                                                                                                                                                                                                                                                                                  |

| REG                       | = 1010 1011                                                                                                                                                                                                                                                                        | Example:                                      | RRCF REG, 0, 0                                                                                                                                                                                                                                                                                                                                                                   |

| After Instruc<br>REG      | tion<br>= 0101 0111                                                                                                                                                                                                                                                                | Before Ins<br>REG<br>C                        | = 1110 0110<br>= 0                                                                                                                                                                                                                                                                                                                                                               |

|                           |                                                                                                                                                                                                                                                                                    | After Instr                                   | iction                                                                                                                                                                                                                                                                                                                                                                           |

|         |                | rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the result<br>is placed in W. If 'd' is '1', the result<br>is placed back in register 'f'<br>(default). If 'a' is '0', the Access<br>Bank will be selected, overriding<br>the BSR value. If 'a' is '1', then the<br>bank will be selected as per the<br>BSR value (default). |                 |                      |  |  |  |

|---------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|--|--|--|

| Vor     | ds:            | 1                                                                                                                                                                                                                                                                                                                                                   |                 |                      |  |  |  |

| ycl     | es:            | 1                                                                                                                                                                                                                                                                                                                                                   |                 |                      |  |  |  |

| ຊດ      | ycle Activity: |                                                                                                                                                                                                                                                                                                                                                     |                 |                      |  |  |  |

|         | Q1             | Q2                                                                                                                                                                                                                                                                                                                                                  | Q3              | Q4                   |  |  |  |

| Decode  |                | Read<br>register 'f'                                                                                                                                                                                                                                                                                                                                | Process<br>Data | Write to destination |  |  |  |

| xample: |                | RRCF                                                                                                                                                                                                                                                                                                                                                | REG, 0, (       | )                    |  |  |  |

ffff

| Delote mat    | uction |           |      |

|---------------|--------|-----------|------|

| REG<br>C      | =<br>= | 1110<br>0 | 0110 |

| After Instruc | ction  |           |      |

| REG           | =      | 1110      | 0110 |

| W             | =      | 0111      | 0011 |

| С             | =      | 0         |      |

## 26.9 MPLAB ICE 2000 High-Performance Universal In-Circuit Emulator

The MPLAB ICE 2000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers. Software control of the MPLAB ICE 2000 in-circuit emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB ICE in-circuit emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE 2000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

## 26.10 MPLAB ICE 4000 High-Performance Universal In-Circuit Emulator

The MPLAB ICE 4000 universal in-circuit emulator is intended to provide the product development engineer with a complete microcontroller design tool set for highend PIC microcontrollers. Software control of the MPLAB ICE in-circuit emulator is provided by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICD 4000 is a premium emulator system, providing the features of MPLAB ICE 2000, but with increased emulation memory and high-speed performance for dsPIC30F and PIC18XXXX devices. Its advanced emulator features include complex triggering and timing, up to 2 Mb of emulation memory and the ability to view variables in real-time.

The MPLAB ICE 4000 in-circuit emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft Windows 32-bit operating system were chosen to best make these features available in a simple, unified application.

## 26.11 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low-cost, run-time development tool, connecting to the host PC via an RS-232 or high-speed USB interface. This tool is based on the Flash PIC MCUs and can be used to develop for these and other PIC microcontrollers. The MPLAB ICD 2 utilizes the incircuit debugging capability built into the Flash devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers cost effective in-circuit Flash debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, singlestepping and watching variables, CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real-time. MPLAB ICD 2 also serves as a development programmer for selected PIC devices

## 26.12 PRO MATE II Universal Device Programmer

The PRO MATE II is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features an LCD display for instructions and error messages and a modular detachable socket assembly to support various package types. In Stand-Alone mode, the PRO MATE II device programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode.

# 26.13 MPLAB PM3 Device Programmer

The MPLAB PM3 is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 device programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. MPLAB PM3 connects to the host PC via an RS-232 or USB cable. MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an SD/ MMC card for file storage and secure data applications.

## 27.2 DC Characteristics: Power-down and Supply Current PIC18FXX8X (Industrial, Extended) PIC18LFXX8X (Industrial) (Continued)

| PIC18LFXX8X<br>(Industrial) |                                                                                                                                                                                                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |     |       |            |            |                                 |  |  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|------------|---------------------------------|--|--|

| PIC18F)<br>(Indu            | Standard Operating Conditions (unless otherwise stated)           Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |                                                                                                                                    |     |       |            |            |                                 |  |  |

| Param. Device               |                                                                                                                                                                                                    | Тур                                                                                                                                | Max | Units | Conditions |            |                                 |  |  |

|                             | Supply Current (IDD) <sup>(2,3</sup>                                                                                                                                                               | 3)                                                                                                                                 |     |       |            |            |                                 |  |  |

|                             | PIC18FXX8X                                                                                                                                                                                         | 13                                                                                                                                 | 27  | mA    | -40°C      |            |                                 |  |  |

|                             |                                                                                                                                                                                                    | 15                                                                                                                                 | 27  | mA    | +25°C      | VDD = 4.2V |                                 |  |  |

|                             |                                                                                                                                                                                                    | 19                                                                                                                                 | 29  | mA    | +85°C      |            | Fosc = 25 MHz,                  |  |  |

|                             | PIC18FXX8X                                                                                                                                                                                         | 17                                                                                                                                 | 31  | mA    | -40°C      |            | EC oscillator                   |  |  |

|                             |                                                                                                                                                                                                    | 21                                                                                                                                 | 31  | mA    | +25°C      | VDD = 5.0V |                                 |  |  |

|                             |                                                                                                                                                                                                    | 23                                                                                                                                 | 34  | mA    | +85°C      |            |                                 |  |  |

|                             | PIC18FXX8X                                                                                                                                                                                         | 20                                                                                                                                 | 34  | mA    | -40°C      |            |                                 |  |  |

|                             |                                                                                                                                                                                                    | 24                                                                                                                                 | 34  | mA    | +25°C      | VDD = 4.2V | Fosc = 40 MHz,<br>EC oscillator |  |  |

|                             |                                                                                                                                                                                                    | 29                                                                                                                                 | 44  | mA    | +85°C      |            |                                 |  |  |

|                             | PIC18FXX8X                                                                                                                                                                                         | 28                                                                                                                                 | 46  | mA    | -40°C      |            |                                 |  |  |

|                             |                                                                                                                                                                                                    | 33                                                                                                                                 | 46  | mA    | +25°C      | VDD = 5.0V |                                 |  |  |

|                             |                                                                                                                                                                                                    | 40                                                                                                                                 | 51  | mA    | +85°C      |            |                                 |  |  |

| D014                        | PIC18LFXX8X                                                                                                                                                                                        | 27                                                                                                                                 | 45  | μΑ    | -10°C      |            |                                 |  |  |

|                             |                                                                                                                                                                                                    | 30                                                                                                                                 | 50  | μΑ    | +25°C      | VDD = 2.0V |                                 |  |  |

|                             | -                                                                                                                                                                                                  | 32                                                                                                                                 | 54  | μΑ    | +70°C      |            |                                 |  |  |

|                             | PIC18LFXX8X                                                                                                                                                                                        | 33                                                                                                                                 | 55  | μΑ    | -10°C      | -          | Fosc = 32 kHz,                  |  |  |

|                             |                                                                                                                                                                                                    | 36                                                                                                                                 | 60  | μA    | +25°C      | VDD = 3.0V | Timer1 as clock                 |  |  |