Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status     Obsolete       Core Processor     PIC       Core Size     8-Bit      |

|-----------------------------------------------------------------------------------------|

| Core Size 8-Bit                                                                         |

|                                                                                         |

|                                                                                         |

| Speed 40MHz                                                                             |

| Connectivity CANbus, I <sup>2</sup> C, SPI, UART/USART                                  |

| Peripherals Brown-out Detect/Reset, LVD, POR, PWM, WDT                                  |

| Number of I/O 52                                                                        |

| Program Memory Size 48KB (24K x 16)                                                     |

| Program Memory Type FLASH                                                               |

| EEPROM Size 1K x 8                                                                      |

| RAM Size 3.25K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd)2V ~ 5.5V                                                     |

| Data Converters A/D 12x10b                                                              |

| Oscillator Type External                                                                |

| Operating Temperature -40°C ~ 85°C (TA)                                                 |

| Mounting Type Surface Mount                                                             |

| Package / Case 68-LCC (J-Lead)                                                          |

| Supplier Device Package68-PLCC (24.23x24.23)                                            |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/pic18lf6585t-i-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                      |          | Pin Nu    | mber         |             |                |                                                    |  |

|----------------------|----------|-----------|--------------|-------------|----------------|----------------------------------------------------|--|

| Pin Name             | PIC18    | F6X8X     | PIC18F8X8X   | Pin<br>Type | Buffer<br>Type | Description                                        |  |

|                      | TQFP     | PLCC      | TQFP         | Type        | Type           |                                                    |  |

|                      |          |           |              |             |                | PORTF is a bidirectional I/O port.                 |  |

| RF0/AN5              | 18       | 28        | 24           |             |                |                                                    |  |

| RF0                  |          |           |              | I/O         | ST             | Digital I/O.                                       |  |

| AN5                  |          |           |              | I           | Analog         | Analog input 5.                                    |  |

| RF1/AN6/C2OUT        | 17       | 27        | 23           |             |                |                                                    |  |

| RF1                  |          |           |              | I/O         | ST             | Digital I/O.                                       |  |

| AN6                  |          |           |              | I           | Analog         | Analog input 6.                                    |  |

| C2OUT                |          |           |              | 0           | ST             | Comparator 2 output.                               |  |

| RF2/AN7/C1OUT        | 16       | 26        | 18           |             |                |                                                    |  |

| RF2                  |          |           |              | I/O         | ST             | Digital I/O.                                       |  |

| AN7                  |          |           |              | I           | Analog         | Analog input 7.                                    |  |

| C1OUT                |          |           |              | 0           | ST             | Comparator 1 output.                               |  |

| RF3/AN8/C2IN+        | 15       | 25        | 17           |             |                |                                                    |  |

| RF1                  |          |           |              | I/O         | ST             | Digital I/O.                                       |  |

| AN8                  |          |           |              | Ι           | Analog         | Analog input 8.                                    |  |

| C2IN+                |          |           |              | Ι           | Analog         | Comparator 2 input (+).                            |  |

| RF4/AN9/C2IN-        | 14       | 24        | 16           |             |                |                                                    |  |

| RF1                  |          |           |              | I/O         | ST             | Digital I/O.                                       |  |

| AN9                  |          |           |              | I           | Analog         | Analog input 9.                                    |  |

| C2IN-                |          |           |              | Ι           | Analog         | Comparator 2 input (-).                            |  |

| RF5/AN10/C1IN+/CVREF | 13       | 23        | 15           |             |                |                                                    |  |

| RF1                  |          |           |              | I/O         | ST             | Disitel I/O                                        |  |

| AN10<br>C1IN+        |          |           |              | 1/O         | Analog         | Digital I/O.<br>Analog input 10.                   |  |

| CVREF                |          |           |              |             | Analog         | Comparator 1 input (+).                            |  |

| OWNER                |          |           |              | ò           | Analog         | Comparator VREF output.                            |  |

| RF6/AN11/C1IN-       | 12       | 22        | 14           | Ū           | , maiog        |                                                    |  |

| RF6                  | 12       | ~~        | 14           | I/O         | ST             | Digital I/O.                                       |  |

| AN11                 |          |           |              | "C          | Analog         | Analog input 11.                                   |  |

| C1IN-                |          |           |              | i           | Analog         | Comparator 1 input (-)                             |  |

| RF7/SS               | 11       | 21        | 13           |             |                |                                                    |  |

| RF7                  |          | 21        |              | I/O         | ST             | Digital I/O.                                       |  |

| SS                   |          |           |              | 1           | TTL            | SPI slave select input.                            |  |

| Legend: TTL = TTL    | compatik | ole input | 1            | []          |                | = CMOS compatible input or output                  |  |

|                      |          |           | with CMOS le | vels        |                | = Analog input                                     |  |

| I = Input            |          |           |              |             |                | = Output                                           |  |

| P = Powe             | ər       |           |              |             | OD             | <ul> <li>Open-Drain (no P diode to VDD)</li> </ul> |  |

### TABLE 1-2: PIC18F6585/8585/6680/8680 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Alternate assignment for CCP2 in all operating modes except Microcontroller – applies to PIC18F8X8X only.

2: Default assignment when CCP2MX is set.

3: External memory interface functions are only available on PIC18F8X8X devices.

4: CCP2 is multiplexed with this pin by default when configured in Microcontroller mode; otherwise, it is multiplexed with either RB3 or RC1.

5: PORTH and PORTJ are only available on PIC18F8X8X (80-pin) devices.

6: PSP is available in Microcontroller mode only.

7: On PIC18F8X8X devices, these pins can be multiplexed with RH7/RH6 by changing the ECCPMX configuration bit.

# TABLE 2-2:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Ranges Tested: |          |          |          |  |  |  |  |  |

|----------------|----------|----------|----------|--|--|--|--|--|

| Mode           | Freq     | C1       | C2       |  |  |  |  |  |

| LP             | 32.0 kHz | 33 pF    | 33 pF    |  |  |  |  |  |

|                | 200 kHz  | 15 pF    | 15 pF    |  |  |  |  |  |

| XT             | 200 kHz  | 47-68 pF | 47-68 pF |  |  |  |  |  |

|                | 1.0 MHz  | 15 pF    | 15 pF    |  |  |  |  |  |

|                | 4.0 MHz  | 15 pF    | 15 pF    |  |  |  |  |  |

| HS             | 4.0 MHz  | 15 pF    | 15 pF    |  |  |  |  |  |

|                | 8.0 MHz  | 15-33 pF | 15-33 pF |  |  |  |  |  |

|                | 20.0 MHz | 15-33 pF | 15-33 pF |  |  |  |  |  |

|                | 25.0 MHz | TBD      | TBD      |  |  |  |  |  |

| <b>T</b> 1     |          | -1       |          |  |  |  |  |  |

These values are for design guidance only. See notes following this table.

| Crystals Used |                        |          |  |  |  |  |

|---------------|------------------------|----------|--|--|--|--|

| 32.0 kHz      | Epson C-001R32.768K-A  | ± 20 PPM |  |  |  |  |

| 200 kHz       | STD XTL 200.000KHz     | ± 20 PPM |  |  |  |  |

| 1.0 MHz       | ECS ECS-10-13-1        | ± 50 PPM |  |  |  |  |

| 4.0 MHz       | ECS ECS-40-20-1        | ± 50 PPM |  |  |  |  |

| 8.0 MHz       | Epson CA-301 8.000M-C  | ± 30 PPM |  |  |  |  |

| 20.0 MHz      | Epson CA-301 20.000M-C | ± 30 PPM |  |  |  |  |

- Note 1: Higher capacitance increases the stability of the oscillator, but also increases the start-up time.

- 2: Rs (see Figure 2-1) may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specifications.

- Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components, or verify oscillator performance.

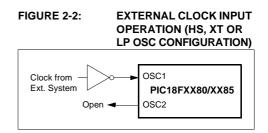

An external clock source may also be connected to the OSC1 pin in the HS, XT and LP modes, as shown in Figure 2-2.

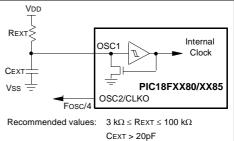

# 2.3 RC Oscillator

For timing insensitive applications, the "RC" and "RCIO" device options offer additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit, due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low CEXT values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 2-3 shows how the R/C combination is connected.

In the RC Oscillator mode, the oscillator frequency divided by 4 is available on the OSC2 pin. This signal may be used for test purposes or to synchronize other logic.

The RCIO Oscillator mode functions like the RC mode except that the OSC2 pin becomes an additional general purpose I/O pin. The I/O pin becomes bit 6 of PORTA (RA6).

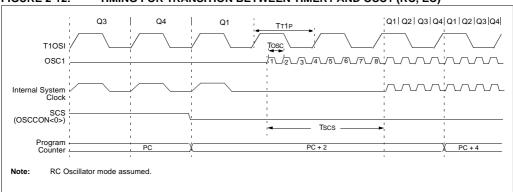

If the main oscillator is configured in the RC, RCIO, EC or ECIO modes, there is no oscillator start-up time-out. Operation will resume after eight cycles of the main oscillator have been counted. A timing diagram, indicating the transition from the Timer1 oscillator to the main oscillator for RC, RCIO, EC and ECIO modes, is shown in Figure 2-12.

### FIGURE 2-12: TIMING FOR TRANSITION BETWEEN TIMER1 AND OSC1 (RC, EC)

© 2003-2013 Microchip Technology Inc.

### 17.4.3.2 Reception

When the  $R/\overline{W}$  bit of the address byte is clear and an address match occurs, the  $R/\overline{W}$  bit of the SSPSTAT register is cleared. The received address is loaded into the SSPBUF register and the SDA line is held low (ACK).

When the address byte overflow condition exists, then the no Acknowledge (ACK) pulse is given. An overflow condition is defined as either bit BF (SSPSTAT<0>) is set or bit SSPOV (SSPCON1<6>) is set.

An MSSP interrupt is generated for each data transfer byte. Flag bit SSPIF (PIR1<3>) must be cleared in software. The SSPSTAT register is used to determine the status of the byte.

If SEN is enabled (SSPCON2<0> = 1), RC3/SCK/SCL will be held low (clock stretch) following each data transfer. The clock must be released by setting bit CKP (SSPCON<4>). See **Section 17.4.4** "Clock **Stretching**" for more detail.

### 17.4.3.3 Transmission

When the R/W bit of the incoming address byte is set and an address match occurs, the R/W bit of the SSPSTAT register is set. The received address is loaded into the SSPBUF register. The ACK pulse will be sent on the ninth bit and pin RC3/SCK/SCL is held low, regardless of SEN (see Section 17.4.4 "Clock Stretching" for more detail). By stretching the clock, the master will be unable to assert another clock pulse until the slave is done preparing the transmit data. The transmit data must be loaded into the SSPBUF register which also loads the SSPSR register. Then pin RC3/ SCK/SCL should be enabled by setting bit CKP (SSPCON1<4>). The eight data bits are shifted out on the falling edge of the SCL input. This ensures that the SDA signal is valid during the SCL high time (Figure 17-9).

The  $\overline{ACK}$  pulse from the master-receiver is latched on the rising edge of the ninth SCL input pulse. If the SDA line is high (not  $\overline{ACK}$ ), then the data transfer is complete. In this case, when the  $\overline{ACK}$  is latched by the slave, the slave logic is reset (resets SSPSTAT register) and the slave monitors for another occurrence of the Start bit. If the SDA line was low ( $\overline{ACK}$ ), the next transmit data must be loaded into the SSPBUF register. Again, pin RC3/SCK/SCL must be enabled by setting bit CKP.

An MSSP interrupt is generated for each data transfer byte. The SSPIF bit must be cleared in software and the SSPSTAT register is used to determine the status of the byte. The SSPIF bit is set on the falling edge of the ninth clock pulse.

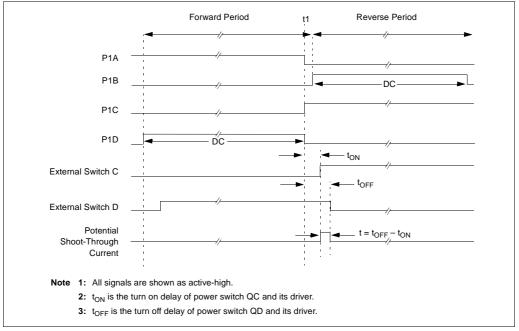

# 17.4.4.5 Clock Synchronization and the CKP bit

When the CKP bit is cleared, the SCL output is forced to '0'. However, setting the CKP bit will not assert the SCL output low until the SCL output is already sampled low. Therefore, the CKP bit will not assert the SCL line until an external  $I^2C$  master device has already asserted the SCL line. The SCL output will remain low until the CKP bit is set and all other devices on the  $I^2C$ bus have deasserted SCL. This ensures that a write to the CKP bit will not violate the minimum high time requirement for SCL (see Figure 17-12).

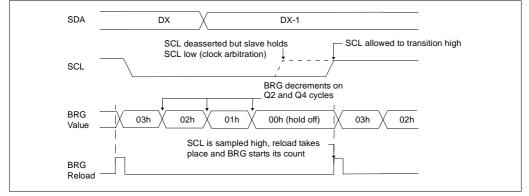

### 17.4.7.1 Clock Arbitration

Clock arbitration occurs when the master, during any receive, transmit or Repeated Start/Stop condition, deasserts the SCL pin (SCL allowed to float high). When the SCL pin is allowed to float high, the Baud Rate Generator (BRG) is suspended from counting until the SCL pin is actually sampled high. When the

SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of SSPADD<6:0> and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device (Figure 17-18).

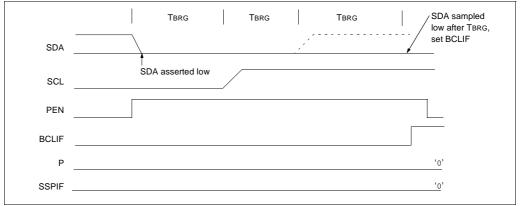

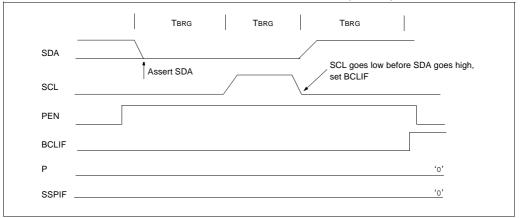

### 17.4.17.3 Bus Collision During a Stop Condition

Bus collision occurs during a Stop condition if:

- After the SDA pin has been deasserted and allowed to float high, SDA is sampled low after the BRG has timed out.

- b) After the SCL pin is deasserted, SCL is sampled low before SDA goes high.

The Stop condition begins with SDA asserted low. When SDA is sampled low, the SCL pin is allowed to float. When the pin is sampled high (clock arbitration), the Baud Rate Generator is loaded with SSPADD-6:0> and counts down to '0'. After the BRG times out, SDA is sampled. If SDA is sampled low, a bus collision has occurred. This is due to another master attempting to drive a data '0' (Figure 17-31). If the SCL pin is sampled low before SDA is allowed to float high, a bus collision occurs. This is another case of another master attempting to drive a data '0' (Figure 17-32).

### FIGURE 17-31: BUS COLLISION DURING A STOP CONDITION (CASE 1)

#### FIGURE 17-32: BUS COLLISION DURING A STOP CONDITION (CASE 2)

# 18.0 ENHANCED UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI.) The USART can be configured as a full-duplex asynchronous system that can communicate with peripheral devices, such as CRT terminals and personal computers. It can also be configured as a half-duplex synchronous system that can communicate with peripheral devices, such as A/D or D/A integrated circuits, serial EEPROMs, etc.

The Enhanced USART module implements additional features, including automatic baud rate detection and calibration, automatic wake-up on sync break reception and 12-bit break character transmit. These make it ideally suited for use in Local Interconnect Network bus (LIN bus) systems.

The USART can be configured in the following modes:

- · Asynchronous (full-duplex) with:

- Auto-wake-up on character reception

- Auto-baud calibration

- 12-bit break character transmission

- Synchronous Master (half-duplex) with selectable clock polarity

- Synchronous Slave (half-duplex) with selectable clock polarity

In order to configure pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter:

- SPEN (RCSTA<7>) bit must be set (= 1),

- TRISC<6> bit must be set (= 1), and

- TRISC<7> bit must be set (= 1).

The operation of the Enhanced USART module is controlled through three registers:

- Transmit Status and Control (TXSTA)

- Receive Status and Control (RCSTA)

- Baud Rate Control (BAUDCON)

These are detailed on the following pages in Register 18-1, Register 18-2 and Register 18-3, respectively.

#### 18.2.4 AUTO-WAKE-UP ON SYNC BREAK CHARACTER

During Sleep mode, all clocks to the USART are suspended. Because of this, the Baud Rate Generator is inactive and a proper byte reception cannot be performed. The auto-wake-up feature allows the controller to wake-up due to activity on the RX/DT line while the USART is operating in Asynchronous mode.

The auto-wake-up feature is enabled by setting the WUE bit (BAUDCON<1>). Once set, the typical receive sequence on RX/DT is disabled and the USART remains in an Idle state monitoring for a wake-up event independent of the CPU mode. A wake-up event consists of a high-to-low transition on the RX/DT line. (This coincides with the start of a sync break or a wake-up signal character for the LIN protocol.)

Following a wake-up event, the module generates an RCIF interrupt. The interrupt is generated synchronously to the Q clocks in normal operating modes (Figure 18-7) and asynchronously, if the device is in Sleep mode (Figure 18-8). The interrupt condition is cleared by reading the RCREG register.

The WUE bit is automatically cleared once a low-tohigh transition is observed on the RX line following the wake-up event. At this point, the USART module is in Idle mode and returns to normal operation. This signals to the user that the sync break event is over.

#### 18.2.4.1 Special Considerations Using Auto-Wake-up

Since auto-wake-up functions by sensing rising edge transitions on RX/DT, information with any state changes before the Stop bit may signal a false end-of-character

and cause data or framing errors. To work properly, therefore, the initial character in the transmission must be all '0's. This can be 00h (8 bytes) for standard RS-232 devices or 000h (12 bits) for LIN bus.

Oscillator start-up time must also be considered, especially in applications using oscillators with longer start-up intervals (i.e., XT or HS mode). The sync break (or wake-up signal) character must be of sufficient length and be followed by a sufficient interval to allow enough time for the selected oscillator to start and provide proper initialization of the USART.

# 18.2.4.2 Special Considerations Using the WUE Bit

The timing of WUE and RCIF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the USART in an Idle mode. The wake-up event causes a receive interrupt by setting the RCIF bit. The WUE bit is cleared after this when a rising edge is seen on RX/DT. The interrupt condition is then cleared by reading the RCREG register. Ordinarily, the data in RCREG will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set) and the RCIF flag is set should not be used as an indicator of the integrity of the data in RCREG. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process. If a receive operation is not occurring, the WUE bit may then be set just prior to entering the Sleep mode.

### FIGURE 18-7: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING NORMAL OPERATION

| 0804       |             |            | nunun. | <u> (</u> 4 | www. | ç.        | nan                                      | yunuru | ntanar      | (î  | , wa | Ω,       | WWWW<br>M |           | Ω. |

|------------|-------------|------------|--------|-------------|------|-----------|------------------------------------------|--------|-------------|-----|------------------------------------------|----------|-----------|-----------|----|

|            | ු පමණිනයාදී | 2000 ····· |        |             |      |           |                                          |        |             | 3   |                                          |          | 1         | geneesees |    |

| WOE 58     |             |            |        | 1           |      | 5         |                                          |        |             | é.  |                                          | 1        | [         |           |    |

|            | ·<br>·      |            |        | Lunda       |      |           |                                          |        | 1           | •   |                                          |          |           |           |    |

| 86601.0999 | 1           | :          |        | . 2         |      | <i></i>   | an a |        |             | 911 |                                          | <u> </u> |           |           |    |

|            |             |            |        | 11          |      | 2         |                                          | S      |             |     | ,<br>,                                   |          |           | ,         |    |

| 199, M     |             |            |        |             |      | inne<br>1 |                                          | -      |             |     |                                          |          |           |           |    |

|            |             |            |        |             |      |           |                                          |        | Cleared det | 230 | 1,669,18692                              | 5 OL     | 20262/    |           |    |

## FIGURE 18-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

### 18.4 USART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit CSRC (TXSTA<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the RC6/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

#### 18.4.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the Sleep mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- If enable bit TXIE is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a synchronous slave transmission:

- Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, set enable bit TXIE.

- 4. If 9-bit transmission is desired, set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name    | Bit 7       | Bit 6          | Bit 5       | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Value on POR, BOR | Value on<br>all other<br>Resets |

|---------|-------------|----------------|-------------|--------|-------|--------|--------|--------|-------------------|---------------------------------|

| INTCON  | GIE/GIEH    | PEIE/GIEL      | TMR0IE      | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | x000 000x         | 0000 000u                       |

| PIR1    | PSPIF       | ADIF           | RCIF        | TXIF   | SSPIF | CCP1IF | TMR2IF | TMR1IF | 0000 0000         | 0000 0000                       |

| PIE1    | PSPIE       | ADIE           | RCIE        | TXIE   | SSPIE | CCP1IE | TMR2IE | TMR1IE | 0000 0000         | 0000 0000                       |

| IPR1    | PSPIP       | ADIP           | RCIP        | TXIP   | SSPIP | CCP1IP | TMR2IP | TMR1IP | 1111 1111         | 1111 1111                       |

| RCSTA   | SPEN        | RX9            | SREN        | CREN   | ADDEN | FERR   | OERR   | RX9D   | x000 000x         | 0000 000x                       |

| TXREG   | USART Trar  | nsmit Register |             |        |       |        |        |        | 0000 0000         | 0000 0000                       |

| TXSTA   | CSRC        | TX9            | TXEN        | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 0000 0010         | 0000 0010                       |

| BAUDCON | _           | RCIDL          | _           | SCKP   | BRG16 | _      | WUE    | ABDEN  | -1-1 0-00         | -1-1 0-00                       |

| SPBRGH  | Baud Rate G | Generator Reg  | ister, High | Byte   |       |        |        |        | 0000 0000         | 0000 0000                       |

| SPBRG   | Baud Rate G | Generator Reg  | ister, Low  | Byte   |       |        |        |        | 0000 0000         | 0000 0000                       |

### TABLE 18-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

Legend: x = unknown, - = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

| REGISTER 23-2: | CANSTAT: CA                                                | N STATU                      | S REGISTER                              |                           |              |            |                |               |  |

|----------------|------------------------------------------------------------|------------------------------|-----------------------------------------|---------------------------|--------------|------------|----------------|---------------|--|

| Mada           | R-1                                                        | R-0                          | R-0                                     | R-0                       | R-0          | R-0        | R-0            | U-0           |  |

| Mode 0         | OPMODE2 <sup>(1)</sup>                                     | OPMODE1 <sup>(1)</sup>       | OPMODE0 <sup>(1)</sup>                  | _                         | ICODE2       | ICODE1     | ICODE0         | _             |  |

|                | ı                                                          |                              |                                         |                           | 1            |            |                |               |  |

| Mode 1, 2      | R-1                                                        | R-0                          | R-0                                     | R-0                       | R-0          | R-0        | R-0            | R-0           |  |

| mode 1, 2      | OPMODE2 <sup>(1)</sup>                                     | OPMODE1 <sup>(1)</sup>       | OPMODE0 <sup>(1)</sup>                  | EICODE4                   | EICODE3      | EICODE2    | EICODE1        | EICODE0       |  |

|                | bit 7                                                      |                              |                                         |                           |              |            |                | bit 0         |  |

| bit 7-5        | OPMODE2:OP                                                 | MODEO: Or                    | peration Mode                           | Status bits               | (1)          |            |                |               |  |

|                | 111 = Reserve                                              |                              |                                         |                           |              |            |                |               |  |

|                |                                                            | 110 = Reserved               |                                         |                           |              |            |                |               |  |

|                | 101 = Reserve                                              | 01 = Reserved                |                                         |                           |              |            |                |               |  |

|                | 100 = Configur                                             |                              |                                         |                           |              |            |                |               |  |

|                | 011 = Listen O                                             |                              |                                         |                           |              |            |                |               |  |

|                | 010 = Loopbac<br>001 = Disable/3                           |                              |                                         |                           |              |            |                |               |  |

|                | 001 = Disable/3<br>000 = Normal r                          | •                            |                                         |                           |              |            |                |               |  |

| bit 4          | Mode 0:                                                    |                              |                                         |                           |              |            |                |               |  |

|                | Unimplemente                                               | d: Read as                   | '0'                                     |                           |              |            |                |               |  |

| bit 3-1        | ICODE2:ICOD                                                |                              |                                         | ode 0                     |              |            |                |               |  |

|                | When an interrecode indicates sible to select the example. | upt occurs, a<br>he source o | a prioritized coo<br>f the interrupt. E | led interru<br>By copying | ICODE2:IO    | CODE0 to V | WIN2:WINC      | ), it is pos- |  |

|                |                                                            | IC                           | ODE2:ICODE0                             | Value                     |              |            |                |               |  |

|                | No interrupt                                               |                              | 000                                     |                           |              |            |                |               |  |

|                | Error interrupt                                            |                              | 001                                     |                           |              |            |                |               |  |

|                | TXB2 interrupt                                             |                              | 010                                     |                           |              |            |                |               |  |

|                | TXB1 interrupt                                             |                              | 011                                     |                           |              |            |                |               |  |

|                | TXB0 interrupt                                             |                              | 100                                     |                           |              |            |                |               |  |

|                | RXB1 interrupt                                             |                              | 101                                     |                           |              |            |                |               |  |

|                | RXB0 interrupt<br>Wake-up interr                           |                              | 110<br>111                              |                           |              |            |                |               |  |

|                | -                                                          | -                            |                                         |                           |              |            |                |               |  |

| bit 0          | Unimplemente                                               | a: Read as                   | .0.                                     |                           |              |            |                |               |  |

|                | Legend:                                                    |                              |                                         |                           |              |            |                |               |  |

|                | R = Readable                                               | bit W                        | = Writable bit                          | U                         | = Unimple    | mented bit | , read as '0   | ,             |  |

|                | - n = Value at F                                           | POR '1                       | = Bit is set                            | '0'                       | = Bit is cle | eared x    | a = Bit is unl | known         |  |

## © 2003-2013 Microchip Technology Inc.

#### EXAMPLE 23-3: TRANSMITTING A CAN MESSAGE USING BANKED METHOD

; Need to transmit Standard Identifier message 123h using TXB0 buffer. ; To successfully transmit, CAN module must be either in Normal or Loopback mode. ; TXBO buffer is not in access bank. And since we want banked method, we need to make sure ; that correct bank is selected. BANKSEL TXB0CON ; One BANKSEL in beginning will make sure that we are ; in correct bank for rest of the buffer access. ; Now load transmit data into TXB0 buffer. MOVLW MY\_DATA BYTE1 ; Load first data byte into buffer ; Compiler will automatically set "BANKED" bit MOVWF TXB0D0 ; Load rest of data bytes - up to 8 bytes into TXBO buffer. . . . ; Load message identifier MOVLW 60H ; Load SID2:SID0, EXIDE = 0 MOVWF TXB0SIDL MOVLW 24H ; Load SID10:SID3 MOVWF TXB0SIDH ; No need to load TXB0EIDL:TXB0EIDH, as we are transmitting Standard Identifier Message only. ; Now that all data bytes are loaded, mark it for transmission. MOVLW B'00001000' ; Normal priority; Request transmission MOVWF TXB0CON ; If required, wait for message to get transmitted BTFSC TXBOCON, TXREQ ; Is it transmitted? BRA \$-2 ; No. Continue to wait... ; Message is transmitted.

| TER 23-48: | MSEL0: M                                                   | ASK SELE         | CT REGIS      | TER 0 <sup>(1)</sup> |            |        |        |        |

|------------|------------------------------------------------------------|------------------|---------------|----------------------|------------|--------|--------|--------|

|            | R/W-0                                                      | R/W-1            | R/W-0         | R/W-1                | R/W-0      | R/W-0  | R/W-0  | R/W-0  |

|            | FIL3_1                                                     | FIL3_0           | FIL2_1        | FIL2_0               | FIL1_1     | FIL1_0 | FIL0_1 | FIL0_0 |

|            | bit 7                                                      |                  |               |                      |            |        |        | bit 0  |

| bit 7-6    | 11 = No mas<br>10 = Filter 1<br>01 = Accept                |                  | elect bits 1  | and 0                |            |        |        |        |

| bit 5-4    | 11 = No mas<br>10 = Filter 1<br>01 = Accept                |                  | elect bits 1  | and 0                |            |        |        |        |

| bit 3-2    | 11 = No mas<br>10 = Filter 1<br>01 = Accept                |                  | elect bits 1  | and 0                |            |        |        |        |

| bit 1-0    | 11 = No mas<br>10 = Filter 1<br>01 = Accept<br>00 = Accept |                  |               |                      |            |        |        |        |

|            | NOLE I.                                                    | i nis register i | s avaliable i |                      | iu z oniy. |        |        |        |

| Legend:            |                  |                                         |

|--------------------|------------------|-----------------------------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented bit, read as '0'      |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

# REGISTER 23-48: MSEL0: MASK SELECT REGISTER 0<sup>(1)</sup>

## 25.1 Instruction Set

| ADD         | DLW             | ADD litera            | al to W           |                        |  |  |  |  |  |

|-------------|-----------------|-----------------------|-------------------|------------------------|--|--|--|--|--|

| Synt        | ax:             | [label] A             | [label] ADDLW k   |                        |  |  |  |  |  |

| Ope         | rands:          | $0 \le k \le 25$      | $0 \le k \le 255$ |                        |  |  |  |  |  |

| Ope         | ration:         | (W) + k $\rightarrow$ | $(W) + k \to W$   |                        |  |  |  |  |  |

| Statu       | us Affected:    | N, OV, C,             | N, OV, C, DC, Z   |                        |  |  |  |  |  |

| Enco        | oding:          | 0000                  | 1111 kk           | kk kkkk                |  |  |  |  |  |

| Des         | cription:       |                       | I 'k' and the     | added to the result is |  |  |  |  |  |

| Wor         | ds:             | 1                     |                   |                        |  |  |  |  |  |

| Cycl        | es:             | 1                     |                   |                        |  |  |  |  |  |

| QC          | cycle Activity: |                       |                   |                        |  |  |  |  |  |

|             | Q1              | Q2                    | Q3                | Q4                     |  |  |  |  |  |

|             | Decode          | Read<br>literal 'k'   | Process<br>Data   | Write to W             |  |  |  |  |  |

| <u>Exar</u> | <u>mple</u> :   | ADDLW 0               | x15               |                        |  |  |  |  |  |

|             | Before Instru   | ction                 |                   |                        |  |  |  |  |  |

|             | W =             | 0x10                  |                   |                        |  |  |  |  |  |

|             | After Instruct  | ion                   |                   |                        |  |  |  |  |  |

|             | W =             | 0x25                  |                   |                        |  |  |  |  |  |

| ADDWF                     | ADD W to                                                                       | o f                                              |                           |                     |                                |  |  |  |  |

|---------------------------|--------------------------------------------------------------------------------|--------------------------------------------------|---------------------------|---------------------|--------------------------------|--|--|--|--|

| Syntax:                   | [ label ] A                                                                    | DDWF                                             | f [,c                     | d [,a               | ] f [,d [,a]                   |  |  |  |  |

| Operands:                 | $0 \le f \le 25$<br>$d \in [0,1]$<br>$a \in [0,1]$                             |                                                  |                           |                     |                                |  |  |  |  |

| Operation:                | (W) + (f) -                                                                    | (W) + (f) $\rightarrow$ dest                     |                           |                     |                                |  |  |  |  |

| Status Affected:          | N, OV, C,                                                                      | DC, Z                                            |                           |                     |                                |  |  |  |  |

| Encoding:                 | 0010                                                                           | 01da                                             | fff                       | f                   | ffff                           |  |  |  |  |

| Description:              | Add W to<br>result is s<br>result is s<br>(default).<br>Bank will<br>the BSR i | tored in<br>tored ba<br>If 'a' is 'o<br>be selec | W. If<br>ck in<br>D', the | ʻd'is<br>regi<br>Ac | s '1', the<br>ster 'd'<br>cess |  |  |  |  |

| Words:                    | 1                                                                              |                                                  |                           |                     |                                |  |  |  |  |

| Cycles:                   | 1                                                                              | 1                                                |                           |                     |                                |  |  |  |  |

| Q Cycle Activity:         |                                                                                |                                                  |                           |                     |                                |  |  |  |  |

| Q1                        | Q2                                                                             | Q3                                               | 3                         |                     | Q4                             |  |  |  |  |

| Decode                    | Read                                                                           | Process<br>Data                                  |                           | N                   | /rite to                       |  |  |  |  |

|                           | register 'f'                                                                   | Data                                             | a                         | des                 | stination                      |  |  |  |  |

| Example:                  | register 'f'                                                                   | Data<br>REG,                                     | -                         | des                 |                                |  |  |  |  |

| Example:<br>Before Instru | ADDWF                                                                          |                                                  | -                         | des                 |                                |  |  |  |  |

|                           | ADDWF                                                                          |                                                  | -                         | des                 |                                |  |  |  |  |

| Before Instru<br>W        | ADDWF<br>uction<br>= 0x17<br>= 0xC2                                            |                                                  | -                         | des                 |                                |  |  |  |  |

| COMF                                               | Complem                                                                                  | ent f                                                                                                                        |                                                                  |                                                                                | CPFSEQ                                   |

|----------------------------------------------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------|

| Syntax:                                            | [label] (                                                                                | COMF f                                                                                                                       | [,d [,a]                                                         | ]                                                                              | Syntax:                                  |

| Operands:                                          | 0 ≤ f ≤ 255<br>d ∈ [0,1]<br>a ∈ [0,1]                                                    | 5                                                                                                                            |                                                                  |                                                                                | Operands:                                |

| Operation:                                         | $(\overline{f}) \rightarrow d\epsilon$                                                   | est                                                                                                                          |                                                                  |                                                                                | Operation:                               |

| Status Affected:                                   | N, Z                                                                                     |                                                                                                                              |                                                                  |                                                                                |                                          |

| Encoding:                                          | 0001                                                                                     | 11da i                                                                                                                       | fff                                                              | ffff                                                                           | Status Affecte                           |

| Description:                                       | plemented<br>stored in V<br>stored bac<br>If 'a' is '0',<br>selected, o<br>If 'a' = 1, t | nts of regis<br>d. If 'd' is 'c<br>W. If 'd' is '<br>ck in regist<br>the Acces<br>overriding t<br>hen the ba<br>as per the B | ster 'f'<br>', the i<br>1', the<br>er 'f' (c<br>s Banl<br>the BS | are com-<br>result is<br>result is<br>default).<br>k will be<br>R value.<br>be | Encoding:<br>Description:                |

| Words:                                             | 1                                                                                        |                                                                                                                              |                                                                  |                                                                                |                                          |

| Cycles:                                            | 1                                                                                        |                                                                                                                              |                                                                  |                                                                                |                                          |

| Q Cycle Activity:                                  | :                                                                                        |                                                                                                                              |                                                                  |                                                                                |                                          |

| Q1                                                 | Q2                                                                                       | Q3                                                                                                                           |                                                                  | Q4                                                                             | Words:                                   |

| Decode                                             | Read<br>register 'f'                                                                     | Process<br>Data                                                                                                              |                                                                  | /rite to<br>stination                                                          | Cycles:                                  |

| Example:                                           | COMF                                                                                     | REG, 0,                                                                                                                      | 0                                                                |                                                                                |                                          |

| Before Instru<br>REG<br>After Instruct<br>REG<br>W | = 0x13                                                                                   |                                                                                                                              |                                                                  |                                                                                | Q Cycle Acti<br>Q1<br>Decode<br>If skip: |

|                                                    |                                                                                          |                                                                                                                              |                                                                  |                                                                                | Q1<br>No<br>operation<br>If skip and fo  |

| CPF         | SEQ                       | Compare f with W, skip if f = W                                                                                                                                                                       |                                                                                                                                |                 |  |  |  |  |  |

|-------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| Synt        | ax:                       | [label]                                                                                                                                                                                               | [label] CPFSEQ f[,a]                                                                                                           |                 |  |  |  |  |  |

| Ope         | rands:                    | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                                                                                              | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                                                                                       |                 |  |  |  |  |  |

| Ope         | ration:                   | (f) – (W),<br>skip if (f) =<br>(unsigned                                                                                                                                                              | = (W)<br>  comparison)                                                                                                         | )               |  |  |  |  |  |

| Statu       | us Affected:              | None                                                                                                                                                                                                  | None                                                                                                                           |                 |  |  |  |  |  |

| Enco        | oding:                    | 0110                                                                                                                                                                                                  | 001a ff:                                                                                                                       | ff ffff         |  |  |  |  |  |

| Desc        | cription:                 | s the contents<br>boation 'f' to t<br>erforming an<br>n.<br>then the fetch<br>is discardec<br>ed instrad, m<br>instruction. If<br>ank will be sk<br>the BSR value<br>sank will be sk<br>SR value (del | he contents<br>unsigned<br>hed<br>a and a NOP<br>aking this a<br>'fa' is '0', the<br>elected,<br>ue. If 'a' = 1,<br>elected as |                 |  |  |  |  |  |

| Wor         | de.                       | 1                                                                                                                                                                                                     |                                                                                                                                | aan).           |  |  |  |  |  |

| Cycl        | es:                       |                                                                                                                                                                                                       |                                                                                                                                |                 |  |  |  |  |  |

| QC          | ycle Activity:            |                                                                                                                                                                                                       |                                                                                                                                |                 |  |  |  |  |  |

|             | Q1                        | Q2                                                                                                                                                                                                    | Q3                                                                                                                             | Q4              |  |  |  |  |  |

|             | Decode                    | Read<br>register 'f'                                                                                                                                                                                  | Process<br>Data                                                                                                                | No<br>operation |  |  |  |  |  |

| lf sk       | kip:                      |                                                                                                                                                                                                       |                                                                                                                                |                 |  |  |  |  |  |

|             | Q1                        | Q2                                                                                                                                                                                                    | Q3                                                                                                                             | Q4              |  |  |  |  |  |

|             | No                        | No                                                                                                                                                                                                    | No                                                                                                                             | No              |  |  |  |  |  |

|             | operation                 | operation                                                                                                                                                                                             | operation                                                                                                                      | operation       |  |  |  |  |  |

| If sk       |                           | -                                                                                                                                                                                                     | d instruction:                                                                                                                 |                 |  |  |  |  |  |

|             | Q1<br>No                  | Q2<br>No                                                                                                                                                                                              | Q3<br>No                                                                                                                       | Q4<br>No        |  |  |  |  |  |

|             | operation                 | operation                                                                                                                                                                                             | operation                                                                                                                      | operation       |  |  |  |  |  |

|             | No                        | No                                                                                                                                                                                                    | No                                                                                                                             | No              |  |  |  |  |  |

|             | operation                 | operation                                                                                                                                                                                             | operation                                                                                                                      | operation       |  |  |  |  |  |

| <u>Exar</u> | nple:                     | HERE<br>NEQUAL<br>EQUAL                                                                                                                                                                               | CPFSEQ REG<br>:<br>:                                                                                                           | 9, 0            |  |  |  |  |  |

|             | Before Instru<br>PC Addre |                                                                                                                                                                                                       | RE                                                                                                                             |                 |  |  |  |  |  |

|             | W<br>REG                  | = ?<br>= ?                                                                                                                                                                                            |                                                                                                                                |                 |  |  |  |  |  |

|             | After Instruct            |                                                                                                                                                                                                       |                                                                                                                                |                 |  |  |  |  |  |

| If REG      |                           | = W                                                                                                                                                                                                   |                                                                                                                                |                 |  |  |  |  |  |

|             | PC                        |                                                                                                                                                                                                       | ddress (EQUA                                                                                                                   | L)              |  |  |  |  |  |

|             | If REG<br>PC              |                                                                                                                                                                                                       |                                                                                                                                |                 |  |  |  |  |  |

| DECFSZ                       |                                | Decreme                                                                                                                               | Decrement f, skip if 0                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |                |  |  |  |

|------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------|--|--|--|

| Syntax:                      |                                | [label]                                                                                                                               | [ label ] DECFSZ f [,d [,a]]                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |                |  |  |  |

| Operands:                    |                                | 0 ≤ f ≤ 25<br>d ∈ [0,1]<br>a ∈ [0,1]                                                                                                  | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                                                                                                                                    |                          |                |  |  |  |

| Ope                          | ration:                        | (f) – 1 $\rightarrow$ skip if res                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |                |  |  |  |

| Statu                        | us Affected:                   | None                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |                |  |  |  |

| Enco                         | oding:                         | 0010                                                                                                                                  | 11da                                                                                                                                                                                                                                                                                                                                                                                                                                               | ffff                     | ffff           |  |  |  |

| Desc                         | cription:                      | decremer<br>is placed<br>is placed<br>(default).<br>If the resu<br>instruction<br>is discard<br>instruction<br>Bank will<br>the BSR v | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed back in register 'f' (default).<br>If the result is '0', the next instruction which is already fetched is discarded and a NOP is executed instead, making it a two-cycle instruction. If 'a' is '0', the Access Bank will be selected, overriding the BSR value. If 'a' = 1, then the bank will be selected as per the |                          |                |  |  |  |

| Wor                          | ds:                            | 1                                                                                                                                     | - (                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |                |  |  |  |

| Cycl                         |                                |                                                                                                                                       | cycles if s<br>a 2-word                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |                |  |  |  |

| QC                           | Cycle Activity                 | -                                                                                                                                     | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          | 04             |  |  |  |

|                              | Decode                         | Q2<br>Read                                                                                                                            | Proces                                                                                                                                                                                                                                                                                                                                                                                                                                             | s V                      | Q4<br>Vrite to |  |  |  |

|                              | Docodo                         | register 'f'                                                                                                                          | Data                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                        | stination      |  |  |  |

| lf sk                        |                                |                                                                                                                                       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                          |                |  |  |  |

|                              | Q1                             | Q2                                                                                                                                    | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          | Q4             |  |  |  |

|                              | No<br>operation                | No<br>operation                                                                                                                       | No<br>operatio                                                                                                                                                                                                                                                                                                                                                                                                                                     | on or                    | No<br>peration |  |  |  |

| lf sk                        | kip and follow                 | -                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |                |  |  |  |