Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betuilis                   |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 40MHz                                                                     |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                |

| Number of I/O              | 52                                                                        |

| Program Memory Size        | 64KB (32K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 3.25K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 16x10b                                                                |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 68-LCC (J-Lead)                                                           |

| Supplier Device Package    | 68-PLCC (24.23x24.23)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf6680-i-l |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

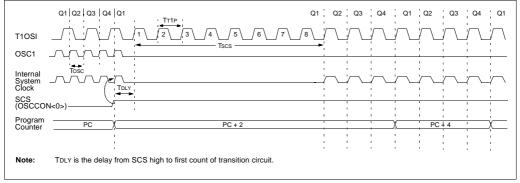

### 2.6.2 OSCILLATOR TRANSITIONS

PIC18F6585/8585/6680/8680 devices contain circuitry to prevent "glitches" when switching between oscillator sources. Essentially, the circuitry waits for eight rising edges of the clock source that the processor is switching to. This ensures that the new clock source is stable and that its pulse width will not be less than the shortest pulse width of the two clock sources.

A timing diagram, indicating the transition from the main oscillator to the Timer1 oscillator, is shown in Figure 2-8. The Timer1 oscillator is assumed to be running all the time. After the SCS0 bit is set, the processor is frozen at the next occurring Q1 cycle. After eight synchronization cycles are counted from the Timer1 oscillator, operation resumes. No additional delays are required after the synchronization cycles.

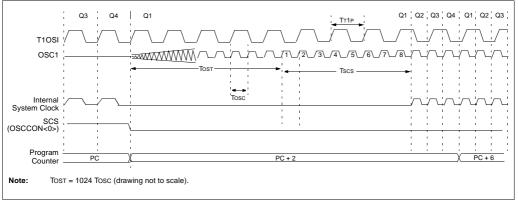

The sequence of events that takes place when switching from the Timer1 oscillator to the main oscillator will depend on the mode of the main oscillator. In addition to eight clock cycles of the main oscillator, additional delays may take place.

If the main oscillator is configured for an external crystal (HS, XT, LP), then the transition will take place after an oscillator start-up time (TOST) has occurred. A timing diagram, indicating the transition from the Timer1 oscillator to the main oscillator for HS, XT and LP modes, is shown in Figure 2-9.

#### FIGURE 2-9: TIMING FOR TRANSITION BETWEEN TIMER1 AND OSC1 (HS, XT, LP)

### 5.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

A read from program memory is executed on one byte at a time. A write to program memory is executed on blocks of 8 bytes at a time. Program memory is erased in blocks of 64 bytes at a time. A bulk erase operation cannot be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

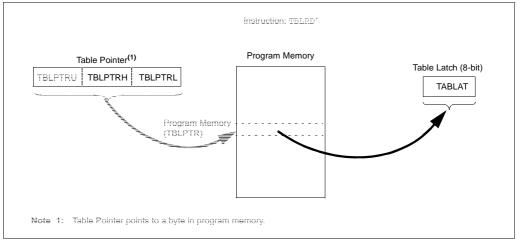

#### 5.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8-bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and places it into the data RAM space. Figure 5-1 shows the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 5.5 "Writing to Flash Program Memory"**. Figure 5-2 shows the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word aligned.

FIGURE 5-1: TABLE READ OPERATION

| REGISTER 7-1: | EECON1                                                                                                                                                                                                                                                                                                                  | REGISTER                                      | (ADDRES       | SS FA6h)      |                |              |               |              |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------|---------------|----------------|--------------|---------------|--------------|

|               | R/W-x                                                                                                                                                                                                                                                                                                                   | R/W-x                                         | U-0           | R/W-0         | R/W-x          | R/W-0        | R/S-0         | R/S-0        |

|               | EEPGD                                                                                                                                                                                                                                                                                                                   | CFGS                                          | —             | FREE          | WRERR          | WREN         | WR            | RD           |

|               | bit 7                                                                                                                                                                                                                                                                                                                   |                                               |               |               |                |              |               | bit 0        |

| bit 7         | EEPGD: Fi                                                                                                                                                                                                                                                                                                               | ash Progran                                   | n or Data EB  | EPROM Mer     | nory Select I  | oit          |               |              |

|               | 1 = Access                                                                                                                                                                                                                                                                                                              | s Flash prog<br>s data EEPR                   | ram memor     | /             |                |              |               |              |

| bit 6         | 1 = Access                                                                                                                                                                                                                                                                                                              | sh Program/<br>s configuratio<br>s Flash prog | on or calibra | tion register | S              |              |               |              |

| bit 5         | Unimpleme                                                                                                                                                                                                                                                                                                               | ented: Read                                   | <b>as</b> '0' |               |                |              |               |              |

| bit 4         | FREE: Flas                                                                                                                                                                                                                                                                                                              | sh Row Eras                                   | e Enable bit  | :             |                |              |               |              |

|               |                                                                                                                                                                                                                                                                                                                         | d by comple                                   | -             |               | by TBLPTR      | t on the nex | t WR comm     | and          |

| bit 3         | WRERR: F                                                                                                                                                                                                                                                                                                                | lash Prograi                                  | m/Data EE E   | Error Flag bi | t              |              |               |              |

|               | <ul> <li>1 = A write operation is prematurely terminated (any MCLR or any WDT Reset during self-timed programming in normal operation)</li> <li>0 = The write operation completed</li> </ul>                                                                                                                            |                                               |               |               |                |              |               | g self-timed |

|               |                                                                                                                                                                                                                                                                                                                         | When a Wi<br>tracing of th                    |               | ,             | GD or FRE      | E bits are n | ot cleared.   | This allows  |

| bit 2         | WREN: Fla                                                                                                                                                                                                                                                                                                               | sh Program                                    | /Data EE W    | rite Enable b | oit            |              |               |              |

|               |                                                                                                                                                                                                                                                                                                                         | write cycles<br>write to the                  |               |               |                |              |               |              |

| bit 1         | WR: Write                                                                                                                                                                                                                                                                                                               | Control bit                                   |               |               |                |              |               |              |

|               | <ul> <li>1 = Initiates a data EEPROM erase/write cycle or a program memory erase cycle or write cycle.<br/>(The operation is self-timed and the bit is cleared by hardware once write is complete. The WR bit can only be set (not cleared) in software.)</li> <li>0 = Write cycle to the EEPROM is complete</li> </ul> |                                               |               |               |                |              |               | -            |

| bit 0         | RD: Read (                                                                                                                                                                                                                                                                                                              | Control bit                                   |               |               |                |              |               |              |

|               | <ul> <li>1 = Initiates an EEPROM read. (Read takes one cycle. RD is cleared in hardware. The RD bit<br/>can only be set (not cleared) in software. RD bit cannot be set when EEPGD = 1.)</li> </ul>                                                                                                                     |                                               |               |               |                |              |               |              |

|               | 0 = Does n                                                                                                                                                                                                                                                                                                              | ot initiate ar                                | EEPROM        | read          |                |              |               |              |

|               | Legend:                                                                                                                                                                                                                                                                                                                 |                                               |               |               |                |              |               |              |

|               | R = Readab                                                                                                                                                                                                                                                                                                              | ble bit                                       | U = Unim      | plemented b   | it, read as '0 | ,            |               |              |

|               | W = Writab                                                                                                                                                                                                                                                                                                              | le bit                                        | S = Settat    | ole bit       |                | - n =        | - Value after | rerase       |

|               | '1' = Bit is s                                                                                                                                                                                                                                                                                                          | et                                            | '0' = Bit is  | cleared       |                | x =          | Bit is unkno  | wn           |

| STER 9-6: | PIR3: PI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ERIPHER                                                                                                                            | AL INTERI                                                                                                                             | RUPT REG                                                           | QUEST (FL                                                | AG) REGIS             | TER 3             |                     |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------|-----------------------|-------------------|---------------------|--|

|           | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0                                                                                                                              | R/W-0                                                                                                                                 | R/W-0                                                              | R/W-0                                                    | R/W-0                 | R/W-0             | R/W-0               |  |

|           | IRXIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | WAKIF                                                                                                                              | ERRIF                                                                                                                                 | TXB2IF/<br>TXBnIF                                                  | TXB1IF <sup>(1)</sup>                                    | TXB0IF <sup>(1)</sup> | RXB1IF/<br>RXBnIF | RXB0IF/<br>FIFOWMIF |  |

|           | bit 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                    |                                                                                                                                       |                                                                    |                                                          | -                     |                   | bit 0               |  |

| bit 7     | 1 = An inv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                    | ge has occu                                                                                                                           | urred on the                                                       | rupt Flag bit<br>CAN bus                                 |                       |                   |                     |  |

| bit 6     | 1 = Activit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CAN bus Act<br>ty on CAN b<br>tivity on CA                                                                                         | us has occ                                                                                                                            | up Interrupt<br>urred                                              | Flag bit                                                 |                       |                   |                     |  |

| bit 5     | 1 = An err                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                    | irred in the                                                                                                                          | -                                                                  | e (multiple so                                           | ources)               |                   |                     |  |

| bit 4     | <ul> <li>0 = No CAN module errors</li> <li>When CAN is in Mode 0:</li> <li>TXB2IF: CAN Transmit Buffer 2 Interrupt Flag bit</li> <li>1 = Transmit Buffer 2 has completed transmission of a message and may be reloaded</li> <li>0 = Transmit Buffer 2 has not completed transmission of a message</li> <li>When CAN is in Mode 1 or 2:</li> <li>TXBnIF: Any Transmit Buffer Interrupt Flag bit</li> <li>1 = One or more transmit buffers has completed transmission of a message and may be</li> </ul>                                                                                                                                  |                                                                                                                                    |                                                                                                                                       |                                                                    |                                                          |                       |                   |                     |  |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | essage was                                                                                                                         |                                                                                                                                       | 2> must be<br>d                                                    |                                                          |                       |                   |                     |  |

| bit 3     | 1 = Trans                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | mit Buffer 1                                                                                                                       | has comple                                                                                                                            |                                                                    | ag bit <sup>(1)</sup><br>ission of a m<br>nsmission of a | 0                     | nay be relo       | aded                |  |

| bit 2     | 1 = Trans                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | mit Buffer 0                                                                                                                       | has comple                                                                                                                            |                                                                    | ission of a m                                            | 0                     | nay be reloa      | aded                |  |

| bit 1     | <ul> <li>1 = Transmit Buffer 0 has completed transmission of a message and may be reloaded</li> <li>0 = Transmit Buffer 0 has not completed transmission of a message</li> <li>When CAN is in Mode 0:</li> <li><b>RXB1IF:</b> CAN Receive Buffer 1 Interrupt Flag bit</li> <li>1 = Receive Buffer 1 has received a new message</li> <li>0 = Receive Buffer 1 has not received a new message</li> <li>When CAN is in Mode 1 or 2:</li> <li><b>RXBnIF:</b> CAN Receive Buffer Interrupt Flag bit</li> <li>1 = One or more receive buffers has received a new message</li> <li>0 = No receive buffer has received a new message</li> </ul> |                                                                                                                                    |                                                                                                                                       |                                                                    |                                                          |                       |                   |                     |  |

| bit 0     | When CA<br>RXB0IF: 0<br>1 = Recei<br>0 = Recei<br>When CA<br>Unimpler<br>When CA<br>FIFOWMI<br>1 = FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <u>N is in Mode</u><br>CAN Receiv<br>ve Buffer 0<br>ve Buffer 0<br><u>N is in Mode</u><br><u>nented:</u> Re<br><u>N is in Mode</u> | <u>e 0:</u><br>ve Buffer 0 l<br>has receive<br>has not rec<br><u>e 1:</u><br>ad as '0'<br><u>e 2:</u><br>ttermark Int<br>nark is reac | Interrupt Fla<br>Ind a new me<br>eived a new<br>eirupt Flag<br>hed | g bit <sup>(1)</sup><br>essage<br>v message              |                       |                   |                     |  |

|           | R = Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | lable bit                                                                                                                          | W =                                                                                                                                   | Writable bit                                                       |                                                          | nimplemente           | d bit, read a     | as '0'              |  |

|           | - n = Valu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ie at POR                                                                                                                          | '1' =                                                                                                                                 | Bit is set                                                         | '0' = E                                                  | lit is cleared        | x = Bit           | is unknown          |  |

R = Readable bit

- n = Value at POR

| REGISTER 9-8: | PIE2: PER                                                                           |                                 | INTERRU                          | PT ENABL      | E REGIST      | ER 2    |        |        |  |

|---------------|-------------------------------------------------------------------------------------|---------------------------------|----------------------------------|---------------|---------------|---------|--------|--------|--|

|               | U-0                                                                                 | R/W-0                           | U-0                              | R/W-0         | R/W-0         | R/W-0   | R/W-0  | R/W-0  |  |

|               | —                                                                                   | CMIE                            | —                                | EEIE          | BCLIE         | LVDIE   | TMR3IE | CCP2IE |  |

|               | bit 7                                                                               |                                 |                                  |               |               |         |        | bit 0  |  |

|               |                                                                                     |                                 |                                  |               |               |         |        |        |  |

| bit 7         | Unimplem                                                                            | ented: Read                     | <b>d as</b> '0'                  |               |               |         |        |        |  |

| bit 6         | CMIE: Com                                                                           | nparator Inte                   | errupt Enable                    | e bit         |               |         |        |        |  |

|               |                                                                                     |                                 | arator interru<br>arator interru |               |               |         |        |        |  |

| bit 5         | Unimplem                                                                            | ented: Read                     | <b>d as</b> '0'                  |               |               |         |        |        |  |

| bit 4         | EEIE: Data                                                                          | EEPROM/F                        | -lash Write (                    | Operation In  | nterrupt Enab | ole bit |        |        |  |

|               |                                                                                     |                                 | operation inte<br>operation int  |               |               |         |        |        |  |

| bit 3         | BCLIE: Bu                                                                           | s Collision Ir                  | nterrupt Ena                     | uble bit      |               |         |        |        |  |

|               |                                                                                     |                                 | ollision interr                  |               |               |         |        |        |  |

| bit 2         | LVDIE: Lov                                                                          | w-Voltage De                    | etect Interru                    | ipt Enable bi | t             |         |        |        |  |

|               |                                                                                     |                                 | oltage Deteo/<br>oltage Dete     |               |               |         |        |        |  |

| bit 1         | TMR3IE: T                                                                           | MR3 Overflo                     | ow Interrupt                     | Enable bit    |               |         |        |        |  |

|               | 1 = Enables the TMR3 overflow interrupt<br>0 = Disables the TMR3 overflow interrupt |                                 |                                  |               |               |         |        |        |  |

| bit 0         | CCP2IE: C                                                                           | CP2 Interru                     | pt Enable bi                     | t             |               |         |        |        |  |

|               | 1 = Enables the CCP2 interrupt                                                      |                                 |                                  |               |               |         |        |        |  |

|               | 0 = Disable                                                                         | 0 = Disables the CCP2 interrupt |                                  |               |               |         |        |        |  |

|               |                                                                                     |                                 |                                  |               |               |         |        |        |  |

|               | Legend:                                                                             |                                 |                                  |               |               |         |        |        |  |

W = Writable bit

'1' = Bit is set

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

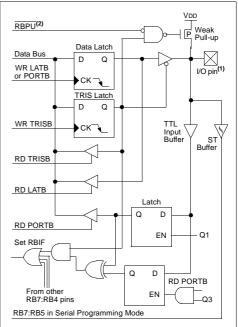

### 10.2 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register read and write the latched output value for PORTB.

EXAMPLE 10-2: INITIALIZING PORTB

| CLRF  | PORTB | ; Initialize PORTB by<br>; clearing output |

|-------|-------|--------------------------------------------|

|       |       | ; data latches                             |

| CLRF  | LATB  | ; Alternate method                         |

|       |       | ; to clear output                          |

|       |       | ; data latches                             |

| MOVLW | 0CFh  | ; Value used to                            |

|       |       | ; initialize data                          |

|       |       | ; direction                                |

| MOVWF | TRISB | ; Set RB<3:0> as inputs                    |

|       |       | ; RB<5:4> as outputs                       |

|       |       | ; RB<7:6> as inputs                        |

|       |       |                                            |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

| Note: | On a Power-on Reset, these pins are |

|-------|-------------------------------------|

|       | configured as digital inputs.       |

Four of the PORTB pins (RB3:RB0) are the external interrupt pins, INT3 through INT0. In order to use these pins as external interrupts, the corresponding TRISB bit must be set to '1'.

The other four PORTB pins (RB7:RB4) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB7:RB4 pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB7:RB4) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB7:RB4 are OR'ed together to generate the RB port change interrupt with flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- Any read or write of PORTB (except with the MOVFF instruction). This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit, RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

For PIC18FXX85 devices, RB3 can be configured by the configuration bit, CCP2MX, as the alternate peripheral pin for the CCP2 module. This is only available when the device is configured in Microprocessor, Microprocessor with Boot Block, or Extended Microcontroller Operating modes.

The RB5 pin is used as the LVP programming pin. When the LVP configuration bit is programmed, this pin loses the I/O function and becomes a programming test function.

Note: When LVP is enabled, the weak pull-up on RB5 is disabled.

#### FIGURE 10-5: BLOCK DIAGRAM OF RB7:RB4 PINS

Note 1:

I/O pins have diode protection to VDD and VSS.

2:

To enable weak pull-ups, set the appropriate TRIS bit(s) and clear the RBPU bit (INTCON2<7>).

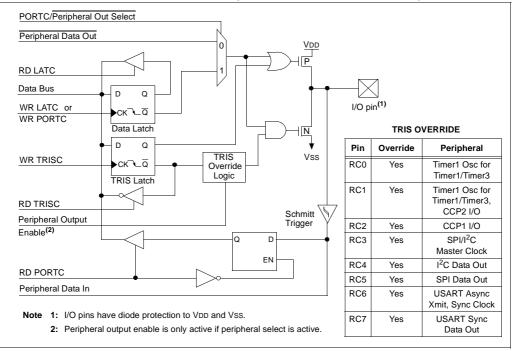

### 10.3 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding data direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISC bit (= 0)will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (Table 10-5). PORTC pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input. The user should refer to the corresponding peripheral section for the correct TRIS bit settings.

Note: On a Power-on Reset, these pins are configured as digital inputs.

The pin override value is not loaded into the TRIS register. This allows read-modify-write of the TRIS register without concern due to peripheral overrides.

RC1 is normally configured by configuration bit, CCP2MX, as the default peripheral pin of the CCP2 module (default/erased state, CCP2MX = 1).

EXAMPLE 10-3: INITIALIZING PORTC

| CLRF  | PORTC | ; Initialize PORTC by<br>; clearing output<br>: data latches |

|-------|-------|--------------------------------------------------------------|

| a     |       |                                                              |

| CLRF  | LATC  | ; Alternate method                                           |

|       |       | ; to clear output                                            |

|       |       | ; data latches                                               |

| MOVLW | 0CFh  | ; Value used to                                              |

|       |       | ; initialize data                                            |

|       |       | ; direction                                                  |

| MOVWF | TRISC | ; Set RC<3:0> as inputs                                      |

|       |       | ; RC<5:4> as outputs                                         |

|       |       | ; RC<7:6> as inputs                                          |

|       |       |                                                              |

### FIGURE 10-8: PORTC BLOCK DIAGRAM (PERIPHERAL OUTPUT OVERRIDE)

| Name    | Bit#  | Buffer Type | Function                                                                             |

|---------|-------|-------------|--------------------------------------------------------------------------------------|

| RJ0/ALE | bit 0 | ST          | Input/output port pin or address latch enable control for external memory interface. |

| RJ1/OE  | bit 1 | ST          | Input/output port pin or output enable control for external memory interface.        |

| RJ2/WRL | bit 2 | ST          | Input/output port pin or write low byte control for external memory interface.       |

| RJ3/WRH | bit 3 | ST          | Input/output port pin or write high byte control for external memory interface.      |

| RJ4/BA0 | bit 4 | ST          | Input/output port pin or byte address 0 control for external memory interface.       |

| RJ5/CE  | bit 5 | ST          | Input/output port pin or external memory chip enable.                                |

| RJ6/LB  | bit 6 | ST          | Input/output port pin or lower byte select control for external memory interface.    |

| RJ7/UB  | bit 7 | ST          | Input/output port pin or upper byte select control for external memory interface.    |

### TABLE 10-17: PORTJ FUNCTIONS

Legend: ST = Schmitt Trigger input

### TABLE 10-18: SUMMARY OF REGISTERS ASSOCIATED WITH PORTJ

| Name  | Bit 7                                     | Bit 6                     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------|-------------------------------------------|---------------------------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| PORTJ | Read PORTJ pin/Write PORTJ Data Latch     |                           |       |       |       |       |       |       | xxxx xxxx            | uuuu uuuu                       |

| LATJ  | LATJ Da                                   | LATJ Data Output Register |       |       |       |       |       |       |                      | uuuu uuuu                       |

| TRISJ | Data Direction Control Register for PORTJ |                           |       |       |       |       |       |       | 1111 1111            | 1111 1111                       |

**Legend:** x = unknown, u = unchanged

'0' = Bit is cleared

x = Bit is unknown

| REGISTER 10-1: | PSPCON                                                                                                                                                                                                                  | REGISTER                                                                                                                                                                          | ર               |              |          |           |                |       |  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|----------|-----------|----------------|-------|--|--|

|                | R-0                                                                                                                                                                                                                     | R-0                                                                                                                                                                               | R/W-0           | R/W-0        | U-0      | U-0       | U-0            | U-0   |  |  |

|                | IBF                                                                                                                                                                                                                     | OBF                                                                                                                                                                               | IBOV            | PSPMODE      | _        | —         | —              | _     |  |  |

|                | bit 7                                                                                                                                                                                                                   |                                                                                                                                                                                   |                 |              |          |           |                | bit 0 |  |  |

| bit 7          | 1 = A data                                                                                                                                                                                                              | <ul> <li>IBF: Input Buffer Full Status bit</li> <li>1 = A data byte has been received and is waiting to be read by the CPU</li> <li>0 = No data byte has been received</li> </ul> |                 |              |          |           |                |       |  |  |

| bit 6          | <b>OBF:</b> Output Buffer Full Status bit<br>1 = The output buffer still holds a previously written data byte<br>0 = The output buffer has been read                                                                    |                                                                                                                                                                                   |                 |              |          |           |                |       |  |  |

| bit 5          | <ul> <li><b>IBOV:</b> Input Buffer Overflow Detect bit</li> <li>1 = A write occurred when a previously input data byte has not been read<br/>(must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul> |                                                                                                                                                                                   |                 |              |          |           |                |       |  |  |

| bit 4          | <b>PSPMODE</b> : Parallel Slave Port Mode Select bit<br>1 = Parallel Slave Port mode<br>0 = General Purpose I/O mode                                                                                                    |                                                                                                                                                                                   |                 |              |          |           |                |       |  |  |

| bit 3-0        | Unimplem                                                                                                                                                                                                                | ented: Rea                                                                                                                                                                        | <b>d as</b> '0' |              |          |           |                |       |  |  |

|                | Legend:                                                                                                                                                                                                                 |                                                                                                                                                                                   |                 |              |          |           |                |       |  |  |

|                | R = Reada                                                                                                                                                                                                               | ble bit                                                                                                                                                                           | W = V           | Vritable bit | U = Unim | plemented | bit, read as ' | 0'    |  |  |

| FIGURE 10-29: | PARALLEL SLAVE PORT WRITE WAVEFORMS |

|---------------|-------------------------------------|

|---------------|-------------------------------------|

- n = Value at POR

|            | Q1   Q2   Q3   Q4 Q1   Q2   Q3 | Q4          | Q1   Q2   Q3   Q4 |

|------------|--------------------------------|-------------|-------------------|

|            |                                |             | 1<br>1<br>1<br>1  |

| WR         |                                | /<br>/<br>  | 1<br>1<br>1       |

| RD         |                                | 1<br>       |                   |

| PORTD<7:0> |                                | 1<br>1<br>1 | 1<br>1<br>1<br>1  |

| IBF        |                                | /           | ,<br> <br> <br>   |

| OBF        |                                | 1<br>1<br>1 | 1<br>1<br>1<br>1  |

| PSPIF      |                                | /           | 1                 |

|            |                                |             |                   |

'1' = Bit is set

| GISTER 23-4: | COMSTAT:                                                                                             | COMMUNIC                                                                         | ATION S    | TATUS RE    | GISTER   |             |              |             |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------|-------------|----------|-------------|--------------|-------------|--|--|--|--|

|              | R/C-0                                                                                                | R/C-0                                                                            | R-0        | R-0         | R-0      | R-0         | R-0          | R-0         |  |  |  |  |

| Mode 0       | RXB00VFL                                                                                             | RXB10VFL                                                                         | ТХВО       | TXBP        | RXBP     | TXWARN      | RXWARN       | EWARN       |  |  |  |  |

|              | U-0                                                                                                  | R/C-0                                                                            | R-0        | R-0         | R-0      | R-0         | R-0          | R-0         |  |  |  |  |

| Mode 1       | <u> </u>                                                                                             | RXBnOVFL                                                                         | TXB0       | TXBP        | RXBP     | TXWARN      | RXWARN       | EWARN       |  |  |  |  |

|              |                                                                                                      | TO BIOTIE                                                                        | in Bo      | 17(B)       | TOUDI    | 17(17) 444  | 10,000,000   | 210,000     |  |  |  |  |

| Mode 2       | R/C-0                                                                                                | R/C-0                                                                            | R-0        | R-0         | R-0      | R-0         | R-0          | R-0         |  |  |  |  |

|              | FIFOEMPTY                                                                                            | RXBnOVFL                                                                         | ТХВО       | TXBP        | RXBP     | TXWARN      | RXWARN       | EWARN       |  |  |  |  |

|              | bit 7                                                                                                |                                                                                  |            |             |          |             |              | bit 0       |  |  |  |  |

| bit 7        | Mode 0 <sup>.</sup>                                                                                  |                                                                                  |            |             |          |             |              |             |  |  |  |  |

| bit /        |                                                                                                      | Mode 0:<br>RXB00VFL: Receive Buffer 0 Overflow bit                               |            |             |          |             |              |             |  |  |  |  |

|              | 1 = Receive Buffer 0 overflowed                                                                      |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              | 0 = Receive Buffer 0 has not overflowed                                                              |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              | Mode 1:                                                                                              |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              | Unimplemented: Read as '0'                                                                           |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              | Mode 2:                                                                                              |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              | FIFOEMPTY: FIFO Not Empty bit                                                                        |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              | <ol> <li>= Receive FIFO is not empty</li> <li>= Receive FIFO is empty</li> </ol>                     |                                                                                  |            |             |          |             |              |             |  |  |  |  |

| bit 6        | Mode 0:                                                                                              |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              | RXB10VFL: Receive Buffer 1 Overflow bit                                                              |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              | 1 = Receive Buffer 1 overflowed                                                                      |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              | 0 = Receive Buffer 1 has not overflowed<br>Mode 1 2                                                  |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              | Mode 1, 2:<br>RXBnOVFL: Receive Buffer Overflow bit                                                  |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              | <b>RXBnOVFL:</b> Receive Buffer Overflow bit<br>1 = Receive buffer has overflowed                    |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed</li> </ul> |                                                                                  |            |             |          |             |              |             |  |  |  |  |

| bit 5        | <b>TXBO:</b> Transmitter Bus-Off bit                                                                 |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              | 1 = Transmit error counter > 255                                                                     |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              | $0 = \text{Transmit error counter} \le 255$                                                          |                                                                                  |            |             |          |             |              |             |  |  |  |  |

| bit 4        | TXBP: Transmitter Bus Passive bit                                                                    |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              |                                                                                                      | 1 = Transmit error counter > 127                                                 |            |             |          |             |              |             |  |  |  |  |

| bit 3        |                                                                                                      | 0 = Transmit error counter ≤ 127<br>RXBP: Receiver Bus Passive bit               |            |             |          |             |              |             |  |  |  |  |

| bit 5        |                                                                                                      | error counter >                                                                  |            |             |          |             |              |             |  |  |  |  |

|              |                                                                                                      | error counter ≤                                                                  |            |             |          |             |              |             |  |  |  |  |

| bit 2        | TXWARN: T                                                                                            | ransmitter War                                                                   | ning bit   |             |          |             |              |             |  |  |  |  |

|              |                                                                                                      | ansmit error co                                                                  |            | 5           |          |             |              |             |  |  |  |  |

|              |                                                                                                      | error counter                                                                    |            |             |          |             |              |             |  |  |  |  |

| bit 1        |                                                                                                      | Receiver Warni                                                                   | -          |             |          |             |              |             |  |  |  |  |

|              |                                                                                                      | $1 = 127 \ge$ Receive error counter > 95<br>$0 =$ Receive error counter $\le 95$ |            |             |          |             |              |             |  |  |  |  |

| bit 0        | 0 = Receive error counter ≤ 95<br>EWARN: Error Warning bit                                           |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              |                                                                                                      | lag of the RXV                                                                   |            | TXWARN bi   | ts.      |             |              |             |  |  |  |  |

|              |                                                                                                      | VARN or the T<br>he RXWARN of                                                    |            |             | e set    |             |              |             |  |  |  |  |

|              | Legend:                                                                                              |                                                                                  |            |             |          |             |              |             |  |  |  |  |

|              | C = Clearabl                                                                                         | e bit R = Re                                                                     | adable bit | t W = Writa | able bit | U = Unimple | emented bit, | read as '0' |  |  |  |  |

|              |                                                                                                      |                                                                                  |            | (0) D'( )-  |          |             | .,           | -           |  |  |  |  |

#### **REGISTER 23** . ~

- n = Value at POR '1' = Bit is set

| REGISTER 23-11: | TXBnDLC                                                      | : TRANSM                                                       | IT BUFFEF       | R n DATA L  | ENGTH CO     | DDE REGI   | STERS[0≤     | n≤2]  |  |  |

|-----------------|--------------------------------------------------------------|----------------------------------------------------------------|-----------------|-------------|--------------|------------|--------------|-------|--|--|

|                 | U-0                                                          | R/W-x                                                          | U-0             | U-0         | R/W-x        | R/W-x      | R/W-x        | R/W-x |  |  |

|                 | _                                                            | TXRTR                                                          | —               | —           | DLC3         | DLC2       | DLC1         | DLC0  |  |  |

|                 | bit 7                                                        |                                                                |                 |             |              |            |              | bit 0 |  |  |

|                 |                                                              |                                                                |                 |             |              |            |              |       |  |  |

| bit 7           | Unimpleme                                                    | ented: Read                                                    | <b>d as</b> '0' |             |              |            |              |       |  |  |

| bit 6           | TXRTR: Tra                                                   | ansmit Rem                                                     | ote Frame T     | ransmissior | n Request bi | t          |              |       |  |  |

|                 | 1 = Transmitted message will have TXRTR bit set              |                                                                |                 |             |              |            |              |       |  |  |

|                 | 0 = Transmitted message will have TXRTR bit cleared          |                                                                |                 |             |              |            |              |       |  |  |

| bit 5-4         | Unimpleme                                                    | Unimplemented: Read as '0'<br>DLC3:DLC0: Data Length Code bits |                 |             |              |            |              |       |  |  |

| bit 3-0         | DLC3:DLC                                                     |                                                                |                 |             |              |            |              |       |  |  |

|                 | 1111 = Reserved                                              |                                                                |                 |             |              |            |              |       |  |  |

|                 | 1110 = Res                                                   | served                                                         |                 |             |              |            |              |       |  |  |

|                 | 1101 = Reserved                                              |                                                                |                 |             |              |            |              |       |  |  |

|                 | 1100 = Reserved                                              |                                                                |                 |             |              |            |              |       |  |  |

|                 | 1011 = Res                                                   |                                                                |                 |             |              |            |              |       |  |  |

|                 | 1010 = Res                                                   |                                                                |                 |             |              |            |              |       |  |  |

|                 | 1001 = Res                                                   |                                                                |                 |             |              |            |              |       |  |  |

|                 |                                                              | a length = 8                                                   |                 |             |              |            |              |       |  |  |

|                 |                                                              | a length = 7                                                   |                 |             |              |            |              |       |  |  |

|                 |                                                              | a length = 6                                                   |                 |             |              |            |              |       |  |  |

|                 | 0101 = Data length = 5 bytes                                 |                                                                |                 |             |              |            |              |       |  |  |

|                 | 0100 = Data length = 4 bytes                                 |                                                                |                 |             |              |            |              |       |  |  |

|                 | 0011 = Data length = 3 bytes                                 |                                                                |                 |             |              |            |              |       |  |  |

|                 | 0010 = Data length = 2 bytes<br>0001 = Data length = 1 bytes |                                                                |                 |             |              |            |              |       |  |  |

|                 |                                                              | ta length = $0$                                                |                 |             |              |            |              |       |  |  |

|                 | 0000 <b>– Da</b> i                                           | a ierigtii – t                                                 | 09183           |             |              |            |              |       |  |  |

|                 | Legend:                                                      |                                                                |                 |             |              |            |              |       |  |  |

|                 | R = Reada                                                    | ble bit                                                        | W = Writa       | ble bit     | U = Unin     | nplemented | bit, read as | '0'   |  |  |

### REGISTER 23-12: TXERRCNT: TRANSMIT ERROR COUNT REGISTER

'1' = Bit is set

- n = Value at POR