Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                 |

| Number of I/O              | 68                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 3.25K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                  |

| Data Converters            | A/D 16x10b                                                                 |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

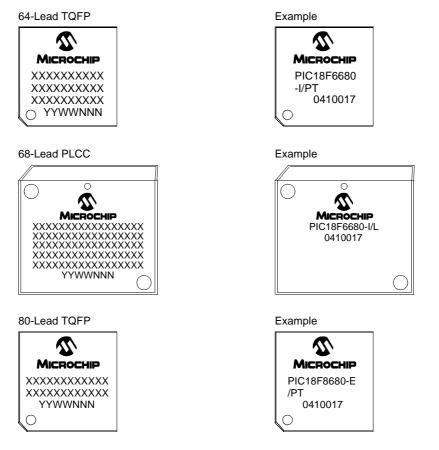

| Package / Case             | 80-TQFP                                                                    |

| Supplier Device Package    | 80-TQFP (12x12)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf8680-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

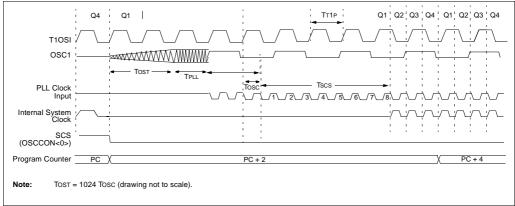

If the main oscillator is configured for HS mode with PLL active, an oscillator start-up time (TOST) plus an additional PLL time-out (TPLL) will occur. The PLL time-out is typically 2 ms and allows the PLL to lock to the main oscillator frequency. A timing diagram, indicating the transition from the Timer1 oscillator to the main oscillator for HS-PLL mode, is shown in Figure 2-10.

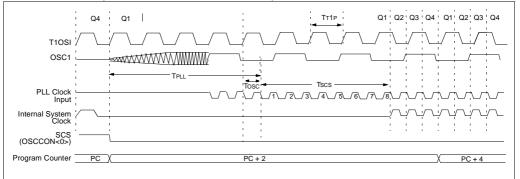

If the main oscillator is configured for EC mode with PLL active, only the PLL time-out (TPLL) will occur. The PLL time-out is typically 2 ms and allows the PLL to lock to the main oscillator frequency. A timing diagram, indicating the transition from the Timer1 oscillator to the main oscillator for EC with PLL active, is shown in Figure 2-11.

#### FIGURE 2-11: TIMING FOR TRANSITION BETWEEN TIMER1 AND OSC1 (EC WITH PLL ACTIVE, SCS1 = 1)

| TADLE 4-3   | ABLE 4-3. REGISTER FILE SOMMART (CONTINUED) |         |         |         |         |         |         |          |                      |                     |  |  |  |

|-------------|---------------------------------------------|---------|---------|---------|---------|---------|---------|----------|----------------------|---------------------|--|--|--|

| File Name   | Bit 7                                       | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0    | Value on<br>POR, BOR | Details<br>on page: |  |  |  |

| RXFBCON7(7) | F15BP_3                                     | F15BP_2 | F15BP_1 | F15BP_0 | F14BP_3 | F14BP_2 | F14BP_1 | F14BP_01 | 0000 0000            | 47, 230             |  |  |  |

| RXFBCON6(7) | F13BP_3                                     | F13BP_2 | F13BP_1 | F13BP_0 | F12BP_3 | F12BP_2 | F12BP_1 | F12BP_01 | 0000 0000            | 47, 230             |  |  |  |

| RXFBCON5(7) | F11BP_3                                     | F11BP_2 | F11BP_1 | F11BP_0 | F10BP_3 | F10BP_2 | F10BP_1 | F10BP_01 | 0000 0000            | 47, 230             |  |  |  |

| RXFBCON4(7) | F9BP_3                                      | F9BP_2  | F9BP_1  | F9BP_0  | F8BP_3  | F8BP_2  | F8BP_1  | F8BP_01  | 0000 0000            | 47, 230             |  |  |  |

| RXFBCON3(7) | F7BP_3                                      | F7BP_2  | F7BP_1  | F7BP_0  | F6BP_3  | F6BP_2  | F6BP_1  | F6BP_01  | 0000 0000            | 47, 230             |  |  |  |

| RXFBCON2(7) | F5BP_3                                      | F5BP_2  | F5BP_1  | F5BP_0  | F4BP_3  | F4BP_2  | F4BP_1  | F4BP_01  | 0000 0000            | 47, 230             |  |  |  |

| RXFBCON1(7) | F3BP_3                                      | F3BP_2  | F3BP_1  | F3BP_0  | F2BP_3  | F2BP_2  | F2BP_1  | F2BP_01  | 0000 0000            | 47, 230             |  |  |  |

| RXFBCON0(7) | F1BP_3                                      | F1BP_2  | F1BP_1  | F1BP_0  | F0BP_3  | F0BP_2  | F0BP_1  | F0BP_01  | 0000 0000            | 47, 230             |  |  |  |

#### TABLE 4-3: REGISTER FILE SUMMARY (CONTINUED)

$\label{eq:legend: Legend: Legend: u = unchanged, -= unimplemented, q = value depends on condition$

Note 1: RA6 and associated bits are configured as port pins in RCIO and ECIO Oscillator mode only and read 'o' in all other oscillator modes.

2: Bit 21 of the TBLPTRU allows access to the device configuration bits.

3: These registers are unused on PIC18F6X80 devices; always maintain these clear.

4: These bits have multiple functions depending on the CAN module mode selection.

5: Meaning of this register depends on whether this buffer is configured as transmit or receive.

6: RG5 is available as an input when MCLR is disabled.

7: This register reads all '0's until the ECAN module is set up in Mode 1 or Mode 2.

If the device fetches or accesses external memory while EBDIS = 1, the pins will switch to external bus. If the EBDIS bit is set by a program executing from external memory, the action of setting the bit will be delayed until the program branches into the internal memory. At that time, the pins will change from external bus to I/O ports.

When the device is executing out of internal memory (with EBDIS = 0) in Microprocessor with Boot Block mode or Extended Microcontroller mode, the control signals will be in inactive. They will go to a state where the AD<15:0>, A<19:16> are tri-state; the  $\overrightarrow{OE}$ ,  $\overrightarrow{WRH}$ ,  $\overrightarrow{WRL}$ ,  $\overrightarrow{UB}$  and  $\overrightarrow{LB}$  signals are '1'; and ALE and BA0 are '0'.

| Name     | Port  | Bit   | Function                                                          |

|----------|-------|-------|-------------------------------------------------------------------|

| RD0/AD0  | PORTD | bit 0 | Input/Output or System Bus Address bit 0 or Data bit 0            |

| RD1/AD1  | PORTD | bit 1 | Input/Output or System Bus Address bit 1 or Data bit 1            |

| RD2/AD2  | PORTD | bit 2 | Input/Output or System Bus Address bit 2 or Data bit 2            |

| RD3/AD3  | PORTD | bit 3 | Input/Output or System Bus Address bit 3 or Data bit 3            |

| RD4/AD4  | PORTD | bit 4 | Input/Output or System Bus Address bit 4 or Data bit 4            |

| RD5/AD5  | PORTD | bit 5 | Input/Output or System Bus Address bit 5 or Data bit 5            |

| RD6/AD6  | PORTD | bit 6 | Input/Output or System Bus Address bit 6 or Data bit 6            |

| RD7/AD7  | PORTD | bit 7 | Input/Output or System Bus Address bit 7 or Data bit 7            |

| RE0/AD8  | PORTE | bit 0 | Input/Output or System Bus Address bit 8 or Data bit 8            |

| RE1/AD9  | PORTE | bit 1 | Input/Output or System Bus Address bit 9 or Data bit 9            |

| RE2/AD10 | PORTE | bit 2 | Input/Output or System Bus Address bit 10 or Data bit 10          |

| RE3/AD11 | PORTE | bit 3 | Input/Output or System Bus Address bit 11 or Data bit 11          |

| RE4/AD12 | PORTE | bit 4 | Input/Output or System Bus Address bit 12 or Data bit 12          |

| RE5/AD13 | PORTE | bit 5 | Input/Output or System Bus Address bit 13 or Data bit 13          |

| RE6/AD14 | PORTE | bit 6 | Input/Output or System Bus Address bit 14 or Data bit 14          |

| RE7/AD15 | PORTE | bit 7 | Input/Output or System Bus Address bit 15 or Data bit 15          |

| RH0/A16  | PORTH | bit 0 | Input/Output or System Bus Address bit 16                         |

| RH1/A17  | PORTH | bit 1 | Input/Output or System Bus Address bit 17                         |

| RH2/A18  | PORTH | bit 2 | Input/Output or System Bus Address bit 18                         |

| RH3/A19  | PORTH | bit 3 | Input/Output or System Bus Address bit 19                         |

| RJ0/ALE  | PORTJ | bit 0 | Input/Output or System Bus Address Latch Enable (ALE) Control pin |

| RJ1/OE   | PORTJ | bit 1 | Input/Output or System Bus Output Enable (OE) Control pin         |

| RJ2/WRL  | PORTJ | bit 2 | Input/Output or System Bus Write Low (WRL) Control pin            |

| RJ3/WRH  | PORTJ | bit 3 | Input/Output or System Bus Write High (WRH) Control pin           |

| RJ4/BA0  | PORTJ | bit 4 | Input/Output or System Bus Byte Address bit 0                     |

| RJ5/CE   | PORTJ | bit 5 | Input/Output or Chip Enable                                       |

| RJ6/LB   | PORTJ | bit 6 | Input/Output or System Bus Lower Byte Enable (IB) Control pin     |

| RJ7/UB   | PORTJ | bit 7 | Input/Output or System Bus Upper Byte Enable (UB) Control pin     |

TABLE 6-1:

PIC18F8X8X EXTERNAL BUS – I/O PORT FUNCTIONS

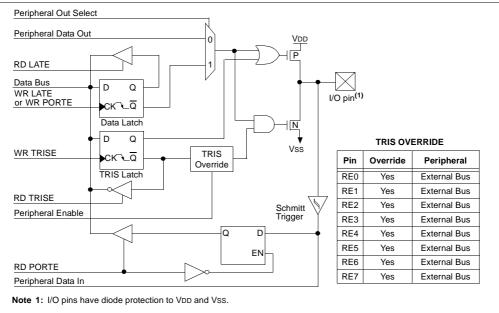

#### FIGURE 10-11: PORTE BLOCK DIAGRAM IN I/O MODE

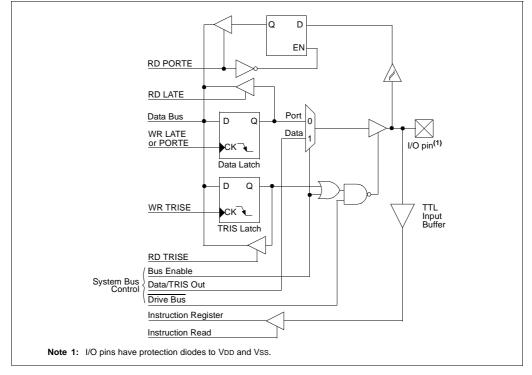

#### FIGURE 10-12: PORTE BLOCK DIAGRAM IN SYSTEM BUS MODE (PIC18F8X8X ONLY)

© 2003-2013 Microchip Technology Inc.

#### 17.4.4 CLOCK STRETCHING

Both 7- and 10-bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit (SSPCON2<0>) allows clock stretching to be enabled during receives. Setting SEN will cause the SCL pin to be held low at the end of each data receive sequence.

#### 17.4.4.1 Clock Stretching for 7-bit Slave Receive Mode (SEN = 1)

In 7-bit Slave Receive mode, on the falling edge of the ninth clock at the end of the ACK sequence if the BF bit is set, the CKP bit in the SSPCON1 register is automatically cleared, forcing the SCL output to be held low. The CKP being cleared to 'o' will assert the SCL line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the SSPBUF before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring (see Figure 17-13).

- Note 1: If the user reads the contents of the SSPBUF before the falling edge of the ninth clock, thus clearing the BF bit, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

#### 17.4.4.2 Clock Stretching for 10-bit Slave Receive Mode (SEN = 1)

In 10-bit Slave Receive mode, during the address sequence, clock stretching automatically takes place but CKP is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address and following the receive of the second byte of the 10-bit address with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPADD. Clock stretching will occur on each data receive sequence as described in 7-bit mode.

Note: If the user polls the UA bit and clears it by updating the SSPADD register before the falling edge of the ninth clock occurs and if the user hasn't cleared the BF bit by reading the SSPBUF register before that time, then the CKP bit will still NOT be asserted low. Clock stretching on the basis of the state of the BF bit only occurs during a data sequence, not an address sequence.

#### 17.4.4.3 Clock Stretching for 7-bit Slave Transmit Mode

7-bit Slave Transmit mode implements clock stretching by clearing the CKP bit after the falling edge of the ninth clock, if the BF bit is clear. This occurs regardless of the state of the SEN bit.

The user's ISR must set the CKP bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the SSPBUF before the master device can initiate another transmit sequence (see Figure 17-9).

- Note 1: If the user loads the contents of SSPBUF, setting the BF bit before the falling edge of the ninth clock, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software regardless of the state of the BF bit.

#### 17.4.4.4 Clock Stretching for 10-bit Slave Transmit Mode

In 10-bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-bit Slave Receive mode. The first two addresses are followed by a third address sequence which contains the high order bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode, and clock stretching is controlled by the BF flag as in 7-bit Slave Transmit mode (see Figure 17-11).

| =R 18-3: | BAUDCON                         | I: BAUD F                    | RATE CON                                      | TROL REC     | SISTER                 |              |              |               |

|----------|---------------------------------|------------------------------|-----------------------------------------------|--------------|------------------------|--------------|--------------|---------------|

|          | U-0                             | R-1                          | U-0                                           | R/W-0        | R/W-0                  | U-0          | R/W-0        | R/W-0         |

|          | _                               | RCIDL                        | —                                             | SCKP         | BRG16                  | —            | WUE          | ABDEN         |

|          | bit 7                           |                              |                                               |              |                        |              |              | bit 0         |

| bit 7    | Unimplem                        | antad: Poo                   | d as 'o'                                      |              |                        |              |              |               |

| bit 6    | -                               |                              |                                               | tuo hit      |                        |              |              |               |

| DILO     | 1 = Receive                     | •                            | ation Idle Sta                                | ilus di      |                        |              |              |               |

|          | 1 = Receive<br>0 = Receive      |                              |                                               |              |                        |              |              |               |

| bit 5    | Unimplem                        | ented: Rea                   | <b>d as</b> '0'                               |              |                        |              |              |               |

| bit 4    | SCKP: Syn                       | chronous C                   | lock Polarity                                 | / Select bit |                        |              |              |               |

|          | Asynchrono<br>Unused in t       |                              |                                               |              |                        |              |              |               |

|          | Synchrono                       |                              |                                               |              |                        |              |              |               |

|          |                                 |                              | (CK) is a hig<br>(CK) is a lov                | ,            |                        |              |              |               |

| bit 3    | BRG16: 16                       | -bit Baud R                  | ate Register                                  | Enable bit   |                        |              |              |               |

|          |                                 |                              | Generator – S<br>enerator – S                 |              | d SPBRG<br>(Compatible | mode), SPE   | BRGH value   | ignored       |

| bit 2    | Unimplem                        | ented: Rea                   | <b>d as</b> '0'                               |              |                        |              |              |               |

| bit 1    | WUE: Wak                        | e-up Enable                  | e bit                                         |              |                        |              |              |               |

|          | in hard                         | T will contin<br>ware on fol | ue to sample<br>lowing rising<br>ed or rising | edge         | – interrupt ge         | enerated on  | falling edge | ; bit cleared |

|          | <u>Synchrono</u><br>Unused in t |                              |                                               |              |                        |              |              |               |

| bit 0    | ABDEN: A                        | uto-Baud De                  | etect Enable                                  | bit          |                        |              |              |               |

|          | (55h);                          | e baud rate<br>cleared in h  | measureme<br>ardware upo<br>ement disab       | on completic |                        | – requires r | eception of  | a sync field  |

|          | Synchrono                       | us mode:                     |                                               |              |                        |              |              |               |

|          | Unused in t                     | his mode.                    |                                               |              |                        |              |              |               |

|          |                                 |                              |                                               |              |                        |              |              |               |

|          | Legend:                         |                              |                                               |              |                        |              |              |               |

#### REGISTER 18-3: BAUDCON: BAUD RATE CONTROL REGISTER

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|              | SYNC = 0, BRGH = 0, BRG16 = 0 |            |                             |                       |            |                             |                       |            |                             |                       |            |                             |

|--------------|-------------------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD<br>RATE | Fosc = 40.000 MHz             |            |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |

| (K)          | Actual<br>Rate<br>(K)         | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3          | -                             | _          | _                           | _                     | _          | _                           |                       | _          | _                           | _                     | _          | _                           |

| 1.2          | —                             | —          | —                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16       | 129                         | 1201                  | -0.16      | 103                         |

| 2.4          | 2.441                         | 1.73       | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16       | 64                          | 2403                  | -0.16      | 51                          |

| 9.6          | 9.615                         | 0.16       | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73       | 15                          | 9615                  | -0.16      | 12                          |

| 19.2         | 19.531                        | 1.73       | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73       | 7                           | _                     | _          | _                           |

| 57.6         | 56.818                        | -1.36      | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58      | 2                           | _                     | _          | —                           |

| 115.2        | 125.000                       | 8.51       | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18     | 1                           | _                     | _          | _                           |

| TABLE 18-3: | BAUD RATES FOR ASYNCHRONOUS MODES |

|-------------|-----------------------------------|

|             |                                   |

|             |                       | <b>SYNC</b> = 0, <b>BRGH</b> = 0, <b>BRG16</b> = 0 |                             |                       |            |                             |                       |            |                             |  |  |  |  |

|-------------|-----------------------|----------------------------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|--|--|--|--|

| BAUD        | Fos                   | c = 4.000                                          | MHz                         | Fos                   | c = 2.000  | MHz                         | Fos                   | c = 1.000  | MHz                         |  |  |  |  |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error                                         | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |  |  |  |  |

| 0.3         | 0.300                 | 0.16                                               | 207                         | 300                   | -0.16      | 103                         | 300                   | -0.16      | 51                          |  |  |  |  |

| 1.2         | 1.202                 | 0.16                                               | 51                          | 1201                  | -0.16      | 25                          | 1201                  | -0.16      | 12                          |  |  |  |  |

| 2.4         | 2.404                 | 0.16                                               | 25                          | 2403                  | -0.16      | 12                          | —                     | _          | —                           |  |  |  |  |

| 9.6         | 8.929                 | -6.99                                              | 6                           | _                     | _          | _                           | _                     | _          | _                           |  |  |  |  |

| 19.2        | 20.833                | 8.51                                               | 2                           | —                     | _          | _                           | _                     | _          | _                           |  |  |  |  |

| 57.6        | 62.500                | 8.51                                               | 0                           | —                     | _          | _                           | _                     | _          | _                           |  |  |  |  |

| 115.2       | 62.500                | -45.75                                             | 0                           | _                     | _          | _                           | _                     | _          | _                           |  |  |  |  |

|              | SYNC = 0, BRGH = 1, BRG16 = 0 |                   |                             |                       |                   |                             |                       |                   |     |                       |                  |                             |  |

|--------------|-------------------------------|-------------------|-----------------------------|-----------------------|-------------------|-----------------------------|-----------------------|-------------------|-----|-----------------------|------------------|-----------------------------|--|

| BAUD<br>RATE | Fosc                          | Fosc = 40.000 MHz |                             |                       | Fosc = 20.000 MHz |                             |                       | Fosc = 10.000 MHz |     |                       | Fosc = 8.000 MHz |                             |  |

| (K)          | Actual<br>Rate<br>(K)         | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error        | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | Rate Frror        |     | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |

| 0.3          | -                             | _                 | _                           | _                     | _                 | _                           | _                     | _                 | _   | _                     | _                | _                           |  |

| 1.2          | —                             | —                 | —                           | —                     | —                 | —                           | —                     | —                 | —   | —                     | —                | —                           |  |

| 2.4          | —                             | —                 | —                           | —                     | _                 | —                           | 2.441                 | 1.73              | 255 | 2403                  | -0.16            | 207                         |  |

| 9.6          | 9.766                         | 1.73              | 255                         | 9.615                 | 0.16              | 129                         | 9.615                 | 0.16              | 64  | 9615                  | -0.16            | 51                          |  |

| 19.2         | 19.231                        | 0.16              | 129                         | 19.231                | 0.16              | 64                          | 19.531                | 1.73              | 31  | 19230                 | -0.16            | 25                          |  |

| 57.6         | 58.140                        | 0.94              | 42                          | 56.818                | -1.36             | 21                          | 56.818                | -1.36             | 10  | 55555                 | 3.55             | 8                           |  |

| 115.2        | 113.636                       | -1.36             | 21                          | 113.636               | -1.36             | 10                          | 125.000               | 8.51              | 4   | _                     | —                | —                           |  |

|       |                       | SYNC = 0, BRGH = 1, BRG16 = 0 |                             |                       |            |                             |                       |                  |                             |  |  |  |  |

|-------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------------|-----------------------------|--|--|--|--|

| BAUD  | Fost                  | c = 4.000                     | MHz                         | Fos                   | c = 2.000  | MHz                         | Fos                   | Fosc = 1.000 MHz |                             |  |  |  |  |

| (K)   | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) |  |  |  |  |

| 0.3   | —                     | _                             | _                           | _                     | _          | _                           | 300                   | -0.16            | 207                         |  |  |  |  |

| 1.2   | 1.202                 | 0.16                          | 207                         | 1201                  | -0.16      | 103                         | 1201                  | -0.16            | 51                          |  |  |  |  |

| 2.4   | 2.404                 | 0.16                          | 103                         | 2403                  | -0.16      | 51                          | 2403                  | -0.16            | 25                          |  |  |  |  |

| 9.6   | 9.615                 | 0.16                          | 25                          | 9615                  | -0.16      | 12                          | _                     | _                | _                           |  |  |  |  |

| 19.2  | 19.231                | 0.16                          | 12                          | _                     | _          | _                           | _                     | _                | _                           |  |  |  |  |

| 57.6  | 62.500                | 8.51                          | 3                           | _                     | _          | _                           | _                     | _                | _                           |  |  |  |  |

| 115.2 | 125.000               | 8.51                          | 1                           | _                     | —          | _                           |                       | _                | —                           |  |  |  |  |

## $\label{eq:register23-30:BnEIDL: TX/RX BUFFER n EXTENDED IDENTIFIER REGISTERS, \\ LOW BYTE IN RECEIVE MODE [0 \le n \le 5, TXnEN (BSEL<n>) = 0]^{(1)}$

| R-x   | R-x  | R-x  | R-x  | R-x  | R-x  | R-x  | R-x   |

|-------|------|------|------|------|------|------|-------|

| EID7  | EID6 | EID5 | EID4 | EID3 | EID2 | EID1 | EID0  |

| bit 7 |      |      |      |      |      |      | bit 0 |

bit 7-0

EID7:EID0: Extended Identifier bits

Note 1: These registers are available in Mode 1 and 2 only.

| Legend   | d:          |                  |                      |                    |

|----------|-------------|------------------|----------------------|--------------------|

| R = Re   | adable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |

| - n = Va | alue at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### REGISTER 23-31: BnEIDL: TX/RX BUFFER n EXTENDED IDENTIFIER REGISTERS, LOW BYTE IN TRANSMIT MODE $[0 \le n \le 5, TXnEN (BSEL<n>) = 1]^{(1)}$

| -     |       |       | <b>L</b> - | - ,   | <b>`</b> | / 1   |       |  |

|-------|-------|-------|------------|-------|----------|-------|-------|--|

| R/W-x | R/W-x | R/W-x | R/W-x      | R/W-x | R/W-x    | R/W-x | R/W-x |  |

| EID7  | EID6  | EID5  | EID4       | EID3  | EID2     | EID1  | EID0  |  |

| bit 7 |       |       |            |       |          |       | bit 0 |  |

#### bit 7-0

EID7:EID0: Extended Identifier bits

Note 1: These registers are available in Mode 1 and 2 only.

| Legend:            |                  |                      |                    |

|--------------------|------------------|----------------------|--------------------|

| R = Readable bit   | W = Writable bit | U = Unimplemented    | l bit, read as '0' |

| - n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### 23.2.6 CAN INTERRUPT REGISTERS

The registers in this section are the same as described in **Section 9.0 "Interrupts"**. They are duplicated here for convenience.

#### REGISTER 23-56: PIR3: PERIPHERAL INTERRUPT FLAG REGISTER

| LIX 23-30. | 1 11(3.1 L)                                                                                                                                                   |                                                                                                                                                                                                                   |              | ULLAC             |                       | IN                    |                   |                     |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------------|-----------------------|-----------------------|-------------------|---------------------|--|--|--|

|            | R/W-0                                                                                                                                                         | R/W-0                                                                                                                                                                                                             | R/W-0        | R/W-0             | R/W-0                 | R/W-0                 | R/W-0             | R/W-0               |  |  |  |

|            | IRXIF                                                                                                                                                         | WAKIF                                                                                                                                                                                                             | ERRIF        | TXB2IF/<br>TXBnIF | TXB1IF <sup>(1)</sup> | TXB0IF <sup>(1)</sup> | RXB1IF/<br>RXBnIF | RXB0IF/<br>FIFOWMIF |  |  |  |

|            | bit 7                                                                                                                                                         | I                                                                                                                                                                                                                 | 1            |                   | 1                     |                       |                   | bit 0               |  |  |  |

| bit 7      |                                                                                                                                                               |                                                                                                                                                                                                                   |              | ssage Interr      |                       |                       |                   |                     |  |  |  |

|            |                                                                                                                                                               |                                                                                                                                                                                                                   |              | irred on the      | CAN bus               |                       |                   |                     |  |  |  |

| bit 6      |                                                                                                                                                               | alid messao                                                                                                                                                                                                       |              | up Interrupt      | Eloa bit              |                       |                   |                     |  |  |  |

| DILO       |                                                                                                                                                               | on CAN b                                                                                                                                                                                                          |              | • •               | Flag bit              |                       |                   |                     |  |  |  |

|            | 0 = No act                                                                                                                                                    | ivity on CAI                                                                                                                                                                                                      | N bus        |                   |                       |                       |                   |                     |  |  |  |

| bit 5      |                                                                                                                                                               | AN bus Erro                                                                                                                                                                                                       |              | -                 | (multiple of          |                       |                   |                     |  |  |  |

|            |                                                                                                                                                               | N module e                                                                                                                                                                                                        |              |                   | e (multiple so        | burces)               |                   |                     |  |  |  |

| bit 4      |                                                                                                                                                               | lis in Mode                                                                                                                                                                                                       |              |                   |                       |                       |                   |                     |  |  |  |

|            | TXB2IF: C                                                                                                                                                     | AN Transm                                                                                                                                                                                                         | nit Buffer 2 | Interrupt Fla     | g bit                 |                       |                   |                     |  |  |  |

|            |                                                                                                                                                               | <b>TXB2IF:</b> CAN Transmit Buffer 2 Interrupt Flag bit<br>1 = Transmit Buffer 2 has completed transmission of a message and may be reloaded<br>0 = Transmit Buffer 2 has not completed transmission of a message |              |                   |                       |                       |                   |                     |  |  |  |

|            | When CAN is in Mode 1 or 2:                                                                                                                                   |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

|            | <b>TXBnIF:</b> Any Transmit Buffer Interrupt Flag bit<br>1 = One or more transmit buffers has completed transmission of a message and may be reloaded         |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

|            | 0 = No transmit buffer is ready for reload                                                                                                                    |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

| bit 3      | TXB1IF: CAN Transmit Buffer 1 Interrupt Flag bit <sup>(1)</sup>                                                                                               |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

|            | 1 = Transmit Buffer 1 has completed transmission of a message and may be reloaded                                                                             |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

| bit 2      | <ul> <li>0 = Transmit Buffer 1 has not completed transmission of a message</li> <li>TXB0IF: CAN Transmit Buffer 0 Interrupt Flag bit<sup>(1)</sup></li> </ul> |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

| DIL Z      | 1 = Transmit Buffer 0 has completed transmission of a message and may be reloaded<br>0 = Transmit Buffer 0 has not completed transmission of a message        |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

| bit 1      |                                                                                                                                                               | lis in Mode                                                                                                                                                                                                       |              | inplotod trail    |                       | amoooago              |                   |                     |  |  |  |

|            | <b>RXB1IF:</b> CAN Receive Buffer 1 Interrupt Flag bit                                                                                                        |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

|            | <ul> <li>1 = Receive Buffer 1 has received a new message</li> <li>0 = Receive Buffer 1 has not received a new message</li> </ul>                              |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

|            | When CAN is in Mode 1 or 2:                                                                                                                                   |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

|            | RXBnIF: Any Receive Buffer Interrupt Flag bit                                                                                                                 |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

|            | <ul> <li>1 = One or more receive buffers has received a new message</li> <li>0 = No receive buffer has received a new message</li> </ul>                      |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

| bit 0      | When CAN is in Mode 0:                                                                                                                                        |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

|            | RXB0IF: CAN Receive Buffer 0 Interrupt Flag bit                                                                                                               |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

|            | 1 = Receive Buffer 0 has received a new message<br>0 = Receive Buffer 0 has not received a new message                                                        |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

|            |                                                                                                                                                               | lis in Mode                                                                                                                                                                                                       |              |                   |                       |                       |                   |                     |  |  |  |

|            | -                                                                                                                                                             | nented: Rea                                                                                                                                                                                                       |              |                   |                       |                       |                   |                     |  |  |  |

|            | -                                                                                                                                                             | <u>∖ is in Mode</u><br>: FIFO Wa                                                                                                                                                                                  |              | errupt Flag b     | bit                   |                       |                   |                     |  |  |  |

|            | FIFOWMIF: FIFO Watermark Interrupt Flag bit<br>1 = FIFO high watermark is reached<br>0 = FIFO high watermark is not reached                                   |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

|            | <b>Note 1:</b> In CAN Mode 1 and 2, this bit is forced to '0'.                                                                                                |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

|            | Legend:                                                                                                                                                       |                                                                                                                                                                                                                   |              |                   |                       |                       |                   |                     |  |  |  |

|            | R = Reada                                                                                                                                                     | able bit                                                                                                                                                                                                          | W = Wri      | table bit         | U = Un                | implemente            | d bit, read a     | s '0'               |  |  |  |

|            |                                                                                                                                                               |                                                                                                                                                                                                                   |              |                   | (0)                   |                       |                   |                     |  |  |  |

- n = Value at POR

'1' = Bit is set

x = Bit is unknown

'0' = Bit is cleared

#### 23.5.3 PROGRAMMABLE TRANSMIT/ RECEIVE BUFFERS

The ECAN module implements six new buffers: B0-B5. These buffers are individually programmable as either transmit or receive buffers. These buffers are available only in Mode 1 and 2. As with dedicated transmit and receive buffers, each of these programmable buffers occupies 14 bytes of SRAM and are mapped into SFR memory map.

Each buffer contains one Control register (BnCON), four Identifier registers (BnSIDL, BnSIDH, BnEIDL, BnEIDH), one Data Length Count register (BnDLC) and eight Data Byte registers (BnDm). Each of these registers contains two sets of control bits. Depending on whether the buffer is configured as transmit or receive, one would use the corresponding control bit set. By default, all buffers are configured as receive buffers. Each buffer can be individually configured as transmit or receive buffers by setting the corresponding TXENn bit in the BSEL0 register.

When configured as transmit buffers, user firmware may access transmit buffers in any order similar to accessing dedicated transmit buffers. In receive configuration, with Mode 1 enabled, user firmware may also access receive buffers in any order required. But in Mode 2, all receive buffers are combined to form a single FIFO. Actual FIFO length is programmable by user firmware. Access to FIFO must be done through the FIFO pointer bits (FP<4:0>) in the CANCON register. It must be noted that there is no hardware protection against out of order FIFO reads.

#### 23.5.4 PROGRAMMABLE AUTO-RTR BUFFERS

In Mode 1 and 2, any of six programmable transmit/ receive buffers may be programmed to automatically respond to predefined RTR messages without user firmware intervention. Automatic RTR handling is enabled by setting the TXnEN bit in the BSEL0 register and the RTREN bit in the BnCON register. After this setup, when an RTR request is received, the TXREQ bit is automatically set and current buffer content is automatically queued for transmission as a RTR response. As with all transmit buffers, once the TXREQ bit is set, buffer registers become read-only and any writes to them will be ignored. The following outlines the steps required to automatically handle RTR messages:

- 1. Set buffer to Transmit mode by setting TXnEN bit to '1' in BSEL0 register.

- At least one acceptance filter must be associated with this buffer and preloaded with expected RTR identifier.

- 3. Bit RTREN in BnCON register must be set to '1'.

- 4. Buffer must be preloaded with the data to be sent as a RTR response.

Normally, user firmware will keep Buffer Data registers up to date. If firmware attempts to update buffer while an automatic RTR response is in process of transmission, all writes to buffers are ignored.

#### 23.6 CAN Message Transmission

#### 23.6.1 INITIATING TRANSMISSION

For the MCU to have write access to the message buffer, the TXREQ bit must be clear, indicating that the message buffer is clear of any pending message to be transmitted. At a minimum, the SIDH, SIDL, and DLC registers must be loaded. If data bytes are present in the message, the data registers must also be loaded. If the message is to use extended identifiers, the EIDH:EIDL registers must also be loaded and the EXIDE bit set.

To initiate message transmission, the TXREQ bit must be set for each buffer to be transmitted. When TXREQ is set, the TXABT, TXLARB and TXERR bits will be cleared. To successfully complete the transmission, there must be at least one node with matching baud rate on the network.

Setting the TXREQ bit does not initiate a message transmission, it merely flags a message buffer as ready for transmission. Transmission will start when the device detects that the bus is available. The device will then begin transmission of the highest priority message that is ready.

When the transmission has completed successfully, the TXREQ bit will be cleared, the TXBnIF bit will be set, and an interrupt will be generated if the TXBnIE bit is set.

If the message transmission fails, the TXREQ will remain set, indicating that the message is still pending for transmission and one of the following condition flags will be set. If the message started to transmit but encountered an error condition, the TXERR and the IRXIF bits will be set and an interrupt will be generated. If the message lost arbitration, the TXLARB bit will be set.

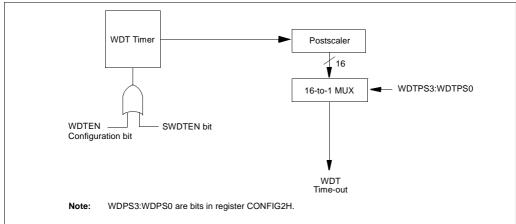

#### 24.2.2 WDT POSTSCALER

The WDT has a postscaler that can extend the WDT Reset period. The postscaler is selected at the time of the device programming by the value written to the CONFIG2H Configuration register.

| Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|----------|-------|-------|-------|--------|--------|--------|--------|--------|

| CONFIG2H | —     | _     | _     | WDTPS3 | WDTPS2 | WDTPS2 | WDTPS0 | WDTEN  |

| RCON     | IPEN  | _     | _     | RI     | TO     | PD     | POR    | BOR    |

| WDTCON   | —     |       |       | —      | —      | —      | _      | SWDTEN |

Legend: Shaded cells are not used by the Watchdog Timer.

#### TABLE 25-2: PIC18FXXX INSTRUCTION SET

| Mnemonic, |                                 | Description                              | Cycles                          | 16-Bit Instruction Word |      |      |      | Status           | Notes    |

|-----------|---------------------------------|------------------------------------------|---------------------------------|-------------------------|------|------|------|------------------|----------|

| Opera     | nds                             | Description                              | Cycles                          | MSb                     |      |      | LSb  | Affected         | Notes    |

| BYTE-OR   | IENTED                          | FILE REGISTER OPERATIONS                 |                                 |                         |      |      |      |                  |          |

| ADDWF     | f, d, a                         | Add WREG and f                           | 1                               | 0010                    | 01da | ffff | ffff | C, DC, Z, OV, N  | 1, 2     |

| ADDWFC    | f, d, a                         | Add WREG and Carry bit to f              | 1                               | 0010                    | 00da | ffff | ffff | C, DC, Z, OV, N  | 1, 2     |

| ANDWF     | f, d, a                         | AND WREG with f                          | 1                               | 0001                    | 01da | ffff | ffff | Z, N             | 1,2      |

| CLRF      | f, a                            | Clear f                                  | 1                               | 0110                    | 101a | ffff | ffff | Z                | 2        |

| COMF      | f, d, a                         | Complement f                             | 1                               | 0001                    | 11da | ffff | ffff | Z, N             | 1, 2     |

| CPFSEQ    | f, a                            | Compare f with WREG, Skip =              | 1 (2 or 3)                      | 0110                    | 001a | ffff | ffff | None             | 4        |

| CPFSGT    | f, a                            | Compare f with WREG, Skip >              | 1 (2 or 3)                      | 0110                    | 010a | ffff | ffff | None             | 4        |

| CPFSLT    | f, a                            | Compare f with WREG, Skip <              | 1 (2 or 3)                      | 0110                    | 000a | ffff | ffff | None             | 1, 2     |

| DECF      | f, d, a                         | Decrement f                              | 1 ΄                             | 0000                    | 01da | ffff | ffff | C, DC, Z, OV, N  | 1, 2, 3, |

| DECFSZ    | f, d, a                         | Decrement f, Skip if 0                   | 1 (2 or 3)                      | 0010                    | 11da | ffff | ffff | None             | 1, 2, 3, |

| DCFSNZ    |                                 | Decrement f, Skip if Not 0               | 1 (2 or 3)                      | 0100                    | 11da | ffff | ffff | None             | 1, 2     |

| INCF      | f, d, a                         | Increment f                              | 1 ΄                             | 0010                    | 10da | ffff | ffff | C, DC, Z, OV, N  |          |

| INCFSZ    | f, d, a                         | Increment f, Skip if 0                   | 1 (2 or 3)                      | 0011                    | 11da | ffff | ffff | None             | 4        |

| INFSNZ    | f, d, a                         | Increment f, Skip if Not 0               | 1 (2 or 3)                      | 0100                    | 10da | ffff | ffff | None             | 1, 2     |

| IORWF     | f, d, a                         | Inclusive OR WREG with f                 | 1 ΄                             | 0001                    | 00da | ffff | ffff | Z, N             | 1, 2     |

| MOVF      | f, d, a                         | Move f                                   | 1                               | 0101                    | 00da | ffff | ffff | Z, N             | 1        |

| MOVFF     | f <sub>s</sub> , f <sub>d</sub> | Move f <sub>s</sub> (source) to 1st word | 2                               | 1100                    | ffff | ffff | ffff | None             |          |

| -         | 3, u                            | f <sub>d</sub> (destination) 2nd word    |                                 | 1111                    | ffff | ffff | ffff |                  |          |

| MOVWF     | f, a                            | Move WREG to f                           | 1                               | 0110                    | 111a | ffff | ffff | None             |          |

| MULWF     | f, a                            | Multiply WREG with f                     | 1                               | 0000                    | 001a | ffff | ffff | None             |          |

| NEGF      | f, a                            | Negate f                                 | 1                               | 0110                    | 110a | ffff | ffff | C, DC, Z, OV, N  | 1, 2     |

| RLCF      | f, d, a                         | Rotate Left f through Carry              | 1                               | 0011                    | 01da | ffff | ffff | C, Z, N          |          |

| RLNCF     | f, d, a                         | Rotate Left f (No Carry)                 | 1                               | 0100                    | 01da | ffff | ffff | Z, N             | 1, 2     |

| RRCF      | f, d, a                         | Rotate Right f through Carry             | 1                               | 0011                    | 00da | ffff | ffff | C, Z, N          |          |

| RRNCF     | f, d, a                         | Rotate Right f (No Carry)                | 1                               | 0100                    | 00da | ffff | ffff | Z, N             |          |

| SETF      | f, a                            | Set f                                    | 1                               | 0110                    | 100a | ffff | ffff | None             |          |

| SUBFWB    | f, d, a                         | Subtract f from WREG with<br>borrow      | 1                               | 0101                    | 01da | ffff | ffff | C, DC, Z, OV, N  | 1, 2     |

| SUBWF     | f, d, a                         | Subtract WREG from f                     | 1                               | 0101                    | 11da | ffff | ffff | C, DC, Z, OV, N  |          |

| SUBWFB    | , ,                             | Subtract WREG from f with                | 1                               |                         | 10da | ffff | ffff |                  | 1.2      |

| 0022      | ., u, u                         | borrow                                   |                                 | 0101                    | 1000 |      |      | 0, 20, 2, 0,,    | ., _     |

| SWAPF     | f, d, a                         | Swap nibbles in f                        | 1                               | 0011                    | 10da | ffff | ffff | None             | 4        |

| TSTFSZ    | f, a                            | Test f, Skip if 0                        | 1 (2 or 3)                      |                         | 011a | ffff | ffff | None             | 1, 2     |

| XORWF     | f, d, a                         | Exclusive OR WREG with f                 | 1                               |                         | 10da | ffff | ffff |                  | ., _     |

|           |                                 | ILE REGISTER OPERATIONS                  | -                               | 0001                    | 2000 |      |      | _,               |          |

| BCF       | f, b, a                         | Bit Clear f                              | 1                               | 1001                    | bbba | ffff | ffff | None             | 1, 2     |

| BSF       | f, b, a                         | Bit Set f                                | 1                               |                         | bbba | ffff | ffff | None             | 1, 2     |

| BTFSC     | f, b, a                         | Bit Test f, Skip if Clear                | 1 (2 or 3)                      |                         |      | ffff | ffff |                  | 3, 4     |

| BTFSS     | f, b, a                         | Bit Test f, Skip if Set                  | 1 (2 or 3)                      |                         | bbba | ffff | ffff | None             | 3, 4     |

| BTG       | f, d, a                         | Bit Toggle f                             | 1                               |                         | bbba | ffff |      | None             | 1, 2     |

|           |                                 |                                          | 1<br>1<br>1<br>1<br>1<br>1<br>1 |                         | JUDA |      |      | the velue weed w | •, •     |

**Note 1:** When a Port register is modified as a function of itself (e.g., MOVF PORTB, 1, 0), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned.

3: If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

4: Some instructions are two-word instructions. The second word of these instructions will be executed as a NOP unless the first word of the instruction retrieves the information embedded in these 16 bits. This ensures that all program memory locations have a valid instruction.

5: If the table write starts the write cycle to internal memory, the write will continue until terminated.

| TBLRD           | Table Read                                                                                                                                                                                                                                                                                           |         |              |                                           |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|-------------------------------------------|--|--|--|--|

| Syntax:         | [ label ]                                                                                                                                                                                                                                                                                            | TBLRD ( | *; *+; *-; + | -*)                                       |  |  |  |  |

| Operands:       | None                                                                                                                                                                                                                                                                                                 |         |              |                                           |  |  |  |  |

| Operation:      | if TBLRD *,<br>(Prog Mem (TBLPTR)) → TABLAT;<br>TBLPTR – No Change;<br>if TBLRD *+,<br>(Prog Mem (TBLPTR)) → TABLAT;<br>(TBLPTR) + 1 → TBLPTR;<br>if TBLRD *-,<br>(Prog Mem (TBLPTR)) → TABLAT;<br>(TBLPTR) - 1 → TBLPTR;<br>if TBLRD +*,<br>(TBLPTR) + 1 → TBLPTR;<br>(Prog Mem (TBLPTR)) → TABLAT; |         |              |                                           |  |  |  |  |

| Status Affected | :None                                                                                                                                                                                                                                                                                                |         |              |                                           |  |  |  |  |

| Encoding:       | 0000                                                                                                                                                                                                                                                                                                 | 0000    | 0000         | 10nn<br>nn=0 *<br>=1 *+<br>=2 *-<br>=3 +* |  |  |  |  |

| Description:    | This instruction is used to read the                                                                                                                                                                                                                                                                 |         |              |                                           |  |  |  |  |

Description: This instruction is used to read the contents of Program Memory (P.M.). To address the program memory, a pointer called Table Pointer (TBLPTR) is used. The TBLPTR (a 21-bit pointer) points to each byte in the program memory. TBLPTR has a 2-Mbyte address range.

TBLPTR[0] = 0: Least Significant Byte of Program Memory Word TBLPTR[0] = 1: Most Significant Byte of Program

Memory Word The TBLRD instruction can modify the value of TBLPTR as follows:

- no change

- post-increment

- post-decrement

- pre-increment

1

2

Words:

Cycles:

Q Cycle Activity:

| Q1              | Q2                                       | Q3              | Q4                                |

|-----------------|------------------------------------------|-----------------|-----------------------------------|

| Decode          | No                                       | No              | No                                |

|                 | operation                                | operation       | operation                         |

| No<br>operation | No operation<br>(Read<br>Program Memory) | No<br>operation | No operation<br>(Write<br>TABLAT) |

| TBLRD                                        | Table Read                        | l (Co       | ontinued)                        |

|----------------------------------------------|-----------------------------------|-------------|----------------------------------|

| Example1:                                    | TBLRD *+                          | ;           |                                  |

| Before Instruc<br>TABLAT<br>TBLPTR<br>MEMORY | tion<br>(0x00A356)                | =<br>=<br>= | 0x55<br>0x00A356<br>0x34         |

| After Instructio<br>TABLAT<br>TBLPTR         | on                                | =<br>=      | 0x34<br>0x00A357                 |

| Example2:                                    | TBLRD +*                          | ;           |                                  |

|                                              | ction<br>(0x01A357)<br>(0x01A358) | =<br>=<br>= | 0xAA<br>0x01A357<br>0x12<br>0x34 |

| After Instructio<br>TABLAT<br>TBLPTR         | on                                | =           | 0x34<br>0x01A358                 |

#### 26.3 MPLAB C17 and MPLAB C18 C Compilers

The MPLAB C17 and MPLAB C18 Code Development Systems are complete ANSI C compilers for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers. These compilers provide powerful integration capabilities, superior code optimization and ease of use not found with other compilers.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 26.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK object linker combines relocatable objects created by the MPASM assembler and the MPLAB C17 and MPLAB C18 C compilers. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB object librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 26.5 MPLAB C30 C Compiler

The MPLAB C30 C compiler is a full-featured, ANSI compliant, optimizing compiler that translates standard ANSI C programs into dsPIC30F assembly language source. The compiler also supports many command line options and language extensions to take full advantage of the dsPIC30F device hardware capabilities and afford fine control of the compiler code generator.

MPLAB C30 is distributed with a complete ANSI C standard library. All library functions have been validated and conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory allocation, data conversion, time-keeping and math functions (trigonometric, exponential and hyperbolic). The compiler provides symbolic information for high-level source debugging with the MPLAB IDE.

### 26.6 MPLAB ASM30 Assembler, Linker and Librarian