Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                     |

| Core Processor             | M8C                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 24MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                       |

| Peripherals                | POR, PWM, WDT                                                                |

| Number of I/O              | 49                                                                           |

| Program Memory Size        | 16KB (16K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 1K x 8                                                                       |

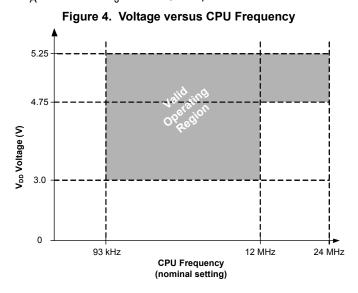

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                   |

| Data Converters            | A/D 47x14b; D/A 2x9b                                                         |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 56-VFQFN Exposed Pad                                                         |

| Supplier Device Package    | 56-QFN (8x8)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c24894-24ltxat |

### Additional System Resources

System resources provide additional capability useful for complete systems. Additional resources include a multiplier, decimator, LVD, and power-on reset (POR). Brief statements describing the merits of each resource follow.

- Digital clock dividers provide three customizable clock frequencies for use in applications. The clocks can be routed to both the digital and analog systems. Additional clocks are generated using digital PSoC blocks as clock dividers.

- Two multiply accumulates (MACs) provide fast 8-bit multipliers with 32-bit accumulate, to assist in both general math and digital filters.

- The decimator provides a custom hardware filter for digital signal processing applications including creation of Delta-Sigma ADCs.

- The I<sup>2</sup>C module provides 0 to 400 kHz communication over two wires. Slave, master, and multi-master modes are all supported.

- LVD interrupts can signal the application of falling voltage levels, while the advanced POR circuit eliminates the need for a system supervisor.

- An internal 1.3-V voltage reference provides an absolute reference for the analog system, including ADCs and DACs.

- Versatile analog multiplexer system.

#### **PSoC Device Characteristics**

Depending on your PSoC device characteristics, the digital and analog systems can have varying numbers of digital and analog blocks. The following table lists the resources available for specific PSoC device groups. The device covered by this datasheet is shown in the highlighted row of the table.

Table 1. PSoC Device Characteristics

| PSoC Part<br>Number       | Digital<br>I/O | Digital<br>Rows | Digital<br>Blocks | Analog<br>Inputs | Analog<br>Outputs | Analog<br>Columns | Analog<br>Blocks               | SRAM<br>Size | Flash<br>Size |

|---------------------------|----------------|-----------------|-------------------|------------------|-------------------|-------------------|--------------------------------|--------------|---------------|

| CY8C29x66 <sup>[1]</sup>  | up to 64       | 4               | 16                | up to 12         | 4                 | 4                 | 12                             | 2 K          | 32 K          |

| CY8C28xxx                 | up to 44       | up to 3         | up to 12          | up to 44         | up to 4           | up to 6           | up to<br>12 + 4 <sup>[2]</sup> | 1 K          | 16 K          |

| CY8C27x43                 | up to 44       | 2               | 8                 | up to 12         | 4                 | 4                 | 12                             | 256          | 16 K          |

| CY8C24x94 <sup>[1]</sup>  | up to 56       | 1               | 4                 | up to 48         | 2                 | 2                 | 6                              | 1 K          | 16 K          |

| CY8C24x23A <sup>[1]</sup> | up to 24       | 1               | 4                 | up to 12         | 2                 | 2                 | 6                              | 256          | 4 K           |

| CY8C23x33                 | up to 26       | 1               | 4                 | up to 12         | 2                 | 2                 | 4                              | 256          | 8 K           |

| CY8C22x45 <sup>[1]</sup>  | up to 38       | 2               | 8                 | up to 38         | 0                 | 4                 | 6 <sup>[2]</sup>               | 1 K          | 16 K          |

| CY8C21x45 <sup>[1]</sup>  | up to 24       | 1               | 4                 | up to 24         | 0                 | 4                 | 6 <sup>[2]</sup>               | 512          | 8 K           |

| CY8C21x34 <sup>[1]</sup>  | up to 28       | 1               | 4                 | up to 28         | 0                 | 2                 | 4 <sup>[2]</sup>               | 512          | 8 K           |

| CY8C21x23                 | up to 16       | 1               | 4                 | up to 8          | 0                 | 2                 | 4 <sup>[2]</sup>               | 256          | 4 K           |

| CY8C20x34 <sup>[1]</sup>  | up to 28       | 0               | 0                 | up to 28         | 0                 | 0                 | 3 <sup>[2,3]</sup>             | 512          | 8 K           |

| CY8C20xx6                 | up to 36       | 0               | 0                 | up to 36         | 0                 | 0                 | 3 <sup>[2,3]</sup>             | up to 2 K    | up to 32 K    |

#### Notes

- Automotive qualified devices available in this group.

- Limited analog functionality.

- 3. Two analog blocks and one CapSense® block.

### **Getting Started**

For in depth information, along with detailed programming details, see the  $PSoC^{\otimes}$  Technical Reference Manual.

For up-to-date ordering, packaging, and electrical specification information, see the latest PSoC device datasheets on the web.

#### **Application Notes**

Cypress application notes are an excellent introduction to the wide variety of possible PSoC designs.

### **Development Kits**

PSoC Development Kits are available online from and through a growing number of regional and global distributors, which include Arrow, Avnet, Digi-Key, Farnell, Future Electronics, and Newark.

#### **Training**

Free PSoC technical training (on demand, webinars, and workshops), which is available online via www.cypress.com, covers a wide variety of topics and skill levels to assist you in your designs.

#### **CYPros Consultants**

Certified PSoC consultants offer everything from technical assistance to completed PSoC designs. To contact or become a PSoC consultant go to the CYPros Consultants web site.

#### **Solutions Library**

Visit our growing library of solution focused designs. Here you can find various application designs that include firmware and hardware design files that enable you to complete your designs quickly.

### **Technical Support**

Technical support – including a searchable Knowledge Base articles and technical forums – is also available online. If you cannot find an answer to your question, call our Technical Support hotline at 1-800-541-4736.

### **Development Tools**

PSoC Designer™ is the revolutionary Integrated Design Environment (IDE) that you can use to customize PSoC to meet your specific application requirements. PSoC Designer software accelerates system design and time to market. Develop your applications using a library of precharacterized analog and digital peripherals (called user modules) in a drag-and-drop design environment. Then, customize your design by leveraging the dynamically generated application programming interface (API) libraries of code. Finally, debug and test your designs with the integrated debug environment, including in-circuit emulation and standard software debug features. PSoC Designer includes:

- Application editor graphical user interface (GUI) for device and user module configuration and dynamic reconfiguration

- Extensive user module catalog

- Integrated source-code editor (C and assembly)

- Free C compiler with no size restrictions or time limits

- Built-in debugger

- In-circuit emulation

- Built-in support for communication interfaces:

- ☐ Hardware and software I<sup>2</sup>C slaves and masters

- □ Full-speed USB 2.0

- Up to four full-duplex universal asynchronous receiver/transmitters (UARTs), SPI master and slave, and wireless

PSoC Designer supports the entire library of PSoC 1 devices and runs on Windows XP, Windows Vista, and Windows 7.

#### **PSoC Designer Software Subsystems**

#### Design Entry

In the chip-level view, choose a base device to work with. Then select different onboard analog and digital components that use the PSoC blocks, which are called user modules. Examples of user modules are analog-to-digital converters (ADCs), digital-to-analog converters (DACs), amplifiers, and filters. Configure the user modules for your chosen application and connect them to each other and to the proper pins. Then generate your project. This prepopulates your project with APIs and libraries that you can use to program your application.

The tool also supports easy development of multiple configurations and dynamic reconfiguration. Dynamic reconfiguration makes it possible to change configurations at run time. In essence, this allows you to use more than 100 percent of PSoC's resources for a given application.

#### Code Generation Tools

The code generation tools work seamlessly within the PSoC Designer interface and have been tested with a full range of debugging tools. You can develop your design in C, assembly, or a combination of the two.

**Assemblers**. The assemblers allow you to merge assembly code seamlessly with C code. Link libraries automatically use absolute addressing or are compiled in relative mode, and linked with other software modules to get absolute addressing.

**C Language Compilers**. C language compilers are available that support the PSoC family of devices. The products allow you to create complete C programs for the PSoC family devices. The optimizing C compilers provide all of the features of C, tailored to the PSoC architecture. They come complete with embedded libraries providing port and bus operations, standard keypad and display support, and extended math functionality.

#### Debugger

PSoC Designer has a debug environment that provides hardware in-circuit emulation, allowing you to test the program in a physical system while providing an internal view of the PSoC device. Debugger commands allow you to read and program and read and write data memory, and read and write I/O registers. You can read and write CPU registers, set and clear breakpoints, and provide program run, halt, and step control. The debugger also allows you to create a trace buffer of registers and memory locations of interest.

## Register Map Bank 0 Table: User Space

|                  |              |        | User Spac | , -          |        |                   |              |        |          |              |                                                  |

|------------------|--------------|--------|-----------|--------------|--------|-------------------|--------------|--------|----------|--------------|--------------------------------------------------|

| Name             | Addr (0,Hex) | Access | Name      | Addr (0,Hex) | Access | Name              | Addr (0,Hex) | Access | Name     | Addr (0,Hex) | Access                                           |

| PRT0DR           | 00           | RW     |           | 40           |        | ASC10CR0          | 80           | RW     |          | C0           |                                                  |

| PRT0IE           | 01           | RW     |           | 41           |        | ASC10CR1          | 81           | RW     |          | C1           |                                                  |

| PRT0GS           | 02           | RW     |           | 42           |        | ASC10CR2          | 82           | RW     |          | C2           |                                                  |

| PRT0DM2          | 03           | RW     |           | 43           |        | ASC10CR3          | 83           | RW     |          | C3           |                                                  |

| PRT1DR           | 04           | RW     |           | 44           |        | ASD11CR0          | 84           | RW     |          | C4           |                                                  |

| PRT1IE           | 05           | RW     |           | 45           |        | ASD11CR1          | 85           | RW     |          | C5           |                                                  |

| PRT1GS           | 06           | RW     |           | 46           |        | ASD11CR2          | 86           | RW     |          | C6           |                                                  |

| PRT1DM2          | 07           | RW     |           | 47           |        | ASD11CR3          | 87           | RW     |          | C7           | <del>                                     </del> |

| PRT2DR           | 08           | RW     |           | 48           |        | ASDITORS          | 88           | 1744   |          | C8           |                                                  |

| PRT2IE           |              |        |           |              |        |                   |              |        |          | C9           |                                                  |

|                  | 09           | RW     |           | 49           |        |                   | 89           |        |          |              | -                                                |

| PRT2GS           | 0A           | RW     |           | 4A           |        |                   | 8A           |        |          | CA           |                                                  |

| PRT2DM2          | 0B           | RW     |           | 4B           |        |                   | 8B           |        |          | CB           |                                                  |

| PRT3DR           | 0C           | RW     |           | 4C           |        |                   | 8C           |        |          | CC           |                                                  |

| PRT3IE           | 0D           | RW     |           | 4D           |        |                   | 8D           |        |          | CD           |                                                  |

| PRT3GS           | 0E           | RW     |           | 4E           |        |                   | 8E           |        |          | CE           | ł                                                |

| PRT3DM2          | 0F           | RW     |           | 4F           |        |                   | 8F           |        |          | CF           |                                                  |

| PRT4DR           | 10           | RW     |           | 50           |        | ASD20CR0          | 90           | RW     | CUR PP   | D0           | RW                                               |

| PRT4IE           | 11           | RW     |           | 51           |        | ASD20CR1          | 91           | RW     | STK PP   | D1           | RW                                               |

| PRT4GS           | 12           | RW     |           | 52           |        | ASD20CR2          | 92           | RW     | ****     | D2           |                                                  |

| PRT4DM2          | 13           | RW     |           | 53           |        | ASD20CR3          | 93           | RW     | IDX PP   | D3           | RW                                               |

| PRT5DR           | 14           | RW     | <b>-</b>  | 54           |        | ASC21CR0          | 93           | RW     | MVR PP   | D3           | RW                                               |

|                  |              |        |           |              |        |                   |              |        | _        |              |                                                  |

| PRT5IE           | 15           | RW     |           | 55           |        | ASC21CR1          | 95           | RW     | MVW_PP   | D5           | RW                                               |

| PRT5GS           | 16           | RW     |           | 56           |        | ASC21CR2          | 96           | RW     | I2C_CFG  | D6           | RW                                               |

| PRT5DM2          | 17           | RW     |           | 57           |        | ASC21CR3          | 97           | RW     | I2C_SCR  | D7           | #                                                |

|                  | 18           |        |           | 58           |        |                   | 98           |        | I2C_DR   | D8           | RW                                               |

|                  | 19           |        |           | 59           |        |                   | 99           |        | I2C_MSCR | D9           | #                                                |

|                  | 1A           |        |           | 5A           |        |                   | 9A           |        | INT_CLR0 | DA           | RW                                               |

|                  | 1B           |        |           | 5B           |        |                   | 9B           |        | INT_CLR1 | DB           | RW                                               |

| PRT7DR           | 1C           | RW     |           | 5C           |        |                   | 9C           |        | INT_CLR2 | DC           | RW                                               |

| PRT7IE           | 1D           | RW     |           | 5D           |        |                   | 9D           |        | INT CLR3 | DD           | RW                                               |

| PRT7GS           | 1E           | RW     |           | 5E           |        |                   | 9E           |        | INT MSK3 | DE           | RW                                               |

| PRT7DM2          | 1F           | RW     |           | 5F           |        |                   | 9F           |        | INT MSK2 | DF           | RW                                               |

| DBB00DR0         | 20           | #      | AMX IN    | 60           | RW     |                   | A0           |        | INT_MSK0 | E0           | RW                                               |

| DBB00DR1         | 21           | W      | AMUXCFG   | 61           | RW     |                   | A1           |        | INT_MSK0 | E1           | RW                                               |

|                  | 1            |        | AWOACFG   | 62           | ICAA   |                   |              |        | INT_WSK1 | E2           |                                                  |

| DBB00DR2         | 22           | RW     | 105.00    |              | D147   |                   | A2           |        | _        |              | RC                                               |

| DBB00CR0         | 23           | #      | ARF_CR    | 63           | RW     |                   | A3           |        | RES_WDT  | E3           | W                                                |

| DBB01DR0         | 24           | #      | CMP_CR0   | 64           | #      |                   | A4           |        | DEC_DH   | E4           | RC                                               |

| DBB01DR1         | 25           | W      | ASY_CR    | 65           | #      |                   | A5           |        | DEC_DL   | E5           | RC                                               |

| DBB01DR2         | 26           | RW     | CMP_CR1   | 66           | RW     |                   | A6           |        | DEC_CR0  | E6           | RW                                               |

| DBB01CR0         | 27           | #      |           | 67           |        |                   | A7           |        | DEC_CR1  | E7           | RW                                               |

| DCB02DR0         | 28           | #      |           | 68           |        | MUL1_X            | A8           | W      | MUL0_X   | E8           | W                                                |

| DCB02DR1         | 29           | W      |           | 69           |        | MUL1_Y            | A9           | W      | MUL0_Y   | E9           | W                                                |

| DCB02DR2         | 2A           | RW     |           | 6A           |        | MUL1 DH           | AA           | R      | MUL0 DH  | EA           | R                                                |

| DCB02CR0         | 2B           | #      |           | 6B           |        | MUL1 DL           | AB           | R      | MUL0 DL  | EB           | R                                                |

| DCB03DR0         | 2C           | #      | TMP DR0   | 6C           | RW     | ACC1 DR1          | AC           | RW     | ACC0 DR1 | EC           | RW                                               |

| DCB03DR1         | 2D           | W      | TMP_DR1   | 6D           | RW     | ACC1 DR0          | AD           | RW     | ACC0 DR0 | ED           | RW                                               |

| DCB03DR1         | 2E           | RW     | TMP_DR2   | 6E           | RW     | ACC1_DR3          | AE           | RW     | ACC0_DR3 | EE           | RW                                               |

| DCB03CR0         | 2F           | #      |           | 6F           | RW     | ACC1_DR3          | AE<br>AF     | RW     | ACC0_DR3 | EF           | RW                                               |

| DCB03CR0         |              | #      | TMP_DR3   | _            |        |                   |              |        | ACCU_DR2 |              | KVV                                              |

|                  | 30           |        | ACB00CR3  | 70           | RW     | RDI0RI            | B0           | RW     |          | F0           |                                                  |

|                  | 31           |        | ACB00CR0  | 71           | RW     | RDI0SYN           | B1           | RW     |          | F1           | -                                                |

|                  | 32           |        | ACB00CR1  | 72           | RW     | RDI0IS            | B2           | RW     |          | F2           |                                                  |

|                  | 33           |        | ACB00CR2  | 73           | RW     | RDI0LT0           | B3           | RW     |          | F3           |                                                  |

|                  | 34           |        | ACB01CR3  | 74           | RW     | RDI0LT1           | B4           | RW     |          | F4           | <u> </u>                                         |

|                  | 35           |        | ACB01CR0  | 75           | RW     | RDI0RO0           | B5           | RW     |          | F5           |                                                  |

|                  | 36           |        | ACB01CR1  | 76           | RW     | RDI0RO1           | B6           | RW     |          | F6           |                                                  |

|                  | 37           |        | ACB01CR2  | 77           | RW     |                   | В7           |        | CPU F    | F7           | RL                                               |

|                  | 38           |        |           | 78           |        |                   | B8           |        |          | F8           |                                                  |

|                  | 39           |        |           | 79           |        |                   | B9           |        |          | F9           |                                                  |

|                  | 3A           |        |           | 79<br>7A     |        |                   | BA           |        |          | FA           |                                                  |

|                  | 3B           |        | 1         | 7B           |        |                   | BB           |        |          | FB           |                                                  |

|                  |              |        |           |              |        |                   |              |        |          |              |                                                  |

|                  | 3C           |        |           | 7C           |        |                   | BC           |        | DAG 5    | FC           | D'A'                                             |

|                  | 3D           |        |           | 7D           |        |                   | BD           |        | DAC_D    | FD           | RW                                               |

|                  | 3E           |        |           | 7E           |        |                   | BE           |        | CPU_SCR1 | FE           | #                                                |

|                  | 3F           |        |           | 7F           |        |                   | BF           |        | CPU_SCR0 | FF           | #                                                |

| Blank fields are |              |        |           |              |        | # Access is hit s |              |        |          |              |                                                  |

Blank fields are Reserved and should not be accessed.

# Access is bit specific.

# **Electrical Specifications**

This section presents the DC and AC electrical specifications of the automotive CY8C24x94 PSoC device family. For the most up to date electrical specifications, confirm that you have the most recent datasheet by visiting <a href="http://www.cypress.com">http://www.cypress.com</a>.

Specifications are valid for –40  $^{\circ}C \leq$  T<sub>A</sub>  $\leq$  85  $^{\circ}C$  and T  $_{J} \leq$  100  $^{\circ}C,$  except where noted.

### **DC Electrical Characteristics**

#### DC Chip Level Specifications

Table 5 lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , or 3.0 V to 3.6 V and  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25  $^{\circ}\text{C}$  and are for design guidance only.

Table 5. DC Chip-Level Specifications

| Symbol           | Description                                                                       | Min | Тур | Max  | Units | Notes                                                                                                                                              |

|------------------|-----------------------------------------------------------------------------------|-----|-----|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{DD}$         | Supply voltage                                                                    | 3.0 | _   | 5.25 | V     | See DC POR and LVD specifications, Table 15 on page 25.                                                                                            |

| I <sub>DD5</sub> | Supply current, IMO = 24 MHz, $V_{DD}$ = 5 V                                      | -   | 14  | 27   | mA    | Conditions are $V_{DD}$ = 5.0 V, $T_A$ = 25 °C, CPU = 3 MHz, 48 MHz disabled, VC1 = 1.5 MHz, VC2 = 93.75 kHz, VC3 = 93.75 kHz, Analog power = off. |

| I <sub>DD3</sub> | Supply current, IMO = 24 MHz, V <sub>DD</sub> = 3.3 V                             | -   | 8   | 14   | mA    | Conditions are $V_{DD}$ = 3.3 V, $T_A$ = 25 °C, CPU = 3 MHz, 48 MHz disabled, VC1 = 1.5 MHz, VC2 = 93.75 kHz, VC3 = 0.367 kHz, Analog power = off. |

| I <sub>SB</sub>  | Sleep [5] (mode) current with POR, LVD, sleep timer, and WDT. [6]                 | -   | 3   | 6.5  | μА    | Conditions are with ILO active, $V_{DD}$ = 3.3 V, -40 °C $\leq$ T <sub>A</sub> $\leq$ 55 °C, Analog power = off.                                   |

| I <sub>SBH</sub> | Sleep (mode) current with POR, LVD, sleep timer, and WDT at high temperature. [6] | -   | 4   | 25   | μА    | Conditions are with ILO active, $V_{DD}$ = 3.3 V, 55 °C < $T_A \le 85$ °C, Analog power = off.                                                     |

### Notes

Errata: When the device is operating at 4.75 V to 5.25 V and the 3.3 V regulator is enabled, a short low pulse may be created on the DP signal line during device wake-up. The 15-20 µs low pulse of the DP line may be interpreted by the host computer as a deattach or the beginning of a wake-up. More details in "Errata" on page 46. Standby current includes all functions (POR, LVD, WDT, sleep timer) needed for reliable system operation. This should be compared with devices that have similar functions enabled.

Table 11. 3.3-V DC Analog Output Buffer Specifications

| Symbol               | Description                                 | Min                       | Тур | Max                       | Units | Notes                                             |

|----------------------|---------------------------------------------|---------------------------|-----|---------------------------|-------|---------------------------------------------------|

| V <sub>OSOB</sub>    | Input offset voltage (absolute value)       | _                         | 3   | 12                        | mV    |                                                   |

| TCV <sub>OSOB</sub>  | Average input offset voltage drift          | _                         | +6  | _                         | μV/°C |                                                   |

| $V_{CMOB}$           | Common mode input voltage range             | 0.5                       | _   | V <sub>DD</sub> – 1.0     | V     |                                                   |

| R <sub>OUTOB</sub>   | Output resistance                           |                           |     |                           |       |                                                   |

|                      | Power = low                                 | _                         | 1   | _                         | Ω     |                                                   |

|                      | Power = high                                | _                         | 1   | _                         | Ω     |                                                   |

| V <sub>OHIGHOB</sub> | High output voltage swing                   |                           |     |                           |       |                                                   |

|                      | (load = 1 K $\Omega$ to V <sub>DD</sub> /2) |                           |     |                           |       |                                                   |

|                      | Power = low                                 | $0.5 \times V_{DD} + 1.0$ | _   | _                         | V     |                                                   |

|                      | Power = high                                | $0.5 \times V_{DD} + 1.0$ | _   | _                         | V     |                                                   |

| $V_{OLOWOB}$         | Low output voltage swing                    |                           |     |                           |       |                                                   |

|                      | (load = 1 K $\Omega$ to V <sub>DD</sub> /2) |                           |     |                           |       |                                                   |

|                      | Power = low                                 | _                         | _   | $0.5 \times V_{DD} - 1.0$ | V     |                                                   |

|                      | Power = high                                | _                         | _   | $0.5 \times V_{DD} - 1.0$ | V     |                                                   |

| I <sub>SOB</sub>     | Supply current including opamp              |                           |     |                           |       |                                                   |

|                      | bias cell (no load)                         |                           |     |                           |       |                                                   |

|                      | Power = low                                 | _                         | 8.0 | 2.0                       | mΑ    |                                                   |

|                      | Power = high                                | _                         | 2.0 | 4.3                       | mΑ    |                                                   |

| PSRR <sub>OB</sub>   | Supply voltage rejection ratio              | 34                        | 64  | _                         | dB    | $(0.5 \times V_{DD} - 1.0) \le V_{OUT} \le (0.5)$ |

|                      |                                             |                           |     |                           |       | × V <sub>DD</sub> + 0.9).                         |

| $C_L$                | Load capacitance                            | _                         | _   | 200                       | pF    | This specification applies to the                 |

|                      |                                             |                           |     |                           |       | external circuit that is being                    |

|                      |                                             |                           |     |                           |       | driven by the analog output                       |

|                      |                                             |                           |     |                           |       | buffer.                                           |

Table 12. 5-V DC Analog Reference Specifications (continued)

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings            | Symbol             | Reference | Description                            | Min                        | Тур                        | Max                        | Units |

|------------------------------|----------------------------------------|--------------------|-----------|----------------------------------------|----------------------------|----------------------------|----------------------------|-------|

| 0b010                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | $V_{DD}$                               | V <sub>DD</sub> – 0.037    | V <sub>DD</sub> – 0.007    | V <sub>DD</sub>            | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                     | V <sub>DD</sub> /2 – 0.036 | V <sub>DD</sub> /2 – 0.001 | V <sub>DD</sub> /2 + 0.036 | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                        | $V_{SS}$                   | V <sub>SS</sub> + 0.005    | V <sub>SS</sub> + 0.029    | V     |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | $V_{DD}$                               | V <sub>DD</sub> – 0.034    | V <sub>DD</sub> – 0.006    | $V_{DD}$                   | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                     | V <sub>DD</sub> /2 – 0.036 | V <sub>DD</sub> /2 – 0.001 | V <sub>DD</sub> /2 + 0.035 | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                        | $V_{SS}$                   | V <sub>SS</sub> + 0.004    | V <sub>SS</sub> + 0.024    | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | $V_{DD}$                               | V <sub>DD</sub> – 0.032    | V <sub>DD</sub> – 0.005    | $V_{DD}$                   | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                     | V <sub>DD</sub> /2 – 0.036 | V <sub>DD</sub> /2 – 0.001 | $V_{DD}/2 + 0.035$         | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | $V_{SS}$                               | $V_{SS}$                   | V <sub>SS</sub> + 0.003    | V <sub>SS</sub> + 0.022    | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | $V_{DD}$                               | V <sub>DD</sub> – 0.031    | V <sub>DD</sub> – 0.005    | $V_{DD}$                   | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                     | V <sub>DD</sub> /2 – 0.037 | V <sub>DD</sub> /2 – 0.001 | V <sub>DD</sub> /2 + 0.035 | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                        | V <sub>SS</sub>            | V <sub>SS</sub> + 0.003    | V <sub>SS</sub> + 0.020    | V     |

| 0b011                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3 × Bandgap                            | 3.760                      | 3.884                      | 4.006                      | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.522                      | 2.593                      | 2.669                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | Bandgap                                | 1.252                      | 1.299                      | 1.342                      | V     |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | 3 × Bandgap                            | 3.766                      | 3.887                      | 4.010                      | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.523                      | 2.594                      | 2.670                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | Bandgap                                | 1.252                      | 1.297                      | 1.342                      | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3 × Bandgap                            | 3.769                      | 3.888                      | 4.013                      | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.523                      | 2.594                      | 2.671                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | Bandgap                                | 1.251                      | 1.296                      | 1.343                      | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | 3 × Bandgap                            | 3.769                      | 3.889                      | 4.015                      | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.523                      | 2.595                      | 2.671                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | Bandgap                                | 1.251                      | 1.296                      | 1.344                      | V     |

| 0b100                        | RefPower = high<br>Opamp bias = high   | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap + P2[6]<br>(P2[6] = 1.3 V) | 2.483 - P2[6]              | 2.582 - P2[6]              | 2.674 - P2[6]              | V     |

|                              |                                        | $V_{AGND}$         | AGND      | 2 × Bandgap                            | 2.522                      | 2.593                      | 2.669                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap – P2[6]<br>(P2[6] = 1.3 V) | 2.524 – P2[6]              | 2.600 - P2[6]              | 2.676 – P2[6]              | V     |

|                              | RefPower = high<br>Opamp bias = low    | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap + P2[6]<br>(P2[6] = 1.3 V) | 2.490 - P2[6]              | 2.586 - P2[6]              | 2.679 - P2[6]              | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.523                      | 2.594                      | 2.669                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap – P2[6]<br>(P2[6] = 1.3 V) | 2.523 – P2[6]              | 2.598 - P2[6]              | 2.675 – P2[6]              | V     |

|                              | RefPower = medium<br>Opamp bias = high | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap + P2[6]<br>(P2[6] = 1.3 V) | 2.493 – P2[6]              | 2.588 – P2[6]              | 2.682 - P2[6]              | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.523                      | 2.594                      | 2.670                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap – P2[6]<br>(P2[6] = 1.3 V) | 2.523 – P2[6]              | 2.597 – P2[6]              | 2.675 – P2[6]              | V     |

|                              | RefPower = medium<br>Opamp bias = low  | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap + P2[6]<br>(P2[6] = 1.3 V) | 2.494 - P2[6]              | 2.589 - P2[6]              | 2.685 - P2[6]              | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | 2 × Bandgap                            | 2.523                      | 2.595                      | 2.671                      | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | 2 × Bandgap – P2[6]<br>(P2[6] = 1.3 V) | 2.522 – P2[6]              | 2.596 - P2[6]              | 2.676 - P2[6]              | V     |

Table 13. 3.3-V DC Analog Reference Specifications

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings            | Symbol             | Reference | Description                                             | Min                        | Тур                        | Max                        | Units |

|------------------------------|----------------------------------------|--------------------|-----------|---------------------------------------------------------|----------------------------|----------------------------|----------------------------|-------|

| 0b000                        | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                            | V <sub>DD</sub> /2 + 1.200 | V <sub>DD</sub> /2 + 1.290 | V <sub>DD</sub> /2 + 1.365 | V     |

|                              | Opamp bias = high                      | $V_{AGND}$         | AGND      | V <sub>DD</sub> /2                                      | V <sub>DD</sub> /2 – 0.030 | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.034$         | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                            | V <sub>DD</sub> /2 – 1.346 | V <sub>DD</sub> /2 – 1.292 | V <sub>DD</sub> /2 – 1.208 | V     |

|                              | RefPower = high                        | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                            | V <sub>DD</sub> /2 + 1.196 | V <sub>DD</sub> /2 + 1.292 | V <sub>DD</sub> /2 + 1.374 | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | V <sub>DD</sub> /2 – 0.029 | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.031$         | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                            | V <sub>DD</sub> /2 – 1.349 | V <sub>DD</sub> /2 – 1.295 | V <sub>DD</sub> /2 – 1.227 | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                            | V <sub>DD</sub> /2 + 1.204 | V <sub>DD</sub> /2 + 1.293 | V <sub>DD</sub> /2 + 1.369 | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | $V_{DD}/2 - 0.030$         | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.030$         | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                            | V <sub>DD</sub> /2 – 1.351 | V <sub>DD</sub> /2 – 1.297 | V <sub>DD</sub> /2 – 1.229 | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub> /2 + Bandgap                            | V <sub>DD</sub> /2 + 1.189 | V <sub>DD</sub> /2 + 1.294 | V <sub>DD</sub> /2 + 1.384 | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | V <sub>DD</sub> /2 – 0.032 | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.029$         | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>DD</sub> /2 – Bandgap                            | V <sub>DD</sub> /2 – 1.353 | V <sub>DD</sub> /2 – 1.297 | V <sub>DD</sub> /2 – 1.230 | V     |

| 0b001                        | RefPower = high<br>Opamp bias = high   | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6] -<br>0.105   | P2[4] + P2[6] –<br>0.008   | P2[4] + P2[6] +<br>0.095   | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                                   | P2[4]                      | P2[4]                      | P2[4]                      | _     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6] –<br>0.035   | P2[4]-P2[6]+<br>0.006      | P2[4] – P2[6] +<br>0.053   | V     |

|                              | RefPower = high<br>Opamp bias = low    | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6] –<br>0.094   | P2[4] + P2[6] –<br>0.005   | P2[4] + P2[6] +<br>0.073   | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                                   | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6] –<br>0.033   | P2[4]-P2[6]+<br>0.002      | P2[4]-P2[6]+<br>0.042      | V     |

|                              | RefPower = medium<br>Opamp bias = high | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6] -<br>0.094   | P2[4] + P2[6] –<br>0.003   | P2[4] + P2[6] +<br>0.075   | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                                   | P2[4]                      | P2[4]                      | P2[4]                      | _     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6] –<br>0.035   | P2[4] – P2[6]              | P2[4]-P2[6]+<br>0.038      | V     |

|                              | RefPower = medium<br>Opamp bias = low  | V <sub>REFHI</sub> | Ref High  | P2[4]+P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6] –<br>0.095   | P2[4] + P2[6] –<br>0.003   | P2[4] + P2[6] +<br>0.080   | V     |

|                              |                                        | V <sub>AGND</sub>  | AGND      | P2[4]                                                   | P2[4]                      | P2[4]                      | P2[4]                      | -     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | P2[4]–P2[6] (P2[4] = V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6] –<br>0.038   | P2[4] – P2[6]              | P2[4] – P2[6] +<br>0.038   | V     |

| 0b010                        | RefPower = high                        | $V_{REFHI}$        | Ref High  | $V_{DD}$                                                | V <sub>DD</sub> – 0.119    | V <sub>DD</sub> – 0.005    | $V_{DD}$                   | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | $V_{DD}/2 - 0.028$         | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.029$         | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                         | V <sub>SS</sub>            | V <sub>SS</sub> + 0.004    | V <sub>SS</sub> + 0.022    | V     |

|                              | RefPower = high                        | $V_{REFHI}$        | Ref High  | $V_{DD}$                                                | V <sub>DD</sub> – 0.131    | V <sub>DD</sub> – 0.004    | $V_{DD}$                   | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | $V_{DD}/2 - 0.028$         | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.028$         | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                         | V <sub>SS</sub>            | V <sub>SS</sub> + 0.003    | V <sub>SS</sub> + 0.021    | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub>                                         | V <sub>DD</sub> – 0.111    | V <sub>DD</sub> – 0.003    | $V_{DD}$                   | V     |

|                              | Opamp bias = high                      | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | V <sub>DD</sub> /2 – 0.029 | V <sub>DD</sub> /2         | V <sub>DD</sub> /2 + 0.028 | V     |

|                              |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                         | V <sub>SS</sub>            | V <sub>SS</sub> + 0.002    | V <sub>SS</sub> + 0.017    | V     |

|                              | RefPower = medium                      | V <sub>REFHI</sub> | Ref High  | V <sub>DD</sub>                                         | V <sub>DD</sub> – 0.128    | V <sub>DD</sub> – 0.003    | $V_{DD}$                   | V     |

|                              | Opamp bias = low                       | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                      | V <sub>DD</sub> /2 – 0.029 | V <sub>DD</sub> /2         | V <sub>DD</sub> /2 + 0.029 | V     |

| ı                            |                                        | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                         | V <sub>SS</sub>            | V <sub>SS</sub> + 0.002    | V <sub>SS</sub> + 0.019    | V     |

Table 13. 3.3-V DC Analog Reference Specifications (continued)

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings                   | Symbol             | Reference | Description                                     | Min             | Тур                     | Max                     | Units |

|------------------------------|-----------------------------------------------|--------------------|-----------|-------------------------------------------------|-----------------|-------------------------|-------------------------|-------|

| 0b011                        | All power settings.<br>Not allowed for 3.3 V. | _                  | _         | -                                               | _               | _                       | _                       | -     |

| 0b100                        | All power settings.<br>Not allowed for 3.3 V. | _                  | _         | -                                               | -               | _                       | _                       | _     |

| 0b101                        | RefPower = high<br>Opamp bias = high          | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.214   | P2[4] + 1.291           | P2[4] + 1.359           | V     |

|                              |                                               | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                               | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.335   | P2[4] - 1.292           | P2[4] - 1.200           | V     |

|                              | RefPower = high<br>Opamp bias = low           | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.219   | P2[4] + 1.293           | P2[4] + 1.357           | V     |

|                              |                                               | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                               | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] - 1.335   | P2[4] - 1.295           | P2[4] - 1.243           | V     |

|                              | RefPower = medium<br>Opamp bias = high        | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.222   | P2[4] + 1.294           | P2[4] + 1.356           | V     |

|                              |                                               | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                               | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] – 1.337   | P2[4] - 1.296           | P2[4] - 1.244           | V     |

|                              | RefPower = medium<br>Opamp bias = low         | V <sub>REFHI</sub> | Ref High  | P2[4] + Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] + 1.224   | P2[4] + 1.295           | P2[4] + 1.355           | V     |

|                              |                                               | V <sub>AGND</sub>  | AGND      | P2[4]                                           | P2[4]           | P2[4]                   | P2[4]                   | -     |

|                              |                                               | V <sub>REFLO</sub> | Ref Low   | P2[4] – Bandgap<br>(P2[4] = V <sub>DD</sub> /2) | P2[4] - 1.339   | P2[4] - 1.297           | P2[4] - 1.244           | V     |

| 0b110                        | RefPower = high                               | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.510           | 2.595                   | 2.655                   | V     |

|                              | Opamp bias = high                             | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.276           | 1.301                   | 1.332                   | V     |

|                              |                                               | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.006 | V <sub>SS</sub> + 0.031 | V     |

|                              | RefPower = high                               | $V_{REFHI}$        | Ref High  | 2 × Bandgap                                     | 2.513           | 2.594                   | 2.656                   | V     |

|                              | Opamp bias = low                              | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.275           | 1.301                   | 1.331                   | V     |

|                              |                                               | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.004 | V <sub>SS</sub> + 0.021 | V     |

|                              | RefPower = medium                             | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.516           | 2.595                   | 2.657                   | V     |

|                              | Opamp bias = high                             | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.275           | 1.301                   | 1.331                   | V     |

|                              |                                               | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.003 | V <sub>SS</sub> + 0.017 | V     |

|                              | RefPower = medium                             | V <sub>REFHI</sub> | Ref High  | 2 × Bandgap                                     | 2.520           | 2.595                   | 2.658                   | V     |

|                              | Opamp bias = low                              | V <sub>AGND</sub>  | AGND      | Bandgap                                         | 1.275           | 1.300                   | 1.331                   | V     |

|                              |                                               | V <sub>REFLO</sub> | Ref Low   | V <sub>SS</sub>                                 | V <sub>SS</sub> | V <sub>SS</sub> + 0.002 | V <sub>SS</sub> + 0.015 | V     |

| 0b111                        | All power settings.<br>Not allowed for 3.3 V. | _                  | _         | -                                               | _               | _                       | _                       | _     |

### DC Analog PSoC Block Specifications

Table 14 lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40  $^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  85  $^{\circ}$ C, or 3.0 V to 3.6 V and -40  $^{\circ}$ C  $\leq$  T<sub>A</sub>  $\leq$  85  $^{\circ}$ C, respectively. Typical parameters apply to 5 V and 3.3 V at 25  $^{\circ}$ C and are for design guidance only.

Table 14. DC Analog PSoC Block Specifications

| Symbol          | Description                               | Min | Тур  | Max | Units | Notes |

|-----------------|-------------------------------------------|-----|------|-----|-------|-------|

| R <sub>CT</sub> | Resistor unit value (continuous time)     | _   | 12.2 | _   | kΩ    |       |

| C <sub>SC</sub> | Capacitor unit value (switched capacitor) | _   | 80   | 1   | fF    |       |

### DC POR and LVD Specifications

Table 15 lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and −40 °C ≤  $T_A \le 85$  °C, or 3.0 V to 3.6 V and -40 °C  $\le T_A \le 85$  °C, respectively. Typical parameters apply to 5 V or 3.3 V at 25 °C and are for design guidance only.

Note The bits PORLEV and VM in the table below refer to bits in the VLT\_CR register. See the PSoC Technical Reference Manual for more information on the VLT\_CR register.

Table 15. DC POR and LVD Specifications

| Symbol                                                                     | Description                                                                                                                                                                        | Min                                                          | Тур                                                          | Max                                                                   | Units                 | Notes                                                                                                                   |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| V <sub>PPOR0</sub> [7]<br>V <sub>PPOR1</sub> [7]<br>V <sub>PPOR2</sub> [7] | V <sub>DD</sub> Value for PPOR Trip (negative ramp) PORLEV[1:0] = 00b PORLEV[1:0] = 01b PORLEV[1:0] = 10b                                                                          | -<br>-<br>-                                                  | 2.82<br>4.39<br>4.55                                         | -<br>-<br>-                                                           | V<br>V<br>V           | V <sub>DD</sub> must be greater than or equal to 2.5 V during startup, reset from the XRES pin, or reset from watchdog. |

| V <sub>PH0</sub><br>V <sub>PH1</sub><br>V <sub>PH2</sub>                   | PPOR Hysteresis PORLEV[1:0] = 00b PORLEV[1:0] = 01b PORLEV[1:0] = 10b                                                                                                              | 1 1 1                                                        | 92<br>0<br>0                                                 | 1 1 1                                                                 | mV<br>mV<br>mV        |                                                                                                                         |

| VLVD0<br>VLVD1<br>VLVD2<br>VLVD3<br>VLVD4<br>VLVD5<br>VLVD6<br>VLVD7       | V <sub>DD</sub> Value for LVD Trip<br>VM[2:0] = 000b<br>VM[2:0] = 001b<br>VM[2:0] = 010b<br>VM[2:0] = 011b<br>VM[2:0] = 100b<br>VM[2:0] = 101b<br>VM[2:0] = 110b<br>VM[2:0] = 111b | 2.86<br>2.96<br>3.07<br>3.92<br>4.39<br>4.55<br>4.63<br>4.72 | 2.92<br>3.02<br>3.13<br>4.00<br>4.48<br>4.64<br>4.73<br>4.81 | 3.02 <sup>[8]</sup> 3.12 3.24 4.12 4.62 4.78 <sup>[9]</sup> 4.87 4.96 | V<br>V<br>V<br>V<br>V |                                                                                                                         |

#### Notes

Errata: When V<sub>DD</sub> of the device is pulled below ground just before power on, the first read from each 8K Flash page may be corrupted. This issue does not affect Flash page 0 because it is the selected page upon reset. More details in "Errata" on page 46.

Always greater than 50 mV above PPOR (PORLEV = 00) for falling supply.

Always greater than 50 mV above PPOR (PORLEV = 10) for falling supply.

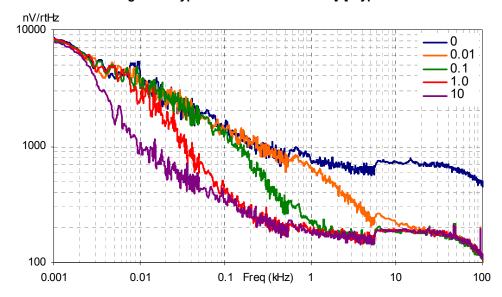

When bypassed by a capacitor on P2[4], the noise of the analog ground signal distributed to each block is reduced by a factor of up to 5 (14 dB). This is at frequencies above the corner frequency defined by the on-chip 8.1 k $\Omega$  resistance and the external capacitor.

Figure 6. Typical AGND Noise with P2[4] Bypass

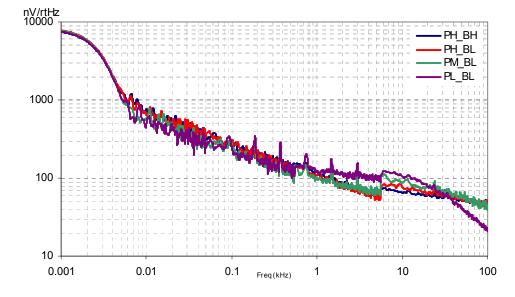

At low frequencies, the opamp noise is proportional to 1/f, power independent, and determined by device geometry. At high frequencies, increased power level reduces the noise spectrum level.

Figure 7. Typical Opamp Noise

Table 22. AC Digital Block Specifications (continued)

| Function | Description                                      | Min | Тур | Max                   | Units | Notes                               |

|----------|--------------------------------------------------|-----|-----|-----------------------|-------|-------------------------------------|

| Receiver | Input clock frequency                            |     |     |                       |       | The baud rate is equal to the input |

|          | $V_{DD} \ge 4.75 \text{ V}, 2 \text{ stop bits}$ | _   | _   | 49.92 <sup>[17]</sup> | MHz   | clock frequency divided by 8.       |

|          | $V_{DD} \ge 4.75 \text{ V}$ , 1 stop bit         | _   | _   | 25.92 <sup>[17]</sup> | MHz   |                                     |

|          | V <sub>DD</sub> < 4.75 V                         | _   | _   | 25.92 <sup>[17]</sup> | MHz   |                                     |

#### AC External Clock Specifications

Table 23 list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \text{ °C} \leq T_A \leq 85 \text{ °C}$ , or 3.0 V to 3.6 V and  $-40 \text{ °C} \leq T_A \leq 85 \text{ °C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

Table 23. AC External Clock Specifications

| Symbol              | Description            | Min  | Тур | Max   | Units | Notes |

|---------------------|------------------------|------|-----|-------|-------|-------|

| F <sub>OSCEXT</sub> | Frequency              | 0    | ı   | 24.24 | MHz   |       |

| -                   | High period            | 20.5 | ı   | ı     | ns    |       |

| -                   | Low period             | 20.5 | _   | _     | ns    |       |

| _                   | Power-up IMO to switch | 150  | _   | _     | μS    |       |

### AC Analog Output Buffer Specifications

Table 24 and Table 25 on page 33 list the guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \text{ °C} \leq T_A \leq 85 \text{ °C}$ , or 3.0 V to 3.6 V and  $-40 \text{ °C} \leq T_A \leq 85 \text{ °C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

Table 24. 5-V AC Analog Output Buffer Specifications

| Symbol             | Description                                                                                       | Min          | Тур      | Max        | Units                    | Notes |

|--------------------|---------------------------------------------------------------------------------------------------|--------------|----------|------------|--------------------------|-------|

| t <sub>ROB</sub>   | Rising settling time to 0.1%, 1 V step, 100pF load<br>Power = low<br>Power = high                 | - 1          | _<br>_   | 2.5<br>2.5 | μ <b>s</b><br>μ <b>s</b> |       |

| t <sub>SOB</sub>   | Falling settling time to 0.1%, 1 V step, 100pF load Power = low Power = high                      | _<br>_       |          | 2.2<br>2.2 | μ <b>s</b><br>μ <b>s</b> |       |

| SR <sub>ROB</sub>  | Rising slew rate (20% to 80%), 1 V step, 100 pF load<br>Power = low<br>Power = high               | 0.65<br>0.65 | _<br>_   | _<br>_     | V/μs<br>V/μs             |       |

| SR <sub>FOB</sub>  | Falling slew rate (80% to 20%), 1 V step, 100 pF load Power = low Power = high                    | 0.65<br>0.65 |          |            | V/μs<br>V/μs             |       |

| BW <sub>OBSS</sub> | Small signal bandwidth, 20 mV <sub>pp</sub> , 3 dB BW, 100 pF load<br>Power = low<br>Power = high | 0.8<br>0.8   |          |            | MHz<br>MHz               |       |

| BW <sub>OBLS</sub> | Large signal bandwidth, 1 V <sub>pp</sub> , 3 dB BW, 100 pF load<br>Power = low<br>Power = high   | 300<br>300   | <u>-</u> | -<br>-     | kHz<br>kHz               |       |

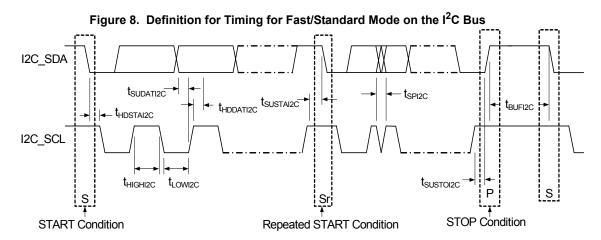

### AC I<sup>2</sup>C Specifications

Table 27 lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and  $-40 \text{ °C} \leq T_A \leq 85 \text{ °C}$ , or 3.0 V to 3.6 V and  $-40 \text{ °C} \leq T_A \leq 85 \text{ °C}$ , respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

Table 27. AC Characteristics of the  $I^2C$  SDA and SCL Pins for  $V_{DD}$

| Symbol                | Description                                                                                  |     | Standard Mode       |                     | Fast Mode           |       | Notes |

|-----------------------|----------------------------------------------------------------------------------------------|-----|---------------------|---------------------|---------------------|-------|-------|

| Symbol                |                                                                                              |     | Min Max             |                     | Max                 | Units | Notes |

| F <sub>SCLI2C</sub>   | SCL clock frequency                                                                          | 0   | 100 <sup>[20]</sup> | 0                   | 400 <sup>[20]</sup> | kHz   |       |

| t <sub>HDSTAI2C</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 4.0 | _                   | 0.6                 | -                   | μS    |       |

| t <sub>LOWI2C</sub>   | LOW period of the SCL clock                                                                  |     | _                   | 1.3                 | _                   | μS    |       |

| t <sub>HIGHI2C</sub>  | HIGH period of the SCL clock                                                                 |     | _                   | 0.6                 | _                   | μS    |       |

| t <sub>SUSTAI2C</sub> | Setup time for a repeated START condition                                                    |     | _                   | 0.6                 | _                   | μS    |       |

| t <sub>HDDATI2C</sub> | TI2C Data hold time                                                                          |     | _                   | 0                   | _                   | μS    |       |

| t <sub>SUDATI2C</sub> | Data setup time                                                                              |     | _                   | 100 <sup>[21]</sup> | _                   | ns    |       |

| t <sub>SUSTOI2C</sub> | Setup time for STOP condition                                                                |     | _                   | 0.6                 | _                   | μS    |       |

| t <sub>BUFI2C</sub>   | Bus free time between a stop and start condition                                             |     | _                   | 1.3                 | _                   | μS    |       |

| t <sub>SPI2C</sub>    | Pulse width of spikes are suppressed by the input filter.                                    |     | _                   | 0                   | 50                  | ns    |       |

### Notes

Document Number: 001-53754 Rev. \*H

<sup>20.</sup> F<sub>SCLI2C</sub> is derived from SysClk of the PSoC. This specification assumes that SysClk is operating at 24 MHz, nominal. If SysClk is at a lower frequency, then the F<sub>SCLI2C</sub> specification adjusts accordingly.

<sup>21.</sup> A Fast-Mode I2C-bus device can be used in a Standard-Mode I2C-bus system, but the requirement t<sub>SUDATI2C</sub> ≥ 250 ns must then be met. This is automatically the case if the device does not stretch the LOW period of the SCL signal. If such device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line t<sub>rmax</sub> + t<sub>SUDATI2C</sub> = 1000 + 250 = 1250 ns (according to the Standard-Mode I2C-bus specification) before the SCL line is released.

### **Tape and Reel Information**

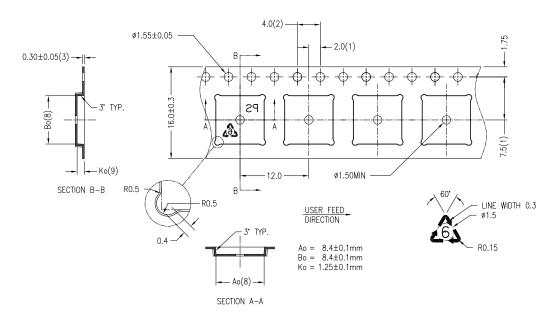

Figure 10. 56-Pin (8 × 8 mm) QFN (Punched) Carrier Tape Drawing

- (1). MEASURED FROM THE CENTERLINE OF SPROCKET HOLE TO CENTERLINE OF THE POCKET HOLE AND FROM THE CENTERLINE OF SPROCKET HOLE TO CENTERLINE OF THE POCKET.

(2). CUMULATIVE TOLERANCE OF 10 SPROCKET HOLES IS ±0.20

- (3). THIS THICKNESS IS APPLICABLE AS MEASURE AT THE EDGE OF THE TAPE.

4. MATERIAL:BLACK POLYSTYRFNF

- MATERIAL:BLACK POLYSTYRENE

DIMENSIONS ARE IN MILLIMETERS.

ALLOWABLE CAMBER TO BE 1MM PER 100MM IN LENGTH, NON-CUMULATIVE OVER 250MM.

UNLESS OTHERWISE SPECIFIED TOLERANCE ±0.10.

- (8). MEASUREMENT POINT TO BE 0.3 FROM BOTTOM POCKET.

- (9). Ko MEASUREMENT POINT SHOULD NOT BE REFERRED ON POCKET RIDGE.

10. SURFACE RESISTIVITY FROM 10<sup>5</sup> TO 10<sup>11</sup> OHMS/SQ

51-51165 \*C

Table 30. Tape and Reel Specifications

| Package    | Cover Tape<br>Width (mm) | Hub Size<br>(inches) | Minimum Leading<br>Empty Pockets | Minimum<br>Trailing Empty<br>Pockets | Standard Full Reel<br>Quantity |

|------------|--------------------------|----------------------|----------------------------------|--------------------------------------|--------------------------------|

| 56-Pin QFN | 13.1                     | 7                    | 42                               | 25                                   | 2000                           |

### Glossary (continued)

shift register A memory storage device that sequentially shifts a word either left or right to output a stream of serial data.

slave device A device that allows another device to control the timing for data exchanges between two devices. Or when

devices are cascaded in width, the slave device is the one that allows another device to control the timing of data exchanges between the cascaded devices and an external interface. The controlling device is called the master