Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Obsolete                                                             |

| Core Processor             | CPU32                                                                |

| Core Size                  | 32-Bit Single-Core                                                   |

| Speed                      | 16MHz                                                                |

| Connectivity               | EBI/EMI, SCI, SPI, UART/USART                                        |

| Peripherals                | POR, PWM, WDT                                                        |

| Number of I/O              | 18                                                                   |

| Program Memory Size        | -                                                                    |

| Program Memory Type        | ROMIess                                                              |

| EEPROM Size                | -                                                                    |

| RAM Size                   | -                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                          |

| Data Converters            | -                                                                    |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 132-BQFP Bumpered                                                    |

| Supplier Device Package    | 132-PQFP (24.13x24.13)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68331cfc16 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Table 1 Ordering Information**

| Package Type | Temperature    | Frequency<br>(MHz) | Package Order<br>Quantity | Order Number   |

|--------------|----------------|--------------------|---------------------------|----------------|

| 132-Pin PQFP | -40 to +85 °C  | 16 MHz             | 2 pc tray                 | SPAKMC331CFC16 |

|              |                |                    | 36 pc tray                | MC68331CFC16   |

|              |                | 20 MHz             | 2 pc tray                 | SPAKMC331CFC20 |

|              |                |                    | 36 pc tray                | MC68331CFC20   |

|              | −40 to +105 °C | 16 MHz             | 2 pc tray                 | SPAKMC331VFC16 |

|              |                |                    | 36 pc tray                | MC68331VFC16   |

|              |                | 20 MHz             | 2 pc tray                 | SPAKMC331VFC20 |

|              |                |                    | 36 pc tray                | MC68331VFC20   |

|              | −40 to +125 °C | 16 MHz             | 2 pc tray                 | SPAKMC331MFC16 |

|              |                |                    | 36 pc tray                | MC68331MFC16   |

|              |                | 20 MHz             | 2 pc tray                 | SPAKMC331MFC20 |

|              |                |                    | 36 pc tray                | MC68331MFC20   |

| 144-Pin QFP  | −40 to +85 °C  | 16 MHz             | 2 pc tray                 | SPAKMC331CFV16 |

|              |                |                    | 44 pc tray                | MC68331CFV16   |

|              |                | 20 MHz             | 2 pc tray                 | SPAKMC331CFV20 |

|              |                |                    | 44 pc tray                | MC68331CFV20   |

|              | −40 to +105 °C | 16 MHz             | 2 pc tray                 | SPAKMC331VFV16 |

|              |                |                    | 44 pc tray                | MC68331VFV16   |

|              |                | 20 MHz             | 2 pc tray                 | SPAKMC331VFV20 |

|              |                |                    | 44 pc tray                | MC68331VFV20   |

|              | −40 to +125 °C | 16 MHz             | 2 pc tray                 | SPAKMC331MFV16 |

|              |                |                    | 44 pc tray                | MC68331MFV16   |

|              |                | 20 MHz             | 2 pc tray                 | SPAKMC331MFV20 |

|              |                |                    | 44 pc tray                | MC68331MFV20   |

| Se | ection                                                      |                                                                                                                                                                                           | Page                                   |

|----|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| 1  | 1.1<br>1.2<br>1.3<br>1.4<br>1.5                             | Introduction Features Block Diagram Pin Assignments Address Map Intermodule Bus                                                                                                           | 5<br>6<br>8                            |

| 2  | 2.1<br>2.2<br>2.3<br>2.4<br>2.5                             | Signal Descriptions Pin Characteristics MCU Power Connections MCU Driver Types Signal Characteristics Signal Function                                                                     | 10<br>10<br>10                         |

| 3  | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9 | System Integration Module Overview System Configuration and Protection System Clock External Bus Interface Chip Selects General-Purpose Input/Output Resets Interrupts Factory Test Block |                                        |

| 4  | 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7               | Central Processor Unit Overview                                                                                                                                                           | 43<br>43<br>43<br>45<br>45<br>45<br>45 |

| 5  | 5.1<br>5.2<br>5.3<br>5.4<br>5.5                             | Queued Serial Module Overview                                                                                                                                                             | 52<br>53<br>56                         |

| 6  | 6.1<br>6.2<br>6.3<br>6.4                                    | General-Purpose Timer Module Overview Capture/Compare Unit Pulse-Width Modulator GPT Registers                                                                                            | <b>70</b><br>70<br>71<br>74            |

| 7  |                                                             | Summary of Changes                                                                                                                                                                        | 82                                     |

#### 1.1 Features

- Modular Architecture

- Central Processing Unit (CPU32)

- Upward Object Code Compatible

- New Instructions for Controller Applications

- 32-Bit Architecture

- Virtual Memory Implementation

- Loop Mode of Instruction Execution

- Table Lookup and Interpolate Instruction

- Improved Exception Handling for Controller Applications

- Trace on Change of Flow

- Hardware Breakpoint Signal, Background Mode

- Fully Static Operation

- System Integration Module (SIM)

- External Bus Support

- Programmable Chip-Select Outputs

- System Protection Logic

- Watchdog Timer, Clock Monitor, and Bus Monitor

- System Protection Logic

- System Clock Based on 32.768-kHz Crystal for Low Power Operation

- Test/Debug Submodule for Factory/User Test and Development

- Queued Serial Module (QSM)

- Enhanced Serial Communication Interface (SCI), Universal Asynchronous Receiver Transmitter (UART): Modulus Baud Rate, Parity

- Queued Serial Peripheral Interface (QSPI): 80-Byte RAM, Up to 16 Automatic Transfers

- Dual Function I/O Ports

- Continuous Cycling, 8 to 16 Bits per Transfer

- General-Purpose Timer (GPT)

- Two 16-Bit Free-Running Counters With One Nine-Stage Prescaler

- Three Input Capture Channels

- Four Output Compare Channels

- One Input Capture/Output Compare Channel

- One Pulse Accumulator/Event Counter Input

- Two Pulse-Width Modulation Outputs

- Optional External Clock Input

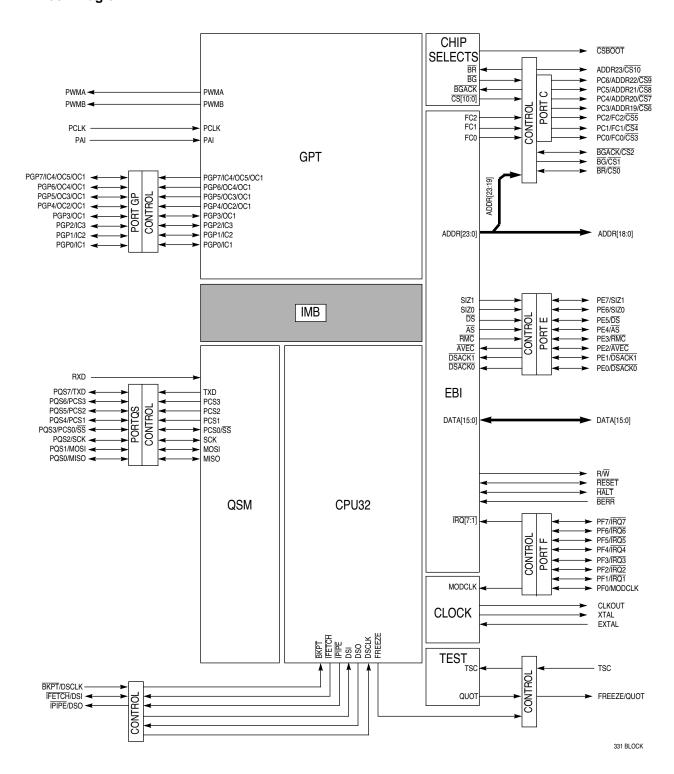

#### 1.2 Block Diagram

Figure 1 MCU Block Diagram

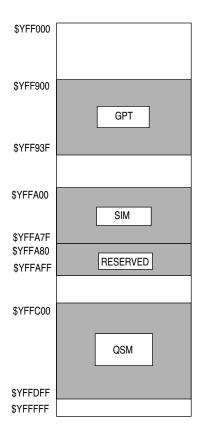

#### 1.4 Address Map

The following figure is a map of the MCU internal addresses. Unimplemented blocks are mapped externally.

331 ADDRESS MAP

Figure 4 MCU Address Map

#### 1.5 Intermodule Bus

The intermodule bus (IMB) is a standardized bus developed to facilitate both design and operation of modular microcontrollers. It contains circuitry to support exception processing, address space partitioning, multiple interrupt levels, and vectored interrupts. The standardized modules in the MCU communicate with one another and with external components through the IMB. The IMB in the MCU uses 24 address and 16 data lines.

**Table 5 MCU Signal Characteristics (Continued)**

| Signal Name | MCU Module | Signal Type  | Active State  |

|-------------|------------|--------------|---------------|

| DSACK[1:0]  | SIM        | Input        | 0             |

| DSCLK       | CPU32      | Input        | Serial Clock  |

| DSI         | CPU32      | Input        | (Serial Data) |

| DSO         | CPU32      | Output       | (Serial Data) |

| EXTAL       | SIM        | Input        | _             |

| FC[2:0]     | SIM        | Output       | _             |

| FREEZE      | SIM        | Output       | 1             |

| HALT        | SIM        | Input/Output | 0             |

| IC[4:1]     | GPT        | Input        | _             |

| ĪFETCH      | CPU32      | Output       | _             |

| ĪPIPĒ       | CPU32      | Output       | _             |

| ĪRQ[7:1]    | SIM        | Input        | 0             |

| MISO        | QSM        | Input/Output | _             |

| MODCLK      | SIM        | Input        | _             |

| MOSI        | QSM        | Input/Output | _             |

| OC[5:1]     | GPT        | Output       | _             |

| PAI         | GPT        | Input        | _             |

| PC[6:0]     | SIM        | Output       | (Port)        |

| PCS[3:0]    | QSM        | Input/Output | _             |

| PE[7:0]     | SIM        | Input/Output | (Port)        |

| PF[7:0]     | SIM        | Input/Output | (Port)        |

| PQS[7:0]    | QSM        | Input/Output | (Port)        |

| PCLK        | GPT        | Input        | _             |

| PWMA, PWMB  | GPT        | Output       | _             |

| QUOT        | SIM        | Output       | _             |

| RESET       | SIM        | Input/Output | 0             |

| RMC         | SIM        | Output       | 0             |

| R/W         | SIM        | Output       | 1/0           |

| RXD         | QSM        | Input        | _             |

| SCK         | QSM        | Input/Output | _             |

| SIZ[1:0]    | SIM        | Output       | _             |

| SS          | QSM        | Input        | 0             |

| TSC         | SIM        | Input        | _             |

| TXD         | QSM        | Output       | _             |

| XFC         | SIM        | Input        | _             |

| XTAL        | SIM        | Output       | _             |

#### 2.5 Signal Function

### **Table 6 MCU Signal Function**

| Signal Name           | Mnemonic   | Function                                                     |

|-----------------------|------------|--------------------------------------------------------------|

| Address Bus           | ADDR[23:0] | 24-bit address bus                                           |

| Address Strobe        | ĀS         | Indicates that a valid address is on the address bus         |

| Autovector            | AVEC       | Requests an automatic vector during interrupt acknowledge    |

| Bus Error             | BERR       | Indicates that a bus error has occurred                      |

| Bus Grant             | BG         | Indicates that the MCU has relinquished the bus              |

| Bus Grant Acknowledge | BGACK      | Indicates that an external device has assumed bus mastership |

| Breakpoint            | BKPT       | Signals a hardware breakpoint to the CPU                     |

| Bus Request           | BR         | Indicates that an external device requires bus mastership    |

| System Clockout       | CLKOUT     | System clock output                                          |

| Chip Selects          | CS[10:0]   | Select external devices at programmed addresses              |

#### 3.2.5 Spurious Interrupt Monitor

The spurious interrupt monitor issues  $\overline{\text{BERR}}$  if no interrupt arbitration occurs during an interrupt-acknowledge cycle.

#### 3.2.6 Software Watchdog

The software watchdog is controlled by SWE in the SYPCR. Once enabled, the watchdog requires that a service sequence be written to SWSR on a periodic basis. If servicing does not take place, the watchdog times out and issues a reset. This register can be written at any time, but returns zeros when read.

| <b>SWSR</b> —Software Service Register |   |   |   |   |   |   |   | \$YF | FFA27 |

|----------------------------------------|---|---|---|---|---|---|---|------|-------|

| 15                                     | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1    | 0     |

| NOT USED                               |   | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0     |

| RESET:                                 |   |   | • | • |   |   |   |      |       |

|                                        |   | 0 | 0 | 0 | 0 | 0 | 0 | 0    | 0     |

Register shown with read value

Perform a software watchdog service sequence as follows:

- 1. Write \$55 to SWSR.

- 2. Write \$AA to SWSR.

Both writes must occur before time-out in the order listed, but any number of instructions can be executed between the two writes.

The watchdog clock rate is affected by SWP and SWT in SYPCR. When SWT[1:0] are modified, a watchdog service sequence must be performed before the new time-out period takes effect.

The reset value of SWP is affected by the state of the MODCLK pin on the rising edge of reset, as shown in the following table.

| MODCLK | SWP |

|--------|-----|

| 0      | 1   |

| 1      | 0   |

#### 3.2.7 Periodic Interrupt Timer

The periodic interrupt timer (PIT) generates interrupts of specified priorities at specified intervals. Timing for the PIT is provided by a programmable prescaler driven by the system clock.

| PICR — | - Perio | dic Inte | errupt ( | Control | Regis | ter   |   |   |   |   |    |   |   | \$YF | FA22 |

|--------|---------|----------|----------|---------|-------|-------|---|---|---|---|----|---|---|------|------|

| 15     | 14      | 13       | 12       | 11      | 10    |       | 8 | 7 |   |   |    |   |   |      | 0    |

| 0      | 0       | 0        | 0        | 0       |       | PIRQL |   |   |   |   | Pl | V |   |      |      |

| RESET: |         |          |          |         |       |       |   | • |   |   |    |   |   |      |      |

| 0      | 0       | 0        | 0        | 0       | 0     | 0     | 0 | 0 | 0 | 0 | 0  | 1 | 1 | 1    | 1    |

This register contains information concerning periodic interrupt priority and vectoring. Bits [10:0] can be read or written at any time. Bits [15:11] are unimplemented and always return zero.

#### PIRQL[2:0] —Periodic Interrupt Request Level

The following table shows what interrupt request level is asserted when a periodic interrupt is generated. If a PIT interrupt and an external  $\overline{IRQ}$  signal of the same priority occur simultaneously, the PIT interrupt is serviced first. The periodic timer continues to run when the interrupt is disabled.

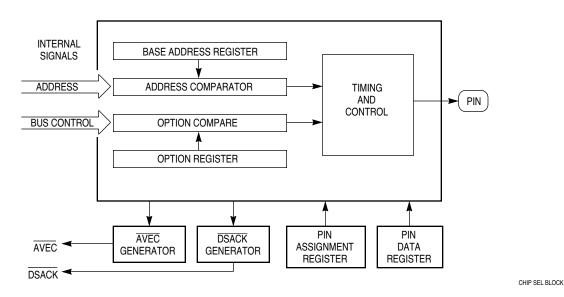

Figure 9 Chip-Select Circuit Block Diagram

The following table lists allocation of chip-selects and discrete outputs on the pins of the MCU.

| Pin    | Chip Select | Discrete Outputs |

|--------|-------------|------------------|

| CSBOOT | CSBOOT      | _                |

| BR     | CS0         | _                |

| BG     | CS1         | _                |

| BGACK  | CS2         | _                |

| FC0    | CS3         | PC0              |

| FC1    | CS4         | PC1              |

| FC2    | CS5         | PC2              |

| ADDR19 | CS6         | PC3              |

| ADDR20 | CS7         | PC4              |

| ADDR21 | CS8         | PC5              |

| ADDR22 | CS9         | PC6              |

| ADDR23 | CS10        | ECLK             |

#### 3.5.1 Chip-Select Registers

Pin assignment registers CSPAR0 and CSPAR1 determine functions of chip-select pins. These registers also determine port size (8- or 16-bit) for dynamic bus allocation.

A pin data register (PORTC) latches discrete output data.

Blocks of addresses are assigned to each chip-select function. Block sizes of 2 Kbytes to 1 Mbyte can be selected by writing values to the appropriate base address register (CSBAR). Address blocks for separate chip-select functions can overlap.

Chip-select option registers (CSORBT and CSOR[10:0]) determine timing of and conditions for assertion of chip-select signals. Eight parameters, including operating mode, access size, synchronization, and wait state insertion can be specified.

Initialization code often resides in a peripheral memory device controlled by the chip-select circuits. A set of special chip-select functions and registers (CSORBT, CSBARBT) is provided to support bootstrap operation.

| Byte | Description |

|------|-------------|

| 00   | Disable     |

| 01   | Lower Byte  |

| 10   | Upper Byte  |

| 11   | Both Bytes  |

#### R/W —Read/Write

This field causes a chip select to be asserted only for a read, only for a write, or for both read and write. Refer to the following table for options available.

| R/W | Description |

|-----|-------------|

| 00  | Reserved    |

| 01  | Read Only   |

| 10  | Write Only  |

| 11  | Read/Write  |

STRB —Address Strobe/Data Strobe

0 = Address strobe

1 = Data strobe

This bit controls the timing for assertion of a chip select in asynchronous mode. Selecting address strobe causes chip select to be asserted synchronized with address strobe. Selecting data strobe causes chip select to be asserted synchronized with data strobe.

#### DSACK —Data and Size Acknowledge

This field specifies the source of  $\overline{DSACK}$  in asynchronous mode. It also allows the user to adjust bus timing with internal  $\overline{DSACK}$  generation by controlling the number of wait states that are inserted to optimize bus speed in a particular application. The following table shows the  $\overline{DSACK}$  field encoding. The fast termination encoding (1110) is used for two-cycle access to external memory.

| DSACK | Description      |

|-------|------------------|

| 0000  | No Wait States   |

| 0001  | 1 Wait State     |

| 0010  | 2 Wait States    |

| 0011  | 3 Wait States    |

| 0100  | 4 Wait States    |

| 0101  | 5 Wait States    |

| 0110  | 6 Wait States    |

| 0111  | 7 Wait States    |

| 1000  | 8 Wait States    |

| 1001  | 9 Wait States    |

| 1010  | 10 Wait States   |

| 1011  | 11 Wait States   |

| 1100  | 12 Wait States   |

| 1101  | 13 Wait States   |

| 1110  | Fast Termination |

| 1111  | External DSACK   |

#### PORTF0, PORTF1 — Port F Data Register \$YFFA19, \$YFFA1B 1 0 15 7 NOT USED PF5 PF4 PF0 PF7 PF6 PF3 PF2 PF1 RESET: U U U U

The write to the port F data register is stored in the internal data latch, and if any port F pin is configured as an output, the value stored for that bit is driven onto the pin. A read of the port F data register returns the value at the pin only if the pin is configured as a discrete input. Otherwise, the value read is the value stored in the register.

The port F data register is a single register that can be accessed in two locations. When accessed at \$YFFA19, the register is referred to as PORTF0; when accessed at \$YFFA1B, the register is referred to as PORTF1. The register can be read or written at any time. It is unaffected by reset.

| <b>DDRF</b> — Port F Data Direction Register |   |      |      |      |      |      | \$YF | FA1D |      |

|----------------------------------------------|---|------|------|------|------|------|------|------|------|

| 15                                           | 8 | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| NOT USED                                     |   | DDF7 | DDF6 | DDF5 | DDF4 | DDF3 | DDF2 | DDF1 | DDF0 |

| RESET:                                       |   |      |      |      |      |      | •    | •    |      |

|                                              |   | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

The bits in this register control the direction of the pin drivers when the pins are configured for I/O. Any bit in this register set to one configures the corresponding pin as an output. Any bit in this register cleared to zero configures the corresponding pin as an input.

| Р | FPAR — Port F Pin Assignment Register |   |       |       |       |       |       |       | \$YF  | -FA1F |

|---|---------------------------------------|---|-------|-------|-------|-------|-------|-------|-------|-------|

|   | 15                                    | 8 | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|   | NOT USED                              |   | PFPA7 | PFPA6 | PFPA5 | PFPA4 | PFPA3 | PFPA2 | PFPA1 | PFPA0 |

|   | RESET:                                |   |       |       |       |       |       |       |       |       |

DATA9 DATA9 DATA9 DATA9 DATA9 DATA9

The bits in this register control the function of each port F pin. Any bit cleared to zero defines the corresponding pin to be an I/O pin. Any bit set to one defines the corresponding pin to be an interrupt request signal or MODCLK. The MODCLK signal has no function after reset.

**Table 17 Port F Pin Assignments**

| PFPAR Field | Port F Signal | Alternate Signal |

|-------------|---------------|------------------|

| PFPA7       | PF7           | ĪRQ7             |

| PFPA6       | PF6           | ĪRQ6             |

| PFPA5       | PF5           | ĪRQ5             |

| PFPA4       | PF4           | ĪRQ4             |

| PFPA3       | PF3           | ĪRQ3             |

| PFPA2       | PF2           | ĪRQ2             |

| PFPA1       | PF1           | ĪRQ1             |

| PFPA0       | PF0           | MODCLK           |

Data bus pin 9 controls the state of this register following reset. If DATA9 is set to one during reset, the register is set to \$FF, which defines all port F pins as interrupt request inputs. If DATA9 is cleared to zero during reset, this register is set to \$00, defining all port F pins as I/O pins.

The SIM clock synthesizer provides clock signals to the other MCU modules. After the clock is running and the internal reset signal is asserted for four clock cycles, these modules reset.  $V_{DD}$  ramp time and VCO frequency ramp time determine how long these four cycles take. Worst case is approximately 15 milliseconds. During this period, module port pins may be in an indeterminate state. While input-only pins can be put in a known state by means of external pull-up resistors, external logic on input/output or output-only pins must condition the lines during this time. Active drivers require high-impedance buffers or isolation resistors to prevent conflict.

#### 3.7.5 Use of Three State Control Pin

Asserting the three-state control (TSC) input causes the MCU to put all output drivers in an inactive, high-impedance state. The signal must remain asserted for 10 clock cycles in order for drivers to change state. There are certain constraints on use of TSC during power-on reset:

When the internal clock synthesizer is used (MODCLK held high during reset), synthesizer rampup time affects how long the 10 cycles take. Worst case is approximately 20 milliseconds from TSC assertion.

When an external clock signal is applied (MODCLK held low during reset), pins go to high-impedance state as soon after TSC assertion as 10 clock pulses have been applied to the EXTAL pin.

When TSC assertion takes effect, internal signals are forced to values that can cause inadvertent mode selection. Once the output drivers change state, the MCU must be powered down and restarted before normal operation can resume.

#### 3.8 Interrupts

Interrupt recognition and servicing involve complex interaction between the central processing unit, the system integration module, and a device or module requesting interrupt service.

The CPU32 provides for eight levels of interrupt priority (0–7), seven automatic interrupt vectors and 200 assignable interrupt vector. All interrupts with priorities less than 7 can be masked by the interrupt priority (IP) field in the status register. The CPU32 handles interrupts as a type of asynchronous exception.

Interrupt recognition is based on the states of interrupt request signals  $\overline{IRQ[7:1]}$  and the IP mask value. Each of the signals corresponds to an interrupt priority.  $\overline{IRQ1}$  has the lowest priority, and  $\overline{IRQ7}$  has the highest priority.

The IP field consists of three bits. Binary values %000 to %111 provide eight priority masks. Masks prevent an interrupt request of a priority less than or equal to the mask value (except for IRQ7) from being recognized and processed. When IP contains %000, no interrupt is masked. During exception processing, the IP field is set to the priority of the interrupt being serviced.

Interrupt request signals can be asserted by external devices or by microcontroller modules. Request lines are connected internally by means of a wired NOR — simultaneous requests of differing priority can be made. Internal assertion of an interrupt request signal does not affect the logic state of the corresponding MCU pin.

External interrupt requests are routed to the CPU via the external bus interface and SIM interrupt control logic. The CPU treats external interrupt requests as though they come from the SIM.

External IRQ[6:1] are active-low level-sensitive inputs. External IRQ7 is an active-low transition-sensitive input. IRQ7 requires both an edge and a voltage level for validity.

IRQ[6:1] are maskable. IRQ7 is nonmaskable. The IRQ7 input is transition-sensitive in order to prevent redundant servicing and stack overflow. A nonmaskable interrupt is generated each time IRQ7 is asserted, and each time the priority mask changes from %111 to a lower number while IRQ7 is asserted.

#### **4 Central Processor Unit**

Based on the powerful MC68020, the CPU32 processing module provides enhanced system performance and also uses the extensive software base for the Motorola M68000 family.

#### 4.1 Overview

The CPU32 is fully object code compatible with the M68000 Family, which excels at processing calculation-intensive algorithms and supporting high-level languages. The CPU32 supports all of the MC68010 and most of the MC68020 enhancements, such as virtual memory support, loop mode operation, instruction pipeline, and 32-bit mathematical operations. Powerful addressing modes provide compatibility with existing software programs and increase the efficiency of high-level language compilers. Special instructions, such as table lookup and interpolate and low-power stop, support the specific requirements of controller applications. Also included is the background debugging mode, an alternate operating mode that suspends normal operation and allows the CPU to accept debugging commands from the development system.

Ease of programming is an important consideration in using a microcontroller. The CPU32 instruction set is optimized for high performance. The eight 32-bit general-purpose data registers readily support 8-bit (byte), 16-bit (word), and 32-bit (long word) operations. Ease of program checking and diagnosis is further enhanced by trace and trap capabilities at the instruction level.

Use of high-level languages is increasing as controller applications become more complex and control programs become larger. High-level languages aid rapid development of software, with less error, and are readily portable. The CPU32 instruction set supports high-level languages.

#### 4.2 Programming Model

The CPU32 has sixteen 32-bit general registers, a 32-bit program counter, one 32-bit supervisor stack pointer, a 16-bit status register, two alternate function code registers, and a 32-bit vector base register.

The programming model of the CPU32 consists of a user model and supervisor model, corresponding to the user and supervisor privilege levels. Some instructions available at the supervisor level are not available at the user level, allowing the supervisor to protect system resources from uncontrolled access. Bit S in the status register determines the privilege level.

The user programming model remains unchanged from previous M68000 Family microprocessors. Application software written to run at the nonprivileged user level migrates without modification to the CPU32 from any M68000 platform. The move from SR instruction, however, is privileged in the CPU32. It is not privileged in the M68000.

#### 4.3 Status Register

The status register contains the condition codes that reflect the results of a previous operation and can be used for conditional instruction execution in a program. The lower byte containing the condition codes is the only portion of the register available at the user privilege level; it is referenced as the condition code register (CCR) in user programs. At the supervisor privilege level, software can access the full status register, including the interrupt priority mask and additional control bits.

#### **SR** —Status Register

| 15     | 14 | 13 | 12 | 11 | 10 |    | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|

| T1     | T0 | S  | 0  | 0  |    | ΙP |   | 0 | 0 | 0 | Х | N | Z | V | С |

| RESET: | •  | •  | •  |    |    |    |   |   |   |   |   |   | • |   |   |

| 0      | 0  | 1  | 0  | 0  | 1  | 1  | 1 | 0 | 0 | 0 | U | U | U | U | U |

#### System Byte

T[1:0] —Trace Enable

S —Supervisor/User State

Bits [12:11] —Unimplemented

IP[2:0] —Interrupt Priority Mask

#### User Byte (Condition Code Register)

Bits [7:5] —Unimplemented

X —Extend

N —Negative

Z —Zero

V —Overflow

C —Carry

#### 4.4 Data Types

Six basic data types are supported:

- Bits

- · Packed Binary Coded Decimal Digits

- Byte Integers (8 bits)

- Word Integers (16 bits)

- Long-Word Integers (32 bits)

- Quad-Word Integers (64 bits)

#### 4.5 Addressing Modes

Addressing in the CPU32 is register-oriented. Most instructions allow the results of the specified operation to be placed either in a register or directly in memory. This flexibility eliminates the need for extra instructions to store register contents in memory. The CPU32 supports seven basic addressing modes:

- Register direct

- Register indirect

- Register indirect with index

- · Program counter indirect with displacement

- · Program counter indirect with index

- Absolute

- Immediate

Included in the register indirect addressing modes are the capabilities to post-increment, predecrement, and offset. The program counter relative mode also has index and offset capabilities. In addition to these addressing modes, many instructions implicitly specify the use of the status register, stack pointer, or program counter.

#### 4.7 Background Debugging Mode

The background debugger on the CPU32 is implemented in CPU microcode. The background debugging commands are summarized below.

**Table 21 Background Debugging Mode**

| Command               | Mnemonic    | Description                                                                                                                                                                                                                               |

|-----------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read D/A Register     | RDREG/RAREG | Read the selected address or data register and return the results through the serial interface.                                                                                                                                           |

| Write D/A Register    | WDREG/WAREG | The data operand is written to the specified address or data register.                                                                                                                                                                    |

| Read System Register  | RSREG       | The specified system control register is read. All registers that can be read in supervisor mode can be read in background mode.                                                                                                          |

| Write System Register | WSREG       | The operand data is written into the specified system control register.                                                                                                                                                                   |

| Read Memory Location  | READ        | Read the sized data at the memory location specified by the long-word address. The source function code register (SFC) determines the address space accessed.                                                                             |

| Write Memory Location | WRITE       | Write the operand data to the memory location specified by the long-word address. The destination function code (DFC) register determines the address space accessed.                                                                     |

| Dump Memory Block     | DUMP        | Used in conjunction with the READ command to dump large blocks of memory. An initial READ is executed to set up the starting address of the block and retrieve the first result. Subsequent operands are retrieved with the DUMP command. |

| Fill Memory Block     | FILL        | Used in conjunction with the WRITE command to fill large blocks of memory. Initially, a WRITE is executed to set up the starting address of the block and supply the first operand. The FILL command writes subsequent operands.          |

| Resume Execution      | GO          | The pipe is flushed and refilled before resuming instruction execution at the current PC.                                                                                                                                                 |

| Patch User Code       | CALL        | Current program counter is stacked at the location of the current stack pointer. Instruction execution begins at user patch code.                                                                                                         |

| Reset Peripherals     | RST         | Asserts RESET for 512 clock cycles. The CPU is not reset by this command. Synonymous with the CPU RESET instruction.                                                                                                                      |

| No Operation          | NOP         | NOP performs no operation and can be used as a null command.                                                                                                                                                                              |

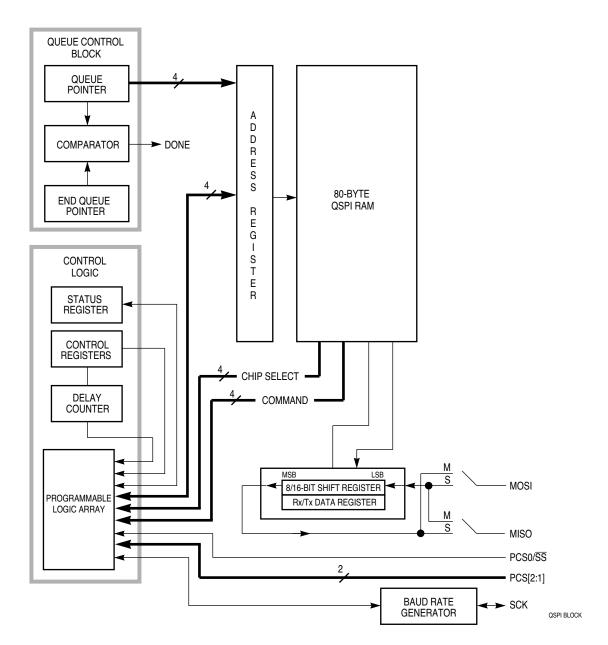

Figure 13 QSPI Block Diagram

#### 5.4.1 QSPI Pins

Seven pins are associated with the QSPI. When not needed for a QSPI application, they can be configured as general-purpose I/O pins. The PCS0/SS pin can function as a peripheral chip select output, slave select input, or general-purpose I/O. Refer to the following table for QSPI input and output pins and their functions.

#### **5.5.1 SCI Pins**

There are two unidirectional pins associated with the SCI. The SCI controls the transmit data (TXD) pin when enabled, whereas the receive data (RXD) pin remains a dedicated input pin to the SCI. TXD is available as a general-purpose I/O pin when the SCI transmitter is disabled. When used for I/O, TXD can be configured either as input or output, as determined by QSM register DDRQS.

The following table shows SCI pins and their functions.

| Pin Names     | Mnemonics | Mode                                        | Function                                           |  |  |  |

|---------------|-----------|---------------------------------------------|----------------------------------------------------|--|--|--|

| Receive Data  | RXD       | Receiver Disabled<br>Receiver Enabled       | Not Used<br>Serial Data Input to SCI               |  |  |  |

| Transmit Data | TXD       | Transmitter Disabled<br>Transmitter Enabled | General-Purpose I/O<br>Serial Data Output from SCI |  |  |  |

#### 5.5.2 SCI Registers

The SCI programming model includes QSM global and pin control registers, and four SCI registers. There are two SCI control registers, one status register, and one data register. All registers can be read or written at any time by the CPU.

Changing the value of SCI control bits during a transfer operation may disrupt operation. Before changing register values, allow the transmitter to complete the current transfer, then disable the receiver and transmitter. Status flags in the SCSR may be cleared at any time.

| SCCR0 — SCI Control Register 0 \$YFF |        |    |    |    |      |   |  |  |  |  |  |  |

|--------------------------------------|--------|----|----|----|------|---|--|--|--|--|--|--|

|                                      | 15     | 14 | 13 | 12 |      | 0 |  |  |  |  |  |  |

|                                      | 0      | 0  | 0  |    | SCBR |   |  |  |  |  |  |  |

|                                      | RESET: | •  | ,  |    |      |   |  |  |  |  |  |  |

SCCR0 contains a baud rate selection parameter. Baud rate must be set before the SCI is enabled. The CPU can read and write this register at any time.

Bits [15:13] — Not Implemented

#### SCBR — Baud Rate

SCI baud rate is programmed by writing a 13-bit value to BR. The baud rate is derived from the MCU system clock by a modulus counter.

The SCI receiver operates asynchronously. An internal clock is necessary to synchronize with an incoming data stream. The SCI baud rate generator produces a receiver sampling clock with a frequency 16 times that of the expected baud rate of the incoming data. The SCI determines the position of bit boundaries from transitions within the received waveform, and adjusts sampling points to the proper positions within the bit period. Receiver sampling rate is always 16 times the frequency of the SCI baud rate, which is calculated as follows:

SCI Baud Rate = System Clock/(32SCBR)

or

SCBR = System Clock(32SCK)(Baud Rate Desired)

where SCBR is in the range {1, 2, 3, ..., 8191}

Writing a value of zero to SCBR disables the baud rate generator.

The following table lists the SCBR settings for standard and maximum baud rates using 16.78-MHz and 20.97-MHz system clocks.

#### RAF — Receiver Active Flag

- 0 = SCI receiver is idle

- 1 = SCI receiver is busy

RAF indicates whether the SCI receiver is busy. It is set when the receiver detects a possible start bit and is cleared when the chosen type of idle line is detected. RAF can be used to reduce collisions in systems with multiple masters.

#### IDLE — Idle-Line Detected Flag

- 0 = SCI receiver did not detect an idle-line condition.

- 1 = SCI receiver detected an idle-line condition.

IDLE is disabled when RWU in SCCR1 is set. IDLE is set when the SCI receiver detects the idle-line condition specified by ILT in SCCR1. If cleared, IDLE will not set again until after RDRF is set. RDRF is set when a break is received, so that a subsequent idle line can be detected.

#### OR — Overrun Error Flag

- 0 = RDRF is cleared before new data arrives.

- 1 = RDRF is not cleared before new data arrives.

OR is set when a new byte is ready to be transferred from the receive serial shifter to the RDR, and RDRF is still set. Data transfer is inhibited until OR is cleared. Previous data in RDR remains valid, but data received during overrun condition (including the byte that set OR) is lost.

#### NF — Noise Error Flag

- 0 = No noise detected on the received data

- 1 = Noise occurred on the received data

NF is set when the SCI receiver detects noise on a valid start bit, on any data bit, or on a stop bit. It is not set by noise on the idle line or on invalid start bits. Each bit is sampled three times. If none of the three samples are the same logic level, the majority value is used for the received data value, and NF is set. NF is not set until an entire frame is received and RDRF is set.

#### FE — Framing Error Flag

- 0 = No framing error on the received data.

- 1 = Framing error or break occurred on the received data.

FE is set when the SCI receiver detects a zero where a stop bit was to have occurred. FE is not set until the entire frame is received and RDRF is set. A break can also cause FE to be set. It is possible to miss a framing error if RXD happens to be at logic level one at the time the stop bit is expected.

#### PF — Parity Error Flag

- 0 = No parity error on the received data

- 1 = Parity error occurred on the received data

PF is set when the SCI receiver detects a parity error. PF is not set until the entire frame is received and RDRF is set.

#### **SCDR** — SCI Data Register

\$YFFC0E

| 15     | 14 | 13 | 12 | 11 | 10 | 9 | 8     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|----|----|----|----|----|---|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0      | 0  | 0  | 0  | 0  | 0  | 0 | R8/T8 | R7/T7 | R6/T6 | R5/T5 | R4/T4 | R3/T3 | R2/T2 | R1/T1 | R0/T0 |

| RESET: |    |    |    |    |    |   |       |       |       |       |       |       |       |       |       |

| 0      | 0  | 0  | 0  | 0  | 0  | 0 | U     | U     | U     | U     | U     | U     | U     | U     | U     |

SCDR contains two data registers at the same address. Receive data register (RDR) is a read-only register that contains data received by the SCI. The data comes into the receive serial shifter and is transferred to RDR. Transmit data register (TDR) is a write-only register that contains data to be transmitted. The data is first written to TDR, then transferred to the transmit serial shifter, where additional format bits are added before transmission. R[7:0]/T[7:0] contain either the first eight data bits received when SCDR is read, or the first eight data bits to be transmitted when SCDR is written. R8/T8 are used when the SCI is configured for 9-bit operation. When it is configured for 8-bit operation, they have no meaning or effect.

#### 6 General-Purpose Timer Module

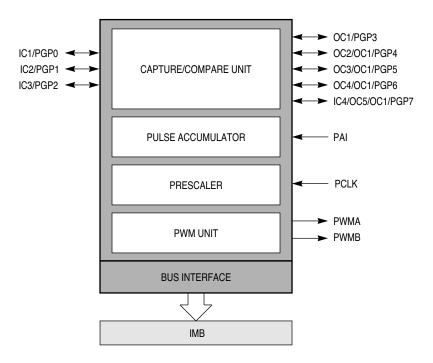

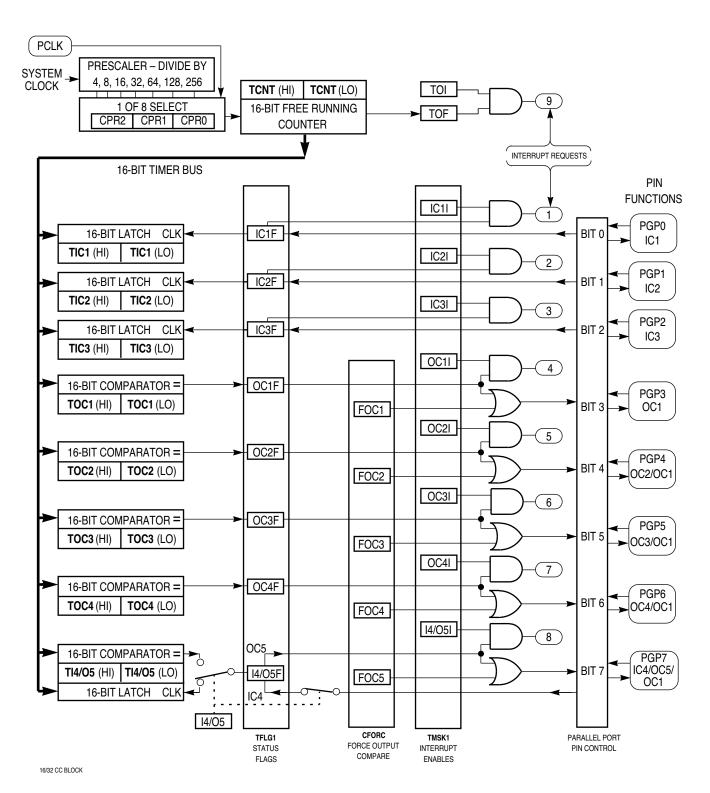

The 11-channel general-purpose timer (GPT) is used in systems where a moderate level of CPU control is required. The GPT consists of a capture/compare unit, a pulse accumulator, and two pulse-width modulators. A bus interface unit connects the GPT to the intermodule bus.

Figure 15 GPT Block Diagram

#### 6.1 Overview

The capture/compare unit features three input capture channels, four output compare channels, and one channel that can be selected as an input capture or output compare channel. These channels share a 16-bit free-running counter (TCNT) which derives its clock from a nine-stage prescaler or from the external clock input signal, PCLK.

Pulse accumulator channel logic includes an 8-bit counter; the pulse accumulator can operate in either event counting mode or gated time accumulation mode.

Pulse-width modulator outputs are periodic waveforms whose duty cycles can be independently selected and modified by user software. The PWM circuits share a 16-bit free-running counter that can be clocked by the same nine-stage prescaler used by the capture/compare unit or by the PCLK input.

All GPT pins can also be used for general-purpose input/output. The input capture and output compare pins form a bidirectional 8-bit parallel port (PORTGP). PWM pins are outputs only. PAI and PCLK pins are inputs only.

GPT input capture/output compare pins are bidirectional and can be used to form an 8-bit parallel port. The pulse-width modulator outputs can be used as general-purpose outputs. The PAI and PCLK inputs can be used as general-purpose inputs.

The GPT control register address map is shown below. The "Access" column in the GPT address map indicates which registers are accessible only at the supervisor privilege level and which can be assigned to either the supervisor or user privilege level, according to the value of the SUPV bit in the GPTMCR.

GPT BLOCK

**Figure 16 GPT Timer Block Diagram**

F1B — Force Logic Level One on PWMB

0 = Force logic level zero output on PWMB pin

1 = Force logic level one output on PWMB pin

#### **PWMA/PWMB** — PWM Control Registers A/B

\$YFF926, \$YFF927

These registers are associated with the pulse-width value of the PWM output on the corresponding PWM pin. A value of \$00 loaded into one of these registers results in a continuously low output on the corresponding pin. A value of \$80 results in a 50% duty cycle output. Maximum value (\$FF) selects an output that is high for 255/256 of the period.

#### **PWMCNT** — PWM Count Register

**\$YFF928**

PWMCNT is the 16-bit free-running counter associated with the PWM functions of the GPT module.

#### **PWMBUFA/B** — PWM Buffer Registers A/B

**\$YFF92A, \$YFF92E**

These read-only registers contain values associated with the duty cycles of the corresponding PWM. Reset state is \$0000.

#### **PRESCL** — GPT Prescaler

\$YFF92C

The 9-bit prescaler value can be read from bits [8:0] at this address. Bits [15:9] always read as zeros. Reset state is \$0000.