# E·XF

### Intel - EPF10K100ABI356-2 Datasheet

Welcome to E-XFL.COM

#### Understanding Embedded - FPGAs (Field Programmable Gate Array)

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| De | et | a | i | k | 5 |

|----|----|---|---|---|---|

| -  |    |   | 1 |   |   |

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 624                                                          |

| Number of Logic Elements/Cells | 4992                                                         |

| Total RAM Bits                 | 24576                                                        |

| Number of I/O                  | 274                                                          |

| Number of Gates                | 158000                                                       |

| Voltage - Supply               | 3V ~ 3.6V                                                    |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | -40°C ~ 85°C (TA)                                            |

| Package / Case                 | 356-LBGA                                                     |

| Supplier Device Package        | 356-BGA (35x35)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k100abi356-2 |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 2. FLEX 10K Device          | Features |                         |            |            |

|-----------------------------------|----------|-------------------------|------------|------------|

| Feature                           | EPF10K70 | EPF10K100<br>EPF10K100A | EPF10K130V | EPF10K250A |

| Typical gates (logic and RAM) (1) | 70,000   | 100,000                 | 130,000    | 250,000    |

| Maximum system gates              | 118,000  | 158,000                 | 211,000    | 310,000    |

| LEs                               | 3,744    | 4,992                   | 6,656      | 12,160     |

| LABs                              | 468      | 624                     | 832        | 1,520      |

| EABs                              | 9        | 12                      | 16         | 20         |

| Total RAM bits                    | 18,432   | 24,576                  | 32,768     | 40,960     |

| Maximum user I/O pins             | 358      | 406                     | 470        | 470        |

#### Note to tables:

(1) The embedded IEEE Std. 1149.1 JTAG circuitry adds up to 31,250 gates in addition to the listed typical or maximum system gates.

## ...and More Features

- Devices are fabricated on advanced processes and operate with a 3.3-V or 5.0-V supply voltage (see Table 3

- In-circuit reconfigurability (ICR) via external configuration device, intelligent controller, or JTAG port

- ClockLock<sup>™</sup> and ClockBoost<sup>™</sup> options for reduced clock delay/skew and clock multiplication

- Built-in low-skew clock distribution trees

- 100% functional testing of all devices; test vectors or scan chains are not required

| Table 3. Supply Voltages for FLEX 10 | Table 3. Supply Voltages for FLEX 10K & FLEX 10KA Devices |  |  |  |  |  |  |  |

|--------------------------------------|-----------------------------------------------------------|--|--|--|--|--|--|--|

| 5.0-V Devices                        | 3.3-V Devices                                             |  |  |  |  |  |  |  |

| EPF10K10                             | EPF10K10A                                                 |  |  |  |  |  |  |  |

| EPF10K20                             | EPF10K30A                                                 |  |  |  |  |  |  |  |

| EPF10K30                             | EPF10K50V                                                 |  |  |  |  |  |  |  |

| EPF10K40                             | EPF10K100A                                                |  |  |  |  |  |  |  |

| EPF10K50                             | EPF10K130V                                                |  |  |  |  |  |  |  |

| EPF10K70                             | EPF10K250A                                                |  |  |  |  |  |  |  |

| EPF10K100                            |                                                           |  |  |  |  |  |  |  |

#### LE Operating Modes

The FLEX 10K LE can operate in the following four modes:

- Normal mode

- Arithmetic mode

- Up/down counter mode

- Clearable counter mode

Each of these modes uses LE resources differently. In each mode, seven available inputs to the LE—the four data inputs from the LAB local interconnect, the feedback from the programmable register, and the carry-in and cascade-in from the previous LE—are directed to different destinations to implement the desired logic function. Three inputs to the LE provide clock, clear, and preset control for the register. The Altera software, in conjunction with parameterized functions such as LPM and DesignWare functions, automatically chooses the appropriate mode for common functions such as counters, adders, and multipliers. If required, the designer can also create special-purpose functions which use a specific LE operating mode for optimal performance.

The architecture provides a synchronous clock enable to the register in all four modes. The Altera software can set DATA1 to enable the register synchronously, providing easy implementation of fully synchronous designs.

Figure 9 shows the LE operating modes.

During compilation, the Compiler automatically selects the best control signal implementation. Because the clear and preset functions are active-low, the Compiler automatically assigns a logic high to an unused clear or preset.

The clear and preset logic is implemented in one of the following six modes chosen during design entry:

- Asynchronous clear

- Asynchronous preset

- Asynchronous clear and preset

- Asynchronous load with clear

- Asynchronous load with preset

- Asynchronous load without clear or preset

In addition to the six clear and preset modes, FLEX 10K devices provide a chip-wide reset pin that can reset all registers in the device. Use of this feature is set during design entry. In any of the clear and preset modes, the chip-wide reset overrides all other signals. Registers with asynchronous presets may be preset when the chip-wide reset is asserted. Inversion can be used to implement the asynchronous preset. Figure 10 shows examples of how to enter a section of a design for the desired functionality.

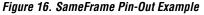

## SameFrame Pin-Outs

FLEX 10KE devices support the SameFrame pin-out feature for FineLine BGA packages. The SameFrame pin-out feature is the arrangement of balls on FineLine BGA packages such that the lower-ballcount packages form a subset of the higher-ball-count packages. SameFrame pin-outs provide the flexibility to migrate not only from device to device within the same package, but also from one package to another. A given printed circuit board (PCB) layout can support multiple device density/package combinations. For example, a single board layout can support a range of devices from an EPF10K10A device in a 256-pin FineLine BGA package to an EPF10K100A device in a 484-pin FineLine BGA package.

The Altera software provides support to design PCBs with SameFrame pin-out devices. Devices can be defined for present and future use. The Altera software generates pin-outs describing how to lay out a board to take advantage of this migration (see Figure 16).

256-Pin FineLine BGA Package (Reduced I/O Count or Logic Requirements)

484-Pin FineLine BGA Package (Increased I/O Count or Logic Requirements)

## ClockLock & ClockBoost Features

To support high-speed designs, selected FLEX 10K devices offer optional ClockLock and ClockBoost circuitry containing a phase-locked loop (PLL) that is used to increase design speed and reduce resource usage. The ClockLock circuitry uses a synchronizing PLL that reduces the clock delay and skew within a device. This reduction minimizes clock-to-output and setup times while maintaining zero hold times. The ClockBoost circuitry, which provides a clock multiplier, allows the designer to enhance device area efficiency by sharing resources within the device. The ClockBoost feature allows the designer to distribute a low-speed clock and multiply that clock on-device. Combined, the ClockLock and ClockBoost features provide significant improvements in system performance and bandwidth.

The ClockLock and ClockBoost features in FLEX 10K devices are enabled through the Altera software. External devices are not required to use these features. The output of the ClockLock and ClockBoost circuits is not available at any of the device pins.

The ClockLock and ClockBoost circuitry locks onto the rising edge of the incoming clock. The circuit output can only drive the clock inputs of registers; the generated clock cannot be gated or inverted.

The dedicated clock pin (GCLK1) supplies the clock to the ClockLock and ClockBoost circuitry. When the dedicated clock pin is driving the ClockLock or ClockBoost circuitry, it cannot drive elsewhere in the device.

In designs that require both a multiplied and non-multiplied clock, the clock trace on the board can be connected to GCLK1. With the Altera software, GCLK1 can feed both the ClockLock and ClockBoost circuitry in the FLEX 10K device. However, when both circuits are used, the other clock pin (GCLK0) cannot be used. Figure 17 shows a block diagram of how to enable both the ClockLock and ClockBoost circuits in the Altera software. The example shown is a schematic, but a similar approach applies for designs created in AHDL, VHDL, and Verilog HDL. When the ClockLock and ClockBoost circuits. In Figure 17, the input frequency must meet the requirements specified when the ClockBoost multiplication factor is two.

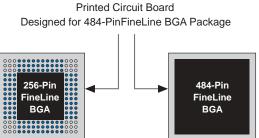

Figure 22 shows the typical output drive characteristics of EPF10K10A, EPF10K30A, EPF10K100A, and EPF10K250A devices with 3.3-V and 2.5-V V<sub>CCIO</sub>. The output driver is compliant with the 3.3-V *PCI Local Bus Specification, Revision* 2.2 (with 3.3-V V<sub>CCIO</sub>). Moreover, device analysis shows that the EPF10K10A, EPF10K30A, and EPF10K10A devices can drive a 5.0-V PCI bus with eight or fewer loads.

Figure 22. Output Drive Characteristics for EPF10K10A, EPF10K30A & EPF10K100A Devices

Figure 23 shows the typical output drive characteristics of the EPF10K250A device with 3.3-V and 2.5-V  $V_{\rm CCIO}.$

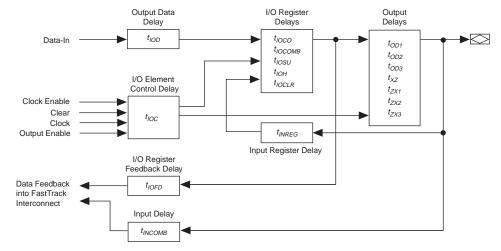

#### Figure 26. FLEX 10K Device IOE Timing Model

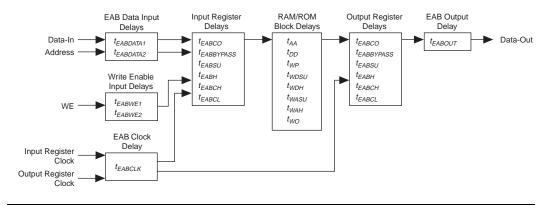

Figure 27. FLEX 10K Device EAB Timing Model

Figures 28 shows the timing model for bidirectional I/O pin timing.

| Symbol                 | Parameter                                            | Conditions |

|------------------------|------------------------------------------------------|------------|

| t <sub>EABDATA1</sub>  | Data or address delay to EAB for combinatorial input |            |

| t <sub>EABDATA2</sub>  | Data or address delay to EAB for registered input    |            |

| t <sub>EABWE1</sub>    | Write enable delay to EAB for combinatorial input    |            |

| t <sub>EABWE2</sub>    | Write enable delay to EAB for registered input       |            |

| t <sub>EABCLK</sub>    | EAB register clock delay                             |            |

| t <sub>EABCO</sub>     | EAB register clock-to-output delay                   |            |

| t <sub>EABBYPASS</sub> | Bypass register delay                                |            |

| t <sub>EABSU</sub>     | EAB register setup time before clock                 |            |

| t <sub>EABH</sub>      | EAB register hold time after clock                   |            |

| t <sub>AA</sub>        | Address access delay                                 |            |

| t <sub>WP</sub>        | Write pulse width                                    |            |

| t <sub>WDSU</sub>      | Data setup time before falling edge of write pulse   | (5)        |

| t <sub>WDH</sub>       | Data hold time after falling edge of write pulse     | (5)        |

| t <sub>WASU</sub>      | Address setup time before rising edge of write pulse | (5)        |

| t <sub>WAH</sub>       | Address hold time after falling edge of write pulse  | (5)        |

| t <sub>WO</sub>        | Write enable to data output valid delay              |            |

| t <sub>DD</sub>        | Data-in to data-out valid delay                      |            |

| t <sub>EABOUT</sub>    | Data-out delay                                       |            |

| t <sub>EABCH</sub>     | Clock high time                                      |            |

| t <sub>EABCL</sub>     | Clock low time                                       |            |

| Symbol              | -3 Spee | d Grade | -4 Spee | ed Grade | Unit |

|---------------------|---------|---------|---------|----------|------|

|                     | Min     | Max     | Min     | Max      |      |

| t <sub>IOD</sub>    |         | 1.3     |         | 1.6      | ns   |

| t <sub>IOC</sub>    |         | 0.5     |         | 0.7      | ns   |

| t <sub>IOCO</sub>   |         | 0.2     |         | 0.2      | ns   |

| t <sub>IOCOMB</sub> |         | 0.0     |         | 0.0      | ns   |

| t <sub>IOSU</sub>   | 2.8     |         | 3.2     |          | ns   |

| t <sub>IOH</sub>    | 1.0     |         | 1.2     |          | ns   |

| t <sub>IOCLR</sub>  |         | 1.0     |         | 1.2      | ns   |

| t <sub>OD1</sub>    |         | 2.6     |         | 3.5      | ns   |

| t <sub>OD2</sub>    |         | 4.9     |         | 6.4      | ns   |

| t <sub>OD3</sub>    |         | 6.3     |         | 8.2      | ns   |

| t <sub>XZ</sub>     |         | 4.5     |         | 5.4      | ns   |

| t <sub>ZX1</sub>    |         | 4.5     |         | 5.4      | ns   |

| t <sub>ZX2</sub>    |         | 6.8     |         | 8.3      | ns   |

| t <sub>ZX3</sub>    |         | 8.2     |         | 10.1     | ns   |

| t <sub>INREG</sub>  |         | 6.0     |         | 7.5      | ns   |

| t <sub>IOFD</sub>   |         | 3.1     |         | 3.5      | ns   |

| t <sub>INCOMB</sub> |         | 3.1     |         | 3.5      | ns   |

| Symbol                 | -3 Spee | d Grade | -4 Spee | Unit |    |

|------------------------|---------|---------|---------|------|----|

|                        | Min     | Max     | Min     | Max  |    |

| t <sub>EABDATA1</sub>  |         | 1.5     |         | 1.9  | ns |

| t <sub>EABDATA2</sub>  |         | 4.8     |         | 6.0  | ns |

| t <sub>EABWE1</sub>    |         | 1.0     |         | 1.2  | ns |

| t <sub>EABWE2</sub>    |         | 5.0     |         | 6.2  | ns |

| t <sub>EABCLK</sub>    |         | 1.0     |         | 2.2  | ns |

| t <sub>EABCO</sub>     |         | 0.5     |         | 0.6  | ns |

| t <sub>EABBYPASS</sub> |         | 1.5     |         | 1.9  | ns |

| t <sub>EABSU</sub>     | 1.5     |         | 1.8     |      | ns |

| t <sub>EABH</sub>      | 2.0     |         | 2.5     |      | ns |

| t <sub>AA</sub>        |         | 8.7     |         | 10.7 | ns |

| t <sub>WP</sub>        | 5.8     |         | 7.2     |      | ns |

| t <sub>WDSU</sub>      | 1.6     |         | 2.0     |      | ns |

| t <sub>WDH</sub>       | 0.3     |         | 0.4     |      | ns |

| t <sub>WASU</sub>      | 0.5     |         | 0.6     |      | ns |

| t <sub>WAH</sub>       | 1.0     |         | 1.2     |      | ns |

| t <sub>WO</sub>        |         | 5.0     |         | 6.2  | ns |

| t <sub>DD</sub>        |         | 5.0     |         | 6.2  | ns |

| t <sub>EABOUT</sub>    |         | 0.5     |         | 0.6  | ns |

| t <sub>EABCH</sub>     | 4.0     |         | 4.0     |      | ns |

| t <sub>EABCL</sub>     | 5.8     |         | 7.2     |      | ns |

| Symbol                 | -2 Speed | l Grade | -3 Spee | d Grade | -4 Spee | Unit |    |

|------------------------|----------|---------|---------|---------|---------|------|----|

|                        | Min      | Max     | Min     | Max     | Min     | Max  | -  |

| t <sub>EABAA</sub>     |          | 12.1    |         | 13.7    |         | 17.0 | ns |

| t <sub>EABRCCOMB</sub> | 12.1     |         | 13.7    |         | 17.0    |      | ns |

| t <sub>EABRCREG</sub>  | 8.6      |         | 9.7     |         | 11.9    |      | ns |

| t <sub>EABWP</sub>     | 5.2      |         | 5.8     |         | 7.2     |      | ns |

| t <sub>EABWCCOMB</sub> | 6.5      |         | 7.3     |         | 9.0     |      | ns |

| t <sub>EABWCREG</sub>  | 11.6     |         | 13.0    |         | 16.0    |      | ns |

| t <sub>EABDD</sub>     |          | 8.8     |         | 10.0    |         | 12.5 | ns |

| t <sub>EABDATACO</sub> |          | 1.7     |         | 2.0     |         | 3.4  | ns |

| t <sub>EABDATASU</sub> | 4.7      |         | 5.3     |         | 5.6     |      | ns |

| t <sub>EABDATAH</sub>  | 0.0      |         | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWESU</sub>   | 4.9      |         | 5.5     |         | 5.8     |      | ns |

| t <sub>EABWEH</sub>    | 0.0      |         | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWDSU</sub>   | 1.8      |         | 2.1     |         | 2.7     |      | ns |

| t <sub>EABWDH</sub>    | 0.0      |         | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWASU</sub>   | 4.1      |         | 4.7     |         | 5.8     |      | ns |

| t <sub>EABWAH</sub>    | 0.0      |         | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWO</sub>     |          | 8.4     |         | 9.5     |         | 11.8 | ns |

| Table 68. EPF10K100 Device Interconn                                    | -        |           | 1       | Note (1) |         |          |      |

|-------------------------------------------------------------------------|----------|-----------|---------|----------|---------|----------|------|

| Symbol                                                                  | -3DX Spe | eed Grade | -3 Spee | ed Grade | -4 Spee | ed Grade | Unit |

|                                                                         | Min      | Max       | Min     | Max      | Min     | Max      |      |

| t <sub>DIN2IOE</sub>                                                    |          | 10.3      |         | 10.3     |         | 12.2     | ns   |

| t <sub>DIN2LE</sub>                                                     |          | 4.8       |         | 4.8      |         | 6.0      | ns   |

| t <sub>DIN2DATA</sub>                                                   |          | 7.3       |         | 7.3      |         | 11.0     | ns   |

| t <sub>DCLK2IOE</sub> without ClockLock or<br>ClockBoost circuitry      |          | 6.2       |         | 6.2      |         | 7.7      | ns   |

| <i>t<sub>DCLK2IOE</sub></i> with ClockLock or ClockBoost circuitry      |          | 2.3       |         | -        |         | -        | ns   |

| <i>t<sub>DCLK2LE</sub></i> without ClockLock or<br>ClockBoost circuitry |          | 4.8       |         | 4.8      |         | 6.0      | ns   |

| <i>t<sub>DCLK2LE</sub></i> with ClockLock or ClockBoost circuitry       |          | 2.3       |         | -        |         | -        | ns   |

| t <sub>SAMELAB</sub>                                                    |          | 0.4       |         | 0.4      |         | 0.5      | ns   |

| t <sub>SAMEROW</sub>                                                    |          | 4.9       |         | 4.9      |         | 5.5      | ns   |

| t <sub>SAMECOLUMN</sub>                                                 |          | 5.1       |         | 5.1      |         | 5.4      | ns   |

| t <sub>DIFFROW</sub>                                                    |          | 10.0      |         | 10.0     |         | 10.9     | ns   |

| t <sub>TWOROWS</sub>                                                    |          | 14.9      |         | 14.9     |         | 16.4     | ns   |

| t <sub>LEPERIPH</sub>                                                   |          | 6.9       |         | 6.9      |         | 8.1      | ns   |

| t <sub>LABCARRY</sub>                                                   |          | 0.9       |         | 0.9      |         | 1.1      | ns   |

| t <sub>LABCASC</sub>                                                    |          | 3.0       |         | 3.0      |         | 3.2      | ns   |

#### Altera Corporation

| Symbol                  | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | -4 Speed Grade |      | Unit |

|-------------------------|----------------|-----|----------------|-----|----------------|-----|----------------|------|------|

|                         | Min            | Max | Min            | Max | Min            | Max | Min            | Max  |      |

| t <sub>DIN2IOE</sub>    |                | 4.7 |                | 6.0 |                | 7.1 |                | 8.2  | ns   |

| t <sub>DIN2LE</sub>     |                | 2.5 |                | 2.6 |                | 3.1 |                | 3.9  | ns   |

| t <sub>DIN2DATA</sub>   |                | 4.4 |                | 5.9 |                | 6.8 |                | 7.7  | ns   |

| t <sub>DCLK2IOE</sub>   |                | 2.5 |                | 3.9 |                | 4.7 |                | 5.5  | ns   |

| t <sub>DCLK2LE</sub>    |                | 2.5 |                | 2.6 |                | 3.1 |                | 3.9  | ns   |

| t <sub>SAMELAB</sub>    |                | 0.2 |                | 0.2 |                | 0.3 |                | 0.3  | ns   |

| t <sub>SAMEROW</sub>    |                | 2.8 |                | 3.0 |                | 3.2 |                | 3.4  | ns   |

| t <sub>SAMECOLUMN</sub> |                | 3.0 |                | 3.2 |                | 3.4 |                | 3.6  | ns   |

| t <sub>DIFFROW</sub>    |                | 5.8 |                | 6.2 |                | 6.6 |                | 7.0  | ns   |

| t <sub>TWOROWS</sub>    |                | 8.6 |                | 9.2 |                | 9.8 |                | 10.4 | ns   |

| t <sub>LEPERIPH</sub>   |                | 4.5 |                | 5.5 |                | 6.1 |                | 7.0  | ns   |

| t <sub>LABCARRY</sub>   |                | 0.3 |                | 0.4 |                | 0.5 |                | 0.7  | ns   |

| t <sub>LABCASC</sub>    |                | 0.0 |                | 1.3 |                | 1.6 |                | 2.0  | ns   |

#### Table 76. EPF10K50V Device External Timing Parameters Note (1)

| Symbol                     | -1 Spee | d Grade | -2 Speed Grade -3 Speed Grade |      | -4 Spee | Unit |     |      |    |

|----------------------------|---------|---------|-------------------------------|------|---------|------|-----|------|----|

|                            | Min     | Max     | Min                           | Max  | Min     | Max  | Min | Max  |    |

| t <sub>DRR</sub>           |         | 11.2    |                               | 14.0 |         | 17.2 |     | 21.1 | ns |

| t <sub>INSU</sub> (2), (3) | 5.5     |         | 4.2                           |      | 5.2     |      | 6.9 |      | ns |

| t <sub>INH</sub> (3)       | 0.0     |         | 0.0                           |      | 0.0     |      | 0.0 |      | ns |

| <b>t</b> оитсо (3)         | 2.0     | 5.9     | 2.0                           | 7.8  | 2.0     | 9.5  | 2.0 | 11.1 | ns |

Table 77. EPF10K50V Device External Bidirectional Timing Parameters

No

Note (1)

| Symbol                  | -1 Speed Grade |     | -2 Spee | d Grade | -3 Speed Grade |      | -4 Spee | -4 Speed Grade |    |

|-------------------------|----------------|-----|---------|---------|----------------|------|---------|----------------|----|

|                         | Min            | Max | Min     | Max     | Min            | Max  | Min     | Max            |    |

| t <sub>INSUBIDIR</sub>  | 2.0            |     | 2.8     |         | 3.5            |      | 4.1     |                | ns |

| t <sub>INHBIDIR</sub>   | 0.0            |     | 0.0     |         | 0.0            |      | 0.0     |                | ns |

| t <sub>OUTCOBIDIR</sub> | 2.0            | 5.9 | 2.0     | 7.8     | 2.0            | 9.5  | 2.0     | 11.1           | ns |

| t <sub>XZBIDIR</sub>    |                | 8.0 |         | 9.8     |                | 11.8 |         | 14.3           | ns |

| t <sub>ZXBIDIR</sub>    |                | 8.0 |         | 9.8     |                | 11.8 |         | 14.3           | ns |

#### FLEX 10K Embedded Programmable Logic Device Family Data Sheet

| Symbol              | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | Unit |    |

|---------------------|----------------|-----|---------|---------|---------|------|----|

|                     | Min            | Max | Min     | Max     | Min     | Max  |    |

| t <sub>IOH</sub>    | 0.8            |     | 1.0     |         | 1.3     |      | ns |

| t <sub>IOCLR</sub>  |                | 1.2 |         | 1.4     |         | 1.9  | ns |

| t <sub>OD1</sub>    |                | 1.2 |         | 1.4     |         | 1.9  | ns |

| t <sub>OD2</sub>    |                | 2.9 |         | 3.5     |         | 4.7  | ns |

| t <sub>OD3</sub>    |                | 6.6 |         | 7.8     |         | 10.5 | ns |

| t <sub>XZ</sub>     |                | 1.2 |         | 1.4     |         | 1.9  | ns |

| t <sub>ZX1</sub>    |                | 1.2 |         | 1.4     |         | 1.9  | ns |

| t <sub>ZX2</sub>    |                | 2.9 |         | 3.5     |         | 4.7  | ns |

| t <sub>ZX3</sub>    |                | 6.6 |         | 7.8     |         | 10.5 | ns |

| t <sub>INREG</sub>  |                | 5.2 |         | 6.3     |         | 8.4  | ns |

| t <sub>IOFD</sub>   |                | 3.1 |         | 3.8     |         | 5.0  | ns |

| t <sub>INCOMB</sub> |                | 3.1 |         | 3.8     |         | 5.0  | ns |

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                        | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>EABDATA1</sub>  |                | 3.3 |                | 3.9 |                | 5.2 | ns   |

| t <sub>EABDATA2</sub>  |                | 1.0 |                | 1.3 |                | 1.7 | ns   |

| t <sub>EABWE1</sub>    |                | 2.6 |                | 3.1 |                | 4.1 | ns   |

| t <sub>EABWE2</sub>    |                | 2.7 |                | 3.2 |                | 4.3 | ns   |

| t <sub>EABCLK</sub>    |                | 0.0 |                | 0.0 |                | 0.0 | ns   |

| t <sub>EABCO</sub>     |                | 1.2 |                | 1.4 |                | 1.8 | ns   |

| t <sub>EABBYPASS</sub> |                | 0.1 |                | 0.2 |                | 0.2 | ns   |

| t <sub>EABSU</sub>     | 1.4            |     | 1.7            |     | 2.2            |     | ns   |

| t <sub>EABH</sub>      | 0.1            |     | 0.1            |     | 0.1            |     | ns   |

| t <sub>AA</sub>        |                | 4.5 |                | 5.4 |                | 7.3 | ns   |

| t <sub>WP</sub>        | 2.0            |     | 2.4            |     | 3.2            |     | ns   |

| t <sub>WDSU</sub>      | 0.7            |     | 0.8            |     | 1.1            |     | ns   |

| t <sub>WDH</sub>       | 0.5            |     | 0.6            |     | 0.7            |     | ns   |

| t <sub>WASU</sub>      | 0.6            |     | 0.7            |     | 0.9            |     | ns   |

| t <sub>WAH</sub>       | 0.9            |     | 1.1            |     | 1.5            |     | ns   |

| t <sub>WO</sub>        |                | 3.3 |                | 3.9 |                | 5.2 | ns   |

| t <sub>DD</sub>        |                | 3.3 |                | 3.9 |                | 5.2 | ns   |

| t<br>EABOUT            |                | 0.1 |                | 0.1 |                | 0.2 | ns   |

| t <sub>EABCH</sub>     | 3.0            |     | 3.5            |     | 4.0            |     | ns   |

| t <sub>EABCL</sub>     | 3.03           |     | 3.5            |     | 4.0            |     | ns   |

#### FLEX 10K Embedded Programmable Logic Device Family Data Sheet

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |     | -3 Spee | Unit |    |

|------------------------|----------------|-----|----------------|-----|---------|------|----|

|                        | Min            | Max | Min            | Max | Min     | Max  |    |

| t <sub>EABDATA1</sub>  |                | 5.5 |                | 6.5 |         | 8.5  | ns |

| t <sub>EABDATA2</sub>  |                | 1.1 |                | 1.3 |         | 1.8  | ns |

| t <sub>EABWE1</sub>    |                | 2.4 |                | 2.8 |         | 3.7  | ns |

| t <sub>EABWE2</sub>    |                | 2.1 |                | 2.5 |         | 3.2  | ns |

| t <sub>EABCLK</sub>    |                | 0.0 |                | 0.0 |         | 0.2  | ns |

| t <sub>EABCO</sub>     |                | 1.7 |                | 2.0 |         | 2.6  | ns |

| t <sub>EABBYPASS</sub> |                | 0.0 |                | 0.0 |         | 0.3  | ns |

| t <sub>EABSU</sub>     | 1.2            |     | 1.4            |     | 1.9     |      | ns |

| t <sub>EABH</sub>      | 0.1            |     | 0.1            |     | 0.3     |      | ns |

| t <sub>AA</sub>        |                | 4.2 |                | 5.0 |         | 6.5  | ns |

| t <sub>WP</sub>        | 3.8            |     | 4.5            |     | 5.9     |      | ns |

| t <sub>WDSU</sub>      | 0.1            |     | 0.1            |     | 0.2     |      | ns |

| t <sub>WDH</sub>       | 0.1            |     | 0.1            |     | 0.2     |      | ns |

| t <sub>WASU</sub>      | 0.1            |     | 0.1            |     | 0.2     |      | ns |

| t <sub>WAH</sub>       | 0.1            |     | 0.1            |     | 0.2     |      | ns |

| t <sub>WO</sub>        |                | 3.7 |                | 4.4 |         | 6.4  | ns |

| t <sub>DD</sub>        |                | 3.7 |                | 4.4 |         | 6.4  | ns |

| t <sub>EABOUT</sub>    |                | 0.0 |                | 0.1 |         | 0.6  | ns |

| t <sub>EABCH</sub>     | 3.0            |     | 3.5            |     | 4.0     |      | ns |

| t <sub>EABCL</sub>     | 3.8            |     | 4.5            |     | 5.9     |      | ns |

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|------------------------|----------------|-----|----------------|------|----------------|------|------|

|                        | Min            | Max | Min            | Max  | Min            | Max  |      |

| t <sub>EABAA</sub>     |                | 9.7 |                | 11.6 |                | 16.2 | ns   |

| t <sub>EABRCCOMB</sub> | 9.7            |     | 11.6           |      | 16.2           |      | ns   |

| t <sub>EABRCREG</sub>  | 5.9            |     | 7.1            |      | 9.7            |      | ns   |

| t <sub>EABWP</sub>     | 3.8            |     | 4.5            |      | 5.9            |      | ns   |

| t <sub>EABWCCOMB</sub> | 4.0            |     | 4.7            |      | 6.3            |      | ns   |

| t <sub>EABWCREG</sub>  | 9.8            |     | 11.6           |      | 16.6           |      | ns   |

| t <sub>EABDD</sub>     |                | 9.2 |                | 11.0 |                | 16.1 | ns   |

| t <sub>EABDATACO</sub> |                | 1.7 |                | 2.1  |                | 3.4  | ns   |

| t <sub>EABDATASU</sub> | 2.3            |     | 2.7            |      | 3.5            |      | ns   |

| t <sub>EABDATAH</sub>  | 0.0            |     | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWESU</sub>   | 3.3            |     | 3.9            |      | 4.9            |      | ns   |

| t <sub>EABWEH</sub>    | 0.0            |     | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWDSU</sub>   | 3.2            |     | 3.8            |      | 5.0            |      | ns   |

| t <sub>EABWDH</sub>    | 0.0            |     | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWASU</sub>   | 3.7            |     | 4.4            |      | 5.1            |      | ns   |

| t <sub>EABWAH</sub>    | 0.0            |     | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWO</sub>     |                | 6.1 |                | 7.3  |                | 11.3 | ns   |

| Symbol                   | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |      | Unit |

|--------------------------|----------------|-----|----------------|-----|----------------|------|------|

|                          | Min            | Max | Min            | Max | Min            | Max  |      |

| t <sub>DIN2IOE</sub>     |                | 4.8 |                | 5.4 |                | 6.0  | ns   |

| t <sub>DIN2LE</sub>      |                | 2.0 |                | 2.4 |                | 2.7  | ns   |

| t <sub>DIN2DATA</sub>    |                | 2.4 |                | 2.7 |                | 2.9  | ns   |

| t <sub>DCLK2IOE</sub>    |                | 2.6 |                | 3.0 |                | 3.5  | ns   |

| t <sub>DCLK2LE</sub>     |                | 2.0 |                | 2.4 |                | 2.7  | ns   |

| t <sub>SAMELAB</sub>     |                | 0.1 |                | 0.1 |                | 0.1  | ns   |

| t <sub>SAMEROW</sub>     |                | 1.5 |                | 1.7 |                | 1.9  | ns   |

| t <sub>SAME</sub> COLUMN |                | 5.5 |                | 6.5 |                | 7.4  | ns   |

| t <sub>DIFFROW</sub>     |                | 7.0 |                | 8.2 |                | 9.3  | ns   |

| t <sub>TWOROWS</sub>     |                | 8.5 |                | 9.9 |                | 11.2 | ns   |

| t <sub>LEPERIPH</sub>    |                | 3.9 |                | 4.2 |                | 4.5  | ns   |

| t <sub>LABCARRY</sub>    |                | 0.2 |                | 0.2 |                | 0.3  | ns   |

| t <sub>LABCASC</sub>     |                | 0.4 |                | 0.5 |                | 0.6  | ns   |

#### Table 104. EPF10K100A Device External Timing Parameters Note (1)

| Symbol                     | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|----------------------------|----------------|------|----------------|------|----------------|------|------|

|                            | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>DRR</sub>           |                | 12.5 |                | 14.5 |                | 17.0 | ns   |

| t <sub>INSU</sub> (2), (3) | 3.7            |      | 4.5            |      | 5.1            |      | ns   |

| t <sub>INH</sub> (3)       | 0.0            |      | 0.0            |      | 0.0            |      | ns   |

| t <sub>оитсо</sub> (3)     | 2.0            | 5.3  | 2.0            | 6.1  | 2.0            | 7.2  | ns   |

7.4

| Table 105. EPF10K100A Device External Bidirectional Timing Parameters       Note (1) |                |     |                |     |                |      |      |  |  |

|--------------------------------------------------------------------------------------|----------------|-----|----------------|-----|----------------|------|------|--|--|

| Symbol                                                                               | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |      | Unit |  |  |

|                                                                                      | Min            | Max | Min            | Max | Min            | Max  | 1    |  |  |

| t <sub>INSUBIDIR</sub>                                                               | 4.9            |     | 5.8            |     | 6.8            |      | ns   |  |  |

| t <sub>INHBIDIR</sub>                                                                | 0.0            |     | 0.0            |     | 0.0            |      | ns   |  |  |

| toutcobidir                                                                          | 2.0            | 5.3 | 2.0            | 6.1 | 2.0            | 7.2  | ns   |  |  |

| t <sub>XZBIDIR</sub>                                                                 |                | 7.4 |                | 8.6 |                | 10.1 | ns   |  |  |

8.6

t<sub>ZXBIDIR</sub>

ns

10.1

| Symbol                 | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | Unit |    |

|------------------------|----------------|-----|---------|---------|---------|------|----|

|                        | Min            | Мах | Min     | Max     | Min     | Max  |    |

| t <sub>EABDATA1</sub>  |                | 1.3 |         | 1.5     |         | 1.7  | ns |

| t <sub>EABDATA2</sub>  |                | 1.3 |         | 1.5     |         | 1.7  | ns |

| t <sub>EABWE1</sub>    |                | 0.9 |         | 1.1     |         | 1.3  | ns |

| t <sub>EABWE2</sub>    |                | 5.0 |         | 5.7     |         | 6.7  | ns |

| t <sub>EABCLK</sub>    |                | 0.6 |         | 0.7     |         | 0.8  | ns |

| t <sub>EABCO</sub>     |                | 0.0 |         | 0.0     |         | 0.0  | ns |

| t <sub>EABBYPASS</sub> |                | 0.1 |         | 0.1     |         | 0.2  | ns |

| t <sub>EABSU</sub>     | 3.8            |     | 4.3     |         | 5.0     |      | ns |

| t <sub>EABH</sub>      | 0.7            |     | 0.8     |         | 0.9     |      | ns |

| t <sub>AA</sub>        |                | 4.5 |         | 5.0     |         | 5.9  | ns |

| t <sub>WP</sub>        | 5.6            |     | 6.4     |         | 7.5     |      | ns |

| t <sub>WDSU</sub>      | 1.3            |     | 1.4     |         | 1.7     |      | ns |

| t <sub>WDH</sub>       | 0.1            |     | 0.1     |         | 0.2     |      | ns |

| t <sub>WASU</sub>      | 0.1            |     | 0.1     |         | 0.2     |      | ns |

| t <sub>WAH</sub>       | 0.1            |     | 0.1     |         | 0.2     |      | ns |

| t <sub>WO</sub>        |                | 4.1 |         | 4.6     |         | 5.5  | ns |

| t <sub>DD</sub>        |                | 4.1 |         | 4.6     |         | 5.5  | ns |

| t <sub>EABOUT</sub>    |                | 0.1 |         | 0.1     |         | 0.2  | ns |

| t <sub>EABCH</sub>     | 2.5            |     | 3.0     |         | 3.5     |      | ns |

| t <sub>EABCL</sub>     | 5.6            |     | 6.4     |         | 7.5     |      | ns |

SRAM configuration elements allow FLEX 10K devices to be reconfigured in-circuit by loading new configuration data into the device. Real-time reconfiguration is performed by forcing the device into command mode with a device pin, loading different configuration data, reinitializing the device, and resuming user-mode operation.

The entire reconfiguration process may be completed in less than 320 ms using an EPF10K250A device with a DCLK frequency of 10 MHz. This process can be used to reconfigure an entire system dynamically. In-field upgrades can be performed by distributing new configuration files.

Refer to the configuration device data sheet to obtain the POR delay when using a configuration device method.

#### **Programming Files**

Despite being function- and pin-compatible, FLEX 10KA and FLEX 10KE devices are not programming- or configuration-file compatible with FLEX 10K devices. A design should be recompiled before it is transferred from a FLEX 10K device to an equivalent FLEX 10KA or FLEX 10KE device. This recompilation should be performed to create a new programming or configuration file and to check design timing on the faster FLEX 10KA or FLEX 10KE device. The programming or configuration files for EPF10K50 devices can program or configure an EPF10K50V device. However, Altera recommends recompiling a design for the EPF10K50V device when transferring it from the EPF10K50 device.

#### **Configuration Schemes**

The configuration data for a FLEX 10K device can be loaded with one of five configuration schemes (see Table 116), chosen on the basis of the target application. An EPC1, EPC2, EPC16, or EPC1441 configuration device, intelligent controller, or the JTAG port can be used to control the configuration of a FLEX 10K device, allowing automatic configuration on system power-up.