Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 624                                                           |

| Number of Logic Elements/Cells | 4992                                                          |

| Total RAM Bits                 | 24576                                                         |

| Number of I/O                  | 189                                                           |

| Number of Gates                | 158000                                                        |

| Voltage - Supply               | 3V ~ 3.6V                                                     |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | 0°C ~ 70°C (TA)                                               |

| Package / Case                 | 240-BFQFP Exposed Pad                                         |

| Supplier Device Package        | 240-RQFP (32x32)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k100arc240-2n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The logic array consists of logic array blocks (LABs). Each LAB contains eight LEs and a local interconnect. An LE consists of a 4-input look-up table (LUT), a programmable flipflop, and dedicated signal paths for carry and cascade functions. The eight LEs can be used to create medium-sized blocks of logic—8-bit counters, address decoders, or state machines—or combined across LABs to create larger logic blocks. Each LAB represents about 96 usable gates of logic.

Signal interconnections within FLEX 10K devices and to and from device pins are provided by the FastTrack Interconnect, a series of fast, continuous row and column channels that run the entire length and width of the device.

Each I/O pin is fed by an I/O element (IOE) located at the end of each row and column of the FastTrack Interconnect. Each IOE contains a bidirectional I/O buffer and a flipflop that can be used as either an output or input register to feed input, output, or bidirectional signals. When used with a dedicated clock pin, these registers provide exceptional performance. As inputs, they provide setup times as low as 1.6 ns and hold times of 0 ns; as outputs, these registers provide clock-to-output times as low as 5.3 ns. IOEs provide a variety of features, such as JTAG BST support, slew-rate control, tri-state buffers, and open-drain outputs.

Figure 1 shows a block diagram of the FLEX 10K architecture. Each group of LEs is combined into an LAB; LABs are arranged into rows and columns. Each row also contains a single EAB. The LABs and EABs are interconnected by the FastTrack Interconnect. IOEs are located at the end of each row and column of the FastTrack Interconnect.

Dedicated Inputs & Global Signals Chip-Wide Reset Row Interconnect 2, 4, 8, 16 Data Data Out 8, 4, 2, 1 2, 4, 8, 16 Address D 8, 9, 10, 11 RAM/ROM  $256 \times 8$ 512 × 4  $1,024 \times 2$ Column 2,048 × 1 Interconnect WE D

Figure 4. FLEX 10K Embedded Array Block

### Note:

EAB Local Interconnect (1)

(1) EPF10K10, EPF10K10A, EPF10K20, EPF10K30, EPF10K30A, EPF10K40, EPF10K50, and EPF10K50V devices have 22 EAB local interconnect channels; EPF10K70, EPF10K100, EPF10K100A, EPF10K130V, and EPF10K250A devices have 26.

During compilation, the Compiler automatically selects the best control signal implementation. Because the clear and preset functions are active-low, the Compiler automatically assigns a logic high to an unused clear or preset.

The clear and preset logic is implemented in one of the following six modes chosen during design entry:

- Asynchronous clear

- Asynchronous preset

- Asynchronous clear and preset

- Asynchronous load with clear

- Asynchronous load with preset

- Asynchronous load without clear or preset

In addition to the six clear and preset modes, FLEX 10K devices provide a chip-wide reset pin that can reset all registers in the device. Use of this feature is set during design entry. In any of the clear and preset modes, the chip-wide reset overrides all other signals. Registers with asynchronous presets may be preset when the chip-wide reset is asserted. Inversion can be used to implement the asynchronous preset. Figure 10 shows examples of how to enter a section of a design for the desired functionality.

#### I/O Element

An I/O element (IOE) contains a bidirectional I/O buffer and a register that can be used either as an input register for external data that requires a fast setup time, or as an output register for data that requires fast clock-to-output performance. In some cases, using an LE register for an input register will result in a faster setup time than using an IOE register. IOEs can be used as input, output, or bidirectional pins. For bidirectional registered I/O implementation, the output register should be in the IOE and, the data input and output enable register should be LE registers placed adjacent to the bidirectional pin. The Compiler uses the programmable inversion option to invert signals from the row and column interconnect automatically where appropriate. Figure 13 shows the bidirectional I/O registers.

Table 10 lists the FLEX 10K row-to-IOE interconnect resources.

| Device                  | Channels per Row (n) | Row Channels per Pin ( <i>m</i> |  |  |

|-------------------------|----------------------|---------------------------------|--|--|

| EPF10K10<br>EPF10K10A   | 144                  | 18                              |  |  |

| EPF10K20                | 144                  | 18                              |  |  |

| EPF10K30<br>EPF10K30A   | 216                  | 27                              |  |  |

| EPF10K40                | 216                  | 27                              |  |  |

| EPF10K50<br>EPF10K50V   | 216                  | 27                              |  |  |

| EPF10K70                | 312                  | 39                              |  |  |

| EPF10K100<br>EPF10K100A | 312                  | 39                              |  |  |

| EPF10K130V              | 312                  | 39                              |  |  |

| EPF10K250A              | 456                  | 57                              |  |  |

#### Column-to-IOE Connections

When an IOE is used as an input, it can drive up to two separate column channels. When an IOE is used as an output, the signal is driven by a multiplexer that selects a signal from the column channels. Two IOEs connect to each side of the column channels. Each IOE can be driven by column channels via a multiplexer. The set of column channels that each IOE can access is different for each IOE. See Figure 15.

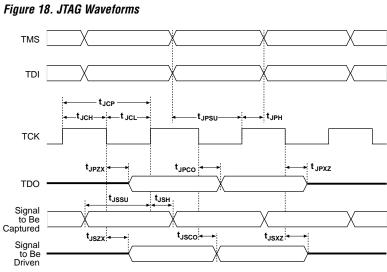

Figure 18 shows the timing requirements for the JTAG signals.

Table 16 shows the timing parameters and values for FLEX 10K devices.

| Table 1           | 6. JTAG Timing Parameters & Values             |     |     |      |

|-------------------|------------------------------------------------|-----|-----|------|

| Symbol            | Parameter                                      | Min | Max | Unit |

| t <sub>JCP</sub>  | TCK clock period                               | 100 |     | ns   |

| t <sub>JCH</sub>  | TCK clock high time                            | 50  |     | ns   |

| t <sub>JCL</sub>  | TCK clock low time                             | 50  |     | ns   |

| t <sub>JPSU</sub> | JTAG port setup time                           | 20  |     | ns   |

| t <sub>JPH</sub>  | JTAG port hold time                            | 45  |     | ns   |

| t <sub>JPCO</sub> | JTAG port clock to output                      |     | 25  | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output       |     | 25  | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance       |     | 25  | ns   |

| t <sub>JSSU</sub> | Capture register setup time                    | 20  |     | ns   |

| t <sub>JSH</sub>  | Capture register hold time                     | 45  |     | ns   |

| t <sub>JSCO</sub> | Update register clock to output                |     | 35  | ns   |

| t <sub>JSZX</sub> | Update register high-impedance to valid output |     | 35  | ns   |

| t <sub>JSXZ</sub> | Update register valid output to high impedance |     | 35  | ns   |

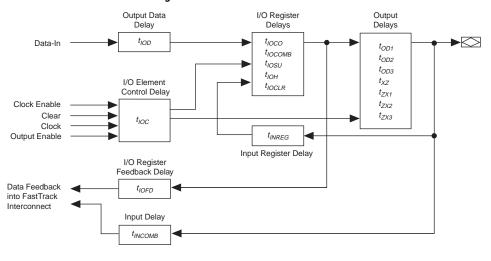

Figure 26. FLEX 10K Device IOE Timing Model

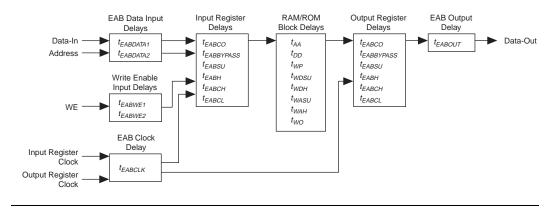

Figure 27. FLEX 10K Device EAB Timing Model

Figures 28 shows the timing model for bidirectional I/O pin timing.

| Symbol                   | Parameter                                                                                                            | Conditions |  |  |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

| t <sub>DIN2IOE</sub>     | DINZIOE Delay from dedicated input pin to IOE control input                                                          |            |  |  |  |

| t <sub>DCLK2LE</sub>     | Delay from dedicated clock pin to LE or EAB clock                                                                    | (7)        |  |  |  |

| t <sub>DIN2DATA</sub>    | Delay from dedicated input or clock to LE or EAB data                                                                |            |  |  |  |

| t <sub>DCLK2IOE</sub>    | Delay from dedicated clock pin to IOE clock                                                                          | (7)        |  |  |  |

| t <sub>DIN2LE</sub>      | Delay from dedicated input pin to LE or EAB control input                                                            | (7)        |  |  |  |

| t <sub>SAMELAB</sub>     | Routing delay for an LE driving another LE in the same LAB                                                           |            |  |  |  |

| t <sub>SAMEROW</sub>     | Routing delay for a row IOE, LE, or EAB driving a row IOE, LE, or EAB in the same row                                | (7)        |  |  |  |

| t <sub>SAME</sub> COLUMN | Routing delay for an LE driving an IOE in the same column                                                            | (7)        |  |  |  |

| t <sub>DIFFROW</sub>     | Routing delay for a column IOE, LE, or EAB driving an LE or EAB in a different row                                   | (7)        |  |  |  |

| t <sub>TWOROWS</sub>     | Routing delay for a row IOE or EAB driving an LE or EAB in a different row                                           | (7)        |  |  |  |

| t <sub>LEPERIPH</sub>    | Routing delay for an LE driving a control signal of an IOE via the peripheral control bus                            | (7)        |  |  |  |

| t <sub>LABCARRY</sub>    | Routing delay for the carry-out signal of an LE driving the carry-in signal of a different LE in a different LAB     |            |  |  |  |

| t <sub>LABCASC</sub>     | Routing delay for the cascade-out signal of an LE driving the cascade-in signal of a different LE in a different LAB |            |  |  |  |

| Table 37. Ex       | ternal Timing Parameters Notes (8), (10)                                                       |            |

|--------------------|------------------------------------------------------------------------------------------------|------------|

| Symbol             | Parameter                                                                                      | Conditions |

| t <sub>DRR</sub>   | Register-to-register delay via four LEs, three row interconnects, and four local interconnects | (9)        |

| t <sub>INSU</sub>  | Setup time with global clock at IOE register                                                   |            |

| t <sub>INH</sub>   | Hold time with global clock at IOE register                                                    |            |

| t <sub>OUTCO</sub> | Clock-to-output delay with global clock at IOE register                                        |            |

| Table 38. Ext           |                                                                                |           |

|-------------------------|--------------------------------------------------------------------------------|-----------|

| Symbol                  | Parameter                                                                      | Condition |

| t <sub>INSUBIDIR</sub>  | Setup time for bidirectional pins with global clock at adjacent LE register    |           |

| t <sub>INHBIDIR</sub>   | Hold time for bidirectional pins with global clock at adjacent LE register     |           |

| t <sub>OUTCOBIDIR</sub> | Clock-to-output delay for bidirectional pins with global clock at IOE register |           |

| t <sub>XZBIDIR</sub>    | Synchronous IOE output buffer disable delay                                    |           |

| t <sub>ZXBIDIR</sub>    | Synchronous IOE output buffer enable delay, slow slew rate = off               |           |

Tables 48 through 56 show EPF10K30, EPF10K40, and EPF10K50 device internal and external timing parameters.

| Symbol              | -3 Spee | d Grade | -4 Spee | Unit |    |

|---------------------|---------|---------|---------|------|----|

|                     | Min     | Max     | Min     | Max  |    |

| $t_{LUT}$           |         | 1.3     |         | 1.8  | ns |

| t <sub>CLUT</sub>   |         | 0.6     |         | 0.6  | ns |

| t <sub>RLUT</sub>   |         | 1.5     |         | 2.0  | ns |

| t <sub>PACKED</sub> |         | 0.5     |         | 0.8  | ns |

| t <sub>EN</sub>     |         | 0.9     |         | 1.5  | ns |

| t <sub>CICO</sub>   |         | 0.2     |         | 0.4  | ns |

| t <sub>CGEN</sub>   |         | 0.9     |         | 1.4  | ns |

| t <sub>CGENR</sub>  |         | 0.9     |         | 1.4  | ns |

| t <sub>CASC</sub>   |         | 1.0     |         | 1.2  | ns |

| $t_{\mathbb{C}}$    |         | 1.3     |         | 1.6  | ns |

| $t_{CO}$            |         | 0.9     |         | 1.2  | ns |

| t <sub>COMB</sub>   |         | 0.6     |         | 0.6  | ns |

| t <sub>SU</sub>     | 1.4     |         | 1.4     |      | ns |

| $t_H$               | 0.9     |         | 1.3     |      | ns |

| t <sub>PRE</sub>    |         | 0.9     |         | 1.2  | ns |

| t <sub>CLR</sub>    |         | 0.9     |         | 1.2  | ns |

| t <sub>CH</sub>     | 4.0     |         | 4.0     |      | ns |

| $t_{CL}$            | 4.0     |         | 4.0     |      | ns |

| Symbol              | -3 Spee | d Grade | -4 Spee | d Grade | Unit |

|---------------------|---------|---------|---------|---------|------|

|                     | Min     | Max     | Min     | Max     |      |

| t <sub>IOD</sub>    |         | 0.4     |         | 0.6     | ns   |

| t <sub>IOC</sub>    |         | 0.5     |         | 0.9     | ns   |

| t <sub>IOCO</sub>   |         | 0.4     |         | 0.5     | ns   |

| t <sub>IOCOMB</sub> |         | 0.0     |         | 0.0     | ns   |

| t <sub>iosu</sub>   | 3.1     |         | 3.5     |         | ns   |

| t <sub>IOH</sub>    | 1.0     |         | 1.9     |         | ns   |

| t <sub>IOCLR</sub>  |         | 1.0     |         | 1.2     | ns   |

| t <sub>OD1</sub>    |         | 3.3     |         | 3.6     | ns   |

| t <sub>OD2</sub>    |         | 5.6     |         | 6.5     | ns   |

| $t_{\text{OD3}}$    |         | 7.0     |         | 8.3     | ns   |

| $t_{XZ}$            |         | 5.2     |         | 5.5     | ns   |

| t <sub>ZX1</sub>    |         | 5.2     |         | 5.5     | ns   |

| t <sub>ZX2</sub>    |         | 7.5     |         | 8.4     | ns   |

| t <sub>ZX3</sub>    |         | 8.9     |         | 10.2    | ns   |

| t <sub>INREG</sub>  |         | 7.7     |         | 10.0    | ns   |

| t <sub>IOFD</sub>   |         | 3.3     |         | 4.0     | ns   |

| t <sub>INCOMB</sub> |         | 3.3     |         | 4.0     | ns   |

| Symbol                 | -3 Snee | d Grade | -4 Spee | Unit |       |

|------------------------|---------|---------|---------|------|-------|

| Symbol                 | -       |         |         |      | Oiiit |

|                        | Min     | Max     | Min     | Max  |       |

| t <sub>EABAA</sub>     |         | 13.7    |         | 17.0 | ns    |

| t <sub>EABRCCOMB</sub> | 13.7    |         | 17.0    |      | ns    |

| t <sub>EABRCREG</sub>  | 9.7     |         | 11.9    |      | ns    |

| t <sub>EABWP</sub>     | 5.8     |         | 7.2     |      | ns    |

| t <sub>EABWCCOMB</sub> | 7.3     |         | 9.0     |      | ns    |

| t <sub>EABWCREG</sub>  | 13.0    |         | 16.0    |      | ns    |

| t <sub>EABDD</sub>     |         | 10.0    |         | 12.5 | ns    |

| t <sub>EABDATACO</sub> |         | 2.0     |         | 3.4  | ns    |

| t <sub>EABDATASU</sub> | 5.3     |         | 5.6     |      | ns    |

| t <sub>EABDATAH</sub>  | 0.0     |         | 0.0     |      | ns    |

| t <sub>EABWESU</sub>   | 5.5     |         | 5.8     |      | ns    |

| t <sub>EABWEH</sub>    | 0.0     |         | 0.0     |      | ns    |

| t <sub>EABWDSU</sub>   | 5.5     |         | 5.8     |      | ns    |

| t <sub>EABWDH</sub>    | 0.0     |         | 0.0     |      | ns    |

| t <sub>EABWASU</sub>   | 2.1     |         | 2.7     |      | ns    |

| t <sub>EABWAH</sub>    | 0.0     |         | 0.0     |      | ns    |

| $t_{EABWO}$            |         | 9.5     |         | 11.8 | ns    |

#### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

Tables 57 through 63 show EPF10K70 device internal and external timing parameters.

| Symbol              | -2 Speed Grade |     | -3 Spee | -3 Speed Grade |     | -4 Speed Grade |    |

|---------------------|----------------|-----|---------|----------------|-----|----------------|----|

|                     | Min            | Max | Min     | Max            | Min | Max            |    |

| $t_{LUT}$           |                | 1.3 |         | 1.5            |     | 2.0            | ns |

| t <sub>CLUT</sub>   |                | 0.4 |         | 0.4            |     | 0.5            | ns |

| t <sub>RLUT</sub>   |                | 1.5 |         | 1.6            |     | 2.0            | ns |

| t <sub>PACKED</sub> |                | 0.8 |         | 0.9            |     | 1.3            | ns |

| t <sub>EN</sub>     |                | 0.8 |         | 0.9            |     | 1.2            | ns |

| t <sub>CICO</sub>   |                | 0.2 |         | 0.2            |     | 0.3            | ns |

| t <sub>CGEN</sub>   |                | 1.0 |         | 1.1            |     | 1.4            | ns |

| t <sub>CGENR</sub>  |                | 1.1 |         | 1.2            |     | 1.5            | ns |

| t <sub>CASC</sub>   |                | 1.0 |         | 1.1            |     | 1.3            | ns |

| $t_{\mathbb{C}}$    |                | 0.7 |         | 0.8            |     | 1.0            | ns |

| $t_{CO}$            |                | 0.9 |         | 1.0            |     | 1.4            | ns |

| t <sub>COMB</sub>   |                | 0.4 |         | 0.5            |     | 0.7            | ns |

| t <sub>SU</sub>     | 1.9            |     | 2.1     |                | 2.6 |                | ns |

| t <sub>H</sub>      | 2.1            |     | 2.3     |                | 3.1 |                | ns |

| t <sub>PRE</sub>    |                | 0.9 |         | 1.0            |     | 1.4            | ns |

| t <sub>CLR</sub>    |                | 0.9 |         | 1.0            |     | 1.4            | ns |

| t <sub>CH</sub>     | 4.0            |     | 4.0     |                | 4.0 |                | ns |

| $t_{CL}$            | 4.0            |     | 4.0     |                | 4.0 |                | ns |

| Symbol                 | -2 Spee | d Grade | -3 Spec | -3 Speed Grade |     | -4 Speed Grade |    |

|------------------------|---------|---------|---------|----------------|-----|----------------|----|

|                        | Min     | Max     | Min     | Max            | Min | Max            |    |

| t <sub>EABDATA1</sub>  |         | 1.3     |         | 1.5            |     | 1.9            | ns |

| t <sub>EABDATA2</sub>  |         | 4.3     |         | 4.8            |     | 6.0            | ns |

| t <sub>EABWE1</sub>    |         | 0.9     |         | 1.0            |     | 1.2            | ns |

| t <sub>EABWE2</sub>    |         | 4.5     |         | 5.0            |     | 6.2            | ns |

| t <sub>EABCLK</sub>    |         | 0.9     |         | 1.0            |     | 2.2            | ns |

| t <sub>EABCO</sub>     |         | 0.4     |         | 0.5            |     | 0.6            | ns |

| t <sub>EABBYPASS</sub> |         | 1.3     |         | 1.5            |     | 1.9            | ns |

| t <sub>EABSU</sub>     | 1.3     |         | 1.5     |                | 1.8 |                | ns |

| t <sub>EABH</sub>      | 1.8     |         | 2.0     |                | 2.5 |                | ns |

| $t_{AA}$               |         | 7.8     |         | 8.7            |     | 10.7           | ns |

| $t_{WP}$               | 5.2     |         | 5.8     |                | 7.2 |                | ns |

| t <sub>WDSU</sub>      | 1.4     |         | 1.6     |                | 2.0 |                | ns |

| t <sub>WDH</sub>       | 0.3     |         | 0.3     |                | 0.4 |                | ns |

| t <sub>WASU</sub>      | 0.4     |         | 0.5     |                | 0.6 |                | ns |

| t <sub>WAH</sub>       | 0.9     |         | 1.0     |                | 1.2 |                | ns |

| $t_{WO}$               |         | 4.5     |         | 5.0            |     | 6.2            | ns |

| $t_{DD}$               |         | 4.5     |         | 5.0            |     | 6.2            | ns |

| t <sub>EABOUT</sub>    |         | 0.4     |         | 0.5            |     | 0.6            | ns |

| t <sub>EABCH</sub>     | 4.0     |         | 4.0     |                | 4.0 |                | ns |

| t <sub>EABCL</sub>     | 5.2     |         | 5.8     |                | 7.2 |                | ns |

| Symbol                 | -2 Speed Grade |      | -3 Speed Grade |      | -4 Speed Grade |      | Unit |

|------------------------|----------------|------|----------------|------|----------------|------|------|

|                        | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>EABAA</sub>     |                | 12.1 |                | 13.7 |                | 17.0 | ns   |

| t <sub>EABRCCOMB</sub> | 12.1           |      | 13.7           |      | 17.0           |      | ns   |

| t <sub>EABRCREG</sub>  | 8.6            |      | 9.7            |      | 11.9           |      | ns   |

| t <sub>EABWP</sub>     | 5.2            |      | 5.8            |      | 7.2            |      | ns   |

| t <sub>EABWCCOMB</sub> | 6.5            |      | 7.3            |      | 9.0            |      | ns   |

| t <sub>EABWCREG</sub>  | 11.6           |      | 13.0           |      | 16.0           |      | ns   |

| t <sub>EABDD</sub>     |                | 8.8  |                | 10.0 |                | 12.5 | ns   |

| t <sub>EABDATACO</sub> |                | 1.7  |                | 2.0  |                | 3.4  | ns   |

| t <sub>EABDATASU</sub> | 4.7            |      | 5.3            |      | 5.6            |      | ns   |

| t <sub>EABDATAH</sub>  | 0.0            |      | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWESU</sub>   | 4.9            |      | 5.5            |      | 5.8            |      | ns   |

| t <sub>EABWEH</sub>    | 0.0            |      | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWDSU</sub>   | 1.8            |      | 2.1            |      | 2.7            |      | ns   |

| t <sub>EABWDH</sub>    | 0.0            |      | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWASU</sub>   | 4.1            |      | 4.7            |      | 5.8            |      | ns   |

| t <sub>EABWAH</sub>    | 0.0            |      | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWO</sub>     |                | 8.4  |                | 9.5  |                | 11.8 | ns   |

| Table 66. EPF10K100    | Device EAB Int   | ernal Micro | parameters | Note (1) |         |      |    |

|------------------------|------------------|-------------|------------|----------|---------|------|----|

| Symbol                 | -3DX Speed Grade |             | -3 Spee    | d Grade  | -4 Spee | Unit |    |

|                        | Min              | Max         | Min        | Max      | Min     | Max  |    |

| t <sub>EABDATA1</sub>  |                  | 1.5         |            | 1.5      |         | 1.9  | ns |

| t <sub>EABDATA2</sub>  |                  | 4.8         |            | 4.8      |         | 6.0  | ns |

| t <sub>EABWE1</sub>    |                  | 1.0         |            | 1.0      |         | 1.2  | ns |

| t <sub>EABWE2</sub>    |                  | 5.0         |            | 5.0      |         | 6.2  | ns |

| t <sub>EABCLK</sub>    |                  | 1.0         |            | 1.0      |         | 2.2  | ns |

| t <sub>EABCO</sub>     |                  | 0.5         |            | 0.5      |         | 0.6  | ns |

| t <sub>EABBYPASS</sub> |                  | 1.5         |            | 1.5      |         | 1.9  | ns |

| t <sub>EABSU</sub>     | 1.5              |             | 1.5        |          | 1.8     |      | ns |

| t <sub>EABH</sub>      | 2.0              |             | 2.0        |          | 2.5     |      | ns |

| $t_{AA}$               |                  | 8.7         |            | 8.7      |         | 10.7 | ns |

| $t_{WP}$               | 5.8              |             | 5.8        |          | 7.2     |      | ns |

| t <sub>WDSU</sub>      | 1.6              |             | 1.6        |          | 2.0     |      | ns |

| t <sub>WDH</sub>       | 0.3              |             | 0.3        |          | 0.4     |      | ns |

| t <sub>WASU</sub>      | 0.5              |             | 0.5        |          | 0.6     |      | ns |

| t <sub>WAH</sub>       | 1.0              |             | 1.0        |          | 1.2     |      | ns |

| $t_{WO}$               |                  | 5.0         |            | 5.0      |         | 6.2  | ns |

| $t_{DD}$               |                  | 5.0         |            | 5.0      |         | 6.2  | ns |

| t <sub>EABOUT</sub>    |                  | 0.5         |            | 0.5      |         | 0.6  | ns |

| t <sub>EABCH</sub>     | 4.0              |             | 4.0        |          | 4.0     |      | ns |

| t <sub>EABCL</sub>     | 5.8              |             | 5.8        |          | 7.2     |      | ns |

| 0                      | 4.0    | 40 10 1        |     | O Creed Orede  |     | 0.0            |     | 40             |    |

|------------------------|--------|----------------|-----|----------------|-----|----------------|-----|----------------|----|

| Symbol                 | -1 Spe | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | -4 Speed Grade |    |

|                        | Min    | Max            | Min | Max            | Min | Max            | Min | Max            |    |

| t <sub>EABDATA1</sub>  |        | 1.7            |     | 2.8            |     | 3.4            |     | 4.6            | ns |

| t <sub>EABDATA2</sub>  |        | 4.9            |     | 3.9            |     | 4.8            |     | 5.9            | ns |

| t <sub>EABWE1</sub>    |        | 0.0            |     | 2.5            |     | 3.0            |     | 3.7            | ns |

| t <sub>EABWE2</sub>    |        | 4.0            |     | 4.1            |     | 5.0            |     | 6.2            | ns |

| t <sub>EABCLK</sub>    |        | 0.4            |     | 0.8            |     | 1.0            |     | 1.2            | ns |

| t <sub>EABCO</sub>     |        | 0.1            |     | 0.2            |     | 0.3            |     | 0.4            | ns |

| t <sub>EABBYPASS</sub> |        | 0.9            |     | 1.1            |     | 1.3            |     | 1.6            | ns |

| t <sub>EABSU</sub>     | 0.8    |                | 1.5 |                | 1.8 |                | 2.2 |                | ns |

| t <sub>EABH</sub>      | 0.8    |                | 1.6 |                | 2.0 |                | 2.5 |                | ns |

| $t_{AA}$               |        | 5.5            |     | 8.2            |     | 10.0           |     | 12.4           | ns |

| $t_{WP}$               | 6.0    |                | 4.9 |                | 6.0 |                | 7.4 |                | ns |

| t <sub>WDSU</sub>      | 0.1    |                | 0.8 |                | 1.0 |                | 1.2 |                | ns |

| t <sub>WDH</sub>       | 0.1    |                | 0.2 |                | 0.3 |                | 0.4 |                | ns |

| t <sub>WASU</sub>      | 0.1    |                | 0.4 |                | 0.5 |                | 0.6 |                | ns |

| t <sub>WAH</sub>       | 0.1    |                | 0.8 |                | 1.0 |                | 1.2 |                | ns |

| $t_{WO}$               |        | 2.8            |     | 4.3            |     | 5.3            |     | 6.5            | ns |

| $t_{DD}$               |        | 2.8            |     | 4.3            |     | 5.3            |     | 6.5            | ns |

| t <sub>EABOUT</sub>    |        | 0.5            |     | 0.4            |     | 0.5            |     | 0.6            | ns |

| t <sub>EABCH</sub>     | 2.0    |                | 4.0 |                | 4.0 |                | 4.0 |                | ns |

| t <sub>EABCL</sub>     | 6.0    |                | 4.9 |                | 6.0 |                | 7.4 |                | ns |

| Symbol                   | -2 Spee | -2 Speed Grade |     | ed Grade | -4 Spee | Unit |    |

|--------------------------|---------|----------------|-----|----------|---------|------|----|

|                          | Min     | Max            | Min | Max      | Min     | Max  |    |

| t <sub>DIN2IOE</sub>     |         | 8.0            |     | 9.0      |         | 9.5  | ns |

| t <sub>DIN2LE</sub>      |         | 2.4            |     | 3.0      |         | 3.1  | ns |

| t <sub>DIN2DATA</sub>    |         | 5.0            |     | 6.3      |         | 7.4  | ns |

| t <sub>DCLK2IOE</sub>    |         | 3.6            |     | 4.6      |         | 5.1  | ns |

| t <sub>DCLK2LE</sub>     |         | 2.4            |     | 3.0      |         | 3.1  | ns |

| t <sub>SAMELAB</sub>     |         | 0.4            |     | 0.6      |         | 0.8  | ns |

| t <sub>SAMEROW</sub>     |         | 4.5            |     | 5.3      |         | 6.5  | ns |

| t <sub>SAME</sub> COLUMN |         | 9.0            |     | 9.5      |         | 9.7  | ns |

| t <sub>DIFFROW</sub>     |         | 13.5           |     | 14.8     |         | 16.2 | ns |

| t <sub>TWOROWS</sub>     |         | 18.0           |     | 20.1     |         | 22.7 | ns |

| t <sub>LEPERIPH</sub>    |         | 8.1            |     | 8.6      |         | 9.5  | ns |

| t <sub>LABCARRY</sub>    |         | 0.6            |     | 0.8      |         | 1.0  | ns |

| t <sub>LABCASC</sub>     |         | 0.8            |     | 1.0      |         | 1.2  | ns |

| Table 83. EPF10K130V Device External Timing Parameters Note (1) |         |          |         |         |         |         |      |  |  |  |  |

|-----------------------------------------------------------------|---------|----------|---------|---------|---------|---------|------|--|--|--|--|

| Symbol                                                          | -2 Spec | ed Grade | -3 Spee | d Grade | -4 Spee | d Grade | Unit |  |  |  |  |

|                                                                 | Min     | Max      | Min     | Max     | Min     | Max     |      |  |  |  |  |

| t <sub>DRR</sub>                                                |         | 15.0     |         | 19.1    |         | 24.2    | ns   |  |  |  |  |

| t <sub>INSU</sub> (2), (3)                                      | 6.9     |          | 8.6     |         | 11.0    |         | ns   |  |  |  |  |

| t <sub>INH</sub> (3)                                            | 0.0     |          | 0.0     |         | 0.0     |         | ns   |  |  |  |  |

| t <sub>оитсо</sub> (3)                                          | 2.0     | 7.8      | 2.0     | 9.9     | 2.0     | 11.3    | ns   |  |  |  |  |

| Table 84. EPF10K130V Device External Bidirectional Timing Parameters Note (1) |         |          |                |      |                |      |      |  |  |  |  |

|-------------------------------------------------------------------------------|---------|----------|----------------|------|----------------|------|------|--|--|--|--|

| Symbol                                                                        | -2 Spec | ed Grade | -3 Speed Grade |      | -4 Speed Grade |      | Unit |  |  |  |  |

|                                                                               | Min     | Max      | Min            | Max  | Min            | Max  |      |  |  |  |  |

| t <sub>INSUBIDIR</sub>                                                        | 6.7     |          | 8.5            |      | 10.8           |      | ns   |  |  |  |  |

| t <sub>INHBIDIR</sub>                                                         | 0.0     |          | 0.0            |      | 0.0            |      | ns   |  |  |  |  |

| t <sub>OUTCOBIDIR</sub>                                                       | 2.0     | 6.9      | 2.0            | 8.8  | 2.0            | 10.2 | ns   |  |  |  |  |

| t <sub>XZBIDIR</sub>                                                          |         | 12.9     |                | 16.4 |                | 19.3 | ns   |  |  |  |  |

| t <sub>ZXBIDIR</sub>                                                          |         | 12.9     |                | 16.4 |                | 19.3 | ns   |  |  |  |  |

| Table 95. EPF10         | K30A Device | EAB Internal   | Timing Macr | oparameters | Note (1) |         |      |

|-------------------------|-------------|----------------|-------------|-------------|----------|---------|------|

| Symbol                  | -1 Spee     | -1 Speed Grade |             | d Grade     | -3 Spee  | d Grade | Unit |

|                         | Min         | Max            | Min         | Max         | Min      | Max     |      |

| t <sub>EABAA</sub>      |             | 9.7            |             | 11.6        |          | 16.2    | ns   |

| t <sub>EABRCCOMB</sub>  | 9.7         |                | 11.6        |             | 16.2     |         | ns   |

| t <sub>EABRCREG</sub>   | 5.9         |                | 7.1         |             | 9.7      |         | ns   |

| t <sub>EABWP</sub>      | 3.8         |                | 4.5         |             | 5.9      |         | ns   |

| t <sub>EABWCCOMB</sub>  | 4.0         |                | 4.7         |             | 6.3      |         | ns   |

| t <sub>EABWCREG</sub>   | 9.8         |                | 11.6        |             | 16.6     |         | ns   |

| t <sub>EABDD</sub>      |             | 9.2            |             | 11.0        |          | 16.1    | ns   |

| t <sub>EABDATA</sub> CO |             | 1.7            |             | 2.1         |          | 3.4     | ns   |

| t <sub>EABDATASU</sub>  | 2.3         |                | 2.7         |             | 3.5      |         | ns   |

| t <sub>EABDATAH</sub>   | 0.0         |                | 0.0         |             | 0.0      |         | ns   |

| t <sub>EABWESU</sub>    | 3.3         |                | 3.9         |             | 4.9      |         | ns   |

| t <sub>EABWEH</sub>     | 0.0         |                | 0.0         |             | 0.0      |         | ns   |

| t <sub>EABWDSU</sub>    | 3.2         |                | 3.8         |             | 5.0      |         | ns   |

| t <sub>EABWDH</sub>     | 0.0         |                | 0.0         |             | 0.0      |         | ns   |

| t <sub>EABWASU</sub>    | 3.7         |                | 4.4         |             | 5.1      |         | ns   |

| t <sub>EABWAH</sub>     | 0.0         |                | 0.0         |             | 0.0      |         | ns   |

| t <sub>EABWO</sub>      |             | 6.1            |             | 7.3         |          | 11.3    | ns   |

| Symbol                   | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | Unit |    |

|--------------------------|---------|---------|---------|---------|---------|------|----|

|                          | Min     | Max     | Min     | Max     | Min     | Max  |    |

| t <sub>DIN2IOE</sub>     |         | 4.8     |         | 5.4     |         | 6.0  | ns |

| t <sub>DIN2LE</sub>      |         | 2.0     |         | 2.4     |         | 2.7  | ns |

| t <sub>DIN2DATA</sub>    |         | 2.4     |         | 2.7     |         | 2.9  | ns |

| t <sub>DCLK2IOE</sub>    |         | 2.6     |         | 3.0     |         | 3.5  | ns |

| t <sub>DCLK2LE</sub>     |         | 2.0     |         | 2.4     |         | 2.7  | ns |

| t <sub>SAMELAB</sub>     |         | 0.1     |         | 0.1     |         | 0.1  | ns |

| t <sub>SAMEROW</sub>     |         | 1.5     |         | 1.7     |         | 1.9  | ns |

| t <sub>SAME</sub> COLUMN |         | 5.5     |         | 6.5     |         | 7.4  | ns |

| t <sub>DIFFROW</sub>     |         | 7.0     |         | 8.2     |         | 9.3  | ns |

| t <sub>TWOROWS</sub>     |         | 8.5     |         | 9.9     |         | 11.2 | ns |

| t <sub>LEPERIPH</sub>    |         | 3.9     |         | 4.2     |         | 4.5  | ns |

| t <sub>LABCARRY</sub>    |         | 0.2     |         | 0.2     |         | 0.3  | ns |

| t <sub>LABCASC</sub>     |         | 0.4     |         | 0.5     |         | 0.6  | ns |

| Table 104. EPF1            | Table 104. EPF10K100A Device External Timing Parameters  Note (1) |          |         |          |         |         |      |  |  |  |  |  |  |

|----------------------------|-------------------------------------------------------------------|----------|---------|----------|---------|---------|------|--|--|--|--|--|--|

| Symbol                     | -1 Spee                                                           | ed Grade | -2 Spec | ed Grade | -3 Spee | d Grade | Unit |  |  |  |  |  |  |

|                            | Min                                                               | Max      | Min     | Max      | Min     | Max     |      |  |  |  |  |  |  |

| t <sub>DRR</sub>           |                                                                   | 12.5     |         | 14.5     |         | 17.0    | ns   |  |  |  |  |  |  |

| t <sub>INSU</sub> (2), (3) | 3.7                                                               |          | 4.5     |          | 5.1     |         | ns   |  |  |  |  |  |  |

| t <sub>INH</sub> (3)       | 0.0                                                               |          | 0.0     |          | 0.0     |         | ns   |  |  |  |  |  |  |

| t <sub>оитсо</sub> (3)     | 2.0                                                               | 5.3      | 2.0     | 6.1      | 2.0     | 7.2     | ns   |  |  |  |  |  |  |

| Table 105. EPF10K100A Device External Bidirectional Timing Parameters       Note (1) |         |          |                |     |                |      |      |  |  |  |

|--------------------------------------------------------------------------------------|---------|----------|----------------|-----|----------------|------|------|--|--|--|

| Symbol                                                                               | -1 Spee | ed Grade | -2 Speed Grade |     | -3 Speed Grade |      | Unit |  |  |  |

|                                                                                      | Min     | Max      | Min            | Max | Min            | Max  |      |  |  |  |

| t <sub>INSUBIDIR</sub>                                                               | 4.9     |          | 5.8            |     | 6.8            |      | ns   |  |  |  |

| t <sub>INHBIDIR</sub>                                                                | 0.0     |          | 0.0            |     | 0.0            |      | ns   |  |  |  |

| toutcobidir                                                                          | 2.0     | 5.3      | 2.0            | 6.1 | 2.0            | 7.2  | ns   |  |  |  |

| t <sub>XZBIDIR</sub>                                                                 |         | 7.4      |                | 8.6 |                | 10.1 | ns   |  |  |  |

| t <sub>ZXBIDIR</sub>                                                                 |         | 7.4      |                | 8.6 |                | 10.1 | ns   |  |  |  |

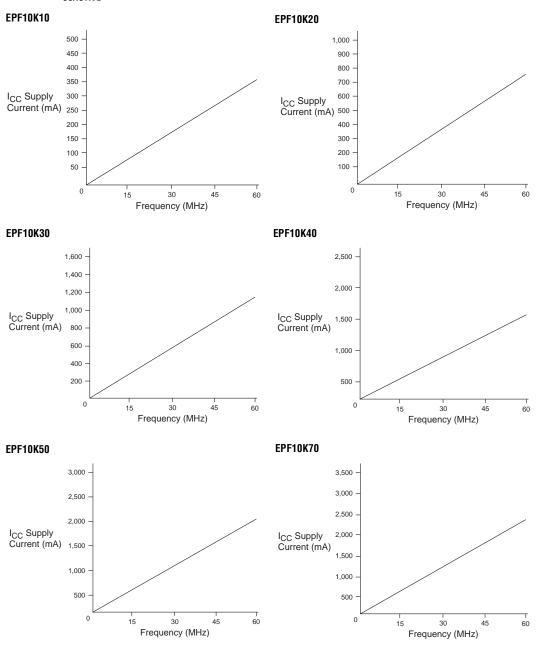

Figure 32. I<sub>CCACTIVE</sub> vs. Operating Frequency (Part 1 of 3)