# E·XFL

## Altera - EPF10K10AQI208-3 Datasheet

Welcome to <u>E-XFL.COM</u>

## Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

## Details

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Active                                                        |

| Number of LABs/CLBs            | 72                                                            |

| Number of Logic Elements/Cells | 576                                                           |

| Total RAM Bits                 | 6144                                                          |

| Number of I/O                  | 134                                                           |

| Number of Gates                | 31000                                                         |

| Voltage - Supply               | 3V ~ 3.6V                                                     |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 85°C (TA)                                             |

| Package / Case                 | 208-BFQFP                                                     |

| Supplier Device Package        | 208-PQFP (28x28)                                              |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=epf10k10aqi208-3 |

|                                |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## FLEX 10K Embedded Programmable Logic Device Family Data Sheet

| Device     | 84-Pin<br>PLCC | 100-Pin<br>TQFP | 144-Pin TQFP | 208-Pin<br>PQFP<br>RQFP | 240-Pin<br>PQFP<br>RQFP |

|------------|----------------|-----------------|--------------|-------------------------|-------------------------|

| EPF10K10   | 59             |                 | 102          | 134                     |                         |

| EPF10K10A  |                | 66              | 102          | 134                     |                         |

| EPF10K20   |                |                 | 102          | 147                     | 189                     |

| EPF10K30   |                |                 |              | 147                     | 189                     |

| EPF10K30A  |                |                 | 102          | 147                     | 189                     |

| EPF10K40   |                |                 |              | 147                     | 189                     |

| EPF10K50   |                |                 |              |                         | 189                     |

| EPF10K50V  |                |                 |              |                         | 189                     |

| EPF10K70   |                |                 |              |                         | 189                     |

| EPF10K100  |                |                 |              |                         |                         |

| EPF10K100A |                |                 |              |                         | 189                     |

| EPF10K130V |                |                 |              |                         |                         |

| EPF10K250A |                |                 |              |                         |                         |

| Device     | 503-Pin | 599-Pin | 256-Pin      | 356-Pin | 484-Pin      | 600-Pin | 403-Pin |

|------------|---------|---------|--------------|---------|--------------|---------|---------|

|            | PGA     | PGA     | FineLine BGA | BGA     | FineLine BGA | BGA     | PGA     |

| EPF10K10   |         |         |              |         |              |         |         |

| EPF10K10A  |         |         | 150          |         | 150 (2)      |         |         |

| EPF10K20   |         |         |              |         |              |         |         |

| EPF10K30   |         |         |              | 246     |              |         |         |

| EPF10K30A  |         |         | 191          | 246     | 246          |         |         |

| EPF10K40   |         |         |              |         |              |         |         |

| EPF10K50   |         |         |              | 274     |              |         | 310     |

| EPF10K50V  |         |         |              | 274     |              |         |         |

| EPF10K70   | 358     |         |              |         |              |         |         |

| EPF10K100  | 406     |         |              |         |              |         |         |

| EPF10K100A |         |         |              | 274     | 369          | 406     |         |

| EPF10K130V |         | 470     |              |         |              | 470     |         |

| EPF10K250A |         | 470     |              |         |              | 470     |         |

Г

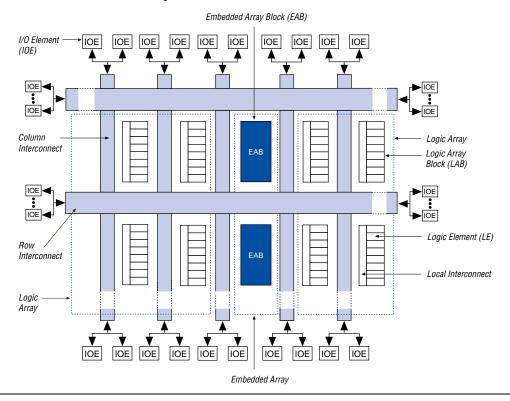

Figure 1. FLEX 10K Device Block Diagram

FLEX 10K devices provide six dedicated inputs that drive the flipflops' control inputs to ensure the efficient distribution of high-speed, low-skew (less than 1.5 ns) control signals. These signals use dedicated routing channels that provide shorter delays and lower skews than the FastTrack Interconnect. Four of the dedicated inputs drive four global signals. These four global signals can also be driven by internal logic, providing an ideal solution for a clock divider or an internally generated asynchronous clear signal that clears many registers in the device.

## Embedded Array Block

The EAB is a flexible block of RAM with registers on the input and output ports, and is used to implement common gate array megafunctions. The EAB is also suitable for functions such as multipliers, vector scalars, and error correction circuits, because it is large and flexible. These functions can be combined in applications such as digital filters and microcontrollers.

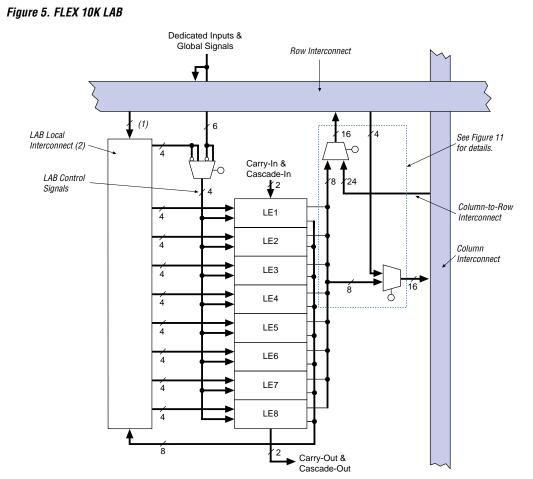

## **Logic Array Block**

Each LAB consists of eight LEs, their associated carry and cascade chains, LAB control signals, and the LAB local interconnect. The LAB provides the coarse-grained structure to the FLEX 10K architecture, facilitating efficient routing with optimum device utilization and high performance. See Figure 5.

#### Notes:

- (1) EPF10K10, EPF10K10A, EPF10K20, EPF10K30, EPF10K30A, EPF10K40, EPF10K50, and EPF10K50V devices have 22 inputs to the LAB local interconnect channel from the row; EPF10K70, EPF10K100, EPF10K100A, EPF10K130V, and EPF10K250A devices have 26.

- (2) EPF10K10, EPF10K10A, EPF10K20, EPF10K30, EPF10K30A, EPF10K40, EPF10K50, and EPF10K50V devices have 30 LAB local interconnect channels; EPF10K70, EPF10K100, EPF10K100A, EPF10K130V, and EPF10K250A devices have 34 LABs.

#### **Altera Corporation**

Each LAB provides four control signals with programmable inversion that can be used in all eight LEs. Two of these signals can be used as clocks; the other two can be used for clear/preset control. The LAB clocks can be driven by the dedicated clock input pins, global signals, I/O signals, or internal signals via the LAB local interconnect. The LAB preset and clear control signals can be driven by the global signals, I/O signals, or internal signals via the LAB local interconnect. The global control signals are typically used for global clock, clear, or preset signals because they provide asynchronous control with very low skew across the device. If logic is required on a control signal, it can be generated in one or more LEs in any LAB and driven into the local interconnect of the target LAB. In addition, the global control signals can be generated from LE outputs.

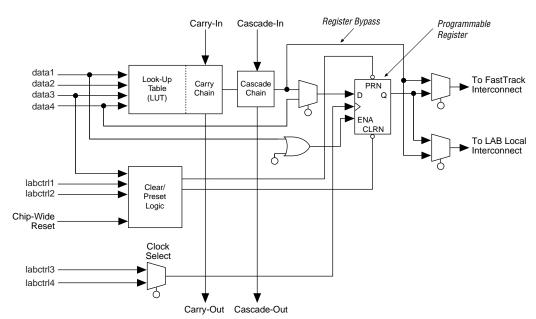

## Logic Element

The LE, the smallest unit of logic in the FLEX 10K architecture, has a compact size that provides efficient logic utilization. Each LE contains a four-input LUT, which is a function generator that can quickly compute any function of four variables. In addition, each LE contains a programmable flipflop with a synchronous enable, a carry chain, and a cascade chain. Each LE drives both the local and the FastTrack Interconnect. See Figure 6.

## Cascade Chain

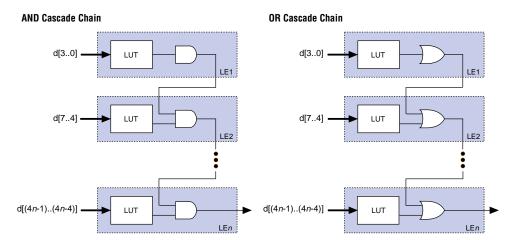

With the cascade chain, the FLEX 10K architecture can implement functions that have a very wide fan-in. Adjacent LUTs can be used to compute portions of the function in parallel; the cascade chain serially connects the intermediate values. The cascade chain can use a logical AND or logical OR (via De Morgan's inversion) to connect the outputs of adjacent LEs. Each additional LE provides four more inputs to the effective width of a function, with a delay as low as 0.7 ns per LE. Cascade chain logic can be created automatically by the Compiler during design processing, or manually by the designer during design entry.

Cascade chains longer than eight bits are implemented automatically by linking several LABs together. For easier routing, a long cascade chain skips every other LAB in a row. A cascade chain longer than one LAB skips either from even-numbered LAB to even-numbered LAB, or from odd-numbered LAB to odd-numbered LAB (e.g., the last LE of the first LAB in a row cascades to the first LE of the third LAB). The cascade chain does not cross the center of the row (e.g., in the EPF10K50 device, the cascade chain stops at the eighteenth LAB and a new one begins at the nineteenth LAB). This break is due to the EAB's placement in the middle of the row.

Figure 8 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in. These examples show functions of 4n variables implemented with n LEs. The LE delay is as low as 1.6 ns; the cascade chain delay is as low as 0.7 ns. With the cascade chain, 3.7 ns is needed to decode a 16-bit address.

## Figure 8. Cascade Chain Operation

Altera Corporation

#### Up/Down Counter Mode

The up/down counter mode offers counter enable, clock enable, synchronous up/down control, and data loading options. These control signals are generated by the data inputs from the LAB local interconnect, the carry-in signal, and output feedback from the programmable register. The Up/down counter mode uses 2 three-input LUTs: one generates the counter data, and the other generates the fast carry bit. A 2-to-1 multiplexer provides synchronous loading. Data can also be loaded asynchronously with the clear and preset register control signals, without using the LUT resources.

## **Clearable Counter Mode**

The clearable counter mode is similar to the up/down counter mode, but supports a synchronous clear instead of the up/down control. The clear function is substituted for the cascade-in signal in the up/down counter mode. Clearable counter mode uses 2 three-input LUTs: one generates the counter data, and the other generates the fast carry bit. Synchronous loading is provided by a 2-to-1 multiplexer. The output of this multiplexer is ANDed with a synchronous clear signal.

## Internal Tri-State Emulation

Internal tri-state emulation provides internal tri-stating without the limitations of a physical tri-state bus. In a physical tri-state bus, the tri-state buffers' output enable (OE) signals select which signal drives the bus. However, if multiple OE signals are active, contending signals can be driven onto the bus. Conversely, if no OE signals are active, the bus will float. Internal tri-state emulation resolves contending tri-state buffers to a low value and floating buses to a high value, thereby eliminating these problems. The Altera software automatically implements tri-state bus functionality with a multiplexer.

## Clear & Preset Logic Control

Logic for the programmable register's clear and preset functions is controlled by the DATA3, LABCTRL1, and LABCTRL2 inputs to the LE. The clear and preset control structure of the LE asynchronously loads signals into a register. Either LABCTRL1 or LABCTRL2 can control the asynchronous clear. Alternatively, the register can be set up so that LABCTRL1 implements an asynchronous load. The data to be loaded is driven to DATA3; when LABCTRL1 is asserted, DATA3 is loaded into the register.

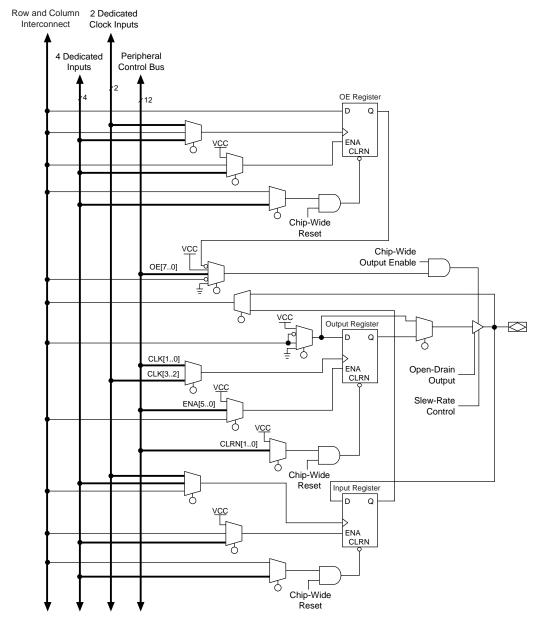

## I/O Element

An I/O element (IOE) contains a bidirectional I/O buffer and a register that can be used either as an input register for external data that requires a fast setup time, or as an output register for data that requires fast clockto-output performance. In some cases, using an LE register for an input register will result in a faster setup time than using an IOE register. IOEs can be used as input, output, or bidirectional pins. For bidirectional registered I/O implementation, the output register should be in the IOE and, the data input and output enable register should be LE registers placed adjacent to the bidirectional pin. The Compiler uses the programmable inversion option to invert signals from the row and column interconnect automatically where appropriate. Figure 13 shows the bidirectional I/O registers.

## Figure 13. Bidirectional I/O Registers

| Symbol           | Parameter                                | Conditions                                          | Min                     | Тур | Max  | Unit |

|------------------|------------------------------------------|-----------------------------------------------------|-------------------------|-----|------|------|

| V <sub>IH</sub>  | High-level input voltage                 |                                                     | 2.0                     |     | 5.75 | V    |

| VIL              | Low-level input voltage                  |                                                     | -0.5                    |     | 0.8  | V    |

| V <sub>OH</sub>  | 3.3-V high-level TTL output voltage      | I <sub>OH</sub> = -8 mA DC <i>(8)</i>               | 2.4                     |     |      | V    |

|                  | 3.3-V high-level CMOS output voltage     | I <sub>OH</sub> = -0.1 mA DC <i>(8)</i>             | V <sub>CCIO</sub> – 0.2 |     |      | V    |

| V <sub>OL</sub>  | 3.3-V low-level TTL output voltage       | I <sub>OL</sub> = 8 mA DC <i>(9)</i>                |                         |     | 0.45 | V    |

|                  | 3.3-V low-level CMOS output voltage      | I <sub>OL</sub> = 0.1 mA DC <i>(9)</i>              |                         |     | 0.2  | V    |

| I <sub>I</sub>   | Input pin leakage current                | V <sub>I</sub> = 5.3 V to -0.3 V (10)               | -10                     |     | 10   | μA   |

| I <sub>OZ</sub>  | Tri-stated I/O pin leakage current       | $V_{\rm O} = 5.3 \text{ V to } -0.3 \text{ V} (10)$ | -10                     |     | 10   | μA   |

| I <sub>CC0</sub> | V <sub>CC</sub> supply current (standby) | V <sub>I</sub> = ground, no load                    |                         | 0.3 | 10   | mA   |

|                  |                                          | $V_1$ = ground, no load (11)                        |                         | 10  |      | mA   |

| Table 2          | 5. EPF10K50V & EPF10K130V D              | <i>Nevice Capacitance</i> (12)      |     |     |      |

|------------------|------------------------------------------|-------------------------------------|-----|-----|------|

| Symbol           | Parameter                                | Conditions                          | Min | Max | Unit |

| C <sub>IN</sub>  | Input capacitance                        | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 10  | pF   |

| CINCLK           | Input capacitance on dedicated clock pin | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 15  | pF   |

| C <sub>OUT</sub> | Output capacitance                       | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 10  | pF   |

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $V_{CC}$  rise time is 100 ms.  $V_{CC}$  must rise monotonically.

- (5) EPF10K50V and EPF10K130V device inputs may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (6) Typical values are for  $T_A = 25^\circ \text{ C}$  and  $V_{CC} = 3.3 \text{ V}$ .

- (7) These values are specified under the EPF10K50V and EPF10K130V device Recommended Operating Conditions in Table 23 on page 48.

- (8) The I<sub>OH</sub> parameter refers to high-level TTL or CMOS output current.

- (9) The I<sub>OL</sub> parameter refers to low-level TTL or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (10) This value is specified for normal device operation. The value may vary during power-up.

- (11) This parameter applies to -1 speed grade EPF10K50V devices, -2 speed grade EPF10K50V industrial temperature devices, and -2 speed grade EPF10K130V devices.

- (12) Capacitance is sample-tested only.

Timing simulation and delay prediction are available with the MAX+PLUS II Simulator and Timing Analyzer, or with industrystandard EDA tools. The Simulator offers both pre-synthesis functional simulation to evaluate logic design accuracy and post-synthesis timing simulation with 0.1-ns resolution. The Timing Analyzer provides pointto-point timing delay information, setup and hold time analysis, and device-wide performance analysis.

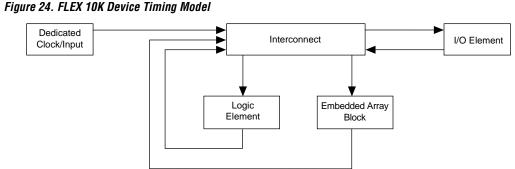

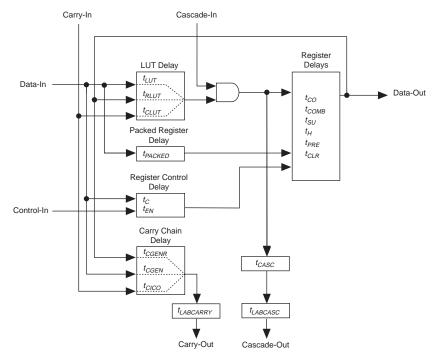

Figure 24 shows the overall timing model, which maps the possible paths to and from the various elements of the FLEX 10K device.

Figures 25 through 27 show the delays that correspond to various paths and functions within the LE, IOE, and EAB timing models.

#### FLEX 10K Embedded Programmable Logic Device Family Data Sheet

#### Notes to tables:

(1) Microparameters are timing delays contributed by individual architectural elements. These parameters cannot be measured explicitly.

| (2) | Operating conditions: V <sub>CC</sub> | $_{\text{TO}}$ = 5.0 V ± 5% for commercial use in FLEX 10K devices.                     |

|-----|---------------------------------------|-----------------------------------------------------------------------------------------|

|     | V <sub>CC</sub>                       | $_{TO} = 5.0 \text{ V} \pm 10\%$ for industrial use in FLEX 10K devices.                |

|     | V <sub>C</sub>                        | $_{TO}$ = 3.3 V ± 10% for commercial or industrial use in FLEX 10KA devices.            |

| (3) | Operating conditions: V <sub>CC</sub> | $_{TO}$ = 3.3 V ± 10% for commercial or industrial use in FLEX 10K devices.             |

|     | V <sub>CC</sub>                       | $_{\text{TO}}$ = 2.5 V ± 0.2 V for commercial or industrial use in FLEX 10KA devices.   |

| (4) | Operating conditions: V <sub>CC</sub> | $_{\rm TO} = 2.5 \text{ V}, 3.3 \text{ V}, \text{ or } 5.0 \text{ V}.$                  |

| (5) | Because the RAM in the EA             | B is self-timed, this parameter can be ignored when the WE signal is registered.        |

| (6) | EAB macroparameters are i             | nternal parameters that can simplify predicting the behavior of an EAB at its boundary; |

|     | these parameters are calcul           | ated by summing selected microparameters.                                               |

| (7) | These parameters are wors             | t-case values for typical applications. Post-compilation timing simulation and timing   |

|     | analysis are required to det          | ermine actual worst-case performance.                                                   |

| (8) | External reference timing p           | arameters are factory-tested, worst-case values specified by Altera. A representative   |

- subset of signal paths is tested to approximate typical device applications.

- (9) Contact Altera Applications for test circuit specifications and test conditions.

- (10) These timing parameters are sample-tested only.

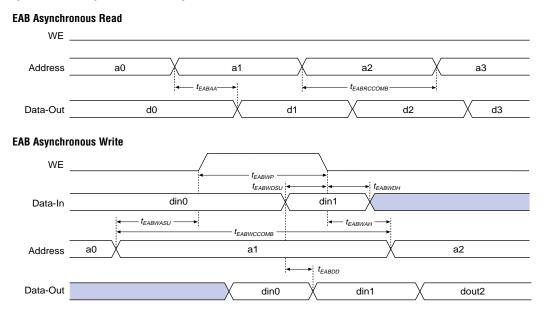

Figures 29 and 30 show the asynchronous and synchronous timing waveforms, respectively, for the EAB macroparameters in Table 34.

#### Figure 29. EAB Asynchronous Timing Waveforms

| Symbol                 | -3 Spee | d Grade | -4 Spee | Unit |    |

|------------------------|---------|---------|---------|------|----|

|                        | Min     | Max     | Min     | Max  |    |

| t <sub>EABAA</sub>     |         | 13.7    |         | 17.0 | ns |

| t <sub>EABRCCOMB</sub> | 13.7    |         | 17.0    |      | ns |

| t <sub>EABRCREG</sub>  | 9.7     |         | 11.9    |      | ns |

| t <sub>EABWP</sub>     | 5.8     |         | 7.2     |      | ns |

| t <sub>EABWCCOMB</sub> | 7.3     |         | 9.0     |      | ns |

| t <sub>EABWCREG</sub>  | 13.0    |         | 16.0    |      | ns |

| t <sub>EABDD</sub>     |         | 10.0    |         | 12.5 | ns |

| t <sub>EABDATACO</sub> |         | 2.0     |         | 3.4  | ns |

| t <sub>EABDATASU</sub> | 5.3     |         | 5.6     |      | ns |

| t <sub>EABDATAH</sub>  | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWESU</sub>   | 5.5     |         | 5.8     |      | ns |

| t <sub>EABWEH</sub>    | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWDSU</sub>   | 5.5     |         | 5.8     |      | ns |

| t <sub>EABWDH</sub>    | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWASU</sub>   | 2.1     |         | 2.7     |      | ns |

| t <sub>EABWAH</sub>    | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWO</sub>     |         | 9.5     |         | 11.8 | ns |

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

Tables 57 through 63 show EPF10K70 device internal and external timing parameters.

| Symbol              | -2 Spee | d Grade | -3 Spe | -3 Speed Grade |     | -4 Speed Grade |    |

|---------------------|---------|---------|--------|----------------|-----|----------------|----|

|                     | Min     | Max     | Min    | Max            | Min | Max            |    |

| t <sub>LUT</sub>    |         | 1.3     |        | 1.5            |     | 2.0            | ns |

| t <sub>CLUT</sub>   |         | 0.4     |        | 0.4            |     | 0.5            | ns |

| t <sub>RLUT</sub>   |         | 1.5     |        | 1.6            |     | 2.0            | ns |

| t <sub>PACKED</sub> |         | 0.8     |        | 0.9            |     | 1.3            | ns |

| t <sub>EN</sub>     |         | 0.8     |        | 0.9            |     | 1.2            | ns |

| t <sub>CICO</sub>   |         | 0.2     |        | 0.2            |     | 0.3            | ns |

| t <sub>CGEN</sub>   |         | 1.0     |        | 1.1            |     | 1.4            | ns |

| t <sub>CGENR</sub>  |         | 1.1     |        | 1.2            |     | 1.5            | ns |

| t <sub>CASC</sub>   |         | 1.0     |        | 1.1            |     | 1.3            | ns |

| t <sub>C</sub>      |         | 0.7     |        | 0.8            |     | 1.0            | ns |

| t <sub>CO</sub>     |         | 0.9     |        | 1.0            |     | 1.4            | ns |

| t <sub>COMB</sub>   |         | 0.4     |        | 0.5            |     | 0.7            | ns |

| t <sub>SU</sub>     | 1.9     |         | 2.1    |                | 2.6 |                | ns |

| t <sub>H</sub>      | 2.1     |         | 2.3    |                | 3.1 |                | ns |

| t <sub>PRE</sub>    |         | 0.9     |        | 1.0            |     | 1.4            | ns |

| t <sub>CLR</sub>    |         | 0.9     |        | 1.0            |     | 1.4            | ns |

| t <sub>CH</sub>     | 4.0     |         | 4.0    |                | 4.0 |                | ns |

| t <sub>CL</sub>     | 4.0     |         | 4.0    |                | 4.0 |                | ns |

Tables 71 through 77 show EPF10K50V device internal and external timing parameters.

| Symbol              | -1 Spee | d Grade | -2 Speed Grade |     | -3 Spee | ed Grade | -4 Speed Grade |     | Unit |

|---------------------|---------|---------|----------------|-----|---------|----------|----------------|-----|------|

|                     | Min     | Max     | Min            | Max | Min     | Max      | Min            | Max |      |

| t <sub>LUT</sub>    |         | 0.9     |                | 1.0 |         | 1.3      |                | 1.6 | ns   |

| t <sub>CLUT</sub>   |         | 0.1     |                | 0.5 |         | 0.6      |                | 0.6 | ns   |

| t <sub>RLUT</sub>   |         | 0.5     |                | 0.8 |         | 0.9      |                | 1.0 | ns   |

| t <sub>PACKED</sub> |         | 0.4     |                | 0.4 |         | 0.5      |                | 0.7 | ns   |

| t <sub>EN</sub>     |         | 0.7     |                | 0.9 |         | 1.1      |                | 1.4 | ns   |

| tcico               |         | 0.2     |                | 0.2 |         | 0.2      |                | 0.3 | ns   |

| t <sub>CGEN</sub>   |         | 0.8     |                | 0.7 |         | 0.8      |                | 1.2 | ns   |

| t <sub>CGENR</sub>  |         | 0.4     |                | 0.3 |         | 0.3      |                | 0.4 | ns   |

| t <sub>CASC</sub>   |         | 0.7     |                | 0.7 |         | 0.8      |                | 0.9 | ns   |

| t <sub>C</sub>      |         | 0.3     |                | 1.0 |         | 1.3      |                | 1.5 | ns   |

| t <sub>CO</sub>     |         | 0.5     |                | 0.7 |         | 0.9      |                | 1.0 | ns   |

| t <sub>COMB</sub>   |         | 0.4     |                | 0.4 |         | 0.5      |                | 0.6 | ns   |

| t <sub>SU</sub>     | 0.8     |         | 1.6            |     | 2.2     |          | 2.5            |     | ns   |

| t <sub>H</sub>      | 0.5     |         | 0.8            |     | 1.0     |          | 1.4            |     | ns   |

| t <sub>PRE</sub>    |         | 0.8     |                | 0.4 |         | 0.5      |                | 0.5 | ns   |

| t <sub>CLR</sub>    |         | 0.8     |                | 0.4 |         | 0.5      |                | 0.5 | ns   |

| t <sub>CH</sub>     | 2.0     |         | 4.0            |     | 4.0     |          | 4.0            |     | ns   |

| t <sub>CL</sub>     | 2.0     |         | 4.0            |     | 4.0     |          | 4.0            | 1   | ns   |

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

Tables 99 through 105 show EPF10K100A device internal and external timing parameters.

| Table 99. EPF10     | K100A Devic | e LE Timing I | Microparame | ters Not | e (1)   |          |      |  |

|---------------------|-------------|---------------|-------------|----------|---------|----------|------|--|

| Symbol              | -1 Spee     | ed Grade      | -2 Spee     | ed Grade | -3 Spee | ed Grade | Unit |  |

|                     | Min         | Max           | Min         | Max      | Min     | Max      |      |  |

| t <sub>LUT</sub>    |             | 1.0           |             | 1.2      |         | 1.4      | ns   |  |

| t <sub>CLUT</sub>   |             | 0.8           |             | 0.9      |         | 1.1      | ns   |  |

| t <sub>RLUT</sub>   |             | 1.4           |             | 1.6      |         | 1.9      | ns   |  |

| t <sub>PACKED</sub> |             | 0.4           |             | 0.5      |         | 0.5      | ns   |  |

| t <sub>EN</sub>     |             | 0.6           |             | 0.7      |         | 0.8      | ns   |  |

| t <sub>CICO</sub>   |             | 0.2           |             | 0.2      |         | 0.3      | ns   |  |

| t <sub>CGEN</sub>   |             | 0.4           |             | 0.4      |         | 0.6      | ns   |  |

| t <sub>CGENR</sub>  |             | 0.6           |             | 0.7      |         | 0.8      | ns   |  |

| t <sub>CASC</sub>   |             | 0.7           |             | 0.9      |         | 1.0      | ns   |  |

| t <sub>C</sub>      |             | 0.9           |             | 1.0      |         | 1.2      | ns   |  |

| t <sub>CO</sub>     |             | 0.2           |             | 0.3      |         | 0.3      | ns   |  |

| t <sub>COMB</sub>   |             | 0.6           |             | 0.7      |         | 0.8      | ns   |  |

| t <sub>SU</sub>     | 0.8         |               | 1.0         |          | 1.2     |          | ns   |  |

| t <sub>H</sub>      | 0.3         |               | 0.5         |          | 0.5     |          | ns   |  |

| t <sub>PRE</sub>    |             | 0.3           |             | 0.3      |         | 0.4      | ns   |  |

| t <sub>CLR</sub>    |             | 0.3           |             | 0.3      |         | 0.4      | ns   |  |

| t <sub>CH</sub>     | 2.5         |               | 3.5         |          | 4.0     |          | ns   |  |

| t <sub>CL</sub>     | 2.5         |               | 3.5         |          | 4.0     |          | ns   |  |

| Symbol                   | -1 Speed Grade |     | -2 Speed Grade |     | -3 Spee | Unit |    |

|--------------------------|----------------|-----|----------------|-----|---------|------|----|

|                          | Min            | Max | Min            | Max | Min     | Max  |    |

| t <sub>DIN2IOE</sub>     |                | 4.8 |                | 5.4 |         | 6.0  | ns |

| t <sub>DIN2LE</sub>      |                | 2.0 |                | 2.4 |         | 2.7  | ns |

| t <sub>DIN2DATA</sub>    |                | 2.4 |                | 2.7 |         | 2.9  | ns |

| t <sub>DCLK2IOE</sub>    |                | 2.6 |                | 3.0 |         | 3.5  | ns |

| t <sub>DCLK2LE</sub>     |                | 2.0 |                | 2.4 |         | 2.7  | ns |

| t <sub>SAMELAB</sub>     |                | 0.1 |                | 0.1 |         | 0.1  | ns |

| t <sub>SAMEROW</sub>     |                | 1.5 |                | 1.7 |         | 1.9  | ns |

| t <sub>SAME</sub> COLUMN |                | 5.5 |                | 6.5 |         | 7.4  | ns |

| t <sub>DIFFROW</sub>     |                | 7.0 |                | 8.2 |         | 9.3  | ns |

| t <sub>TWOROWS</sub>     |                | 8.5 |                | 9.9 |         | 11.2 | ns |

| t <sub>LEPERIPH</sub>    |                | 3.9 |                | 4.2 |         | 4.5  | ns |

| t <sub>LABCARRY</sub>    |                | 0.2 |                | 0.2 |         | 0.3  | ns |

| t <sub>LABCASC</sub>     |                | 0.4 |                | 0.5 |         | 0.6  | ns |

#### Table 104. EPF10K100A Device External Timing Parameters Note (1)

| Symbol                            | -1 Spee | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |    |

|-----------------------------------|---------|----------------|-----|----------------|-----|----------------|----|

|                                   | Min     | Max            | Min | Max            | Min | Max            |    |

| t <sub>DRR</sub>                  |         | 12.5           |     | 14.5           |     | 17.0           | ns |

| t <sub>INSU</sub> (2), (3)        | 3.7     |                | 4.5 |                | 5.1 |                | ns |

| t <sub>INH</sub> (3)              | 0.0     |                | 0.0 |                | 0.0 |                | ns |

| <sup>t</sup> оитсо <sup>(3)</sup> | 2.0     | 5.3            | 2.0 | 6.1            | 2.0 | 7.2            | ns |

7.4

| Table 105. EPF10K10    | OA Device Ext  | ernal Bidirec | tional Timing  | g Parameters | Note (1)       | )    |      |

|------------------------|----------------|---------------|----------------|--------------|----------------|------|------|

| Symbol                 | -1 Speed Grade |               | -2 Speed Grade |              | -3 Speed Grade |      | Unit |

|                        | Min            | Max           | Min            | Max          | Min            | Max  | 1    |

| t <sub>INSUBIDIR</sub> | 4.9            |               | 5.8            |              | 6.8            |      | ns   |

| t <sub>INHBIDIR</sub>  | 0.0            |               | 0.0            |              | 0.0            |      | ns   |

| toutcobidir            | 2.0            | 5.3           | 2.0            | 6.1          | 2.0            | 7.2  | ns   |

| t <sub>XZBIDIR</sub>   |                | 7.4           |                | 8.6          |                | 10.1 | ns   |

8.6

t<sub>ZXBIDIR</sub>

ns

10.1

| Symbol              | -1 Speed Grade |     | -2 Speed Grade |      | -3 Speed Grade |      | Unit |  |

|---------------------|----------------|-----|----------------|------|----------------|------|------|--|

|                     | Min            | Max | Min            | Max  | Min            | Max  |      |  |

| t <sub>IOD</sub>    |                | 1.2 |                | 1.3  |                | 1.6  | ns   |  |

| t <sub>IOC</sub>    |                | 0.4 |                | 0.4  |                | 0.5  | ns   |  |

| t <sub>IOCO</sub>   |                | 0.8 |                | 0.9  |                | 1.1  | ns   |  |

| t <sub>IOCOMB</sub> |                | 0.7 |                | 0.7  |                | 0.8  | ns   |  |

| t <sub>IOSU</sub>   | 2.7            |     | 3.1            |      | 3.6            |      | ns   |  |

| t <sub>IOH</sub>    | 0.2            |     | 0.3            |      | 0.3            |      | ns   |  |

| t <sub>IOCLR</sub>  |                | 1.2 |                | 1.3  |                | 1.6  | ns   |  |

| t <sub>OD1</sub>    |                | 3.2 |                | 3.6  |                | 4.2  | ns   |  |

| t <sub>OD2</sub>    |                | 5.9 |                | 6.7  |                | 7.8  | ns   |  |

| t <sub>OD3</sub>    |                | 8.7 |                | 9.8  |                | 11.5 | ns   |  |

| t <sub>XZ</sub>     |                | 3.8 |                | 4.3  |                | 5.0  | ns   |  |

| t <sub>ZX1</sub>    |                | 3.8 |                | 4.3  |                | 5.0  | ns   |  |

| t <sub>ZX2</sub>    |                | 6.5 |                | 7.4  |                | 8.6  | ns   |  |

| t <sub>ZX3</sub>    |                | 9.3 |                | 10.5 |                | 12.3 | ns   |  |

| t <sub>INREG</sub>  |                | 8.2 |                | 9.3  |                | 10.9 | ns   |  |

| t <sub>IOFD</sub>   |                | 9.0 |                | 10.2 |                | 12.0 | ns   |  |

| t <sub>INCOMB</sub> |                | 9.0 |                | 10.2 |                | 12.0 | ns   |  |

- (1) All timing parameters are described in Tables 32 through 37 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

# ClockLock & ClockBoost Timing Parameters

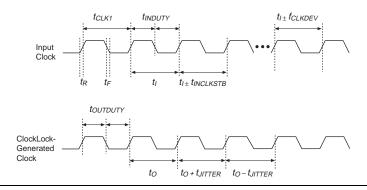

For the ClockLock and ClockBoost circuitry to function properly, the incoming clock must meet certain requirements. If these specifications are not met, the circuitry may not lock onto the incoming clock, which generates an erroneous clock within the device. The clock generated by the ClockLock and ClockBoost circuitry must also meet certain specifications. If the incoming clock meets these requirements during configuration, the ClockLock and ClockBoost circuitry will lock onto the clock during configuration. The circuit will be ready for use immediately after configuration. Figure 31 illustrates the incoming and generated clock specifications.

## Figure 31. Specifications for the Incoming & Generated Clocks

The  $t_l$  parameter refers to the nominal input clock period; the  $t_0$  parameter refers to the nominal output clock period.

## Table 113 summarizes the ClockLock and ClockBoost parameters.

| Table 113. ClockLock & ClockBoost Parameters  (Part 1 of 2) |                                                                         |      |     |      |      |  |  |  |

|-------------------------------------------------------------|-------------------------------------------------------------------------|------|-----|------|------|--|--|--|

| Symbol                                                      | Parameter                                                               | Min  | Тур | Max  | Unit |  |  |  |

| t <sub>R</sub>                                              | Input rise time                                                         |      |     | 2    | ns   |  |  |  |

| t <sub>F</sub>                                              | Input fall time                                                         |      |     | 2    | ns   |  |  |  |

| t <sub>INDUTY</sub>                                         | Input duty cycle                                                        | 45   |     | 55   | %    |  |  |  |

| f <sub>CLK1</sub>                                           | Input clock frequency (ClockBoost clock multiplication factor equals 1) | 30   |     | 80   | MHz  |  |  |  |

| t <sub>CLK1</sub>                                           | Input clock period (ClockBoost clock multiplication factor equals 1)    | 12.5 |     | 33.3 | ns   |  |  |  |

| f <sub>CLK2</sub>                                           | Input clock frequency (ClockBoost clock multiplication factor equals 2) | 16   |     | 50   | MHz  |  |  |  |

| t <sub>CLK2</sub>                                           | Input clock period (ClockBoost clock multiplication factor equals 2)    | 20   |     | 62.5 | ns   |  |  |  |

## Altera Corporation

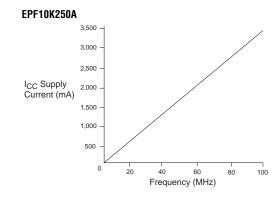

## Figure 32. I<sub>CCACTIVE</sub> vs. Operating Frequency (Part 3 of 3)

## Configuration & Operation

The FLEX 10K architecture supports several configuration schemes. This section summarizes the device operating modes and available device configuration schemes.

See Application Note 116 (Configuring APEX 20K, FLEX 10K & FLEX 6000 Devices) for detailed descriptions of device configuration options, device configuration pins, and for information on configuring FLEX 10K devices, including sample schematics, timing diagrams, and configuration parameters.

## **Operating Modes**

The FLEX 10K architecture uses SRAM configuration elements that require configuration data to be loaded every time the circuit powers up. The process of physically loading the SRAM data into the device is called *configuration*. Before configuration, as VCC rises, the device initiates a Power-On Reset (POR). This POR event clears the device and prepares it for configuration. The FLEX 10K POR time does not exceed 50 µs.

During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called *command mode*; normal device operation is called *user mode*.