## E·XFL

#### Altera - EPF10K10ATC144-1N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Product Status                 | Active                                                         |

|--------------------------------|----------------------------------------------------------------|

| Number of LABs/CLBs            | 72                                                             |

| Number of Logic Elements/Cells | 576                                                            |

| Total RAM Bits                 | -                                                              |

| Number of I/O                  | 102                                                            |

| Number of Gates                |                                                                |

| Voltage - Supply               | 3V ~ 3.6V                                                      |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                |

| Package / Case                 | 144-LQFP                                                       |

| Supplier Device Package        | 144-TQFP (20x20)                                               |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=epf10k10atc144-1n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Flexible interconnect

- FastTrack<sup>®</sup> Interconnect continuous routing structure for fast, predictable interconnect delays

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

- Dedicated cascade chain that implements high-speed, high-fan-in logic functions (automatically used by software tools and megafunctions)

- Tri-state emulation that implements internal tri-state buses

- Up to six global clock signals and four global clear signals

- Powerful I/O pins

- Individual tri-state output enable control for each pin

- Open-drain option on each I/O pin

- Programmable output slew-rate control to reduce switching noise

- FLEX 10KA devices support hot-socketing

- Peripheral register for fast setup and clock-to-output delay

- Flexible package options

- Available in a variety of packages with 84 to 600 pins (see Tables 4 and 5)

- Pin-compatibility with other FLEX 10K devices in the same package

- FineLine BGA<sup>™</sup> packages maximize board space efficiency

- Software design support and automatic place-and-route provided by Altera development systems for Windows-based PCs and Sun SPARCstation, HP 9000 Series 700/800 workstations

- Additional design entry and simulation support provided by EDIF 2 0 0 and 3 0 0 netlist files, library of parameterized modules (LPM), DesignWare components, Verilog HDL, VHDL, and other interfaces to popular EDA tools from manufacturers such as Cadence, Exemplar Logic, Mentor Graphics, OrCAD, Synopsys, Synplicity, VeriBest, and Viewlogic

For more information, see the following documents:

- Configuration Devices for APEX & FLEX Devices Data Sheet

- BitBlaster Serial Download Cable Data Sheet

- ByteBlasterMV Parallel Port Download Cable Data Sheet

- Application Note 116 (Configuring APEX 20K, FLEX 10K & FLEX 6000 Devices)

FLEX 10K devices are supported by Altera development systems; single, integrated packages that offer schematic, text (including AHDL), and waveform design entry, compilation and logic synthesis, full simulation and worst-case timing analysis, and device configuration. The Altera software provides EDIF 2 0 0 and 3 0 0, LPM, VHDL, Verilog HDL, and other interfaces for additional design entry and simulation support from other industry-standard PC- and UNIX workstation-based EDA tools.

The Altera software works easily with common gate array EDA tools for synthesis and simulation. For example, the Altera software can generate Verilog HDL files for simulation with tools such as Cadence Verilog-XL. Additionally, the Altera software contains EDA libraries that use devicespecific features such as carry chains which are used for fast counter and arithmetic functions. For instance, the Synopsys Design Compiler library supplied with the Altera development systems include DesignWare functions that are optimized for the FLEX 10K architecture.

The Altera development systems run on Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800 workstations.

See the MAX+PLUS II Programmable Logic Development System & Software Data Sheet for more information.

# Functional Description

Each FLEX 10K device contains an embedded array to implement memory and specialized logic functions, and a logic array to implement general logic.

The embedded array consists of a series of EABs. When implementing memory functions, each EAB provides 2,048 bits, which can be used to create RAM, ROM, dual-port RAM, or first-in first-out (FIFO) functions. When implementing logic, each EAB can contribute 100 to 600 gates towards complex logic functions, such as multipliers, microcontrollers, state machines, and DSP functions. EABs can be used independently, or multiple EABs can be combined to implement larger functions.

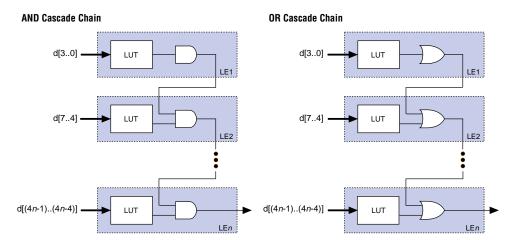

#### Cascade Chain

With the cascade chain, the FLEX 10K architecture can implement functions that have a very wide fan-in. Adjacent LUTs can be used to compute portions of the function in parallel; the cascade chain serially connects the intermediate values. The cascade chain can use a logical AND or logical OR (via De Morgan's inversion) to connect the outputs of adjacent LEs. Each additional LE provides four more inputs to the effective width of a function, with a delay as low as 0.7 ns per LE. Cascade chain logic can be created automatically by the Compiler during design processing, or manually by the designer during design entry.

Cascade chains longer than eight bits are implemented automatically by linking several LABs together. For easier routing, a long cascade chain skips every other LAB in a row. A cascade chain longer than one LAB skips either from even-numbered LAB to even-numbered LAB, or from odd-numbered LAB to odd-numbered LAB (e.g., the last LE of the first LAB in a row cascades to the first LE of the third LAB). The cascade chain does not cross the center of the row (e.g., in the EPF10K50 device, the cascade chain stops at the eighteenth LAB and a new one begins at the nineteenth LAB). This break is due to the EAB's placement in the middle of the row.

Figure 8 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in. These examples show functions of 4n variables implemented with n LEs. The LE delay is as low as 1.6 ns; the cascade chain delay is as low as 0.7 ns. With the cascade chain, 3.7 ns is needed to decode a 16-bit address.

#### Figure 8. Cascade Chain Operation

Altera Corporation

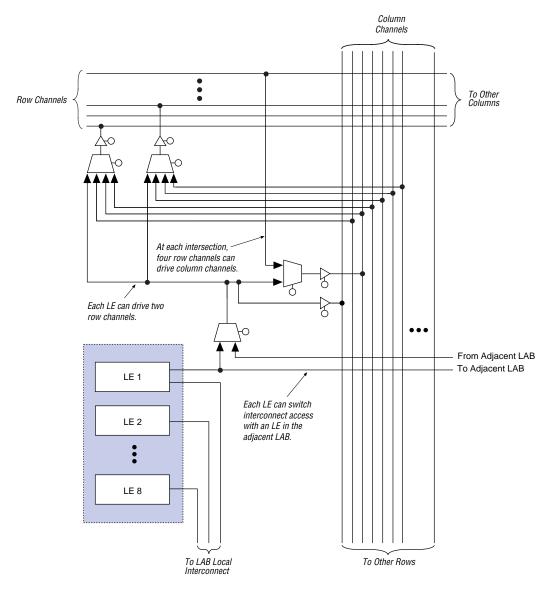

#### Figure 11. LAB Connections to Row & Column Interconnect

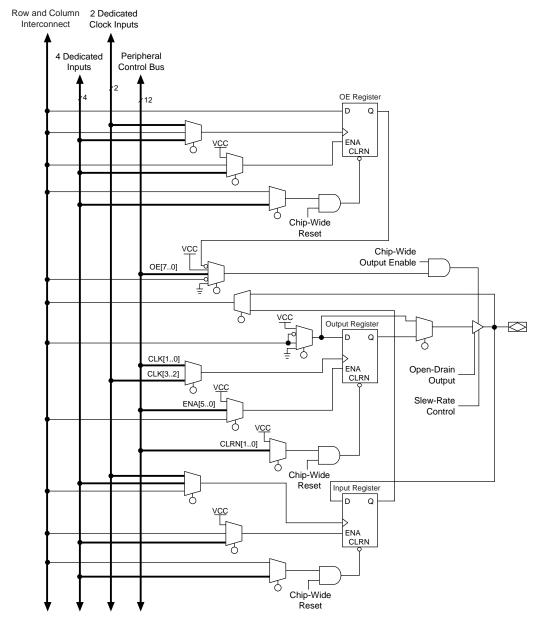

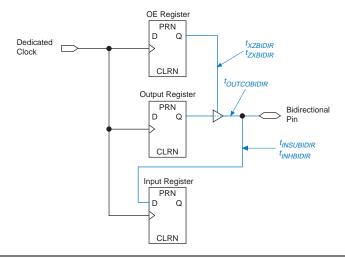

#### Figure 13. Bidirectional I/O Registers

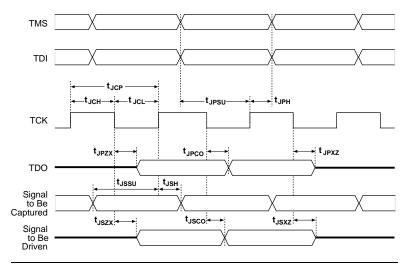

Figure 18 shows the timing requirements for the JTAG signals.

Figure 18. JTAG Waveforms

Table 16 shows the timing parameters and values for FLEX 10K devices.

| Table 1           | 6. JTAG Timing Parameters & Values             |     |     |      |

|-------------------|------------------------------------------------|-----|-----|------|

| Symbol            | Parameter                                      | Min | Мах | Unit |

| t <sub>JCP</sub>  | TCK clock period                               | 100 |     | ns   |

| t <sub>JCH</sub>  | TCK clock high time                            | 50  |     | ns   |

| t <sub>JCL</sub>  | TCK clock low time                             | 50  |     | ns   |

| t <sub>JPSU</sub> | JTAG port setup time                           | 20  |     | ns   |

| t <sub>JPH</sub>  | JTAG port hold time                            | 45  |     | ns   |

| t <sub>JPCO</sub> | JTAG port clock to output                      |     | 25  | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output       |     | 25  | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance       |     | 25  | ns   |

| t <sub>JSSU</sub> | Capture register setup time                    | 20  |     | ns   |

| t <sub>JSH</sub>  | Capture register hold time                     | 45  |     | ns   |

| t <sub>JSCO</sub> | Update register clock to output                |     | 35  | ns   |

| t <sub>JSZX</sub> | Update register high-impedance to valid output |     | 35  | ns   |

| t <sub>JSXZ</sub> | Update register valid output to high impedance |     | 35  | ns   |

| Table 1            | 8. FLEX 10K 5.0-V Device Reco                         | mmended Operating Conditions |             |                   |      |

|--------------------|-------------------------------------------------------|------------------------------|-------------|-------------------|------|

| Symbol             | Parameter                                             | Conditions                   | Min         | Max               | Unit |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers   | (3), (4)                     | 4.75 (4.50) | 5.25 (5.50)       | V    |

| V <sub>CCIO</sub>  | Supply voltage for output<br>buffers, 5.0-V operation | (3), (4)                     | 4.75 (4.50) | 5.25 (5.50)       | V    |

|                    | Supply voltage for output<br>buffers, 3.3-V operation | (3), (4)                     | 3.00 (3.00) | 3.60 (3.60)       | V    |

| VI                 | Input voltage                                         |                              | -0.5        | $V_{CCINT} + 0.5$ | V    |

| Vo                 | Output voltage                                        |                              | 0           | V <sub>CCIO</sub> | V    |

| T <sub>A</sub>     | Ambient temperature                                   | For commercial use           | 0           | 70                | °C   |

|                    |                                                       | For industrial use           | -40         | 85                | °C   |

| ТJ                 | Operating temperature                                 | For commercial use           | 0           | 85                | °C   |

|                    |                                                       | For industrial use           | -40         | 100               | °C   |

| t <sub>R</sub>     | Input rise time                                       |                              |             | 40                | ns   |

| t <sub>F</sub>     | Input fall time                                       |                              |             | 40                | ns   |

| Table 2            | 7. FLEX 10KA 3.3-V Device Rec                         | ommended Operating Conditions |             |                   |      |

|--------------------|-------------------------------------------------------|-------------------------------|-------------|-------------------|------|

| Symbol             | Parameter                                             | Conditions                    | Min         | Max               | Unit |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers   | (3), (4)                      | 3.00 (3.00) | 3.60 (3.60)       | V    |

| V <sub>CCIO</sub>  | Supply voltage for output<br>buffers, 3.3-V operation | (3), (4)                      | 3.00 (3.00) | 3.60 (3.60)       | V    |

|                    | Supply voltage for output<br>buffers, 2.5-V operation | (3), (4)                      | 2.30 (2.30) | 2.70 (2.70)       | V    |

| VI                 | Input voltage                                         | (5)                           | -0.5        | 5.75              | V    |

| Vo                 | Output voltage                                        |                               | 0           | V <sub>CCIO</sub> | V    |

| Τ <sub>Α</sub>     | Ambient temperature                                   | For commercial use            | 0           | 70                | °C   |

|                    |                                                       | For industrial use            | -40         | 85                | °C   |

| ТJ                 | Operating temperature                                 | For commercial use            | 0           | 85                | °C   |

|                    |                                                       | For industrial use            | -40         | 100               | °C   |

| t <sub>R</sub>     | Input rise time                                       |                               |             | 40                | ns   |

| t <sub>F</sub>     | Input fall time                                       |                               |             | 40                | ns   |

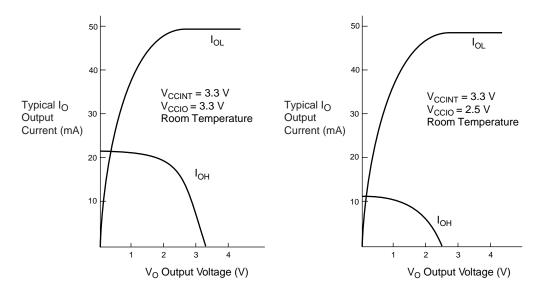

Figure 23. Output Drive Characteristics for EPF10K250A Device

### Timing Model

The continuous, high-performance FastTrack Interconnect routing resources ensure predictable performance and accurate simulation and timing analysis. This predictable performance contrasts with that of FPGAs, which use a segmented connection scheme and therefore have unpredictable performance.

Device performance can be estimated by following the signal path from a source, through the interconnect, to the destination. For example, the registered performance between two LEs on the same row can be calculated by adding the following parameters:

- LE register clock-to-output delay  $(t_{CO})$

- Interconnect delay (*t*<sub>SAMEROW</sub>)

- LE look-up table delay ( $t_{LUT}$ )

- LE register setup time  $(t_{SU})$

The routing delay depends on the placement of the source and destination LEs. A more complex registered path may involve multiple combinatorial LEs between the source and destination LEs.

Figure 28. Synchronous Bidirectional Pin External Timing Model

Tables 32 through 36 describe the FLEX 10K device internal timing parameters. These internal timing parameters are expressed as worst-case values. Using hand calculations, these parameters can be used to estimate design performance. However, before committing designs to silicon, actual worst-case performance should be modeled using timing simulation and analysis. Tables 37 through 38 describe FLEX 10K external timing parameters.

| Symbol              | Parameter                               | Conditions |

|---------------------|-----------------------------------------|------------|

| t <sub>LUT</sub>    | LUT delay for data-in                   |            |

| t <sub>CLUT</sub>   | LUT delay for carry-in                  |            |

| t <sub>RLUT</sub>   | LUT delay for LE register feedback      |            |

| t <sub>PACKED</sub> | Data-in to packed register delay        |            |

| t <sub>EN</sub>     | LE register enable delay                |            |

| tcico               | Carry-in to carry-out delay             |            |

| t <sub>CGEN</sub>   | Data-in to carry-out delay              |            |

| t <sub>CGENR</sub>  | LE register feedback to carry-out delay |            |

| t <sub>CASC</sub>   | Cascade-in to cascade-out delay         |            |

| t <sub>C</sub>      | LE register control signal delay        |            |

| t <sub>CO</sub>     | LE register clock-to-output delay       |            |

| t <sub>COMB</sub>   | Combinatorial delay                     |            |

| Symbol                | -3 Spee | d Grade | -4 Spee | ed Grade | Unit |

|-----------------------|---------|---------|---------|----------|------|

|                       | Min     | Max     | Min     | Max      |      |

| t <sub>DIN2IOE</sub>  |         | 8.4     |         | 10.2     | ns   |

| t <sub>DIN2LE</sub>   |         | 3.6     |         | 4.8      | ns   |

| t <sub>DIN2DATA</sub> |         | 5.5     |         | 7.2      | ns   |

| t <sub>DCLK2IOE</sub> |         | 4.6     |         | 6.2      | ns   |

| t <sub>DCLK2LE</sub>  |         | 3.6     |         | 4.8      | ns   |

| t <sub>SAMELAB</sub>  |         | 0.3     |         | 0.3      | ns   |

| t <sub>SAMEROW</sub>  |         | 3.3     |         | 3.7      | ns   |

| <i>t</i> SAMECOLUMN   |         | 3.9     |         | 4.1      | ns   |

| t <sub>DIFFROW</sub>  |         | 7.2     |         | 7.8      | ns   |

| t <sub>TWOROWS</sub>  |         | 10.5    |         | 11.5     | ns   |

| t <sub>LEPERIPH</sub> |         | 7.5     |         | 8.2      | ns   |

| t <sub>LABCARRY</sub> |         | 0.4     |         | 0.6      | ns   |

| t <sub>LABCASC</sub>  |         | 2.4     |         | 3.0      | ns   |

| Symbol                        | -3 Spee | d Grade | -4 Spee | d Grade | Unit |

|-------------------------------|---------|---------|---------|---------|------|

|                               | Min     | Max     | Min     | Max     |      |

| t <sub>DRR</sub>              |         | 17.2    |         | 21.1    | ns   |

| t <sub>INSU</sub> (2), (3)    | 5.7     |         | 6.4     |         | ns   |

| t <sub>INH</sub> (3)          | 0.0     |         | 0.0     |         | ns   |

| <b>t</b> оитсо <sup>(3)</sup> | 2.0     | 8.8     | 2.0     | 11.2    | ns   |

| Table 56. EPF10K30, EPF10K40 & EPF10K50 Device External Bidirectional Timing Parameters No |        |          |         |          |      |  |  |  |  |  |

|--------------------------------------------------------------------------------------------|--------|----------|---------|----------|------|--|--|--|--|--|

| Symbol                                                                                     | -3 Spe | ed Grade | -4 Spee | ed Grade | Unit |  |  |  |  |  |

|                                                                                            | Min    | Max      | Min     | Max      |      |  |  |  |  |  |

| t <sub>INSUBIDIR</sub>                                                                     | 4.1    |          | 4.6     |          | ns   |  |  |  |  |  |

| t <sub>INHBIDIR</sub>                                                                      | 0.0    |          | 0.0     |          | ns   |  |  |  |  |  |

| toutcobidir                                                                                | 2.0    | 8.8      | 2.0     | 11.2     | ns   |  |  |  |  |  |

| t <sub>XZBIDIR</sub>                                                                       |        | 12.3     |         | 15.0     | ns   |  |  |  |  |  |

| t <sub>ZXBIDIR</sub>                                                                       |        | 12.3     |         | 15.0     | ns   |  |  |  |  |  |

| Symbol                 | -2 Speed | -2 Speed Grade |      | -3 Speed Grade |      | -4 Speed Grade |    |  |

|------------------------|----------|----------------|------|----------------|------|----------------|----|--|

|                        | Min      | Max            | Min  | Max            | Min  | Max            |    |  |

| t <sub>EABAA</sub>     |          | 12.1           |      | 13.7           |      | 17.0           | ns |  |

| t <sub>EABRCCOMB</sub> | 12.1     |                | 13.7 |                | 17.0 |                | ns |  |

| t <sub>EABRCREG</sub>  | 8.6      |                | 9.7  |                | 11.9 |                | ns |  |

| t <sub>EABWP</sub>     | 5.2      |                | 5.8  |                | 7.2  |                | ns |  |

| t <sub>EABWCCOMB</sub> | 6.5      |                | 7.3  |                | 9.0  |                | ns |  |

| t <sub>EABWCREG</sub>  | 11.6     |                | 13.0 |                | 16.0 |                | ns |  |

| t <sub>EABDD</sub>     |          | 8.8            |      | 10.0           |      | 12.5           | ns |  |

| t <sub>EABDATACO</sub> |          | 1.7            |      | 2.0            |      | 3.4            | ns |  |

| t <sub>EABDATASU</sub> | 4.7      |                | 5.3  |                | 5.6  |                | ns |  |

| t <sub>EABDATAH</sub>  | 0.0      |                | 0.0  |                | 0.0  |                | ns |  |

| t <sub>EABWESU</sub>   | 4.9      |                | 5.5  |                | 5.8  |                | ns |  |

| t <sub>EABWEH</sub>    | 0.0      |                | 0.0  |                | 0.0  |                | ns |  |

| t <sub>EABWDSU</sub>   | 1.8      |                | 2.1  |                | 2.7  |                | ns |  |

| t <sub>EABWDH</sub>    | 0.0      |                | 0.0  |                | 0.0  |                | ns |  |

| t <sub>EABWASU</sub>   | 4.1      |                | 4.7  |                | 5.8  |                | ns |  |

| t <sub>EABWAH</sub>    | 0.0      |                | 0.0  |                | 0.0  |                | ns |  |

| t <sub>EABWO</sub>     |          | 8.4            |      | 9.5            |      | 11.8           | ns |  |

| Symbol                 | -3DX Sne | ed Grade | -3 Speed Grade |     | -4 Speed Grade |      | Unit |

|------------------------|----------|----------|----------------|-----|----------------|------|------|

| oyinbor                | Min      | Max      | Min            | Max | Min            | Max  | -    |

|                        | IVIII    |          | IVIII          |     | IVIIII         | -    |      |

| t <sub>EABDATA1</sub>  |          | 1.5      |                | 1.5 |                | 1.9  | ns   |

| t <sub>EABDATA2</sub>  |          | 4.8      |                | 4.8 |                | 6.0  | ns   |

| t <sub>EABWE1</sub>    |          | 1.0      |                | 1.0 |                | 1.2  | ns   |

| t <sub>EABWE2</sub>    |          | 5.0      |                | 5.0 |                | 6.2  | ns   |

| t <sub>EABCLK</sub>    |          | 1.0      |                | 1.0 |                | 2.2  | ns   |

| t <sub>EABCO</sub>     |          | 0.5      |                | 0.5 |                | 0.6  | ns   |

| t <sub>EABBYPASS</sub> |          | 1.5      |                | 1.5 |                | 1.9  | ns   |

| t <sub>EABSU</sub>     | 1.5      |          | 1.5            |     | 1.8            |      | ns   |

| t <sub>EABH</sub>      | 2.0      |          | 2.0            |     | 2.5            |      | ns   |

| t <sub>AA</sub>        |          | 8.7      |                | 8.7 |                | 10.7 | ns   |

| t <sub>WP</sub>        | 5.8      |          | 5.8            |     | 7.2            |      | ns   |

| t <sub>WDSU</sub>      | 1.6      |          | 1.6            |     | 2.0            |      | ns   |

| t <sub>WDH</sub>       | 0.3      |          | 0.3            |     | 0.4            |      | ns   |

| t <sub>WASU</sub>      | 0.5      |          | 0.5            |     | 0.6            |      | ns   |

| t <sub>WAH</sub>       | 1.0      |          | 1.0            |     | 1.2            |      | ns   |

| t <sub>WO</sub>        |          | 5.0      |                | 5.0 |                | 6.2  | ns   |

| t <sub>DD</sub>        |          | 5.0      |                | 5.0 |                | 6.2  | ns   |

| t <sub>EABOUT</sub>    |          | 0.5      |                | 0.5 |                | 0.6  | ns   |

| t <sub>EABCH</sub>     | 4.0      |          | 4.0            |     | 4.0            |      | ns   |

| t <sub>EABCL</sub>     | 5.8      |          | 5.8            | ĺ   | 7.2            |      | ns   |

| Table 68. EPF10K100 Device Interconn                                    | -        |           | 1       | Note (1)       |     |                | Unit |

|-------------------------------------------------------------------------|----------|-----------|---------|----------------|-----|----------------|------|

| Symbol                                                                  | -3DX Spe | eed Grade | -3 Spee | -3 Speed Grade |     | -4 Speed Grade |      |

|                                                                         | Min      | Max       | Min     | Max            | Min | Max            |      |

| t <sub>DIN2IOE</sub>                                                    |          | 10.3      |         | 10.3           |     | 12.2           | ns   |

| t <sub>DIN2LE</sub>                                                     |          | 4.8       |         | 4.8            |     | 6.0            | ns   |

| t <sub>DIN2DATA</sub>                                                   |          | 7.3       |         | 7.3            |     | 11.0           | ns   |

| t <sub>DCLK2IOE</sub> without ClockLock or<br>ClockBoost circuitry      |          | 6.2       |         | 6.2            |     | 7.7            | ns   |

| <i>t<sub>DCLK2IOE</sub></i> with ClockLock or ClockBoost circuitry      |          | 2.3       |         | -              |     | -              | ns   |

| <i>t<sub>DCLK2LE</sub></i> without ClockLock or<br>ClockBoost circuitry |          | 4.8       |         | 4.8            |     | 6.0            | ns   |

| <i>t<sub>DCLK2LE</sub></i> with ClockLock or ClockBoost circuitry       |          | 2.3       |         | -              |     | -              | ns   |

| t <sub>SAMELAB</sub>                                                    |          | 0.4       |         | 0.4            |     | 0.5            | ns   |

| t <sub>SAMEROW</sub>                                                    |          | 4.9       |         | 4.9            |     | 5.5            | ns   |

| t <sub>SAMECOLUMN</sub>                                                 |          | 5.1       |         | 5.1            |     | 5.4            | ns   |

| t <sub>DIFFROW</sub>                                                    |          | 10.0      |         | 10.0           |     | 10.9           | ns   |

| t <sub>TWOROWS</sub>                                                    |          | 14.9      |         | 14.9           |     | 16.4           | ns   |

| t <sub>LEPERIPH</sub>                                                   |          | 6.9       |         | 6.9            |     | 8.1            | ns   |

| t <sub>LABCARRY</sub>                                                   |          | 0.9       |         | 0.9            |     | 1.1            | ns   |

| t <sub>LABCASC</sub>                                                    |          | 3.0       |         | 3.0            |     | 3.2            | ns   |

#### Altera Corporation

#### FLEX 10K Embedded Programmable Logic Device Family Data Sheet

| Symbol              | -1 Spee | ed Grade | -2 Spee | ed Grade | ade -3 Speed Grade |     | -4 Spee | ed Grade | Unit |

|---------------------|---------|----------|---------|----------|--------------------|-----|---------|----------|------|

|                     | Min     | Мах      | Min     | Max      | Min                | Мах | Min     | Max      |      |

| t <sub>IOD</sub>    |         | 1.2      |         | 1.6      |                    | 1.9 |         | 2.1      | ns   |

| t <sub>IOC</sub>    |         | 0.3      |         | 0.4      |                    | 0.5 |         | 0.5      | ns   |

| t <sub>IOCO</sub>   |         | 0.3      |         | 0.3      |                    | 0.4 |         | 0.4      | ns   |

| t <sub>IOCOMB</sub> |         | 0.0      |         | 0.0      |                    | 0.0 |         | 0.0      | ns   |

| t <sub>IOSU</sub>   | 2.8     |          | 2.8     |          | 3.4                |     | 3.9     |          | ns   |

| t <sub>IOH</sub>    | 0.7     |          | 0.8     |          | 1.0                |     | 1.4     |          | ns   |

| t <sub>IOCLR</sub>  |         | 0.5      |         | 0.6      |                    | 0.7 |         | 0.7      | ns   |

| t <sub>OD1</sub>    |         | 2.8      |         | 3.2      |                    | 3.9 |         | 4.7      | ns   |

| t <sub>OD2</sub>    |         | -        |         | -        |                    | -   |         | -        | ns   |

| t <sub>OD3</sub>    |         | 6.5      |         | 6.9      |                    | 7.6 |         | 8.4      | ns   |

| t <sub>XZ</sub>     |         | 2.8      |         | 3.1      |                    | 3.8 |         | 4.6      | ns   |

| t <sub>ZX1</sub>    |         | 2.8      |         | 3.1      |                    | 3.8 |         | 4.6      | ns   |

| t <sub>ZX2</sub>    |         | -        |         | -        |                    | -   |         | -        | ns   |

| t <sub>ZX3</sub>    |         | 6.5      |         | 6.8      |                    | 7.5 |         | 8.3      | ns   |

| t <sub>INREG</sub>  |         | 5.0      |         | 5.7      |                    | 7.0 |         | 9.0      | ns   |

| t <sub>IOFD</sub>   |         | 1.5      |         | 1.9      |                    | 2.3 |         | 2.7      | ns   |

| t <sub>INCOMB</sub> |         | 1.5      |         | 1.9      |                    | 2.3 |         | 2.7      | ns   |

#### FLEX 10K Embedded Programmable Logic Device Family Data Sheet

| Symbol                 | -2 Speed Grade |     | -3 Speed Grade |     | -4 Speed Grade |     | Unit |

|------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                        | Min            | Max | Min            | Max | Min            | Мах | 1    |

| t <sub>EABDATA1</sub>  |                | 1.9 |                | 2.4 |                | 2.4 | ns   |

| t <sub>EABDATA2</sub>  |                | 3.7 |                | 4.7 |                | 4.7 | ns   |

| t <sub>EABWE1</sub>    |                | 1.9 |                | 2.4 |                | 2.4 | ns   |

| t <sub>EABWE2</sub>    |                | 3.7 |                | 4.7 |                | 4.7 | ns   |

| t <sub>EABCLK</sub>    |                | 0.7 |                | 0.9 |                | 0.9 | ns   |

| t <sub>EABCO</sub>     |                | 0.5 |                | 0.6 |                | 0.6 | ns   |

| t <sub>EABBYPASS</sub> |                | 0.6 |                | 0.8 |                | 0.8 | ns   |

| t <sub>EABSU</sub>     | 1.4            |     | 1.8            |     | 1.8            |     | ns   |

| t <sub>EABH</sub>      | 0.0            |     | 0.0            |     | 0.0            |     | ns   |

| t <sub>AA</sub>        |                | 5.6 |                | 7.1 |                | 7.1 | ns   |

| t <sub>WP</sub>        | 3.7            |     | 4.7            |     | 4.7            |     | ns   |

| t <sub>WDSU</sub>      | 4.6            |     | 5.9            |     | 5.9            |     | ns   |

| t <sub>WDH</sub>       | 0.0            |     | 0.0            |     | 0.0            |     | ns   |

| t <sub>WASU</sub>      | 3.9            |     | 5.0            |     | 5.0            |     | ns   |

| t <sub>WAH</sub>       | 0.0            |     | 0.0            |     | 0.0            |     | ns   |

| t <sub>WO</sub>        |                | 5.6 |                | 7.1 |                | 7.1 | ns   |

| t <sub>DD</sub>        |                | 5.6 |                | 7.1 |                | 7.1 | ns   |

| t <sub>EABOUT</sub>    |                | 2.4 |                | 3.1 |                | 3.1 | ns   |

| t <sub>EABCH</sub>     | 4.0            |     | 4.0            |     | 4.0            |     | ns   |

| t <sub>EABCL</sub>     | 4.0            |     | 4.7            |     | 4.7            |     | ns   |

#### FLEX 10K Embedded Programmable Logic Device Family Data Sheet

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                        | Min            | Max | Min            | Max | Min            | Max | -    |

| t <sub>EABDATA1</sub>  |                | 5.5 |                | 6.5 |                | 8.5 | ns   |

| t <sub>EABDATA2</sub>  |                | 1.1 |                | 1.3 |                | 1.8 | ns   |

| t <sub>EABWE1</sub>    |                | 2.4 |                | 2.8 |                | 3.7 | ns   |

| t <sub>EABWE2</sub>    |                | 2.1 |                | 2.5 |                | 3.2 | ns   |

| t <sub>EABCLK</sub>    |                | 0.0 |                | 0.0 |                | 0.2 | ns   |

| t <sub>EABCO</sub>     |                | 1.7 |                | 2.0 |                | 2.6 | ns   |

| t <sub>EABBYPASS</sub> |                | 0.0 |                | 0.0 |                | 0.3 | ns   |

| t <sub>EABSU</sub>     | 1.2            |     | 1.4            |     | 1.9            |     | ns   |

| t <sub>EABH</sub>      | 0.1            |     | 0.1            |     | 0.3            |     | ns   |

| t <sub>AA</sub>        |                | 4.2 |                | 5.0 |                | 6.5 | ns   |

| t <sub>WP</sub>        | 3.8            |     | 4.5            |     | 5.9            |     | ns   |

| t <sub>WDSU</sub>      | 0.1            |     | 0.1            |     | 0.2            |     | ns   |

| t <sub>WDH</sub>       | 0.1            |     | 0.1            |     | 0.2            |     | ns   |

| t <sub>WASU</sub>      | 0.1            |     | 0.1            |     | 0.2            |     | ns   |

| t <sub>WAH</sub>       | 0.1            |     | 0.1            |     | 0.2            |     | ns   |

| t <sub>WO</sub>        |                | 3.7 |                | 4.4 |                | 6.4 | ns   |

| t <sub>DD</sub>        |                | 3.7 |                | 4.4 |                | 6.4 | ns   |

| t <sub>EABOUT</sub>    |                | 0.0 |                | 0.1 |                | 0.6 | ns   |

| t <sub>EABCH</sub>     | 3.0            |     | 3.5            |     | 4.0            |     | ns   |

| t <sub>EABCL</sub>     | 3.8            |     | 4.5            |     | 5.9            |     | ns   |

| Symbol              | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |      | Unit |

|---------------------|----------------|-----|----------------|-----|----------------|------|------|

|                     | Min            | Max | Min            | Max | Min            | Max  | 1    |

| t <sub>IOD</sub>    |                | 2.5 |                | 2.9 |                | 3.4  | ns   |

| t <sub>IOC</sub>    |                | 0.3 |                | 0.3 |                | 0.4  | ns   |

| t <sub>IOCO</sub>   |                | 0.2 |                | 0.2 |                | 0.3  | ns   |

| t <sub>IOCOMB</sub> |                | 0.5 |                | 0.6 |                | 0.7  | ns   |

| t <sub>IOSU</sub>   | 1.3            |     | 1.7            |     | 1.8            |      | ns   |

| t <sub>IOH</sub>    | 0.2            |     | 0.2            |     | 0.3            |      | ns   |

| t <sub>IOCLR</sub>  |                | 1.0 |                | 1.2 |                | 1.4  | ns   |

| t <sub>OD1</sub>    |                | 2.2 |                | 2.6 |                | 3.0  | ns   |

| t <sub>OD2</sub>    |                | 4.5 |                | 5.3 |                | 6.1  | ns   |

| t <sub>OD3</sub>    |                | 6.8 |                | 7.9 |                | 9.3  | ns   |

| t <sub>XZ</sub>     |                | 2.7 |                | 3.1 |                | 3.7  | ns   |

| t <sub>ZX1</sub>    |                | 2.7 |                | 3.1 |                | 3.7  | ns   |

| t <sub>ZX2</sub>    |                | 5.0 |                | 5.8 |                | 6.8  | ns   |

| t <sub>ZX3</sub>    |                | 7.3 |                | 8.4 |                | 10.0 | ns   |

| t <sub>INREG</sub>  |                | 5.3 |                | 6.1 |                | 7.2  | ns   |

| t <sub>IOFD</sub>   |                | 4.7 |                | 5.5 |                | 6.4  | ns   |

| t <sub>INCOMB</sub> |                | 4.7 |                | 5.5 |                | 6.4  | ns   |

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                        | Min            | Max | Min            | Max | Min            | Max | 1    |

| t <sub>EABDATA1</sub>  |                | 1.8 |                | 2.1 |                | 2.4 | ns   |

| t <sub>EABDATA2</sub>  |                | 3.2 |                | 3.7 |                | 4.4 | ns   |

| t <sub>EABWE1</sub>    |                | 0.8 |                | 0.9 |                | 1.1 | ns   |

| t <sub>EABWE2</sub>    |                | 2.3 |                | 2.7 |                | 3.1 | ns   |

| t <sub>EABCLK</sub>    |                | 0.8 |                | 0.9 |                | 1.1 | ns   |

| t <sub>EABCO</sub>     |                | 1.0 |                | 1.1 |                | 1.4 | ns   |

| t <sub>EABBYPASS</sub> |                | 0.3 |                | 0.3 |                | 0.4 | ns   |

| t <sub>EABSU</sub>     | 1.3            |     | 1.5            |     | 1.8            |     | ns   |

| t <sub>EABH</sub>      | 0.4            |     | 0.5            |     | 0.5            |     | ns   |

| t <sub>AA</sub>        |                | 4.1 |                | 4.8 |                | 5.6 | ns   |

| t <sub>WP</sub>        | 3.2            |     | 3.7            |     | 4.4            |     | ns   |

| t <sub>WDSU</sub>      | 2.4            |     | 2.8            |     | 3.3            |     | ns   |

| t <sub>WDH</sub>       | 0.2            |     | 0.2            |     | 0.3            |     | ns   |

| t <sub>WASU</sub>      | 0.2            |     | 0.2            |     | 0.3            |     | ns   |

| t <sub>WAH</sub>       | 0.0            |     | 0.0            |     | 0.0            |     | ns   |

| t <sub>WO</sub>        |                | 3.4 |                | 3.9 |                | 4.6 | ns   |

| t <sub>DD</sub>        |                | 3.4 |                | 3.9 |                | 4.6 | ns   |

| t<br>EABOUT            |                | 0.3 |                | 0.3 |                | 0.4 | ns   |

| t <sub>EABCH</sub>     | 2.5            |     | 3.5            |     | 4.0            |     | ns   |

| t <sub>EABCL</sub>     | 3.2            |     | 3.7            |     | 4.4            |     | ns   |

#### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

### Tables 106 through 112 show EPF10K250A device internal and external timing parameters.

| Table 106. EPF10K250A Device LE Timing Microparameters Note (1) |                |     |                |     |                |     |      |

|-----------------------------------------------------------------|----------------|-----|----------------|-----|----------------|-----|------|

| Symbol                                                          | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|                                                                 | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>LUT</sub>                                                |                | 0.9 |                | 1.0 |                | 1.4 | ns   |

| t <sub>CLUT</sub>                                               |                | 1.2 |                | 1.3 |                | 1.6 | ns   |

| t <sub>RLUT</sub>                                               |                | 2.0 |                | 2.3 |                | 2.7 | ns   |

| t <sub>PACKED</sub>                                             |                | 0.4 |                | 0.4 |                | 0.5 | ns   |

| t <sub>EN</sub>                                                 |                | 1.4 |                | 1.6 |                | 1.9 | ns   |

| t <sub>CICO</sub>                                               |                | 0.2 |                | 0.3 |                | 0.3 | ns   |

| t <sub>CGEN</sub>                                               |                | 0.4 |                | 0.6 |                | 0.6 | ns   |

| t <sub>CGENR</sub>                                              |                | 0.8 |                | 1.0 |                | 1.1 | ns   |

| t <sub>CASC</sub>                                               |                | 0.7 |                | 0.8 |                | 1.0 | ns   |

| t <sub>C</sub>                                                  |                | 1.2 |                | 1.3 |                | 1.6 | ns   |

| t <sub>CO</sub>                                                 |                | 0.6 |                | 0.7 |                | 0.9 | ns   |

| t <sub>COMB</sub>                                               |                | 0.5 |                | 0.6 |                | 0.7 | ns   |

| t <sub>SU</sub>                                                 | 1.2            |     | 1.4            |     | 1.7            |     | ns   |

| t <sub>H</sub>                                                  | 1.2            |     | 1.3            |     | 1.6            |     | ns   |

| t <sub>PRE</sub>                                                |                | 0.7 |                | 0.8 |                | 0.9 | ns   |

| t <sub>CLR</sub>                                                |                | 0.7 |                | 0.8 |                | 0.9 | ns   |

| t <sub>CH</sub>                                                 | 2.5            |     | 3.0            |     | 3.5            |     | ns   |

| t <sub>CL</sub>                                                 | 2.5            |     | 3.0            |     | 3.5            |     | ns   |