Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 144                                                        |

| Number of Logic Elements/Cells | 1152                                                       |

| Total RAM Bits                 | 12288                                                      |

| Number of I/O                  | 147                                                        |

| Number of Gates                | 63000                                                      |

| Voltage - Supply               | 4.75V ~ 5.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 70°C (TA)                                            |

| Package / Case                 | 208-BFQFP Exposed Pad                                      |

| Supplier Device Package        | 208-RQFP (28x28)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k20rc208-4 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Notes to tables:

- (1) FLEX 10K and FLEX 10KA device package types include plastic J-lead chip carrier (PLCC), thin quad flat pack (TQFP), plastic quad flat pack (PQFP), power quad flat pack (RQFP), ball-grid array (BGA), pin-grid array (PGA), and FineLine BGA™ packages.

- (2) This option is supported with a 256-pin FineLine BGA package. By using SameFrame pin migration, all FineLine BGA packages are pin compatible. For example, a board can be designed to support both 256-pin and 484-pin FineLine BGA packages. The Altera software automatically avoids conflicting pins when future migration is set.

# General Description

Altera's FLEX 10K devices are the industry's first embedded PLDs. Based on reconfigurable CMOS SRAM elements, the Flexible Logic Element MatriX (FLEX) architecture incorporates all features necessary to implement common gate array megafunctions. With up to 250,000 gates, the FLEX 10K family provides the density, speed, and features to integrate entire systems, including multiple 32-bit buses, into a single device.

FLEX 10K devices are reconfigurable, which allows 100% testing prior to shipment. As a result, the designer is not required to generate test vectors for fault coverage purposes. Additionally, the designer does not need to manage inventories of different ASIC designs; FLEX 10K devices can be configured on the board for the specific functionality required.

Table 6 shows FLEX 10K performance for some common designs. All performance values were obtained with Synopsys DesignWare or LPM functions. No special design technique was required to implement the applications; the designer simply inferred or instantiated a function in a Verilog HDL, VHDL, Altera Hardware Description Language (AHDL), or schematic design file.

| Application                       |     | urces<br>sed |                   | Perfor            | mance             |                   | Units |

|-----------------------------------|-----|--------------|-------------------|-------------------|-------------------|-------------------|-------|

|                                   | LEs | EABs         | -1 Speed<br>Grade | -2 Speed<br>Grade | -3 Speed<br>Grade | -4 Speed<br>Grade |       |

| 16-bit loadable counter (1)       | 16  | 0            | 204               | 166               | 125               | 95                | MHz   |

| 16-bit accumulator (1)            | 16  | 0            | 204               | 166               | 125               | 95                | MHz   |

| 16-to-1 multiplexer (2)           | 10  | 0            | 4.2               | 5.8               | 6.0               | 7.0               | ns    |

| 256 × 8 RAM read cycle speed (3)  | 0   | 1            | 172               | 145               | 108               | 84                | MHz   |

| 256 × 8 RAM write cycle speed (3) | 0   | 1            | 106               | 89                | 68                | 63                | MHz   |

### Notes:

- (1) The speed grade of this application is limited because of clock high and low specifications.

- (2) This application uses combinatorial inputs and outputs.

- (3) This application uses registered inputs and outputs.

Embedded Array Block (EAB) I/O Element IOE (10E) Column Logic Array Interconnect EAB Logic Array Block (LAB) Logic Element (LE) Row EAB Interconnect Local Interconnect Logic Array IOE IOE IOE IOE IOE IOE IOE Embedded Array

Figure 1. FLEX 10K Device Block Diagram

FLEX 10K devices provide six dedicated inputs that drive the flipflops' control inputs to ensure the efficient distribution of high-speed, low-skew (less than 1.5 ns) control signals. These signals use dedicated routing channels that provide shorter delays and lower skews than the FastTrack Interconnect. Four of the dedicated inputs drive four global signals. These four global signals can also be driven by internal logic, providing an ideal solution for a clock divider or an internally generated asynchronous clear signal that clears many registers in the device.

## **Embedded Array Block**

The EAB is a flexible block of RAM with registers on the input and output ports, and is used to implement common gate array megafunctions. The EAB is also suitable for functions such as multipliers, vector scalars, and error correction circuits, because it is large and flexible. These functions can be combined in applications such as digital filters and microcontrollers.

Dedicated Inputs & Global Signals Chip-Wide Reset Row Interconnect 2, 4, 8, 16 Data Data Out 8, 4, 2, 1 2, 4, 8, 16 Address D 8, 9, 10, 11 RAM/ROM  $256 \times 8$ 512 × 4  $1,024 \times 2$ Column 2,048 × 1 Interconnect WE D

Figure 4. FLEX 10K Embedded Array Block

### Note:

EAB Local Interconnect (1)

(1) EPF10K10, EPF10K10A, EPF10K20, EPF10K30, EPF10K30A, EPF10K40, EPF10K50, and EPF10K50V devices have 22 EAB local interconnect channels; EPF10K70, EPF10K100, EPF10K100A, EPF10K130V, and EPF10K250A devices have 26.

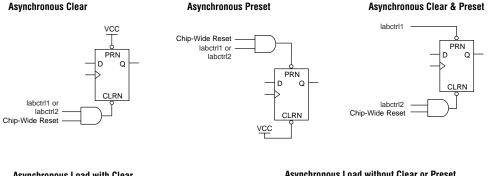

Figure 10. LE Clear & Preset Modes

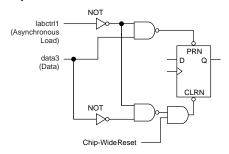

### **Asynchronous Load with Clear**

### labctrl1 (Asynchronous Load) PRN data3 (Data) NOT CLRN labctrl2 (Clear) Chip-Wide Reset

### **Asynchronous Load without Clear or Preset**

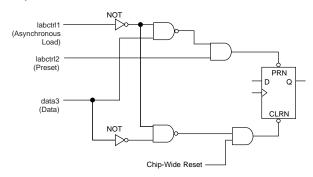

### **Asynchronous Load with Preset**

### Asynchronous Clear

The flipflop can be cleared by either LABCTRL1 or LABCTRL2. In this mode, the preset signal is tied to V<sub>CC</sub> to deactivate it.

For improved routing, the row interconnect is comprised of a combination of full-length and half-length channels. The full-length channels connect to all LABs in a row; the half-length channels connect to the LABs in half of the row. The EAB can be driven by the half-length channels in the left half of the row and by the full-length channels. The EAB drives out to the full-length channels. In addition to providing a predictable, row-wide interconnect, this architecture provides increased routing resources. Two neighboring LABs can be connected using a half-row channel, thereby saving the other half of the channel for the other half of the row.

Table 7 summarizes the FastTrack Interconnect resources available in each FLEX  $10 \mathrm{K}$  device.

| Table 7. FLEX 1         | Table 7. FLEX 10K FastTrack Interconnect Resources |                     |         |                        |  |  |  |  |

|-------------------------|----------------------------------------------------|---------------------|---------|------------------------|--|--|--|--|

| Device                  | Rows                                               | Channels per<br>Row | Columns | Channels per<br>Column |  |  |  |  |

| EPF10K10<br>EPF10K10A   | 3                                                  | 144                 | 24      | 24                     |  |  |  |  |

| EPF10K20                | 6                                                  | 144                 | 24      | 24                     |  |  |  |  |

| EPF10K30<br>EPF10K30A   | 6                                                  | 216                 | 36      | 24                     |  |  |  |  |

| EPF10K40                | 8                                                  | 216                 | 36      | 24                     |  |  |  |  |

| EPF10K50<br>EPF10K50V   | 10                                                 | 216                 | 36      | 24                     |  |  |  |  |

| EPF10K70                | 9                                                  | 312                 | 52      | 24                     |  |  |  |  |

| EPF10K100<br>EPF10K100A | 12                                                 | 312                 | 52      | 24                     |  |  |  |  |

| EPF10K130V              | 16                                                 | 312                 | 52      | 32                     |  |  |  |  |

| EPF10K250A              | 20                                                 | 456                 | 76      | 40                     |  |  |  |  |

In addition to general-purpose I/O pins, FLEX 10K devices have six dedicated input pins that provide low-skew signal distribution across the device. These six inputs can be used for global clock, clear, preset, and peripheral output enable and clock enable control signals. These signals are available as control signals for all LABs and IOEs in the device.

The dedicated inputs can also be used as general-purpose data inputs because they can feed the local interconnect of each LAB in the device. However, the use of dedicated inputs as data inputs can introduce additional delay into the control signal network.

### I/O Element

An I/O element (IOE) contains a bidirectional I/O buffer and a register that can be used either as an input register for external data that requires a fast setup time, or as an output register for data that requires fast clock-to-output performance. In some cases, using an LE register for an input register will result in a faster setup time than using an IOE register. IOEs can be used as input, output, or bidirectional pins. For bidirectional registered I/O implementation, the output register should be in the IOE and, the data input and output enable register should be LE registers placed adjacent to the bidirectional pin. The Compiler uses the programmable inversion option to invert signals from the row and column interconnect automatically where appropriate. Figure 13 shows the bidirectional I/O registers.

# ClockLock & ClockBoost Features

To support high-speed designs, selected FLEX 10K devices offer optional ClockLock and ClockBoost circuitry containing a phase-locked loop (PLL) that is used to increase design speed and reduce resource usage. The ClockLock circuitry uses a synchronizing PLL that reduces the clock delay and skew within a device. This reduction minimizes clock-to-output and setup times while maintaining zero hold times. The ClockBoost circuitry, which provides a clock multiplier, allows the designer to enhance device area efficiency by sharing resources within the device. The ClockBoost feature allows the designer to distribute a low-speed clock and multiply that clock on-device. Combined, the ClockLock and ClockBoost features provide significant improvements in system performance and bandwidth.

The ClockLock and ClockBoost features in FLEX 10K devices are enabled through the Altera software. External devices are not required to use these features. The output of the ClockLock and ClockBoost circuits is not available at any of the device pins.

The ClockLock and ClockBoost circuitry locks onto the rising edge of the incoming clock. The circuit output can only drive the clock inputs of registers; the generated clock cannot be gated or inverted.

The dedicated clock pin (GCLK1) supplies the clock to the ClockLock and ClockBoost circuitry. When the dedicated clock pin is driving the ClockLock or ClockBoost circuitry, it cannot drive elsewhere in the device.

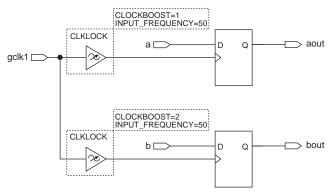

In designs that require both a multiplied and non-multiplied clock, the clock trace on the board can be connected to GCLK1. With the Altera software, GCLK1 can feed both the ClockLock and ClockBoost circuitry in the FLEX 10K device. However, when both circuits are used, the other clock pin (GCLK0) cannot be used. Figure 17 shows a block diagram of how to enable both the ClockLock and ClockBoost circuits in the Altera software. The example shown is a schematic, but a similar approach applies for designs created in AHDL, VHDL, and Verilog HDL. When the ClockLock and ClockBoost circuits are used simultaneously, the input frequency parameter must be the same for both circuits. In Figure 17, the input frequency must meet the requirements specified when the ClockBoost multiplication factor is two.

Figure 17. Enabling ClockLock & ClockBoost in the Same Design

To use both the ClockLock and ClockBoost circuits in the same design, designers must use Revision C EPF10K100GC503-3DX devices and MAX+PLUS II software versions 7.2 or higher. The die revision is indicated by the third digit of the nine-digit code on the top side of the device.

# Output Configuration

This section discusses the peripheral component interconnect (PCI) pull-up clamping diode option, slew-rate control, open-drain output option, MultiVolt I/O interface, and power sequencing for FLEX 10K devices. The PCI pull-up clamping diode, slew-rate control, and open-drain output options are controlled pin-by-pin via Altera logic options. The MultiVolt I/O interface is controlled by connecting  $V_{CCIO}$  to a different voltage than  $V_{CCINT}.$  Its effect can be simulated in the Altera software via the **Global Project Device Options** dialog box (Assign menu).

### **PCI Clamping Diodes**

The EPF10K10A and EPF10K30A devices have a pull-up clamping diode on every I/O, dedicated input, and dedicated clock pin. PCI clamping diodes clamp the transient overshoot caused by reflected waves to the  $V_{\rm CCIO}$  value and are required for 3.3-V PCI compliance. Clamping diodes can also be used to limit overshoot in other systems.

Clamping diodes are controlled on a pin-by-pin basis via a logic option in the Altera software. When  $V_{\rm CCIO}$  is 3.3 V, a pin that has the clamping diode turned on can be driven by a 2.5-V or 3.3-V signal, but not a 5.0-V signal. When  $V_{\rm CCIO}$  is 2.5 V, a pin that has the clamping diode turned on can be driven by a 2.5-V signal, but not a 3.3-V or 5.0-V signal. However, a clamping diode can be turned on for a subset of pins, which allows devices to bridge between a 3.3-V PCI bus and a 5.0-V device.

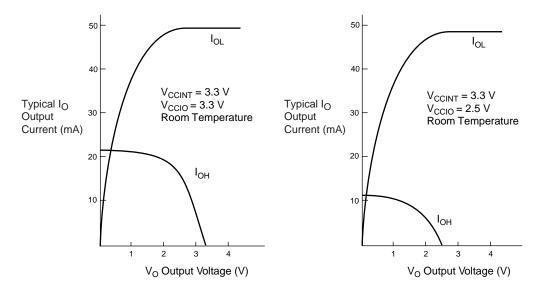

Figure 23. Output Drive Characteristics for EPF10K250A Device

# **Timing Model**

The continuous, high-performance FastTrack Interconnect routing resources ensure predictable performance and accurate simulation and timing analysis. This predictable performance contrasts with that of FPGAs, which use a segmented connection scheme and therefore have unpredictable performance.

Device performance can be estimated by following the signal path from a source, through the interconnect, to the destination. For example, the registered performance between two LEs on the same row can be calculated by adding the following parameters:

- LE register clock-to-output delay ( $t_{CO}$ )

- Interconnect delay ( $t_{SAMEROW}$ )

- LE look-up table delay ( $t_{LIIT}$ )

- LE register setup time ( $t_{SU}$ )

The routing delay depends on the placement of the source and destination LEs. A more complex registered path may involve multiple combinatorial LEs between the source and destination LEs.

| Table 32. LE Timing Microparameters (Part 2 of 2) Note (1) |                                                                                                                                      |            |  |  |  |  |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|--|

| Symbol                                                     | Parameter                                                                                                                            | Conditions |  |  |  |  |

| t <sub>SU</sub>                                            | LE register setup time for data and enable signals before clock; LE register recovery time after asynchronous clear, preset, or load |            |  |  |  |  |

| t <sub>H</sub>                                             | LE register hold time for data and enable signals after clock                                                                        |            |  |  |  |  |

| t <sub>PRE</sub>                                           | LE register preset delay                                                                                                             |            |  |  |  |  |

| t <sub>CLR</sub>                                           | LE register clear delay                                                                                                              |            |  |  |  |  |

| t <sub>CH</sub>                                            | Minimum clock high time from clock pin                                                                                               |            |  |  |  |  |

| $t_{CL}$                                                   | Minimum clock low time from clock pin                                                                                                |            |  |  |  |  |

| Table 33. IOE       | E Timing Microparameters Note (1)                                                                                     |                |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|----------------|

| Symbol              | Parameter                                                                                                             | Conditions     |

| $t_{IOD}$           | IOE data delay                                                                                                        |                |

| t <sub>IOC</sub>    | IOE register control signal delay                                                                                     |                |

| t <sub>IOCO</sub>   | IOE register clock-to-output delay                                                                                    |                |

| t <sub>IOCOMB</sub> | IOE combinatorial delay                                                                                               |                |

| t <sub>IOSU</sub>   | IOE register setup time for data and enable signals before clock; IOE register recovery time after asynchronous clear |                |

| t <sub>IOH</sub>    | IOE register hold time for data and enable signals after clock                                                        |                |

| t <sub>IOCLR</sub>  | IOE register clear time                                                                                               |                |

| t <sub>OD1</sub>    | Output buffer and pad delay, slow slew rate = off, $V_{CCIO} = V_{CCINT}$                                             | C1 = 35 pF (2) |

| $t_{OD2}$           | Output buffer and pad delay, slow slew rate = off, $V_{CCIO}$ = low voltage                                           | C1 = 35 pF (3) |

| t <sub>OD3</sub>    | Output buffer and pad delay, slow slew rate = on                                                                      | C1 = 35 pF (4) |

| $t_{XZ}$            | IOE output buffer disable delay                                                                                       |                |

| $t_{ZX1}$           | IOE output buffer enable delay, slow slew rate = off, $V_{CCIO} = V_{CCINT}$                                          | C1 = 35 pF (2) |

| $t_{ZX2}$           | IOE output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = low voltage                                 | C1 = 35 pF (3) |

| $t_{ZX3}$           | IOE output buffer enable delay, slow slew rate = on                                                                   | C1 = 35 pF (4) |

| t <sub>INREG</sub>  | IOE input pad and buffer to IOE register delay                                                                        |                |

| $t_{IOFD}$          | IOE register feedback delay                                                                                           |                |

| t <sub>INCOMB</sub> | IOE input pad and buffer to FastTrack Interconnect delay                                                              |                |

| Symbol                   | Parameter                                                                                                            | Conditions |

|--------------------------|----------------------------------------------------------------------------------------------------------------------|------------|

| t <sub>DIN2IOE</sub>     | Delay from dedicated input pin to IOE control input                                                                  | (7)        |

| t <sub>DCLK2LE</sub>     | Delay from dedicated clock pin to LE or EAB clock                                                                    | (7)        |

| t <sub>DIN2DATA</sub>    | Delay from dedicated input or clock to LE or EAB data                                                                | (7)        |

| t <sub>DCLK2IOE</sub>    | Delay from dedicated clock pin to IOE clock                                                                          | (7)        |

| t <sub>DIN2LE</sub>      | Delay from dedicated input pin to LE or EAB control input                                                            | (7)        |

| t <sub>SAMELAB</sub>     | Routing delay for an LE driving another LE in the same LAB                                                           |            |

| t <sub>SAMEROW</sub>     | Routing delay for a row IOE, LE, or EAB driving a row IOE, LE, or EAB in the same row                                | (7)        |

| t <sub>SAME</sub> COLUMN | Routing delay for an LE driving an IOE in the same column                                                            | (7)        |

| t <sub>DIFFROW</sub>     | Routing delay for a column IOE, LE, or EAB driving an LE or EAB in a different row                                   | (7)        |

| t <sub>TWOROWS</sub>     | Routing delay for a row IOE or EAB driving an LE or EAB in a different row                                           | (7)        |

| t <sub>LEPERIPH</sub>    | Routing delay for an LE driving a control signal of an IOE via the peripheral control bus                            | (7)        |

| t <sub>LABCARRY</sub>    | Routing delay for the carry-out signal of an LE driving the carry-in signal of a different LE in a different LAB     |            |

| t <sub>LABCASC</sub>     | Routing delay for the cascade-out signal of an LE driving the cascade-in signal of a different LE in a different LAB |            |

| Table 37. External Timing Parameters Notes (8), (10) |                                                                                                |            |  |  |  |  |

|------------------------------------------------------|------------------------------------------------------------------------------------------------|------------|--|--|--|--|

| Symbol                                               | Parameter                                                                                      | Conditions |  |  |  |  |

| t <sub>DRR</sub>                                     | Register-to-register delay via four LEs, three row interconnects, and four local interconnects | (9)        |  |  |  |  |

| t <sub>INSU</sub>                                    | Setup time with global clock at IOE register                                                   |            |  |  |  |  |

| t <sub>INH</sub>                                     | Hold time with global clock at IOE register                                                    |            |  |  |  |  |

| t <sub>OUTCO</sub>                                   | Clock-to-output delay with global clock at IOE register                                        |            |  |  |  |  |

| Table 38. External Bidirectional Timing Parameters     Note (10) |                                                                                |           |  |  |  |  |

|------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------|--|--|--|--|

| Symbol                                                           | Parameter                                                                      | Condition |  |  |  |  |

| t <sub>INSUBIDIR</sub>                                           | Setup time for bidirectional pins with global clock at adjacent LE register    |           |  |  |  |  |

| t <sub>INHBIDIR</sub>                                            | Hold time for bidirectional pins with global clock at adjacent LE register     |           |  |  |  |  |

| t <sub>OUTCOBIDIR</sub>                                          | Clock-to-output delay for bidirectional pins with global clock at IOE register |           |  |  |  |  |

| t <sub>XZBIDIR</sub>                                             | Synchronous IOE output buffer disable delay                                    |           |  |  |  |  |

| t <sub>ZXBIDIR</sub>                                             | Synchronous IOE output buffer enable delay, slow slew rate = off               |           |  |  |  |  |

| Symbol              | -3 Spee | d Grade | -4 Spee | Unit |    |

|---------------------|---------|---------|---------|------|----|

|                     | Min     | Max     | Min     | Max  |    |

| $t_{IOD}$           |         | 0.4     |         | 0.6  | ns |

| t <sub>IOC</sub>    |         | 0.5     |         | 0.9  | ns |

| t <sub>IOCO</sub>   |         | 0.4     |         | 0.5  | ns |

| $t_{IOCOMB}$        |         | 0.0     |         | 0.0  | ns |

| t <sub>IOSU</sub>   | 3.1     |         | 3.5     |      | ns |

| t <sub>IOH</sub>    | 1.0     |         | 1.9     |      | ns |

| t <sub>IOCLR</sub>  |         | 1.0     |         | 1.2  | ns |

| t <sub>OD1</sub>    |         | 3.3     |         | 3.6  | ns |

| $t_{OD2}$           |         | 5.6     |         | 6.5  | ns |

| $t_{OD3}$           |         | 7.0     |         | 8.3  | ns |

| $t_{XZ}$            |         | 5.2     |         | 5.5  | ns |

| t <sub>ZX1</sub>    |         | 5.2     |         | 5.5  | ns |

| t <sub>ZX2</sub>    |         | 7.5     |         | 8.4  | ns |

| t <sub>ZX3</sub>    |         | 8.9     |         | 10.2 | ns |

| t <sub>INREG</sub>  |         | 7.7     |         | 10.0 | ns |

| t <sub>IOFD</sub>   |         | 3.3     |         | 4.0  | ns |

| t <sub>INCOMB</sub> |         | 3.3     |         | 4.0  | ns |

| Symbol                 | -3 Spee | d Grade | -4 Spee | d Grade | Unit |

|------------------------|---------|---------|---------|---------|------|

|                        | Min     | Max     | Min     | Max     |      |

| t <sub>EABDATA1</sub>  |         | 1.5     |         | 1.9     | ns   |

| t <sub>EABDATA2</sub>  |         | 4.8     |         | 6.0     | ns   |

| t <sub>EABWE1</sub>    |         | 1.0     |         | 1.2     | ns   |

| t <sub>EABWE2</sub>    |         | 5.0     |         | 6.2     | ns   |

| t <sub>EABCLK</sub>    |         | 1.0     |         | 2.2     | ns   |

| t <sub>EABCO</sub>     |         | 0.5     |         | 0.6     | ns   |

| t <sub>EABBYPASS</sub> |         | 1.5     |         | 1.9     | ns   |

| t <sub>EABSU</sub>     | 1.5     |         | 1.8     |         | ns   |

| t <sub>EABH</sub>      | 2.0     |         | 2.5     |         | ns   |

| $t_{AA}$               |         | 8.7     |         | 10.7    | ns   |

| $t_{WP}$               | 5.8     |         | 7.2     |         | ns   |

| t <sub>WDSU</sub>      | 1.6     |         | 2.0     |         | ns   |

| t <sub>WDH</sub>       | 0.3     |         | 0.4     |         | ns   |

| t <sub>WASU</sub>      | 0.5     |         | 0.6     |         | ns   |

| t <sub>WAH</sub>       | 1.0     |         | 1.2     |         | ns   |

| $t_{WO}$               |         | 5.0     |         | 6.2     | ns   |

| t <sub>DD</sub>        |         | 5.0     |         | 6.2     | ns   |

| t <sub>EABOUT</sub>    |         | 0.5     |         | 0.6     | ns   |

| t <sub>EABCH</sub>     | 4.0     |         | 4.0     |         | ns   |

| t <sub>EABCL</sub>     | 5.8     |         | 7.2     |         | ns   |

| Symbol                 | -3 Snee | d Grade | -4 Spee | Unit |       |

|------------------------|---------|---------|---------|------|-------|

| Symbol                 | -       |         |         |      | Oiiit |

|                        | Min     | Max     | Min     | Max  |       |

| t <sub>EABAA</sub>     |         | 13.7    |         | 17.0 | ns    |

| t <sub>EABRCCOMB</sub> | 13.7    |         | 17.0    |      | ns    |

| t <sub>EABRCREG</sub>  | 9.7     |         | 11.9    |      | ns    |

| t <sub>EABWP</sub>     | 5.8     |         | 7.2     |      | ns    |

| t <sub>EABWCCOMB</sub> | 7.3     |         | 9.0     |      | ns    |

| t <sub>EABWCREG</sub>  | 13.0    |         | 16.0    |      | ns    |

| t <sub>EABDD</sub>     |         | 10.0    |         | 12.5 | ns    |

| t <sub>EABDATACO</sub> |         | 2.0     |         | 3.4  | ns    |

| t <sub>EABDATASU</sub> | 5.3     |         | 5.6     |      | ns    |

| t <sub>EABDATAH</sub>  | 0.0     |         | 0.0     |      | ns    |

| t <sub>EABWESU</sub>   | 5.5     |         | 5.8     |      | ns    |

| t <sub>EABWEH</sub>    | 0.0     |         | 0.0     |      | ns    |

| t <sub>EABWDSU</sub>   | 5.5     |         | 5.8     |      | ns    |

| t <sub>EABWDH</sub>    | 0.0     |         | 0.0     |      | ns    |

| t <sub>EABWASU</sub>   | 2.1     |         | 2.7     |      | ns    |

| t <sub>EABWAH</sub>    | 0.0     |         | 0.0     |      | ns    |

| $t_{EABWO}$            |         | 9.5     |         | 11.8 | ns    |

| Table 72. EPI       | F10K50V D | evice IOE T    | iming Mic | roparamet | ers No         | ote (1) |         |               |    |

|---------------------|-----------|----------------|-----------|-----------|----------------|---------|---------|---------------|----|

| Symbol              | -1 Spec   | -1 Speed Grade |           | d Grade   | -3 Speed Grade |         | -4 Spee | Speed Grade I |    |

|                     | Min       | Max            | Min       | Max       | Min            | Max     | Min     | Max           |    |

| $t_{IOD}$           |           | 1.2            |           | 1.6       |                | 1.9     |         | 2.1           | ns |

| $t_{IOC}$           |           | 0.3            |           | 0.4       |                | 0.5     |         | 0.5           | ns |

| t <sub>IOCO</sub>   |           | 0.3            |           | 0.3       |                | 0.4     |         | 0.4           | ns |

| t <sub>IOCOMB</sub> |           | 0.0            |           | 0.0       |                | 0.0     |         | 0.0           | ns |

| $t_{IOSU}$          | 2.8       |                | 2.8       |           | 3.4            |         | 3.9     |               | ns |

| t <sub>IOH</sub>    | 0.7       |                | 0.8       |           | 1.0            |         | 1.4     |               | ns |

| t <sub>IOCLR</sub>  |           | 0.5            |           | 0.6       |                | 0.7     |         | 0.7           | ns |

| t <sub>OD1</sub>    |           | 2.8            |           | 3.2       |                | 3.9     |         | 4.7           | ns |

| t <sub>OD2</sub>    |           | _              |           | _         |                | _       |         | _             | ns |

| t <sub>OD3</sub>    |           | 6.5            |           | 6.9       |                | 7.6     |         | 8.4           | ns |

| $t_{XZ}$            |           | 2.8            |           | 3.1       |                | 3.8     |         | 4.6           | ns |

| $t_{ZX1}$           |           | 2.8            |           | 3.1       |                | 3.8     |         | 4.6           | ns |

| $t_{ZX2}$           |           | _              |           | _         |                | _       |         | _             | ns |

| $t_{ZX3}$           |           | 6.5            |           | 6.8       |                | 7.5     |         | 8.3           | ns |

| t <sub>INREG</sub>  |           | 5.0            |           | 5.7       |                | 7.0     |         | 9.0           | ns |

| t <sub>IOFD</sub>   |           | 1.5            |           | 1.9       |                | 2.3     |         | 2.7           | ns |

| t <sub>INCOMB</sub> |           | 1.5            |           | 1.9       |                | 2.3     |         | 2.7           | ns |

| Symbol                 | -2 Speed Grade |     | -3 Speed Grade |     | -4 Speed Grade |     | Unit |

|------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                        | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>EABDATA1</sub>  |                | 1.9 |                | 2.4 |                | 2.4 | ns   |

| t <sub>EABDATA2</sub>  |                | 3.7 |                | 4.7 |                | 4.7 | ns   |

| t <sub>EABWE1</sub>    |                | 1.9 |                | 2.4 |                | 2.4 | ns   |

| t <sub>EABWE2</sub>    |                | 3.7 |                | 4.7 |                | 4.7 | ns   |

| t <sub>EABCLK</sub>    |                | 0.7 |                | 0.9 |                | 0.9 | ns   |

| t <sub>EABCO</sub>     |                | 0.5 |                | 0.6 |                | 0.6 | ns   |

| t <sub>EABBYPASS</sub> |                | 0.6 |                | 0.8 |                | 0.8 | ns   |

| t <sub>EABSU</sub>     | 1.4            |     | 1.8            |     | 1.8            |     | ns   |

| t <sub>EABH</sub>      | 0.0            |     | 0.0            |     | 0.0            |     | ns   |

| $t_{AA}$               |                | 5.6 |                | 7.1 |                | 7.1 | ns   |

| $t_{WP}$               | 3.7            |     | 4.7            |     | 4.7            |     | ns   |

| $t_{WDSU}$             | 4.6            |     | 5.9            |     | 5.9            |     | ns   |

| t <sub>WDH</sub>       | 0.0            |     | 0.0            |     | 0.0            |     | ns   |

| t <sub>WASU</sub>      | 3.9            |     | 5.0            |     | 5.0            |     | ns   |

| t <sub>WAH</sub>       | 0.0            |     | 0.0            |     | 0.0            |     | ns   |

| $t_{WO}$               |                | 5.6 |                | 7.1 |                | 7.1 | ns   |

| $t_{DD}$               |                | 5.6 |                | 7.1 |                | 7.1 | ns   |

| t <sub>EABOUT</sub>    |                | 2.4 |                | 3.1 |                | 3.1 | ns   |

| t <sub>EABCH</sub>     | 4.0            |     | 4.0            |     | 4.0            |     | ns   |

| t <sub>EABCL</sub>     | 4.0            |     | 4.7            |     | 4.7            |     | ns   |

| Symbol                   | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | Unit |    |

|--------------------------|----------------|-----|---------|---------|---------|------|----|

|                          | Min            | Max | Min     | Max     | Min     | Max  |    |

| t <sub>DIN2IOE</sub>     |                | 4.8 |         | 5.4     |         | 6.0  | ns |

| t <sub>DIN2LE</sub>      |                | 2.0 |         | 2.4     |         | 2.7  | ns |

| t <sub>DIN2DATA</sub>    |                | 2.4 |         | 2.7     |         | 2.9  | ns |

| t <sub>DCLK2IOE</sub>    |                | 2.6 |         | 3.0     |         | 3.5  | ns |

| t <sub>DCLK2LE</sub>     |                | 2.0 |         | 2.4     |         | 2.7  | ns |

| t <sub>SAMELAB</sub>     |                | 0.1 |         | 0.1     |         | 0.1  | ns |

| t <sub>SAMEROW</sub>     |                | 1.5 |         | 1.7     |         | 1.9  | ns |

| t <sub>SAME</sub> COLUMN |                | 5.5 |         | 6.5     |         | 7.4  | ns |

| t <sub>DIFFROW</sub>     |                | 7.0 |         | 8.2     |         | 9.3  | ns |

| t <sub>TWOROWS</sub>     |                | 8.5 |         | 9.9     |         | 11.2 | ns |

| t <sub>LEPERIPH</sub>    |                | 3.9 |         | 4.2     |         | 4.5  | ns |

| t <sub>LABCARRY</sub>    |                | 0.2 |         | 0.2     |         | 0.3  | ns |

| t <sub>LABCASC</sub>     |                | 0.4 |         | 0.5     |         | 0.6  | ns |

| Table 104. EPF10K100A Device External Timing Parameters Note (1) |                   |      |         |          |         |      |    |  |

|------------------------------------------------------------------|-------------------|------|---------|----------|---------|------|----|--|

| Symbol                                                           | ol -1 Speed Grade |      | -2 Spec | ed Grade | -3 Spee | Unit |    |  |

|                                                                  | Min               | Max  | Min     | Max      | Min     | Max  |    |  |

| t <sub>DRR</sub>                                                 |                   | 12.5 |         | 14.5     |         | 17.0 | ns |  |

| t <sub>INSU</sub> (2), (3)                                       | 3.7               |      | 4.5     |          | 5.1     |      | ns |  |

| t <sub>INH</sub> (3)                                             | 0.0               |      | 0.0     |          | 0.0     |      | ns |  |

| t <sub>оитсо</sub> (3)                                           | 2.0               | 5.3  | 2.0     | 6.1      | 2.0     | 7.2  | ns |  |

| Table 105. EPF10K100A Device External Bidirectional Timing Parameters       Note (1) |         |                               |     |         |      |      |    |  |

|--------------------------------------------------------------------------------------|---------|-------------------------------|-----|---------|------|------|----|--|

| Symbol                                                                               | -1 Spee | -1 Speed Grade -2 Speed Grade |     | -3 Spec | Unit |      |    |  |

|                                                                                      | Min     | Max                           | Min | Max     | Min  | Max  |    |  |

| t <sub>INSUBIDIR</sub>                                                               | 4.9     |                               | 5.8 |         | 6.8  |      | ns |  |

| t <sub>INHBIDIR</sub>                                                                | 0.0     |                               | 0.0 |         | 0.0  |      | ns |  |

| toutcobidir                                                                          | 2.0     | 5.3                           | 2.0 | 6.1     | 2.0  | 7.2  | ns |  |

| t <sub>XZBIDIR</sub>                                                                 |         | 7.4                           |     | 8.6     |      | 10.1 | ns |  |

| t <sub>ZXBIDIR</sub>                                                                 |         | 7.4                           |     | 8.6     |      | 10.1 | ns |  |

### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 37 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

# ClockLock & ClockBoost Timing Parameters

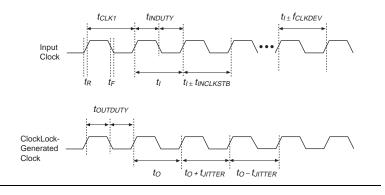

For the ClockLock and ClockBoost circuitry to function properly, the incoming clock must meet certain requirements. If these specifications are not met, the circuitry may not lock onto the incoming clock, which generates an erroneous clock within the device. The clock generated by the ClockLock and ClockBoost circuitry must also meet certain specifications. If the incoming clock meets these requirements during configuration, the ClockLock and ClockBoost circuitry will lock onto the clock during configuration. The circuit will be ready for use immediately after configuration. Figure 31 illustrates the incoming and generated clock specifications.

### Figure 31. Specifications for the Incoming & Generated Clocks

The  $t_l$  parameter refers to the nominal input clock period; the  $t_0$  parameter refers to the nominal output clock period.

Table 113 summarizes the ClockLock and ClockBoost parameters.

| Table 1             | Table 113. ClockLock & ClockBoost Parameters (Part 1 of 2)                       |     |     |     |      |  |  |  |

|---------------------|----------------------------------------------------------------------------------|-----|-----|-----|------|--|--|--|

| Symbol              | Parameter                                                                        | Min | Тур | Max | Unit |  |  |  |

| $t_R$               | Input rise time                                                                  |     |     | 2   | ns   |  |  |  |

| t <sub>F</sub>      | Input fall time                                                                  |     |     | 2   | ns   |  |  |  |

| t <sub>INDUTY</sub> | Input duty cycle                                                                 | 45  |     | 55  | %    |  |  |  |

| f <sub>CLK1</sub>   | Input clock frequency (ClockBoost clock multiplication factor equals 1)          |     |     | 80  | MHz  |  |  |  |

| t <sub>CLK1</sub>   | Input clock period (ClockBoost clock multiplication factor equals 1) 12.5 33.3 n |     | ns  |     |      |  |  |  |

| f <sub>CLK2</sub>   | Input clock frequency (ClockBoost clock multiplication factor equals 2) 16 50    |     | MHz |     |      |  |  |  |

| t <sub>CLK2</sub>   | Input clock period (ClockBoost clock multiplication factor equals 2) 20 62.5 n   |     | ns  |     |      |  |  |  |

Multiple FLEX 10K devices can be configured in any of the five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

| Table 116. Data Sources for Configuration |                                                                                                                         |  |  |  |  |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Configuration Scheme                      | Data Source                                                                                                             |  |  |  |  |

| Configuration device                      | EPC1, EPC2, EPC16, or EPC1441 configuration device                                                                      |  |  |  |  |

| Passive serial (PS)                       | BitBlaster, MasterBlaster, or ByteBlasterMV download cable, or serial data source                                       |  |  |  |  |

| Passive parallel asynchronous (PPA)       | Parallel data source                                                                                                    |  |  |  |  |

| Passive parallel synchronous (PPS)        | Parallel data source                                                                                                    |  |  |  |  |

| JTAG                                      | BitBlaster, MasterBlaster, or ByteBlasterMV download cable, or microprocessor with Jam STAPL file or Jam Byte-Code file |  |  |  |  |

# Device Pin-Outs

See the Altera web site (http://www.altera.com) or the Altera Digital Library for pin-out information.

# Revision History

The information contained in the *FLEX 10K Embedded Programmable Logic Device Family Data Sheet* version 4.2 supersedes information published in previous versions.

### **Version 4.2 Changes**

The following change was made to version 4.2 of the *FLEX 10K Embedded Programmable Logic Device Family Data Sheet*: updated Figure 13.

## **Version 4.1 Changes**

The following changes were made to version 4.1 of the FLEX 10K Embedded Programmable Logic Device Family Data Sheet.

- Updated General Description section

- Updated I/O Element section

- Updated SameFrame Pin-Outs section

- Updated Figure 16

- Updated Tables 13 and 116

- Added Note 9 to Table 19

- Added Note 10 to Table 24

- Added Note 10 to Table 28

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Applications Hotline: (800) 800-EPLD Customer Marketing: (408) 544-7104 Literature Services: lit\_req@altera.com

Copyright © 2003 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to

current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

I.S. EN ISO 9001