Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 144                                                        |

| Number of Logic Elements/Cells | 1152                                                       |

| Total RAM Bits                 | 12288                                                      |

| Number of I/O                  | 189                                                        |

| Number of Gates                | 63000                                                      |

| Voltage - Supply               | 4.75V ~ 5.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 70°C (TA)                                            |

| Package / Case                 | 240-BFQFP Exposed Pad                                      |

| Supplier Device Package        | 240-RQFP (32x32)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k20rc240-3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Dedicated Inputs & Global Signals Chip-Wide Reset Row Interconnect 2, 4, 8, 16 Data Data Out 8, 4, 2, 1 2, 4, 8, 16 Address D 8, 9, 10, 11 RAM/ROM  $256 \times 8$ 512 × 4  $1,024 \times 2$ Column 2,048 × 1 Interconnect WE D

Figure 4. FLEX 10K Embedded Array Block

## Note:

EAB Local Interconnect (1)

(1) EPF10K10, EPF10K10A, EPF10K20, EPF10K30, EPF10K30A, EPF10K40, EPF10K50, and EPF10K50V devices have 22 EAB local interconnect channels; EPF10K70, EPF10K100, EPF10K100A, EPF10K130V, and EPF10K250A devices have 26.

#### Normal Mode

The normal mode is suitable for general logic applications and wide decoding functions that can take advantage of a cascade chain. In normal mode, four data inputs from the LAB local interconnect and the carry-in are inputs to a four-input LUT. The Compiler automatically selects the carry-in or the DATA3 signal as one of the inputs to the LUT. The LUT output can be combined with the cascade-in signal to form a cascade chain through the cascade-out signal. Either the register or the LUT can be used to drive both the local interconnect and the FastTrack Interconnect at the same time.

The LUT and the register in the LE can be used independently; this feature is known as register packing. To support register packing, the LE has two outputs; one drives the local interconnect and the other drives the FastTrack Interconnect. The DATA4 signal can drive the register directly, allowing the LUT to compute a function that is independent of the registered signal; a three-input function can be computed in the LUT, and a fourth independent signal can be registered. Alternatively, a four-input function can be generated, and one of the inputs to this function can be used to drive the register. The register in a packed LE can still use the clock enable, clear, and preset signals in the LE. In a packed LE, the register can drive the FastTrack Interconnect while the LUT drives the local interconnect, or vice versa.

#### Arithmetic Mode

The arithmetic mode offers 2 three-input LUTs that are ideal for implementing adders, accumulators, and comparators. One LUT computes a three-input function, and the other generates a carry output. As shown in Figure 9 on page 19, the first LUT uses the carry-in signal and two data inputs from the LAB local interconnect to generate a combinatorial or registered output. For example, in an adder, this output is the sum of three signals: a, b, and carry-in. The second LUT uses the same three signals to generate a carry-out signal, thereby creating a carry chain. The arithmetic mode also supports simultaneous use of the cascade chain.

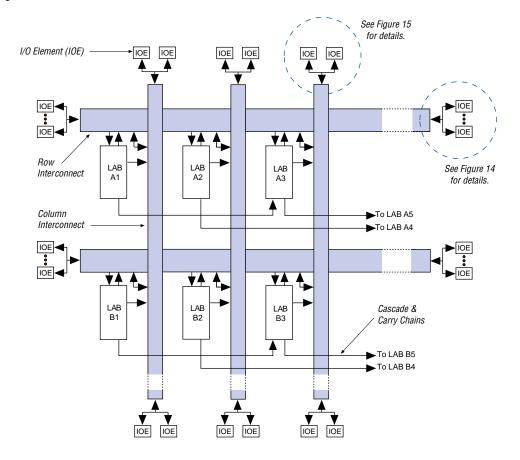

Figure 12 shows the interconnection of adjacent LABs and EABs with row, column, and local interconnects, as well as the associated cascade and carry chains. Each LAB is labeled according to its location: a letter represents the row and a number represents the column. For example, LAB B3 is in row B, column 3.

Figure 12. Interconnect Resources

Signals on the peripheral control bus can also drive the four global signals, referred to as GLOBAL0 through GLOBAL3 in Tables 8 and 9. The internally generated signal can drive the global signal, providing the same low-skew, low-delay characteristics for an internally generated signal as for a signal driven by an input. This feature is ideal for internally generated clear or clock signals with high fan-out. When a global signal is driven by internal logic, the dedicated input pin that drives that global signal cannot be used. The dedicated input pin should be driven to a known logic state (such as ground) and not be allowed to float.

When the chip-wide output enable pin is held low, it will tri-state all pins on the device. This option can be set in the Global Project Device Options menu. Additionally, the registers in the IOE can be reset by holding the chip-wide reset pin low.

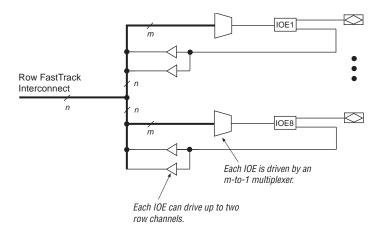

## Row-to-IOE Connections

When an IOE is used as an input signal, it can drive two separate row channels. The signal is accessible by all LEs within that row. When an IOE is used as an output, the signal is driven by a multiplexer that selects a signal from the row channels. Up to eight IOEs connect to each side of each row channel. See Figure 14.

Figure 14. FLEX 10K Row-to-IOE Connections

The values for m and n are provided in Table 10.

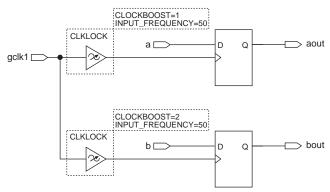

# ClockLock & ClockBoost Features

To support high-speed designs, selected FLEX 10K devices offer optional ClockLock and ClockBoost circuitry containing a phase-locked loop (PLL) that is used to increase design speed and reduce resource usage. The ClockLock circuitry uses a synchronizing PLL that reduces the clock delay and skew within a device. This reduction minimizes clock-to-output and setup times while maintaining zero hold times. The ClockBoost circuitry, which provides a clock multiplier, allows the designer to enhance device area efficiency by sharing resources within the device. The ClockBoost feature allows the designer to distribute a low-speed clock and multiply that clock on-device. Combined, the ClockLock and ClockBoost features provide significant improvements in system performance and bandwidth.

The ClockLock and ClockBoost features in FLEX 10K devices are enabled through the Altera software. External devices are not required to use these features. The output of the ClockLock and ClockBoost circuits is not available at any of the device pins.

The ClockLock and ClockBoost circuitry locks onto the rising edge of the incoming clock. The circuit output can only drive the clock inputs of registers; the generated clock cannot be gated or inverted.

The dedicated clock pin (GCLK1) supplies the clock to the ClockLock and ClockBoost circuitry. When the dedicated clock pin is driving the ClockLock or ClockBoost circuitry, it cannot drive elsewhere in the device.

In designs that require both a multiplied and non-multiplied clock, the clock trace on the board can be connected to GCLK1. With the Altera software, GCLK1 can feed both the ClockLock and ClockBoost circuitry in the FLEX 10K device. However, when both circuits are used, the other clock pin (GCLK0) cannot be used. Figure 17 shows a block diagram of how to enable both the ClockLock and ClockBoost circuits in the Altera software. The example shown is a schematic, but a similar approach applies for designs created in AHDL, VHDL, and Verilog HDL. When the ClockLock and ClockBoost circuits are used simultaneously, the input frequency parameter must be the same for both circuits. In Figure 17, the input frequency must meet the requirements specified when the ClockBoost multiplication factor is two.

Figure 17. Enabling ClockLock & ClockBoost in the Same Design

To use both the ClockLock and ClockBoost circuits in the same design, designers must use Revision C EPF10K100GC503-3DX devices and MAX+PLUS II software versions 7.2 or higher. The die revision is indicated by the third digit of the nine-digit code on the top side of the device.

## Output Configuration

This section discusses the peripheral component interconnect (PCI) pull-up clamping diode option, slew-rate control, open-drain output option, MultiVolt I/O interface, and power sequencing for FLEX 10K devices. The PCI pull-up clamping diode, slew-rate control, and open-drain output options are controlled pin-by-pin via Altera logic options. The MultiVolt I/O interface is controlled by connecting  $V_{CCIO}$  to a different voltage than  $V_{CCINT}.$  Its effect can be simulated in the Altera software via the **Global Project Device Options** dialog box (Assign menu).

## **PCI Clamping Diodes**

The EPF10K10A and EPF10K30A devices have a pull-up clamping diode on every I/O, dedicated input, and dedicated clock pin. PCI clamping diodes clamp the transient overshoot caused by reflected waves to the  $V_{\rm CCIO}$  value and are required for 3.3-V PCI compliance. Clamping diodes can also be used to limit overshoot in other systems.

Clamping diodes are controlled on a pin-by-pin basis via a logic option in the Altera software. When  $V_{\rm CCIO}$  is 3.3 V, a pin that has the clamping diode turned on can be driven by a 2.5-V or 3.3-V signal, but not a 5.0-V signal. When  $V_{\rm CCIO}$  is 2.5 V, a pin that has the clamping diode turned on can be driven by a 2.5-V signal, but not a 3.3-V or 5.0-V signal. However, a clamping diode can be turned on for a subset of pins, which allows devices to bridge between a 3.3-V PCI bus and a 5.0-V device.

Table 12 describes the FLEX 10K device supply voltages and MultiVolt  $\rm I/O$  support levels.

| Devices       | Supply Vo          | oltage (V)        | MultiVolt I/O Sup | MultiVolt I/O Support Levels (V) |  |  |

|---------------|--------------------|-------------------|-------------------|----------------------------------|--|--|

|               | V <sub>CCINT</sub> | V <sub>CCIO</sub> | Input             | Output                           |  |  |

| FLEX 10K (1)  | 5.0                | 5.0               | 3.3 or 5.0        | 5.0                              |  |  |

|               | 5.0                | 3.3               | 3.3 or 5.0        | 3.3 or 5.0                       |  |  |

| EPF10K50V (1) | 3.3                | 3.3               | 3.3 or 5.0        | 3.3 or 5.0                       |  |  |

| EPF10K130V    | 3.3                | 3.3               | 3.3 or 5.0        | 3.3 or 5.0                       |  |  |

| FLEX 10KA (1) | 3.3                | 3.3               | 2.5, 3.3, or 5.0  | 3.3 or 5.0                       |  |  |

|               | 3.3                | 2.5               | 2.5, 3.3, or 5.0  | 2.5                              |  |  |

#### Note

(1) 240-pin QFP packages do not support the MultiVolt I/O features, so they do not have separate V<sub>CCIO</sub> pins.

## Power Sequencing & Hot-Socketing

Because FLEX 10K devices can be used in a multi-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. The  $V_{\rm CCIO}$  and  $V_{\rm CCINT}$  power supplies can be powered in any order.

Signals can be driven into FLEX 10KA devices before and during power up without damaging the device. Additionally, FLEX 10KA devices do not drive out during power up. Once operating conditions are reached, FLEX 10KA devices operate as specified by the user.

IEEE Std. 1149.1 (JTAG) Boundary-Scan Support All FLEX 10K devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1-1990 specification. All FLEX 10K devices can also be configured using the JTAG pins through the BitBlaster serial download cable, or ByteBlasterMV parallel port download cable, or via hardware that uses the Jam<sup>TM</sup> programming and test language. JTAG BST can be performed before or after configuration, but not during configuration. FLEX 10K devices support the JTAG instructions shown in Table 13.

| Table 13. FLEX 10K | JTAG Instructions                                                                                                                                                                                                                     |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Instruction   | Description                                                                                                                                                                                                                           |

| SAMPLE/PRELOAD     | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern output at the device pins.                                                            |

| EXTEST             | Allows the external circuitry and board-level interconnections to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                |

| BYPASS             | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through a selected device to adjacent devices during normal device operation.                                          |

| USERCODE           | Selects the user electronic signature (USERCODE) register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                        |

| IDCODE             | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                 |

| ICR Instructions   | These instructions are used when configuring a FLEX 10K device via JTAG ports with a BitBlaster, or ByteBlasterMV or MasterBlaster download cable, or using a Jam File (.jam) or Jam Byte-Code File (.jbc) via an embedded processor. |

The instruction register length of FLEX 10K devices is 10 bits. The USERCODE register length in FLEX 10K devices is 32 bits; 7 bits are determined by the user, and 25 bits are predetermined. Tables 14 and 15 show the boundary-scan register length and device IDCODE information for FLEX 10K devices.

| Device                | Boundary-Scan<br>Register Length |  |  |

|-----------------------|----------------------------------|--|--|

| EPF10K10, EPF10K10A   | 480                              |  |  |

| EPF10K20              | 624                              |  |  |

| EPF10K30, EPF10K30A   | 768                              |  |  |

| EPF10K40              | 864                              |  |  |

| EPF10K50, EPF10K50V   | 960                              |  |  |

| EPF10K70              | 1,104                            |  |  |

| EPF10K100, EPF10K100A | 1,248                            |  |  |

| EPF10K130V            | 1,440                            |  |  |

| EPF10K250A            | 1,440                            |  |  |

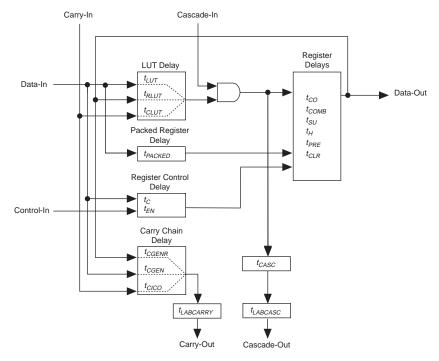

Figures 25 through 27 show the delays that correspond to various paths and functions within the LE, IOE, and EAB timing models.

Figure 25. FLEX 10K Device LE Timing Model

Tables 39 through 47 show EPF10K10 and EPF10K20 device internal and external timing parameters.

| Symbol              | -3 Spee | d Grade | -4 Spee | Unit |    |

|---------------------|---------|---------|---------|------|----|

|                     | Min     | Max     | Min     | Max  |    |

| $t_{LUT}$           |         | 1.4     |         | 1.7  | ns |

| t <sub>CLUT</sub>   |         | 0.6     |         | 0.7  | ns |

| t <sub>RLUT</sub>   |         | 1.5     |         | 1.9  | ns |

| t <sub>PACKED</sub> |         | 0.6     |         | 0.9  | ns |

| $t_{EN}$            |         | 1.0     |         | 1.2  | ns |

| t <sub>CICO</sub>   |         | 0.2     |         | 0.3  | ns |

| t <sub>CGEN</sub>   |         | 0.9     |         | 1.2  | ns |

| t <sub>CGENR</sub>  |         | 0.9     |         | 1.2  | ns |

| t <sub>CASC</sub>   |         | 0.8     |         | 0.9  | ns |

| $t_{\mathbb{C}}$    |         | 1.3     |         | 1.5  | ns |

| $t_{CO}$            |         | 0.9     |         | 1.1  | ns |

| $t_{\text{COMB}}$   |         | 0.5     |         | 0.6  | ns |

| t <sub>SU</sub>     | 1.3     |         | 2.5     |      | ns |

| $t_H$               | 1.4     |         | 1.6     |      | ns |

| t <sub>PRE</sub>    |         | 1.0     |         | 1.2  | ns |

| t <sub>CLR</sub>    |         | 1.0     |         | 1.2  | ns |

| t <sub>CH</sub>     | 4.0     |         | 4.0     |      | ns |

| $t_{CL}$            | 4.0     |         | 4.0     |      | ns |

| Symbol              | -3 Spee | d Grade | -4 Spee | Unit |    |

|---------------------|---------|---------|---------|------|----|

|                     | Min     | Max     | Min     | Max  |    |

| $t_{IOD}$           |         | 1.3     |         | 1.6  | ns |

| t <sub>IOC</sub>    |         | 0.5     |         | 0.7  | ns |

| t <sub>IOCO</sub>   |         | 0.2     |         | 0.2  | ns |

| t <sub>IOCOMB</sub> |         | 0.0     |         | 0.0  | ns |

| t <sub>IOSU</sub>   | 2.8     |         | 3.2     |      | ns |

| t <sub>IOH</sub>    | 1.0     |         | 1.2     |      | ns |

| t <sub>IOCLR</sub>  |         | 1.0     |         | 1.2  | ns |

| $t_{\text{OD1}}$    |         | 2.6     |         | 3.5  | ns |

| $t_{OD2}$           |         | 4.9     |         | 6.4  | ns |

| $t_{OD3}$           |         | 6.3     |         | 8.2  | ns |

| $t_{XZ}$            |         | 4.5     |         | 5.4  | ns |

| t <sub>ZX1</sub>    |         | 4.5     |         | 5.4  | ns |

| t <sub>ZX2</sub>    |         | 6.8     |         | 8.3  | ns |

| t <sub>ZX3</sub>    |         | 8.2     |         | 10.1 | ns |

| t <sub>INREG</sub>  |         | 6.0     |         | 7.5  | ns |

| t <sub>IOFD</sub>   |         | 3.1     |         | 3.5  | ns |

| t <sub>INCOMB</sub> |         | 3.1     |         | 3.5  | ns |

| Symbol                   | -3 Spee | d Grade | -4 Spee | d Grade | Unit |

|--------------------------|---------|---------|---------|---------|------|

|                          | Min     | Max     | Min     | Max     |      |

| t <sub>DIN2IOE</sub>     |         | 4.8     |         | 6.2     | ns   |

| t <sub>DIN2LE</sub>      |         | 2.6     |         | 3.8     | ns   |

| t <sub>DIN2DATA</sub>    |         | 4.3     |         | 5.2     | ns   |

| t <sub>DCLK2IOE</sub>    |         | 3.4     |         | 4.0     | ns   |

| t <sub>DCLK2LE</sub>     |         | 2.6     |         | 3.8     | ns   |

| t <sub>SAMELAB</sub>     |         | 0.6     |         | 0.6     | ns   |

| t <sub>SAMEROW</sub>     |         | 3.6     |         | 3.8     | ns   |

| t <sub>SAME</sub> COLUMN |         | 0.9     |         | 1.1     | ns   |

| t <sub>DIFFROW</sub>     |         | 4.5     |         | 4.9     | ns   |

| t <sub>TWOROWS</sub>     |         | 8.1     |         | 8.7     | ns   |

| t <sub>LEPERIPH</sub>    |         | 3.3     |         | 3.9     | ns   |

| t <sub>LABCARRY</sub>    |         | 0.5     |         | 0.8     | ns   |

| t <sub>LABCASC</sub>     |         | 2.7     |         | 3.0     | ns   |

| Symbol                   | -3 Spee | d Grade | -4 Spee | Unit |    |

|--------------------------|---------|---------|---------|------|----|

|                          | Min     | Max     | Min     | Max  |    |

| t <sub>DIN2IOE</sub>     |         | 5.2     |         | 6.6  | ns |

| t <sub>DIN2LE</sub>      |         | 2.6     |         | 3.8  | ns |

| t <sub>DIN2DATA</sub>    |         | 4.3     |         | 5.2  | ns |

| t <sub>DCLK2IOE</sub>    |         | 4.3     |         | 4.0  | ns |

| t <sub>DCLK2LE</sub>     |         | 2.6     |         | 3.8  | ns |

| t <sub>SAMELAB</sub>     |         | 0.6     |         | 0.6  | ns |

| t <sub>SAMEROW</sub>     |         | 3.7     |         | 3.9  | ns |

| t <sub>SAME</sub> COLUMN |         | 1.4     |         | 1.6  | ns |

| t <sub>DIFFROW</sub>     |         | 5.1     |         | 5.5  | ns |

| t <sub>TWOROWS</sub>     |         | 8.8     |         | 9.4  | ns |

| LEPERIPH                 |         | 4.7     |         | 5.6  | ns |

| t <sub>LABCARRY</sub>    |         | 0.5     |         | 0.8  | ns |

| t <sub>LABCASC</sub>     |         | 2.7     |         | 3.0  | ns |

| Symbol                 | -3 Snee | d Grade | -4 Spee | Unit |        |

|------------------------|---------|---------|---------|------|--------|

| Symbol                 | -       |         |         |      | O IIII |

|                        | Min     | Max     | Min     | Max  |        |

| t <sub>EABAA</sub>     |         | 13.7    |         | 17.0 | ns     |

| t <sub>EABRCCOMB</sub> | 13.7    |         | 17.0    |      | ns     |

| t <sub>EABRCREG</sub>  | 9.7     |         | 11.9    |      | ns     |

| t <sub>EABWP</sub>     | 5.8     |         | 7.2     |      | ns     |

| t <sub>EABWCCOMB</sub> | 7.3     |         | 9.0     |      | ns     |

| t <sub>EABWCREG</sub>  | 13.0    |         | 16.0    |      | ns     |

| t <sub>EABDD</sub>     |         | 10.0    |         | 12.5 | ns     |

| t <sub>EABDATACO</sub> |         | 2.0     |         | 3.4  | ns     |

| t <sub>EABDATASU</sub> | 5.3     |         | 5.6     |      | ns     |

| t <sub>EABDATAH</sub>  | 0.0     |         | 0.0     |      | ns     |

| t <sub>EABWESU</sub>   | 5.5     |         | 5.8     |      | ns     |

| t <sub>EABWEH</sub>    | 0.0     |         | 0.0     |      | ns     |

| t <sub>EABWDSU</sub>   | 5.5     |         | 5.8     |      | ns     |

| t <sub>EABWDH</sub>    | 0.0     |         | 0.0     |      | ns     |

| t <sub>EABWASU</sub>   | 2.1     |         | 2.7     |      | ns     |

| t <sub>EABWAH</sub>    | 0.0     |         | 0.0     |      | ns     |

| $t_{EABWO}$            |         | 9.5     |         | 11.8 | ns     |

| Symbol                  | -3DX Spe | ed Grade | -3 Spee | d Grade | -4 Spee | Unit |    |

|-------------------------|----------|----------|---------|---------|---------|------|----|

|                         | Min      | Max      | Min     | Max     | Min     | Max  |    |

| t <sub>EABAA</sub>      |          | 13.7     |         | 13.7    |         | 17.0 | ns |

| t <sub>EABRCCOMB</sub>  | 13.7     |          | 13.7    |         | 17.0    |      | ns |

| t <sub>EABRCREG</sub>   | 9.7      |          | 9.7     |         | 11.9    |      | ns |

| t <sub>EABWP</sub>      | 5.8      |          | 5.8     |         | 7.2     |      | ns |

| t <sub>EABWCCOMB</sub>  | 7.3      |          | 7.3     |         | 9.0     |      | ns |

| t <sub>EABWCREG</sub>   | 13.0     |          | 13.0    |         | 16.0    |      | ns |

| t <sub>EABDD</sub>      |          | 10.0     |         | 10.0    |         | 12.5 | ns |

| t <sub>EABDATA</sub> CO |          | 2.0      |         | 2.0     |         | 3.4  | ns |

| t <sub>EABDATASU</sub>  | 5.3      |          | 5.3     |         | 5.6     |      | ns |

| t <sub>EABDATAH</sub>   | 0.0      |          | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWESU</sub>    | 5.5      |          | 5.5     |         | 5.8     |      | ns |

| t <sub>EABWEH</sub>     | 0.0      |          | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWDSU</sub>    | 5.5      |          | 5.5     |         | 5.8     |      | ns |

| t <sub>EABWDH</sub>     | 0.0      |          | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWASU</sub>    | 2.1      |          | 2.1     |         | 2.7     |      | ns |

| t <sub>EABWAH</sub>     | 0.0      |          | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWO</sub>      |          | 9.5      |         | 9.5     |         | 11.8 | ns |

| Cumbal                 | 1 One and Owned |     | 3 Chood Crods  |     | O Cuend Ounds  |      | 40             |      | 11-24 |

|------------------------|-----------------|-----|----------------|-----|----------------|------|----------------|------|-------|

| Symbol                 | -1 Speed Grade  |     | -2 Speed Grade |     | -3 Speed Grade |      | -4 Speed Grade |      | Unit  |

|                        | Min             | Max | Min            | Max | Min            | Max  | Min            | Max  |       |

| t <sub>EABDATA1</sub>  |                 | 1.7 |                | 2.8 |                | 3.4  |                | 4.6  | ns    |

| t <sub>EABDATA2</sub>  |                 | 4.9 |                | 3.9 |                | 4.8  |                | 5.9  | ns    |

| t <sub>EABWE1</sub>    |                 | 0.0 |                | 2.5 |                | 3.0  |                | 3.7  | ns    |

| t <sub>EABWE2</sub>    |                 | 4.0 |                | 4.1 |                | 5.0  |                | 6.2  | ns    |

| t <sub>EABCLK</sub>    |                 | 0.4 |                | 0.8 |                | 1.0  |                | 1.2  | ns    |

| t <sub>EABCO</sub>     |                 | 0.1 |                | 0.2 |                | 0.3  |                | 0.4  | ns    |

| t <sub>EABBYPASS</sub> |                 | 0.9 |                | 1.1 |                | 1.3  |                | 1.6  | ns    |

| t <sub>EABSU</sub>     | 0.8             |     | 1.5            |     | 1.8            |      | 2.2            |      | ns    |

| t <sub>EABH</sub>      | 0.8             |     | 1.6            |     | 2.0            |      | 2.5            |      | ns    |

| $t_{AA}$               |                 | 5.5 |                | 8.2 |                | 10.0 |                | 12.4 | ns    |

| $t_{WP}$               | 6.0             |     | 4.9            |     | 6.0            |      | 7.4            |      | ns    |

| t <sub>WDSU</sub>      | 0.1             |     | 0.8            |     | 1.0            |      | 1.2            |      | ns    |

| t <sub>WDH</sub>       | 0.1             |     | 0.2            |     | 0.3            |      | 0.4            |      | ns    |

| t <sub>WASU</sub>      | 0.1             |     | 0.4            |     | 0.5            |      | 0.6            |      | ns    |

| t <sub>WAH</sub>       | 0.1             |     | 0.8            |     | 1.0            |      | 1.2            |      | ns    |

| $t_{WO}$               |                 | 2.8 |                | 4.3 |                | 5.3  |                | 6.5  | ns    |

| $t_{DD}$               |                 | 2.8 |                | 4.3 |                | 5.3  |                | 6.5  | ns    |

| t <sub>EABOUT</sub>    |                 | 0.5 |                | 0.4 |                | 0.5  |                | 0.6  | ns    |

| t <sub>EABCH</sub>     | 2.0             |     | 4.0            |     | 4.0            |      | 4.0            |      | ns    |

| t <sub>EABCL</sub>     | 6.0             |     | 4.9            |     | 6.0            |      | 7.4            |      | ns    |

### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

Tables 78 through 84 show EPF10K130V device internal and external timing parameters.

| Symbol              | -2 Speed Grade |     | -3 Spee | ed Grade | -4 Spee | Unit |    |

|---------------------|----------------|-----|---------|----------|---------|------|----|

|                     | Min            | Max | Min     | Max      | Min     | Max  |    |

| $t_{LUT}$           |                | 1.3 |         | 1.8      |         | 2.3  | ns |

| t <sub>CLUT</sub>   |                | 0.5 |         | 0.7      |         | 0.9  | ns |

| $t_{RLUT}$          |                | 1.2 |         | 1.7      |         | 2.2  | ns |

| t <sub>PACKED</sub> |                | 0.5 |         | 0.6      |         | 0.7  | ns |

| $t_{EN}$            |                | 0.6 |         | 0.8      |         | 1.0  | ns |

| $t_{CICO}$          |                | 0.2 |         | 0.3      |         | 0.4  | ns |

| t <sub>CGEN</sub>   |                | 0.3 |         | 0.4      |         | 0.5  | ns |

| t <sub>CGENR</sub>  |                | 0.7 |         | 1.0      |         | 1.3  | ns |

| $t_{CASC}$          |                | 0.9 |         | 1.2      |         | 1.5  | ns |

| $t_{\rm C}$         |                | 1.9 |         | 2.4      |         | 3.0  | ns |

| $t_{CO}$            |                | 0.6 |         | 0.9      |         | 1.1  | ns |

| t <sub>COMB</sub>   |                | 0.5 |         | 0.7      |         | 0.9  | ns |

| t <sub>SU</sub>     | 0.2            |     | 0.2     |          | 0.3     |      | ns |

| t <sub>H</sub>      | 0.0            |     | 0.0     |          | 0.0     |      | ns |

| t <sub>PRE</sub>    |                | 2.4 |         | 3.1      |         | 3.9  | ns |

| t <sub>CLR</sub>    |                | 2.4 |         | 3.1      |         | 3.9  | ns |

| t <sub>CH</sub>     | 4.0            |     | 4.0     |          | 4.0     |      | ns |

| $t_{CL}$            | 4.0            |     | 4.0     |          | 4.0     |      | ns |

### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

Tables 92 through 98 show EPF10K30A device internal and external timing parameters.

| Table 92. EPF10K30A Device LE Timing Microparameters Note (1) |                |     |                |     |                |     |      |  |

|---------------------------------------------------------------|----------------|-----|----------------|-----|----------------|-----|------|--|

| Symbol                                                        | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |  |

|                                                               | Min            | Max | Min            | Max | Min            | Max |      |  |

| $t_{LUT}$                                                     |                | 0.8 |                | 1.1 |                | 1.5 | ns   |  |

| t <sub>CLUT</sub>                                             |                | 0.6 |                | 0.7 |                | 1.0 | ns   |  |

| t <sub>RLUT</sub>                                             |                | 1.2 |                | 1.5 |                | 2.0 | ns   |  |

| t <sub>PACKED</sub>                                           |                | 0.6 |                | 0.6 |                | 1.0 | ns   |  |

| t <sub>EN</sub>                                               |                | 1.3 |                | 1.5 |                | 2.0 | ns   |  |

| t <sub>CICO</sub>                                             |                | 0.2 |                | 0.3 |                | 0.4 | ns   |  |

| t <sub>CGEN</sub>                                             |                | 0.8 |                | 1.0 |                | 1.3 | ns   |  |

| t <sub>CGENR</sub>                                            |                | 0.6 |                | 0.8 |                | 1.0 | ns   |  |

| t <sub>CASC</sub>                                             |                | 0.9 |                | 1.1 |                | 1.4 | ns   |  |

| $t_{C}$                                                       |                | 1.1 |                | 1.3 |                | 1.7 | ns   |  |

| $t_{CO}$                                                      |                | 0.4 |                | 0.6 |                | 0.7 | ns   |  |

| $t_{COMB}$                                                    |                | 0.6 |                | 0.7 |                | 0.9 | ns   |  |

| $t_{SU}$                                                      | 0.9            |     | 0.9            |     | 1.4            |     | ns   |  |

| $t_H$                                                         | 1.1            |     | 1.3            |     | 1.7            |     | ns   |  |

| t <sub>PRE</sub>                                              |                | 0.5 |                | 0.6 |                | 0.8 | ns   |  |

| t <sub>CLR</sub>                                              |                | 0.5 |                | 0.6 |                | 0.8 | ns   |  |

| t <sub>CH</sub>                                               | 3.0            |     | 3.5            |     | 4.0            |     | ns   |  |

| $t_{CL}$                                                      | 3.0            |     | 3.5            |     | 4.0            |     | ns   |  |

| Symbol              | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|---------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                     | Min            | Max | Min            | Max | Min            | Max |      |

| $t_{IOD}$           |                | 2.2 |                | 2.6 |                | 3.4 | ns   |

| t <sub>IOC</sub>    |                | 0.3 |                | 0.3 |                | 0.5 | ns   |

| t <sub>IOCO</sub>   |                | 0.2 |                | 0.2 |                | 0.3 | ns   |

| t <sub>IOCOMB</sub> |                | 0.5 |                | 0.6 |                | 0.8 | ns   |

| t <sub>IOSU</sub>   | 1.4            |     | 1.7            |     | 2.2            |     | ns   |

#### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 37 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

## ClockLock & ClockBoost Timing Parameters

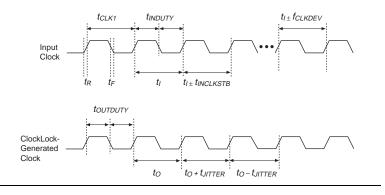

For the ClockLock and ClockBoost circuitry to function properly, the incoming clock must meet certain requirements. If these specifications are not met, the circuitry may not lock onto the incoming clock, which generates an erroneous clock within the device. The clock generated by the ClockLock and ClockBoost circuitry must also meet certain specifications. If the incoming clock meets these requirements during configuration, the ClockLock and ClockBoost circuitry will lock onto the clock during configuration. The circuit will be ready for use immediately after configuration. Figure 31 illustrates the incoming and generated clock specifications.

## Figure 31. Specifications for the Incoming & Generated Clocks

The  $t_l$  parameter refers to the nominal input clock period; the  $t_0$  parameter refers to the nominal output clock period.

Table 113 summarizes the ClockLock and ClockBoost parameters.

| Table 113. ClockLock & ClockBoost Parameters (Part 1 of 2) |                                                                         |      |     |      |      |  |  |

|------------------------------------------------------------|-------------------------------------------------------------------------|------|-----|------|------|--|--|

| Symbol                                                     | Parameter                                                               | Min  | Тур | Max  | Unit |  |  |

| t <sub>R</sub>                                             | Input rise time                                                         |      |     | 2    | ns   |  |  |

| t <sub>F</sub>                                             | Input fall time                                                         |      |     | 2    | ns   |  |  |

| t <sub>INDUTY</sub>                                        | Input duty cycle                                                        | 45   |     | 55   | %    |  |  |

| f <sub>CLK1</sub>                                          | Input clock frequency (ClockBoost clock multiplication factor equals 1) | 30   |     | 80   | MHz  |  |  |

| t <sub>CLK1</sub>                                          | Input clock period (ClockBoost clock multiplication factor equals 1)    | 12.5 |     | 33.3 | ns   |  |  |

| f <sub>CLK2</sub>                                          | Input clock frequency (ClockBoost clock multiplication factor equals 2) | 16   |     | 50   | MHz  |  |  |

| t <sub>CLK2</sub>                                          | Input clock period (ClockBoost clock multiplication factor equals 2)    | 20   |     | 62.5 | ns   |  |  |

$f_{MAX}$  = Maximum operating frequency in MHz

N = Total number of logic cells used in the device

tog<sub>LC</sub> = Average percent of logic cells toggling at each clock (typically 12.5%)

K = Constant, shown in Tables 114 and 115

| Table 114. FLEX 10K K Constant Values |         |  |  |  |  |

|---------------------------------------|---------|--|--|--|--|

| Device                                | K Value |  |  |  |  |

| EPF10K10                              | 82      |  |  |  |  |

| EPF10K20                              | 89      |  |  |  |  |

| EPF10K30                              | 88      |  |  |  |  |

| EPF10K40                              | 92      |  |  |  |  |

| EPF10K50                              | 95      |  |  |  |  |

| EPF10K70                              | 85      |  |  |  |  |

| EPF10K100                             | 88      |  |  |  |  |

| Table 115. FLEX 10KA K Constant Values |         |  |  |  |

|----------------------------------------|---------|--|--|--|

| Device                                 | K Value |  |  |  |

| EPF10K10A                              | 17      |  |  |  |

| EPF10K30A                              | 17      |  |  |  |

| EPF10K50V                              | 19      |  |  |  |

| EPF10K100A                             | 19      |  |  |  |

| EPF10K130V                             | 22      |  |  |  |

| EPF10K250A                             | 23      |  |  |  |

This calculation provides an  $I_{CC}$  estimate based on typical conditions with no output load. The actual  $I_{CC}$  should be verified during operation because this measurement is sensitive to the actual pattern in the device and the environmental operating conditions.

To better reflect actual designs, the power model (and the constant *K* in the power calculation equations) for continuous interconnect FLEX devices assumes that logic cells drive FastTrack Interconnect channels. In contrast, the power model of segmented FPGAs assumes that all logic cells drive only one short interconnect segment. This assumption may lead to inaccurate results, compared to measured power consumption for an actual design in a segmented interconnect FPGA.

Figure 32 shows the relationship between the current and operating frequency of FLEX 10K devices.

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Applications Hotline: (800) 800-EPLD Customer Marketing: (408) 544-7104 Literature Services: lit\_req@altera.com

Copyright © 2003 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to

current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

I.S. EN ISO 9001