Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                               |

|--------------------------------|---------------------------------------------------------------|

| Product Status                 | Obsolete                                                      |

| Number of LABs/CLBs            | 216                                                           |

| Number of Logic Elements/Cells | 1728                                                          |

| Total RAM Bits                 | 12288                                                         |

| Number of I/O                  | 102                                                           |

| Number of Gates                | 69000                                                         |

| Voltage - Supply               | 3V ~ 3.6V                                                     |

| Mounting Type                  | Surface Mount                                                 |

| Operating Temperature          | -40°C ~ 85°C (TA)                                             |

| Package / Case                 | 144-LQFP                                                      |

| Supplier Device Package        | 144-TQFP (20x20)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k30a3nti144-3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The programmable flipflop in the LE can be configured for D, T, JK, or SR operation. The clock, clear, and preset control signals on the flipflop can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the flipflop is bypassed and the output of the LUT drives the output of the LE.

The LE has two outputs that drive the interconnect; one drives the local interconnect and the other drives either the row or column FastTrack Interconnect. The two outputs can be controlled independently. For example, the LUT can drive one output while the register drives the other output. This feature, called register packing, can improve LE utilization because the register and the LUT can be used for unrelated functions.

The FLEX 10K architecture provides two types of dedicated high-speed data paths that connect adjacent LEs without using local interconnect paths: carry chains and cascade chains. The carry chain supports high-speed counters and adders; the cascade chain implements wide-input functions with minimum delay. Carry and cascade chains connect all LEs in an LAB and all LABs in the same row. Intensive use of carry and cascade chains can reduce routing flexibility. Therefore, the use of these chains should be limited to speed-critical portions of a design.

# Carry Chain

The carry chain provides a very fast (as low as 0.2 ns) carry-forward function between LEs. The carry-in signal from a lower-order bit drives forward into the higher-order bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the FLEX 10K architecture to implement high-speed counters, adders, and comparators of arbitrary width efficiently. Carry chain logic can be created automatically by the Compiler during design processing, or manually by the designer during design entry. Parameterized functions such as LPM and DesignWare functions automatically take advantage of carry chains.

Carry chains longer than eight LEs are automatically implemented by linking LABs together. For enhanced fitting, a long carry chain skips alternate LABs in a row. A carry chain longer than one LAB skips either from even-numbered LAB to even-numbered LAB, or from odd-numbered LAB to odd-numbered LAB. For example, the last LE of the first LAB in a row carries to the first LE of the third LAB in the row. The carry chain does not cross the EAB at the middle of the row. For instance, in the EPF10K50 device, the carry chain stops at the eighteenth LAB and a new one begins at the nineteenth LAB.

#### Normal Mode

The normal mode is suitable for general logic applications and wide decoding functions that can take advantage of a cascade chain. In normal mode, four data inputs from the LAB local interconnect and the carry-in are inputs to a four-input LUT. The Compiler automatically selects the carry-in or the DATA3 signal as one of the inputs to the LUT. The LUT output can be combined with the cascade-in signal to form a cascade chain through the cascade-out signal. Either the register or the LUT can be used to drive both the local interconnect and the FastTrack Interconnect at the same time.

The LUT and the register in the LE can be used independently; this feature is known as register packing. To support register packing, the LE has two outputs; one drives the local interconnect and the other drives the FastTrack Interconnect. The DATA4 signal can drive the register directly, allowing the LUT to compute a function that is independent of the registered signal; a three-input function can be computed in the LUT, and a fourth independent signal can be registered. Alternatively, a four-input function can be generated, and one of the inputs to this function can be used to drive the register. The register in a packed LE can still use the clock enable, clear, and preset signals in the LE. In a packed LE, the register can drive the FastTrack Interconnect while the LUT drives the local interconnect, or vice versa.

#### Arithmetic Mode

The arithmetic mode offers 2 three-input LUTs that are ideal for implementing adders, accumulators, and comparators. One LUT computes a three-input function, and the other generates a carry output. As shown in Figure 9 on page 19, the first LUT uses the carry-in signal and two data inputs from the LAB local interconnect to generate a combinatorial or registered output. For example, in an adder, this output is the sum of three signals: a, b, and carry-in. The second LUT uses the same three signals to generate a carry-out signal, thereby creating a carry chain. The arithmetic mode also supports simultaneous use of the cascade chain.

# Up/Down Counter Mode

The up/down counter mode offers counter enable, clock enable, synchronous up/down control, and data loading options. These control signals are generated by the data inputs from the LAB local interconnect, the carry-in signal, and output feedback from the programmable register. The Up/down counter mode uses 2 three-input LUTs: one generates the counter data, and the other generates the fast carry bit. A 2-to-1 multiplexer provides synchronous loading. Data can also be loaded asynchronously with the clear and preset register control signals, without using the LUT resources.

## Clearable Counter Mode

The clearable counter mode is similar to the up/down counter mode, but supports a synchronous clear instead of the up/down control. The clear function is substituted for the cascade-in signal in the up/down counter mode. Clearable counter mode uses 2 three-input LUTs: one generates the counter data, and the other generates the fast carry bit. Synchronous loading is provided by a 2-to-1 multiplexer. The output of this multiplexer is ANDed with a synchronous clear signal.

# Internal Tri-State Emulation

Internal tri-state emulation provides internal tri-stating without the limitations of a physical tri-state bus. In a physical tri-state bus, the tri-state buffers' output enable (OE) signals select which signal drives the bus. However, if multiple OE signals are active, contending signals can be driven onto the bus. Conversely, if no OE signals are active, the bus will float. Internal tri-state emulation resolves contending tri-state buffers to a low value and floating buses to a high value, thereby eliminating these problems. The Altera software automatically implements tri-state bus functionality with a multiplexer.

# Clear & Preset Logic Control

Logic for the programmable register's clear and preset functions is controlled by the DATA3, LABCTRL1, and LABCTRL2 inputs to the LE. The clear and preset control structure of the LE asynchronously loads signals into a register. Either LABCTRL1 or LABCTRL2 can control the asynchronous clear. Alternatively, the register can be set up so that LABCTRL1 implements an asynchronous load. The data to be loaded is driven to DATA3; when LABCTRL1 is asserted, DATA3 is loaded into the register.

For improved routing, the row interconnect is comprised of a combination of full-length and half-length channels. The full-length channels connect to all LABs in a row; the half-length channels connect to the LABs in half of the row. The EAB can be driven by the half-length channels in the left half of the row and by the full-length channels. The EAB drives out to the full-length channels. In addition to providing a predictable, row-wide interconnect, this architecture provides increased routing resources. Two neighboring LABs can be connected using a half-row channel, thereby saving the other half of the channel for the other half of the row.

Table 7 summarizes the FastTrack Interconnect resources available in each FLEX  $10 \mathrm{K}$  device.

| Table 7. FLEX 1         | Table 7. FLEX 10K FastTrack Interconnect Resources |                     |         |                        |  |  |  |  |

|-------------------------|----------------------------------------------------|---------------------|---------|------------------------|--|--|--|--|

| Device                  | Rows                                               | Channels per<br>Row | Columns | Channels per<br>Column |  |  |  |  |

| EPF10K10<br>EPF10K10A   | 3                                                  | 144                 | 24      | 24                     |  |  |  |  |

| EPF10K20                | 6                                                  | 144                 | 24      | 24                     |  |  |  |  |

| EPF10K30<br>EPF10K30A   | 6                                                  | 216                 | 36      | 24                     |  |  |  |  |

| EPF10K40                | 8                                                  | 216                 | 36      | 24                     |  |  |  |  |

| EPF10K50<br>EPF10K50V   | 10                                                 | 216                 | 36      | 24                     |  |  |  |  |

| EPF10K70                | 9                                                  | 312                 | 52      | 24                     |  |  |  |  |

| EPF10K100<br>EPF10K100A | 12                                                 | 312                 | 52      | 24                     |  |  |  |  |

| EPF10K130V              | 16                                                 | 312                 | 52      | 32                     |  |  |  |  |

| EPF10K250A              | 20                                                 | 456                 | 76      | 40                     |  |  |  |  |

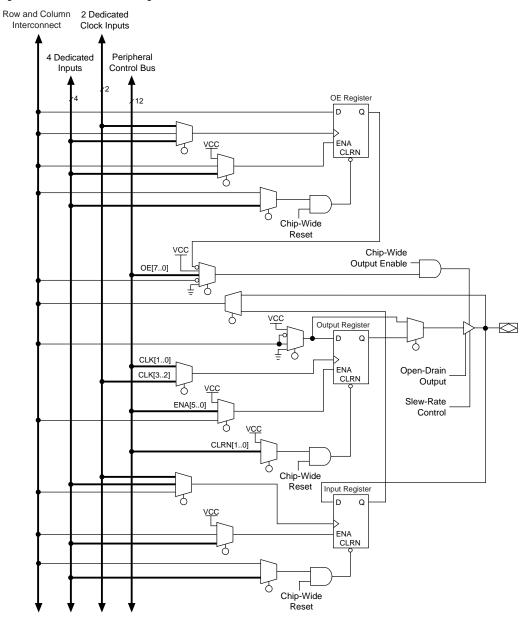

In addition to general-purpose I/O pins, FLEX 10K devices have six dedicated input pins that provide low-skew signal distribution across the device. These six inputs can be used for global clock, clear, preset, and peripheral output enable and clock enable control signals. These signals are available as control signals for all LABs and IOEs in the device.

The dedicated inputs can also be used as general-purpose data inputs because they can feed the local interconnect of each LAB in the device. However, the use of dedicated inputs as data inputs can introduce additional delay into the control signal network.

Figure 13. Bidirectional I/O Registers

Each IOE selects the clock, clear, clock enable, and output enable controls from a network of I/O control signals called the peripheral control bus. The peripheral control bus uses high-speed drivers to minimize signal skew across devices; it provides up to 12 peripheral control signals that can be allocated as follows:

- Up to eight output enable signals

- Up to six clock enable signals

- Up to two clock signals

- Up to two clear signals

If more than six clock enable or eight output enable signals are required, each IOE on the device can be controlled by clock enable and output enable signals driven by specific LEs. In addition to the two clock signals available on the peripheral control bus, each IOE can use one of two dedicated clock pins. Each peripheral control signal can be driven by any of the dedicated input pins or the first LE of each LAB in a particular row. In addition, an LE in a different row can drive a column interconnect, which causes a row interconnect to drive the peripheral control signal. The chip-wide reset signal will reset all IOE registers, overriding any other control signals.

Tables 8 and 9 list the sources for each peripheral control signal, and the rows that can drive global signals. These tables also show how the output enable, clock enable, clock, and clear signals share 12 peripheral control signals.

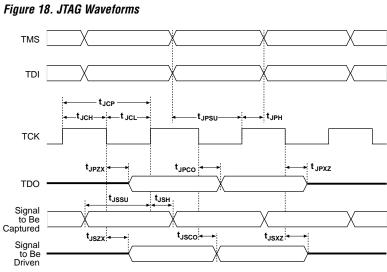

Figure 18 shows the timing requirements for the JTAG signals.

Table 16 shows the timing parameters and values for FLEX 10K devices.

| Table 1           | 6. JTAG Timing Parameters & Values             |     |     |      |

|-------------------|------------------------------------------------|-----|-----|------|

| Symbol            | Parameter                                      | Min | Max | Unit |

| t <sub>JCP</sub>  | TCK clock period                               | 100 |     | ns   |

| t <sub>JCH</sub>  | TCK clock high time                            | 50  |     | ns   |

| t <sub>JCL</sub>  | TCK clock low time                             | 50  |     | ns   |

| t <sub>JPSU</sub> | JTAG port setup time                           | 20  |     | ns   |

| t <sub>JPH</sub>  | JTAG port hold time                            | 45  |     | ns   |

| t <sub>JPCO</sub> | JTAG port clock to output                      |     | 25  | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output       |     | 25  | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance       |     | 25  | ns   |

| t <sub>JSSU</sub> | Capture register setup time                    | 20  |     | ns   |

| t <sub>JSH</sub>  | Capture register hold time                     | 45  |     | ns   |

| t <sub>JSCO</sub> | Update register clock to output                |     | 35  | ns   |

| t <sub>JSZX</sub> | Update register high-impedance to valid output |     | 35  | ns   |

| t <sub>JSXZ</sub> | Update register valid output to high impedance |     | 35  | ns   |

#### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $V_{CC}$  rise time is 100 ms.  $V_{CC}$  must rise monotonically.

- (5) Typical values are for  $T_A = 25^{\circ}$  C and  $V_{CC} = 5.0$  V.

- (6) These values are specified under the Recommended Operation Condition shown in Table 18 on page 45.

- (7) The I<sub>OH</sub> parameter refers to high-level TTL or CMOS output current.

- (8) The  $I_{OL}$  parameter refers to low-level TTL or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (9) This value is specified for normal device operation. The value may vary during power-up.

- (10) Capacitance is sample-tested only.

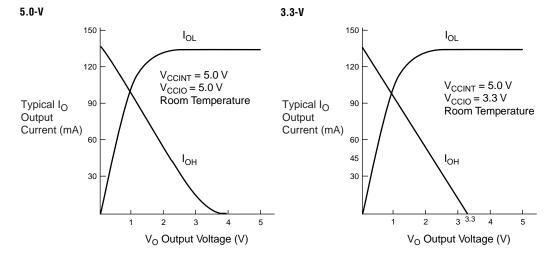

Figure 20 shows the typical output drive characteristics of FLEX 10K devices with 5.0-V and 3.3-V  $V_{\rm CCIO}$ . The output driver is compliant with the 5.0-V *PCI Local Bus Specification, Revision 2.2* (for 5.0-V  $V_{\rm CCIO}$ ).

Figure 20. Output Drive Characteristics of FLEX 10K Devices

Figure 21 shows the typical output drive characteristics of EPF10K50V and EPF10K130V devices.

Typical I<sub>O</sub>

Output

Current (mA)

40

V<sub>CC</sub> = 3.3 V

Room Temperature

1

2

V<sub>O</sub> Output Voltage (V)

Figure 21. Output Drive Characteristics of EPF10K50V & EPF10K130V Devices

Tables 26 through 31 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 3.3-V FLEX 10K devices.

| Table 2          | 6. FLEX 10KA 3.3-V Device A | bsolute Maximum Ratings Note ( | (1)  |      |      |

|------------------|-----------------------------|--------------------------------|------|------|------|

| Symbol           | Parameter                   | Conditions                     | Min  | Max  | Unit |

| V <sub>CC</sub>  | Supply voltage              | With respect to ground (2)     | -0.5 | 4.6  | V    |

| V <sub>I</sub>   | DC input voltage            |                                | -2.0 | 5.75 | V    |

| I <sub>OUT</sub> | DC output current, per pin  |                                | -25  | 25   | mA   |

| T <sub>STG</sub> | Storage temperature         | No bias                        | -65  | 150  | ° C  |

| T <sub>AMB</sub> | Ambient temperature         | Under bias                     | -65  | 135  | °C   |

| TJ               | Junction temperature        | Ceramic packages, under bias   |      | 150  | ° C  |

|                  |                             | PQFP, TQFP, RQFP, and BGA      |      | 135  | ° C  |

|                  |                             | packages, under bias           |      |      |      |

#### Notes to tables:

- Microparameters are timing delays contributed by individual architectural elements. These parameters cannot be measured explicitly.

- (2) Operating conditions:  $V_{CCIO} = 5.0 \text{ V} \pm 5\%$  for commercial use in FLEX 10K devices.

$V_{CCIO}$  = 5.0 V ± 10% for industrial use in FLEX 10K devices.

$V_{CCIO} = 3.3 \text{ V} \pm 10\%$  for commercial or industrial use in FLEX 10KA devices.

- (3) Operating conditions:  $V_{CCIO} = 3.3 \text{ V} \pm 10\%$  for commercial or industrial use in FLEX 10K devices.

- $V_{CCIO}$  = 2.5 V ± 0.2 V for commercial or industrial use in FLEX 10KA devices.

- (4) Operating conditions:  $V_{CCIO} = 2.5 \text{ V}$ , 3.3 V, or 5.0 V.

- (5) Because the RAM in the EAB is self-timed, this parameter can be ignored when the WE signal is registered.

- (6) EAB macroparameters are internal parameters that can simplify predicting the behavior of an EAB at its boundary; these parameters are calculated by summing selected microparameters.

- (7) These parameters are worst-case values for typical applications. Post-compilation timing simulation and timing analysis are required to determine actual worst-case performance.

- (8) External reference timing parameters are factory-tested, worst-case values specified by Altera. A representative subset of signal paths is tested to approximate typical device applications.

- (9) Contact Altera Applications for test circuit specifications and test conditions.

- (10) These timing parameters are sample-tested only.

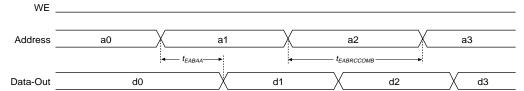

Figures 29 and 30 show the asynchronous and synchronous timing waveforms, respectively, for the EAB macroparameters in Table 34.

Figure 29. EAB Asynchronous Timing Waveforms

## **EAB Asynchronous Read**

## **EAB Asynchronous Write**

| Symbol              | -3 Spee | d Grade | -4 Spee | d Grade | Unit |

|---------------------|---------|---------|---------|---------|------|

|                     | Min     | Max     | Min     | Max     |      |

| $t_{IOD}$           |         | 1.3     |         | 1.6     | ns   |

| t <sub>IOC</sub>    |         | 0.5     |         | 0.7     | ns   |

| t <sub>IOCO</sub>   |         | 0.2     |         | 0.2     | ns   |

| t <sub>IOCOMB</sub> |         | 0.0     |         | 0.0     | ns   |

| t <sub>IOSU</sub>   | 2.8     |         | 3.2     |         | ns   |

| t <sub>IOH</sub>    | 1.0     |         | 1.2     |         | ns   |

| t <sub>IOCLR</sub>  |         | 1.0     |         | 1.2     | ns   |

| t <sub>OD1</sub>    |         | 2.6     |         | 3.5     | ns   |

| $t_{OD2}$           |         | 4.9     |         | 6.4     | ns   |

| $t_{\text{OD3}}$    |         | 6.3     |         | 8.2     | ns   |

| $t_{XZ}$            |         | 4.5     |         | 5.4     | ns   |

| t <sub>ZX1</sub>    |         | 4.5     |         | 5.4     | ns   |

| t <sub>ZX2</sub>    |         | 6.8     |         | 8.3     | ns   |

| t <sub>ZX3</sub>    |         | 8.2     |         | 10.1    | ns   |

| t <sub>INREG</sub>  |         | 6.0     |         | 7.5     | ns   |

| t <sub>IOFD</sub>   |         | 3.1     |         | 3.5     | ns   |

| t <sub>INCOMB</sub> |         | 3.1     |         | 3.5     | ns   |

| Table 45. EPF10K10 & EPF10K20 Device External Timing Parameters         Note (1) |        |          |         |          |      |  |  |  |  |

|----------------------------------------------------------------------------------|--------|----------|---------|----------|------|--|--|--|--|

| Symbol                                                                           | -3 Spe | ed Grade | -4 Spee | ed Grade | Unit |  |  |  |  |

|                                                                                  | Min    | Max      | Min     | Max      |      |  |  |  |  |

| t <sub>DRR</sub>                                                                 |        | 16.1     |         | 20.0     | ns   |  |  |  |  |

| t <sub>INSU</sub> (2), (3)                                                       | 5.5    |          | 6.0     |          | ns   |  |  |  |  |

| t <sub>INH</sub> (3)                                                             | 0.0    |          | 0.0     |          | ns   |  |  |  |  |

| t <sub>оитсо</sub> (3)                                                           | 2.0    | 6.7      | 2.0     | 8.4      | ns   |  |  |  |  |

| Table 46. EPF10K10 Device External Bidirectional Timing Parameters         Note (1) |        |          |         |                |    |  |  |  |  |  |

|-------------------------------------------------------------------------------------|--------|----------|---------|----------------|----|--|--|--|--|--|

| Symbol                                                                              | -3 Spe | ed Grade | -4 Spee | -4 Speed Grade |    |  |  |  |  |  |

|                                                                                     | Min    | Max      | Min     | Max            |    |  |  |  |  |  |

| t <sub>INSUBIDIR</sub>                                                              | 4.5    |          | 5.6     |                | ns |  |  |  |  |  |

| t <sub>INHBIDIR</sub>                                                               | 0.0    |          | 0.0     |                | ns |  |  |  |  |  |

| t <sub>OUTCOBIDIR</sub>                                                             | 2.0    | 6.7      | 2.0     | 8.4            | ns |  |  |  |  |  |

| t <sub>XZBIDIR</sub>                                                                |        | 10.5     |         | 13.4           | ns |  |  |  |  |  |

| t <sub>ZXBIDIR</sub>                                                                |        | 10.5     |         | 13.4           | ns |  |  |  |  |  |

| Symbol                  | -3 Spec | ed Grade | -4 Spee | d Grade | Unit |

|-------------------------|---------|----------|---------|---------|------|

|                         | Min     | Max      | Min     | Max     |      |

| t <sub>INSUBIDIR</sub>  | 4.6     |          | 5.7     |         | ns   |

| t <sub>INHBIDIR</sub>   | 0.0     |          | 0.0     |         | ns   |

| t <sub>OUTCOBIDIR</sub> | 2.0     | 6.7      | 2.0     | 8.4     | ns   |

| t <sub>XZBIDIR</sub>    |         | 10.5     |         | 13.4    | ns   |

| t <sub>ZXBIDIR</sub>    |         | 10.5     |         | 13.4    | ns   |

# Notes to tables:

- All timing parameters are described in Tables 32 through 38 in this data sheet.

Using an LE to register the signal may provide a lower setup time.

This parameter is specified by characterization.

| Symbol                 | -2 Speed Grade |      | -3 Speed Grade |      | -4 Speed Grade |      | Unit |

|------------------------|----------------|------|----------------|------|----------------|------|------|

|                        | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>EABAA</sub>     |                | 12.1 |                | 13.7 |                | 17.0 | ns   |

| t <sub>EABRCCOMB</sub> | 12.1           |      | 13.7           |      | 17.0           |      | ns   |

| t <sub>EABRCREG</sub>  | 8.6            |      | 9.7            |      | 11.9           |      | ns   |

| t <sub>EABWP</sub>     | 5.2            |      | 5.8            |      | 7.2            |      | ns   |

| t <sub>EABWCCOMB</sub> | 6.5            |      | 7.3            |      | 9.0            |      | ns   |

| t <sub>EABWCREG</sub>  | 11.6           |      | 13.0           |      | 16.0           |      | ns   |

| t <sub>EABDD</sub>     |                | 8.8  |                | 10.0 |                | 12.5 | ns   |

| t <sub>EABDATACO</sub> |                | 1.7  |                | 2.0  |                | 3.4  | ns   |

| t <sub>EABDATASU</sub> | 4.7            |      | 5.3            |      | 5.6            |      | ns   |

| t <sub>EABDATAH</sub>  | 0.0            |      | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWESU</sub>   | 4.9            |      | 5.5            |      | 5.8            |      | ns   |

| t <sub>EABWEH</sub>    | 0.0            |      | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWDSU</sub>   | 1.8            |      | 2.1            |      | 2.7            |      | ns   |

| t <sub>EABWDH</sub>    | 0.0            |      | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWASU</sub>   | 4.1            |      | 4.7            |      | 5.8            |      | ns   |

| t <sub>EABWAH</sub>    | 0.0            |      | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWO</sub>     |                | 8.4  |                | 9.5  |                | 11.8 | ns   |

| Symbol                  | -3DX Spe | -3DX Speed Grade |      | -3 Speed Grade |      | d Grade | Unit |  |

|-------------------------|----------|------------------|------|----------------|------|---------|------|--|

|                         | Min      | Max              | Min  | Max            | Min  | Max     |      |  |

| t <sub>EABAA</sub>      |          | 13.7             |      | 13.7           |      | 17.0    | ns   |  |

| t <sub>EABRCCOMB</sub>  | 13.7     |                  | 13.7 |                | 17.0 |         | ns   |  |

| t <sub>EABRCREG</sub>   | 9.7      |                  | 9.7  |                | 11.9 |         | ns   |  |

| t <sub>EABWP</sub>      | 5.8      |                  | 5.8  |                | 7.2  |         | ns   |  |

| t <sub>EABWCCOMB</sub>  | 7.3      |                  | 7.3  |                | 9.0  |         | ns   |  |

| t <sub>EABWCREG</sub>   | 13.0     |                  | 13.0 |                | 16.0 |         | ns   |  |

| t <sub>EABDD</sub>      |          | 10.0             |      | 10.0           |      | 12.5    | ns   |  |

| t <sub>EABDATA</sub> CO |          | 2.0              |      | 2.0            |      | 3.4     | ns   |  |

| t <sub>EABDATASU</sub>  | 5.3      |                  | 5.3  |                | 5.6  |         | ns   |  |

| t <sub>EABDATAH</sub>   | 0.0      |                  | 0.0  |                | 0.0  |         | ns   |  |

| t <sub>EABWESU</sub>    | 5.5      |                  | 5.5  |                | 5.8  |         | ns   |  |

| t <sub>EABWEH</sub>     | 0.0      |                  | 0.0  |                | 0.0  |         | ns   |  |

| t <sub>EABWDSU</sub>    | 5.5      |                  | 5.5  |                | 5.8  |         | ns   |  |

| t <sub>EABWDH</sub>     | 0.0      |                  | 0.0  |                | 0.0  |         | ns   |  |

| t <sub>EABWASU</sub>    | 2.1      |                  | 2.1  |                | 2.7  |         | ns   |  |

| t <sub>EABWAH</sub>     | 0.0      |                  | 0.0  |                | 0.0  |         | ns   |  |

| t <sub>EABWO</sub>      |          | 9.5              |      | 9.5            |      | 11.8    | ns   |  |

| Symbol                                                            | -3DX Spe | ed Grade | -3 Speed Grade |      | -4 Speed Grade |      | Unit |

|-------------------------------------------------------------------|----------|----------|----------------|------|----------------|------|------|

|                                                                   | Min      | Max      | Min            | Max  | Min            | Max  |      |

| t <sub>DIN2IOE</sub>                                              |          | 10.3     |                | 10.3 |                | 12.2 | ns   |

| t <sub>DIN2LE</sub>                                               |          | 4.8      |                | 4.8  |                | 6.0  | ns   |

| t <sub>DIN2DATA</sub>                                             |          | 7.3      |                | 7.3  |                | 11.0 | ns   |

| t <sub>DCLK2IOE</sub> without ClockLock or ClockBoost circuitry   |          | 6.2      |                | 6.2  |                | 7.7  | ns   |

| $t_{DCLK2IOE}$ with ClockLock or ClockBoost circuitry             |          | 2.3      |                | _    |                | _    | ns   |

| t <sub>DCLK2LE</sub> without ClockLock or<br>ClockBoost circuitry |          | 4.8      |                | 4.8  |                | 6.0  | ns   |

| $t_{DCLK2LE}$ with ClockLock or ClockBoost circuitry              |          | 2.3      |                | _    |                | _    | ns   |

| <sup>t</sup> SAMELAB                                              |          | 0.4      |                | 0.4  |                | 0.5  | ns   |

| <sup>t</sup> SAMEROW                                              |          | 4.9      |                | 4.9  |                | 5.5  | ns   |

| <sup>t</sup> SAMECOLUMN                                           |          | 5.1      |                | 5.1  |                | 5.4  | ns   |

| t <sub>DIFFROW</sub>                                              |          | 10.0     |                | 10.0 |                | 10.9 | ns   |

| t <sub>TWOROWS</sub>                                              |          | 14.9     |                | 14.9 |                | 16.4 | ns   |

| t <sub>LEPERIPH</sub>                                             |          | 6.9      |                | 6.9  |                | 8.1  | ns   |

| t <sub>LABCARRY</sub>                                             |          | 0.9      |                | 0.9  |                | 1.1  | ns   |

| t <sub>LABCASC</sub>                                              |          | 3.0      |                | 3.0  |                | 3.2  | ns   |

| Symbol                 | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | Unit |    |

|------------------------|----------------|-----|---------|---------|---------|------|----|

|                        | Min            | Max | Min     | Max     | Min     | Max  |    |

| t <sub>EABDATA1</sub>  |                | 3.3 |         | 3.9     |         | 5.2  | ns |

| t <sub>EABDATA2</sub>  |                | 1.0 |         | 1.3     |         | 1.7  | ns |

| t <sub>EABWE1</sub>    |                | 2.6 |         | 3.1     |         | 4.1  | ns |

| t <sub>EABWE2</sub>    |                | 2.7 |         | 3.2     |         | 4.3  | ns |

| t <sub>EABCLK</sub>    |                | 0.0 |         | 0.0     |         | 0.0  | ns |

| t <sub>EABCO</sub>     |                | 1.2 |         | 1.4     |         | 1.8  | ns |

| t <sub>EABBYPASS</sub> |                | 0.1 |         | 0.2     |         | 0.2  | ns |

| t <sub>EABSU</sub>     | 1.4            |     | 1.7     |         | 2.2     |      | ns |

| t <sub>EABH</sub>      | 0.1            |     | 0.1     |         | 0.1     |      | ns |

| $t_{AA}$               |                | 4.5 |         | 5.4     |         | 7.3  | ns |

| $t_{WP}$               | 2.0            |     | 2.4     |         | 3.2     |      | ns |

| t <sub>WDSU</sub>      | 0.7            |     | 0.8     |         | 1.1     |      | ns |

| t <sub>WDH</sub>       | 0.5            |     | 0.6     |         | 0.7     |      | ns |

| t <sub>WASU</sub>      | 0.6            |     | 0.7     |         | 0.9     |      | ns |

| t <sub>WAH</sub>       | 0.9            |     | 1.1     |         | 1.5     |      | ns |

| $t_{WO}$               |                | 3.3 |         | 3.9     |         | 5.2  | ns |

| $t_{DD}$               |                | 3.3 |         | 3.9     |         | 5.2  | ns |

| t <sub>EABOUT</sub>    |                | 0.1 |         | 0.1     |         | 0.2  | ns |

| t <sub>EABCH</sub>     | 3.0            |     | 3.5     |         | 4.0     |      | ns |

| t <sub>EABCL</sub>     | 3.03           |     | 3.5     |         | 4.0     |      | ns |

| Symbol                   | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |

|--------------------------|----------------|-----|----------------|-----|----------------|-----|------|

|                          | Min            | Max | Min            | Max | Min            | Max |      |

| t <sub>DIN2IOE</sub>     |                | 4.2 |                | 5.0 |                | 6.5 | ns   |

| t <sub>DIN2LE</sub>      |                | 2.2 |                | 2.6 |                | 3.4 | ns   |

| t <sub>DIN2DATA</sub>    |                | 4.3 |                | 5.2 |                | 7.1 | ns   |

| t <sub>DCLK2IOE</sub>    |                | 4.2 |                | 4.9 |                | 6.6 | ns   |

| t <sub>DCLK2LE</sub>     |                | 2.2 |                | 2.6 |                | 3.4 | ns   |

| t <sub>SAMELAB</sub>     |                | 0.1 |                | 0.1 |                | 0.2 | ns   |

| t <sub>SAMEROW</sub>     |                | 2.2 |                | 2.4 |                | 2.9 | ns   |

| t <sub>SAME</sub> COLUMN |                | 0.8 |                | 1.0 |                | 1.4 | ns   |

| t <sub>DIFFROW</sub>     |                | 3.0 |                | 3.4 |                | 4.3 | ns   |

| t <sub>TWOROWS</sub>     |                | 5.2 |                | 5.8 |                | 7.2 | ns   |

| t <sub>LEPERIPH</sub>    |                | 1.8 |                | 2.2 |                | 2.8 | ns   |

| t <sub>LABCARRY</sub>    |                | 0.5 |                | 0.5 |                | 0.7 | ns   |

| t <sub>LABCASC</sub>     |                | 0.9 |                | 1.0 |                | 1.5 | ns   |

| Table 90. EPF10K10A External Reference Timing Parameters Note (1) |                |      |                |      |                |      |      |

|-------------------------------------------------------------------|----------------|------|----------------|------|----------------|------|------|

| Symbol                                                            | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |

|                                                                   | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>DRR</sub>                                                  |                | 10.0 |                | 12.0 |                | 16.0 | ns   |

| t <sub>INSU</sub> (2), (3)                                        | 1.6            |      | 2.1            |      | 2.8            |      | ns   |

| t <sub>INH</sub> (3)                                              | 0.0            |      | 0.0            |      | 0.0            |      | ns   |

| t <sub>outco</sub> (3)                                            | 2.0            | 5.8  | 2.0            | 6.9  | 2.0            | 9.2  | ns   |

| Table 91. EPF10K10A Device External Bidirectional Timing Parameters         Note (1) |         |         |                |     |                |     |      |

|--------------------------------------------------------------------------------------|---------|---------|----------------|-----|----------------|-----|------|

| Symbol                                                                               | -2 Spee | d Grade | -3 Speed Grade |     | -4 Speed Grade |     | Unit |

|                                                                                      | Min     | Max     | Min            | Max | Min            | Max | 1    |

| t <sub>INSUBIDIR</sub>                                                               | 2.4     |         | 3.3            |     | 4.5            |     | ns   |

| t <sub>INHBIDIR</sub>                                                                | 0.0     |         | 0.0            |     | 0.0            |     | ns   |

| toutcobidir                                                                          | 2.0     | 5.8     | 2.0            | 6.9 | 2.0            | 9.2 | ns   |

| t <sub>XZBIDIR</sub>                                                                 |         | 6.3     |                | 7.5 |                | 9.9 | ns   |

| t <sub>ZXBIDIR</sub>                                                                 |         | 6.3     |                | 7.5 |                | 9.9 | ns   |

### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

Tables 99 through 105 show EPF10K100A device internal and external timing parameters.

| Symbol              | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit    |

|---------------------|----------------|-----|----------------|-----|----------------|-----|---------|

|                     | Min            | Max | Min            | Max | Min            | Max | - Oilin |

| $t_{LUT}$           |                | 1.0 |                | 1.2 |                | 1.4 | ns      |

| t <sub>CLUT</sub>   |                | 0.8 |                | 0.9 |                | 1.1 | ns      |

| t <sub>RLUT</sub>   |                | 1.4 |                | 1.6 |                | 1.9 | ns      |

| t <sub>PACKED</sub> |                | 0.4 |                | 0.5 |                | 0.5 | ns      |

| $t_{EN}$            |                | 0.6 |                | 0.7 |                | 0.8 | ns      |

| t <sub>CICO</sub>   |                | 0.2 |                | 0.2 |                | 0.3 | ns      |

| t <sub>CGEN</sub>   |                | 0.4 |                | 0.4 |                | 0.6 | ns      |

| t <sub>CGENR</sub>  |                | 0.6 |                | 0.7 |                | 0.8 | ns      |

| t <sub>CASC</sub>   |                | 0.7 |                | 0.9 |                | 1.0 | ns      |

| t <sub>C</sub>      |                | 0.9 |                | 1.0 |                | 1.2 | ns      |

| t <sub>CO</sub>     |                | 0.2 |                | 0.3 |                | 0.3 | ns      |

| t <sub>COMB</sub>   |                | 0.6 |                | 0.7 |                | 0.8 | ns      |

| $t_{SU}$            | 0.8            |     | 1.0            |     | 1.2            |     | ns      |

| t <sub>H</sub>      | 0.3            |     | 0.5            |     | 0.5            |     | ns      |

| t <sub>PRE</sub>    |                | 0.3 |                | 0.3 |                | 0.4 | ns      |

| t <sub>CLR</sub>    |                | 0.3 |                | 0.3 |                | 0.4 | ns      |

| t <sub>CH</sub>     | 2.5            |     | 3.5            |     | 4.0            |     | ns      |

| $t_{CL}$            | 2.5            |     | 3.5            |     | 4.0            |     | ns      |

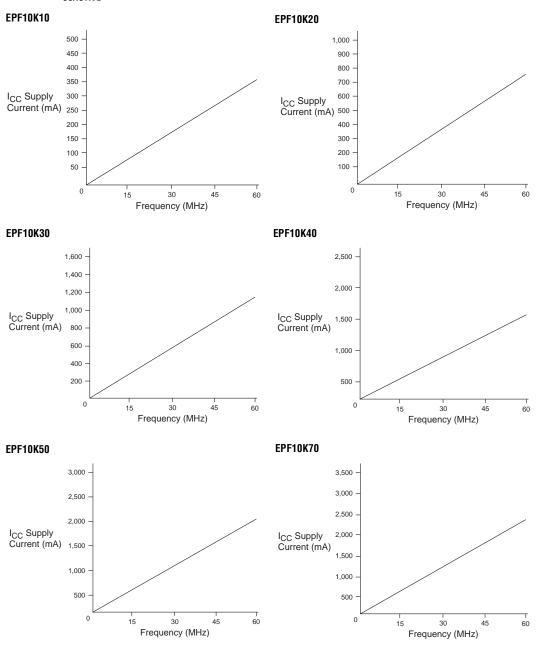

$f_{MAX}$  = Maximum operating frequency in MHz

N = Total number of logic cells used in the device

tog<sub>LC</sub> = Average percent of logic cells toggling at each clock

(typically 12.5%)

K = Constant, shown in Tables 114 and 115

| Table 114. FLEX 10K K Constant Values |         |  |  |  |  |

|---------------------------------------|---------|--|--|--|--|

| Device                                | K Value |  |  |  |  |

| EPF10K10                              | 82      |  |  |  |  |

| EPF10K20                              | 89      |  |  |  |  |

| EPF10K30                              | 88      |  |  |  |  |

| EPF10K40                              | 92      |  |  |  |  |

| EPF10K50                              | 95      |  |  |  |  |

| EPF10K70                              | 85      |  |  |  |  |

| EPF10K100                             | 88      |  |  |  |  |

| Table 115. FLEX 10KA K Constant Values |         |  |  |  |  |

|----------------------------------------|---------|--|--|--|--|

| Device                                 | K Value |  |  |  |  |

| EPF10K10A                              | 17      |  |  |  |  |

| EPF10K30A                              | 17      |  |  |  |  |

| EPF10K50V                              | 19      |  |  |  |  |

| EPF10K100A                             | 19      |  |  |  |  |

| EPF10K130V                             | 22      |  |  |  |  |

| EPF10K250A                             | 23      |  |  |  |  |

This calculation provides an  $I_{CC}$  estimate based on typical conditions with no output load. The actual  $I_{CC}$  should be verified during operation because this measurement is sensitive to the actual pattern in the device and the environmental operating conditions.

To better reflect actual designs, the power model (and the constant *K* in the power calculation equations) for continuous interconnect FLEX devices assumes that logic cells drive FastTrack Interconnect channels. In contrast, the power model of segmented FPGAs assumes that all logic cells drive only one short interconnect segment. This assumption may lead to inaccurate results, compared to measured power consumption for an actual design in a segmented interconnect FPGA.

Figure 32 shows the relationship between the current and operating frequency of FLEX 10K devices.

Figure 32. I<sub>CCACTIVE</sub> vs. Operating Frequency (Part 1 of 3)