Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 216                                                          |

| Number of Logic Elements/Cells | 1728                                                         |

| Total RAM Bits                 | 12288                                                        |

| Number of I/O                  | 102                                                          |

| Number of Gates                | 69000                                                        |

| Voltage - Supply               | 3V ~ 3.6V                                                    |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 70°C (TA)                                              |

| Package / Case                 | 144-LQFP                                                     |

| Supplier Device Package        | 144-TQFP (20x20)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k30atc144-2n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

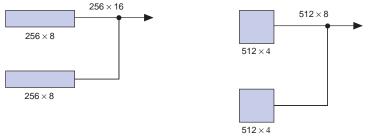

Larger blocks of RAM are created by combining multiple EABs. For example, two  $256 \times 8$  RAM blocks can be combined to form a  $256 \times 16$  RAM block; two  $512 \times 4$  blocks of RAM can be combined to form a  $512 \times 8$  RAM block. See Figure 3.

Figure 3. Examples of Combining EABs

If necessary, all EABs in a device can be cascaded to form a single RAM block. EABs can be cascaded to form RAM blocks of up to 2,048 words without impacting timing. Altera's software automatically combines EABs to meet a designer's RAM specifications.

EABs provide flexible options for driving and controlling clock signals. Different clocks can be used for the EAB inputs and outputs. Registers can be independently inserted on the data input, EAB output, or the address and WE inputs. The global signals and the EAB local interconnect can drive the WE signal. The global signals, dedicated clock pins, and EAB local interconnect can drive the EAB clock signals. Because the LEs drive the EAB local interconnect, the LEs can control the WE signal or the EAB clock signals.

Each EAB is fed by a row interconnect and can drive out to row and column interconnects. Each EAB output can drive up to two row channels and up to two column channels; the unused row channel can be driven by other LEs. This feature increases the routing resources available for EAB outputs. See Figure 4.

Dedicated Inputs & Global Signals Chip-Wide Reset Row Interconnect 2, 4, 8, 16 Data Data Out 8, 4, 2, 1 2, 4, 8, 16 Address D 8, 9, 10, 11 RAM/ROM  $256 \times 8$ 512 × 4  $1,024 \times 2$ Column 2,048 × 1 Interconnect WE D

Figure 4. FLEX 10K Embedded Array Block

#### Note:

EAB Local Interconnect (1)

(1) EPF10K10, EPF10K10A, EPF10K20, EPF10K30, EPF10K30A, EPF10K40, EPF10K50, and EPF10K50V devices have 22 EAB local interconnect channels; EPF10K70, EPF10K100, EPF10K100A, EPF10K130V, and EPF10K250A devices have 26.

The programmable flipflop in the LE can be configured for D, T, JK, or SR operation. The clock, clear, and preset control signals on the flipflop can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the flipflop is bypassed and the output of the LUT drives the output of the LE.

The LE has two outputs that drive the interconnect; one drives the local interconnect and the other drives either the row or column FastTrack Interconnect. The two outputs can be controlled independently. For example, the LUT can drive one output while the register drives the other output. This feature, called register packing, can improve LE utilization because the register and the LUT can be used for unrelated functions.

The FLEX 10K architecture provides two types of dedicated high-speed data paths that connect adjacent LEs without using local interconnect paths: carry chains and cascade chains. The carry chain supports high-speed counters and adders; the cascade chain implements wide-input functions with minimum delay. Carry and cascade chains connect all LEs in an LAB and all LABs in the same row. Intensive use of carry and cascade chains can reduce routing flexibility. Therefore, the use of these chains should be limited to speed-critical portions of a design.

#### Carry Chain

The carry chain provides a very fast (as low as 0.2 ns) carry-forward function between LEs. The carry-in signal from a lower-order bit drives forward into the higher-order bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the FLEX 10K architecture to implement high-speed counters, adders, and comparators of arbitrary width efficiently. Carry chain logic can be created automatically by the Compiler during design processing, or manually by the designer during design entry. Parameterized functions such as LPM and DesignWare functions automatically take advantage of carry chains.

Carry chains longer than eight LEs are automatically implemented by linking LABs together. For enhanced fitting, a long carry chain skips alternate LABs in a row. A carry chain longer than one LAB skips either from even-numbered LAB to even-numbered LAB, or from odd-numbered LAB to odd-numbered LAB. For example, the last LE of the first LAB in a row carries to the first LE of the third LAB in the row. The carry chain does not cross the EAB at the middle of the row. For instance, in the EPF10K50 device, the carry chain stops at the eighteenth LAB and a new one begins at the nineteenth LAB.

#### FastTrack Interconnect

In the FLEX 10K architecture, connections between LEs and device I/O pins are provided by the FastTrack Interconnect, which is a series of continuous horizontal and vertical routing channels that traverse the device. This global routing structure provides predictable performance, even in complex designs. In contrast, the segmented routing in FPGAs requires switch matrices to connect a variable number of routing paths, increasing the delays between logic resources and reducing performance.

The FastTrack Interconnect consists of row and column interconnect channels that span the entire device. Each row of LABs is served by a dedicated row interconnect. The row interconnect can drive I/O pins and feed other LABs in the device. The column interconnect routes signals between rows and can drive I/O pins.

A row channel can be driven by an LE or by one of three column channels. These four signals feed dual 4-to-1 multiplexers that connect to two specific row channels. These multiplexers, which are connected to each LE, allow column channels to drive row channels even when all eight LEs in an LAB drive the row interconnect.

Each column of LABs is served by a dedicated column interconnect. The column interconnect can then drive I/O pins or another row's interconnect to route the signals to other LABs in the device. A signal from the column interconnect, which can be either the output of an LE or an input from an I/O pin, must be routed to the row interconnect before it can enter an LAB or EAB. Each row channel that is driven by an IOE or EAB can drive one specific column channel.

Access to row and column channels can be switched between LEs in adjacent pairs of LABs. For example, an LE in one LAB can drive the row and column channels normally driven by a particular LE in the adjacent LAB in the same row, and vice versa. This routing flexibility enables routing resources to be used more efficiently. See Figure 11.

Each IOE selects the clock, clear, clock enable, and output enable controls from a network of I/O control signals called the peripheral control bus. The peripheral control bus uses high-speed drivers to minimize signal skew across devices; it provides up to 12 peripheral control signals that can be allocated as follows:

- Up to eight output enable signals

- Up to six clock enable signals

- Up to two clock signals

- Up to two clear signals

If more than six clock enable or eight output enable signals are required, each IOE on the device can be controlled by clock enable and output enable signals driven by specific LEs. In addition to the two clock signals available on the peripheral control bus, each IOE can use one of two dedicated clock pins. Each peripheral control signal can be driven by any of the dedicated input pins or the first LE of each LAB in a particular row. In addition, an LE in a different row can drive a column interconnect, which causes a row interconnect to drive the peripheral control signal. The chip-wide reset signal will reset all IOE registers, overriding any other control signals.

Tables 8 and 9 list the sources for each peripheral control signal, and the rows that can drive global signals. These tables also show how the output enable, clock enable, clock, and clear signals share 12 peripheral control signals.

| Table 8. EPF10K10, EPF10K20, | Table 8. EPF10K10, EPF10K20, EPF10K30, EPF10K40 & EPF10K50 Peripheral Bus Sources |          |                       |          |                       |  |  |  |  |

|------------------------------|-----------------------------------------------------------------------------------|----------|-----------------------|----------|-----------------------|--|--|--|--|

| Peripheral<br>Control Signal | EPF10K10<br>EPF10K10A                                                             | EPF10K20 | EPF10K30<br>EPF10K30A | EPF10K40 | EPF10K50<br>EPF10K50V |  |  |  |  |

| OE0                          | Row A                                                                             | Row A    | Row A                 | Row A    | Row A                 |  |  |  |  |

| OE1                          | Row A                                                                             | Row B    | Row B                 | Row C    | Row B                 |  |  |  |  |

| OE2                          | Row B                                                                             | Row C    | Row C                 | Row D    | Row D                 |  |  |  |  |

| OE3                          | Row B                                                                             | Row D    | Row D                 | Row E    | Row F                 |  |  |  |  |

| OE4                          | Row C                                                                             | Row E    | Row E                 | Row F    | Row H                 |  |  |  |  |

| OE5                          | Row C                                                                             | Row F    | Row F                 | Row G    | Row J                 |  |  |  |  |

| CLKENA0/CLK0/GLOBAL0         | Row A                                                                             | Row A    | Row A                 | Row B    | Row A                 |  |  |  |  |

| CLKENA1/OE6/GLOBAL1          | Row A                                                                             | Row B    | Row B                 | Row C    | Row C                 |  |  |  |  |

| CLKENA2/CLR0                 | Row B                                                                             | Row C    | Row C                 | Row D    | Row E                 |  |  |  |  |

| CLKENA3/OE7/GLOBAL2          | Row B                                                                             | Row D    | Row D                 | Row E    | Row G                 |  |  |  |  |

| CLKENA4/CLR1                 | Row C                                                                             | Row E    | Row E                 | Row F    | Row I                 |  |  |  |  |

| CLKENA5/CLK1/GLOBAL3         | Row C                                                                             | Row F    | Row F                 | Row H    | Row J                 |  |  |  |  |

| Peripheral<br>Control Signal | EPF10K70 | EPF10K100<br>EPF10K100A | EPF10K130V | EPF10K250A |

|------------------------------|----------|-------------------------|------------|------------|

| OE 0                         | Row A    | Row A                   | Row C      | Row E      |

| OE1                          | Row B    | Row C                   | Row E      | Row G      |

| OE2                          | Row D    | Row E                   | Row G      | Row I      |

| OE3                          | Row I    | Row L                   | Row N      | Row P      |

| OE 4                         | Row G    | Row I                   | Row K      | Row M      |

| OE5                          | Row H    | Row K                   | Row M      | Row O      |

| CLKENA0/CLK0/GLOBAL0         | Row E    | Row F                   | Row H      | Row J      |

| CLKENA1/OE6/GLOBAL1          | Row C    | Row D                   | Row F      | Row H      |

| CLKENA2/CLR0                 | Row B    | Row B                   | Row D      | Row F      |

| CLKENA3/OE7/GLOBAL2          | Row F    | Row H                   | Row J      | Row L      |

| CLKENA4/CLR1                 | Row H    | Row J                   | Row L      | Row N      |

| CLKENA5/CLK1/GLOBAL3         | Row E    | Row G                   | Row I      | Row K      |

| Table 15. 32-Bit FLEX 10K Device IDCODE Note (1) |                     |                          |                                      |                  |  |  |  |  |

|--------------------------------------------------|---------------------|--------------------------|--------------------------------------|------------------|--|--|--|--|

| Device                                           |                     | IDCODE (3                | 2 Bits)                              |                  |  |  |  |  |

|                                                  | Version<br>(4 Bits) | Part Number<br>(16 Bits) | Manufacturer's Identity<br>(11 Bits) | 1 (1 Bit)<br>(2) |  |  |  |  |

| EPF10K10, EPF10K10A                              | 0000                | 0001 0000 0001 0000      | 00001101110                          | 1                |  |  |  |  |

| EPF10K20                                         | 0000                | 0001 0000 0010 0000      | 00001101110                          | 1                |  |  |  |  |

| EPF10K30, EPF10K30A                              | 0000                | 0001 0000 0011 0000      | 00001101110                          | 1                |  |  |  |  |

| EPF10K40                                         | 0000                | 0001 0000 0100 0000      | 00001101110                          | 1                |  |  |  |  |

| EPF10K50, EPF10K50V                              | 0000                | 0001 0000 0101 0000      | 00001101110                          | 1                |  |  |  |  |

| EPF10K70                                         | 0000                | 0001 0000 0111 0000      | 00001101110                          | 1                |  |  |  |  |

| EPF10K100, EPF10K100A                            | 0000                | 0000 0001 0000 0000      | 00001101110                          | 1                |  |  |  |  |

| EPF10K130V                                       | 0000                | 0000 0001 0011 0000      | 00001101110                          | 1                |  |  |  |  |

| EPF10K250A                                       | 0000                | 0000 0010 0101 0000      | 00001101110                          | 1                |  |  |  |  |

#### Notes:

- (1) The most significant bit (MSB) is on the left.

- (2) The least significant bit (LSB) for all JTAG IDCODEs is 1.

FLEX 10K devices include weak pull-ups on JTAG pins.

For more information, see the following documents:

- Application Note 39 (IEEE 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices)

- BitBlaster Serial Download Cable Data Sheet

- ByteBlasterMV Parallel Port Download Cable Data Sheet

- Jam Programming & Test Language Specification

### **Generic Testing**

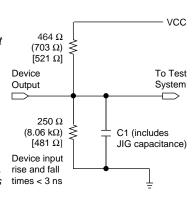

Each FLEX 10K device is functionally tested. Complete testing of each configurable SRAM bit and all logic functionality ensures 100% yield. AC test measurements for FLEX 10K devices are made under conditions equivalent to those shown in Figure 19. Multiple test patterns can be used to configure devices during all stages of the production flow.

#### Figure 19. FLEX 10K AC Test Conditions

Power supply transients can affect AC measurements. Simultaneous transitions of multiple outputs should be avoided for accurate measurement. Threshold tests must not be performed under AC conditions. Large-amplitude, fast-ground-current transients normally occur as the device outputs discharge the load capacitances. When these transients flow through the parasitic inductance between the device ground pin and the test system ground, significant reductions in observable noise immunity can result. Numbers without parentheses are for 5.0-V devices or outputs. Numbers in parentheses are for 3.3-V devices or outputs. Numbers in brackets are for 2.5-V devices or outputs.

# Operating Conditions

Tables 17 through 21 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 5.0-V FLEX 10K devices.

| Table 17. FLEX 10K 5.0-V Device Absolute Maximum Ratings     Note (1) |                            |                              |      |     |      |  |  |

|-----------------------------------------------------------------------|----------------------------|------------------------------|------|-----|------|--|--|

| Symbol                                                                | Parameter                  | Conditions                   | Min  | Max | Unit |  |  |

| V <sub>CC</sub>                                                       | Supply voltage             | With respect to ground (2)   | -2.0 | 7.0 | V    |  |  |

| V <sub>I</sub>                                                        | DC input voltage           |                              | -2.0 | 7.0 | V    |  |  |

| I <sub>OUT</sub>                                                      | DC output current, per pin |                              | -25  | 25  | mA   |  |  |

| T <sub>STG</sub>                                                      | Storage temperature        | No bias                      | -65  | 150 | ° C  |  |  |

| T <sub>AMB</sub>                                                      | Ambient temperature        | Under bias                   | -65  | 135 | ° C  |  |  |

| T <sub>J</sub>                                                        | Junction temperature       | Ceramic packages, under bias |      | 150 | ° C  |  |  |

|                                                                       |                            | PQFP, TQFP, RQFP, and BGA    |      | 135 | ° C  |  |  |

|                                                                       |                            | packages, under bias         |      |     |      |  |  |

| Table 1            | Table 18. FLEX 10K 5.0-V Device Recommended Operating Conditions |                    |             |                          |      |  |  |  |

|--------------------|------------------------------------------------------------------|--------------------|-------------|--------------------------|------|--|--|--|

| Symbol             | Parameter                                                        | Conditions         | Min         | Max                      | Unit |  |  |  |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers              | (3), (4)           | 4.75 (4.50) | 5.25 (5.50)              | V    |  |  |  |

| V <sub>CCIO</sub>  | Supply voltage for output buffers, 5.0-V operation               | (3), (4)           | 4.75 (4.50) | 5.25 (5.50)              | V    |  |  |  |

|                    | Supply voltage for output buffers, 3.3-V operation               | (3), (4)           | 3.00 (3.00) | 3.60 (3.60)              | V    |  |  |  |

| VI                 | Input voltage                                                    |                    | -0.5        | V <sub>CCINT</sub> + 0.5 | V    |  |  |  |

| Vo                 | Output voltage                                                   |                    | 0           | V <sub>CCIO</sub>        | V    |  |  |  |

| T <sub>A</sub>     | Ambient temperature                                              | For commercial use | 0           | 70                       | °C   |  |  |  |

|                    |                                                                  | For industrial use | -40         | 85                       | °C   |  |  |  |

| T <sub>J</sub>     | Operating temperature                                            | For commercial use | 0           | 85                       | °C   |  |  |  |

|                    |                                                                  | For industrial use | -40         | 100                      | °C   |  |  |  |

| t <sub>R</sub>     | Input rise time                                                  |                    |             | 40                       | ns   |  |  |  |

| t <sub>F</sub>     | Input fall time                                                  |                    |             | 40                       | ns   |  |  |  |

| Symbol                   | Parameter                                                                                                            | Conditions |

|--------------------------|----------------------------------------------------------------------------------------------------------------------|------------|

| t <sub>DIN2IOE</sub>     | Delay from dedicated input pin to IOE control input                                                                  | (7)        |

| t <sub>DCLK2LE</sub>     | Delay from dedicated clock pin to LE or EAB clock                                                                    | (7)        |

| t <sub>DIN2DATA</sub>    | Delay from dedicated input or clock to LE or EAB data                                                                | (7)        |

| t <sub>DCLK2IOE</sub>    | Delay from dedicated clock pin to IOE clock                                                                          | (7)        |

| t <sub>DIN2LE</sub>      | Delay from dedicated input pin to LE or EAB control input                                                            | (7)        |

| t <sub>SAMELAB</sub>     | Routing delay for an LE driving another LE in the same LAB                                                           |            |

| t <sub>SAMEROW</sub>     | Routing delay for a row IOE, LE, or EAB driving a row IOE, LE, or EAB in the same row                                | (7)        |

| t <sub>SAME</sub> COLUMN | Routing delay for an LE driving an IOE in the same column                                                            | (7)        |

| t <sub>DIFFROW</sub>     | Routing delay for a column IOE, LE, or EAB driving an LE or EAB in a different row                                   | (7)        |

| t <sub>TWOROWS</sub>     | Routing delay for a row IOE or EAB driving an LE or EAB in a different row                                           | (7)        |

| t <sub>LEPERIPH</sub>    | Routing delay for an LE driving a control signal of an IOE via the peripheral control bus                            | (7)        |

| t <sub>LABCARRY</sub>    | Routing delay for the carry-out signal of an LE driving the carry-in signal of a different LE in a different LAB     |            |

| t <sub>LABCASC</sub>     | Routing delay for the cascade-out signal of an LE driving the cascade-in signal of a different LE in a different LAB |            |

| Table 37. Ex       |                                                                                                |            |

|--------------------|------------------------------------------------------------------------------------------------|------------|

| Symbol             | Parameter                                                                                      | Conditions |

| t <sub>DRR</sub>   | Register-to-register delay via four LEs, three row interconnects, and four local interconnects | (9)        |

| t <sub>INSU</sub>  | Setup time with global clock at IOE register                                                   |            |

| t <sub>INH</sub>   | Hold time with global clock at IOE register                                                    |            |

| t <sub>OUTCO</sub> | Clock-to-output delay with global clock at IOE register                                        |            |

| Table 38. External Bidirectional Timing Parameters       Note (10) |                                                                                |  |  |  |  |  |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol                                                             | Condition                                                                      |  |  |  |  |  |

| t <sub>INSUBIDIR</sub>                                             | Setup time for bidirectional pins with global clock at adjacent LE register    |  |  |  |  |  |

| t <sub>INHBIDIR</sub>                                              | Hold time for bidirectional pins with global clock at adjacent LE register     |  |  |  |  |  |

| t <sub>OUTCOBIDIR</sub>                                            | Clock-to-output delay for bidirectional pins with global clock at IOE register |  |  |  |  |  |

| t <sub>XZBIDIR</sub>                                               | Synchronous IOE output buffer disable delay                                    |  |  |  |  |  |

| t <sub>ZXBIDIR</sub>                                               | Synchronous IOE output buffer enable delay, slow slew rate = off               |  |  |  |  |  |

| Table 66. EPF10K100 Device EAB Internal Microparameters       Note (1) |          |                  |     |         |         |      |    |  |

|------------------------------------------------------------------------|----------|------------------|-----|---------|---------|------|----|--|

| Symbol                                                                 | -3DX Spe | -3DX Speed Grade |     | d Grade | -4 Spee | Unit |    |  |

|                                                                        | Min      | Max              | Min | Max     | Min     | Max  |    |  |

| t <sub>EABDATA1</sub>                                                  |          | 1.5              |     | 1.5     |         | 1.9  | ns |  |

| t <sub>EABDATA2</sub>                                                  |          | 4.8              |     | 4.8     |         | 6.0  | ns |  |

| t <sub>EABWE1</sub>                                                    |          | 1.0              |     | 1.0     |         | 1.2  | ns |  |

| t <sub>EABWE2</sub>                                                    |          | 5.0              |     | 5.0     |         | 6.2  | ns |  |

| t <sub>EABCLK</sub>                                                    |          | 1.0              |     | 1.0     |         | 2.2  | ns |  |

| t <sub>EABCO</sub>                                                     |          | 0.5              |     | 0.5     |         | 0.6  | ns |  |

| t <sub>EABBYPASS</sub>                                                 |          | 1.5              |     | 1.5     |         | 1.9  | ns |  |

| t <sub>EABSU</sub>                                                     | 1.5      |                  | 1.5 |         | 1.8     |      | ns |  |

| t <sub>EABH</sub>                                                      | 2.0      |                  | 2.0 |         | 2.5     |      | ns |  |

| $t_{AA}$                                                               |          | 8.7              |     | 8.7     |         | 10.7 | ns |  |

| $t_{WP}$                                                               | 5.8      |                  | 5.8 |         | 7.2     |      | ns |  |

| t <sub>WDSU</sub>                                                      | 1.6      |                  | 1.6 |         | 2.0     |      | ns |  |

| t <sub>WDH</sub>                                                       | 0.3      |                  | 0.3 |         | 0.4     |      | ns |  |

| t <sub>WASU</sub>                                                      | 0.5      |                  | 0.5 |         | 0.6     |      | ns |  |

| t <sub>WAH</sub>                                                       | 1.0      |                  | 1.0 |         | 1.2     |      | ns |  |

| $t_{WO}$                                                               |          | 5.0              |     | 5.0     |         | 6.2  | ns |  |

| $t_{DD}$                                                               |          | 5.0              |     | 5.0     |         | 6.2  | ns |  |

| t <sub>EABOUT</sub>                                                    |          | 0.5              |     | 0.5     |         | 0.6  | ns |  |

| t <sub>EABCH</sub>                                                     | 4.0      |                  | 4.0 |         | 4.0     |      | ns |  |

| t <sub>EABCL</sub>                                                     | 5.8      |                  | 5.8 |         | 7.2     |      | ns |  |

| Table 72. EPF10K50V Device IOE Timing Microparameters       Note (1) |         |          |         |                |     |                |     |                |    |

|----------------------------------------------------------------------|---------|----------|---------|----------------|-----|----------------|-----|----------------|----|

| Symbol                                                               | -1 Spec | ed Grade | -2 Spee | -2 Speed Grade |     | -3 Speed Grade |     | -4 Speed Grade |    |

|                                                                      | Min     | Max      | Min     | Max            | Min | Max            | Min | Max            |    |

| $t_{IOD}$                                                            |         | 1.2      |         | 1.6            |     | 1.9            |     | 2.1            | ns |

| $t_{IOC}$                                                            |         | 0.3      |         | 0.4            |     | 0.5            |     | 0.5            | ns |

| t <sub>IOCO</sub>                                                    |         | 0.3      |         | 0.3            |     | 0.4            |     | 0.4            | ns |

| t <sub>IOCOMB</sub>                                                  |         | 0.0      |         | 0.0            |     | 0.0            |     | 0.0            | ns |

| $t_{IOSU}$                                                           | 2.8     |          | 2.8     |                | 3.4 |                | 3.9 |                | ns |

| t <sub>IOH</sub>                                                     | 0.7     |          | 0.8     |                | 1.0 |                | 1.4 |                | ns |

| t <sub>IOCLR</sub>                                                   |         | 0.5      |         | 0.6            |     | 0.7            |     | 0.7            | ns |

| t <sub>OD1</sub>                                                     |         | 2.8      |         | 3.2            |     | 3.9            |     | 4.7            | ns |

| t <sub>OD2</sub>                                                     |         | _        |         | _              |     | _              |     | _              | ns |

| t <sub>OD3</sub>                                                     |         | 6.5      |         | 6.9            |     | 7.6            |     | 8.4            | ns |

| $t_{XZ}$                                                             |         | 2.8      |         | 3.1            |     | 3.8            |     | 4.6            | ns |

| $t_{ZX1}$                                                            |         | 2.8      |         | 3.1            |     | 3.8            |     | 4.6            | ns |

| $t_{ZX2}$                                                            |         | _        |         | _              |     | _              |     | _              | ns |

| $t_{ZX3}$                                                            |         | 6.5      |         | 6.8            |     | 7.5            |     | 8.3            | ns |

| t <sub>INREG</sub>                                                   |         | 5.0      |         | 5.7            |     | 7.0            |     | 9.0            | ns |

| t <sub>IOFD</sub>                                                    |         | 1.5      |         | 1.9            |     | 2.3            |     | 2.7            | ns |

| t <sub>INCOMB</sub>                                                  |         | 1.5      |         | 1.9            |     | 2.3            |     | 2.7            | ns |

| • • • •                | 1.0     |         |         |         |        |          |         |          |      |

|------------------------|---------|---------|---------|---------|--------|----------|---------|----------|------|

| Symbol                 | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spe | ed Grade | -4 Spee | ed Grade | Unit |

|                        | Min     | Max     | Min     | Max     | Min    | Max      | Min     | Max      |      |

| t <sub>EABDATA1</sub>  |         | 1.7     |         | 2.8     |        | 3.4      |         | 4.6      | ns   |

| t <sub>EABDATA2</sub>  |         | 4.9     |         | 3.9     |        | 4.8      |         | 5.9      | ns   |

| t <sub>EABWE1</sub>    |         | 0.0     |         | 2.5     |        | 3.0      |         | 3.7      | ns   |

| t <sub>EABWE2</sub>    |         | 4.0     |         | 4.1     |        | 5.0      |         | 6.2      | ns   |

| t <sub>EABCLK</sub>    |         | 0.4     |         | 0.8     |        | 1.0      |         | 1.2      | ns   |

| t <sub>EABCO</sub>     |         | 0.1     |         | 0.2     |        | 0.3      |         | 0.4      | ns   |

| t <sub>EABBYPASS</sub> |         | 0.9     |         | 1.1     |        | 1.3      |         | 1.6      | ns   |

| t <sub>EABSU</sub>     | 0.8     |         | 1.5     |         | 1.8    |          | 2.2     |          | ns   |

| t <sub>EABH</sub>      | 0.8     |         | 1.6     |         | 2.0    |          | 2.5     |          | ns   |

| $t_{AA}$               |         | 5.5     |         | 8.2     |        | 10.0     |         | 12.4     | ns   |

| $t_{WP}$               | 6.0     |         | 4.9     |         | 6.0    |          | 7.4     |          | ns   |

| t <sub>WDSU</sub>      | 0.1     |         | 0.8     |         | 1.0    |          | 1.2     |          | ns   |

| t <sub>WDH</sub>       | 0.1     |         | 0.2     |         | 0.3    |          | 0.4     |          | ns   |

| t <sub>WASU</sub>      | 0.1     |         | 0.4     |         | 0.5    |          | 0.6     |          | ns   |

| t <sub>WAH</sub>       | 0.1     |         | 0.8     |         | 1.0    |          | 1.2     |          | ns   |

| $t_{WO}$               |         | 2.8     |         | 4.3     |        | 5.3      |         | 6.5      | ns   |

| $t_{DD}$               |         | 2.8     |         | 4.3     |        | 5.3      |         | 6.5      | ns   |

| t <sub>EABOUT</sub>    |         | 0.5     |         | 0.4     |        | 0.5      |         | 0.6      | ns   |

| t <sub>EABCH</sub>     | 2.0     |         | 4.0     |         | 4.0    |          | 4.0     |          | ns   |

| t <sub>EABCL</sub>     | 6.0     |         | 4.9     |         | 6.0    |          | 7.4     |          | ns   |

| Symbol              | -2 Spee | d Grade | -3 Speed Grade |      | -4 Speed Grade |      | Unit |

|---------------------|---------|---------|----------------|------|----------------|------|------|

|                     | Min     | Max     | Min            | Max  | Min            | Max  |      |

| $t_{IOD}$           |         | 1.3     |                | 1.6  |                | 2.0  | ns   |

| t <sub>IOC</sub>    |         | 0.4     |                | 0.5  |                | 0.7  | ns   |

| t <sub>IOCO</sub>   |         | 0.3     |                | 0.4  |                | 0.5  | ns   |

| $t_{IOCOMB}$        |         | 0.0     |                | 0.0  |                | 0.0  | ns   |

| $t_{IOSU}$          | 2.6     |         | 3.3            |      | 3.8            |      | ns   |

| $t_{IOH}$           | 0.0     |         | 0.0            |      | 0.0            |      | ns   |

| t <sub>IOCLR</sub>  |         | 1.7     |                | 2.2  |                | 2.7  | ns   |

| $t_{\text{OD1}}$    |         | 3.5     |                | 4.4  |                | 5.0  | ns   |

| $t_{OD2}$           |         | -       |                | -    |                | -    | ns   |

| $t_{OD3}$           |         | 8.2     |                | 8.1  |                | 9.7  | ns   |

| $t_{XZ}$            |         | 4.9     |                | 6.3  |                | 7.4  | ns   |

| $t_{ZX1}$           |         | 4.9     |                | 6.3  |                | 7.4  | ns   |

| $t_{ZX2}$           |         | _       |                | -    |                | _    | ns   |

| $t_{ZX3}$           |         | 9.6     |                | 10.0 |                | 12.1 | ns   |

| t <sub>INREG</sub>  |         | 7.9     |                | 10.0 |                | 12.6 | ns   |

| $t_{IOFD}$          |         | 6.2     |                | 7.9  |                | 9.9  | ns   |

| t <sub>INCOMB</sub> |         | 6.2     |                | 7.9  |                | 9.9  | ns   |

| Symbol                 | -1 Spee | d Grade | -2 Spee | d Grade | -3 Speed Grade |     | Unit |

|------------------------|---------|---------|---------|---------|----------------|-----|------|

|                        | Min     | Max     | Min     | Max     | Min            | Max |      |

| t <sub>EABDATA1</sub>  |         | 5.5     |         | 6.5     |                | 8.5 | ns   |

| t <sub>EABDATA2</sub>  |         | 1.1     |         | 1.3     |                | 1.8 | ns   |

| t <sub>EABWE1</sub>    |         | 2.4     |         | 2.8     |                | 3.7 | ns   |

| t <sub>EABWE2</sub>    |         | 2.1     |         | 2.5     |                | 3.2 | ns   |

| t <sub>EABCLK</sub>    |         | 0.0     |         | 0.0     |                | 0.2 | ns   |

| t <sub>EABCO</sub>     |         | 1.7     |         | 2.0     |                | 2.6 | ns   |

| t <sub>EABBYPASS</sub> |         | 0.0     |         | 0.0     |                | 0.3 | ns   |

| t <sub>EABSU</sub>     | 1.2     |         | 1.4     |         | 1.9            |     | ns   |

| t <sub>EABH</sub>      | 0.1     |         | 0.1     |         | 0.3            |     | ns   |

| t <sub>AA</sub>        |         | 4.2     |         | 5.0     |                | 6.5 | ns   |

| $t_{WP}$               | 3.8     |         | 4.5     |         | 5.9            |     | ns   |

| t <sub>WDSU</sub>      | 0.1     |         | 0.1     |         | 0.2            |     | ns   |

| t <sub>WDH</sub>       | 0.1     |         | 0.1     |         | 0.2            |     | ns   |

| t <sub>WASU</sub>      | 0.1     |         | 0.1     |         | 0.2            |     | ns   |

| t <sub>WAH</sub>       | 0.1     |         | 0.1     |         | 0.2            |     | ns   |

| $t_{WO}$               |         | 3.7     |         | 4.4     |                | 6.4 | ns   |

| $t_{DD}$               |         | 3.7     |         | 4.4     |                | 6.4 | ns   |

| t <sub>EABOUT</sub>    |         | 0.0     |         | 0.1     |                | 0.6 | ns   |

| t <sub>EABCH</sub>     | 3.0     |         | 3.5     |         | 4.0            |     | ns   |

| t <sub>EABCL</sub>     | 3.8     |         | 4.5     |         | 5.9            |     | ns   |

#### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

Tables 99 through 105 show EPF10K100A device internal and external timing parameters.

| Symbol              | -1 Snee | d Grade | -2 Snee | d Grade | -3 Spee | Unit |       |

|---------------------|---------|---------|---------|---------|---------|------|-------|

| -,                  | Min     | Max     | Min     | Max     | Min     | Max  | Oiiii |

| $t_{LUT}$           |         | 1.0     |         | 1.2     |         | 1.4  | ns    |

| t <sub>CLUT</sub>   |         | 0.8     |         | 0.9     |         | 1.1  | ns    |

| t <sub>RLUT</sub>   |         | 1.4     |         | 1.6     |         | 1.9  | ns    |

| t <sub>PACKED</sub> |         | 0.4     |         | 0.5     |         | 0.5  | ns    |

| $t_{EN}$            |         | 0.6     |         | 0.7     |         | 0.8  | ns    |

| t <sub>CICO</sub>   |         | 0.2     |         | 0.2     |         | 0.3  | ns    |

| t <sub>CGEN</sub>   |         | 0.4     |         | 0.4     |         | 0.6  | ns    |

| t <sub>CGENR</sub>  |         | 0.6     |         | 0.7     |         | 0.8  | ns    |

| t <sub>CASC</sub>   |         | 0.7     |         | 0.9     |         | 1.0  | ns    |

| t <sub>C</sub>      |         | 0.9     |         | 1.0     |         | 1.2  | ns    |

| t <sub>CO</sub>     |         | 0.2     |         | 0.3     |         | 0.3  | ns    |

| t <sub>COMB</sub>   |         | 0.6     |         | 0.7     |         | 0.8  | ns    |

| $t_{SU}$            | 0.8     |         | 1.0     |         | 1.2     |      | ns    |

| t <sub>H</sub>      | 0.3     |         | 0.5     |         | 0.5     |      | ns    |

| t <sub>PRE</sub>    |         | 0.3     |         | 0.3     |         | 0.4  | ns    |

| t <sub>CLR</sub>    |         | 0.3     |         | 0.3     |         | 0.4  | ns    |

| t <sub>CH</sub>     | 2.5     |         | 3.5     |         | 4.0     |      | ns    |

| $t_{CL}$            | 2.5     |         | 3.5     |         | 4.0     |      | ns    |

| Symbol                   | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | Unit |    |

|--------------------------|----------------|-----|---------|---------|---------|------|----|

|                          | Min            | Max | Min     | Max     | Min     | Max  |    |

| t <sub>DIN2IOE</sub>     |                | 4.8 |         | 5.4     |         | 6.0  | ns |

| t <sub>DIN2LE</sub>      |                | 2.0 |         | 2.4     |         | 2.7  | ns |

| t <sub>DIN2DATA</sub>    |                | 2.4 |         | 2.7     |         | 2.9  | ns |

| t <sub>DCLK2IOE</sub>    |                | 2.6 |         | 3.0     |         | 3.5  | ns |

| t <sub>DCLK2LE</sub>     |                | 2.0 |         | 2.4     |         | 2.7  | ns |

| t <sub>SAMELAB</sub>     |                | 0.1 |         | 0.1     |         | 0.1  | ns |

| t <sub>SAMEROW</sub>     |                | 1.5 |         | 1.7     |         | 1.9  | ns |

| t <sub>SAME</sub> COLUMN |                | 5.5 |         | 6.5     |         | 7.4  | ns |

| t <sub>DIFFROW</sub>     |                | 7.0 |         | 8.2     |         | 9.3  | ns |

| t <sub>TWOROWS</sub>     |                | 8.5 |         | 9.9     |         | 11.2 | ns |

| t <sub>LEPERIPH</sub>    |                | 3.9 |         | 4.2     |         | 4.5  | ns |

| t <sub>LABCARRY</sub>    |                | 0.2 |         | 0.2     |         | 0.3  | ns |

| t <sub>LABCASC</sub>     |                | 0.4 |         | 0.5     |         | 0.6  | ns |

| Table 104. EPF10K100A Device External Timing Parameters Note (1) |         |          |         |          |                |      |      |  |  |

|------------------------------------------------------------------|---------|----------|---------|----------|----------------|------|------|--|--|

| Symbol                                                           | -1 Spee | ed Grade | -2 Spec | ed Grade | -3 Speed Grade |      | Unit |  |  |

|                                                                  | Min     | Max      | Min     | Max      | Min            | Max  |      |  |  |

| t <sub>DRR</sub>                                                 |         | 12.5     |         | 14.5     |                | 17.0 | ns   |  |  |

| t <sub>INSU</sub> (2), (3)                                       | 3.7     |          | 4.5     |          | 5.1            |      | ns   |  |  |

| t <sub>INH</sub> (3)                                             | 0.0     |          | 0.0     |          | 0.0            |      | ns   |  |  |

| t <sub>оитсо</sub> (3)                                           | 2.0     | 5.3      | 2.0     | 6.1      | 2.0            | 7.2  | ns   |  |  |

| Table 105. EPF10K10    | Table 105. EPF10K100A Device External Bidirectional Timing Parameters       Note (1) |          |        |          |         |      |    |  |  |

|------------------------|--------------------------------------------------------------------------------------|----------|--------|----------|---------|------|----|--|--|

| Symbol                 | -1 Spee                                                                              | ed Grade | -2 Spe | ed Grade | -3 Spec | Unit |    |  |  |

|                        | Min                                                                                  | Max      | Min    | Max      | Min     | Max  |    |  |  |

| t <sub>INSUBIDIR</sub> | 4.9                                                                                  |          | 5.8    |          | 6.8     |      | ns |  |  |

| t <sub>INHBIDIR</sub>  | 0.0                                                                                  |          | 0.0    |          | 0.0     |      | ns |  |  |

| toutcobidir            | 2.0                                                                                  | 5.3      | 2.0    | 6.1      | 2.0     | 7.2  | ns |  |  |

| t <sub>XZBIDIR</sub>   |                                                                                      | 7.4      |        | 8.6      |         | 10.1 | ns |  |  |

| t <sub>ZXBIDIR</sub>   |                                                                                      | 7.4      |        | 8.6      |         | 10.1 | ns |  |  |

| Symbol              | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | d Grade | Unit |

|---------------------|----------------|-----|---------|---------|---------|---------|------|

|                     | Min            | Max | Min     | Max     | Min     | Max     |      |

| $t_{IOD}$           |                | 1.2 |         | 1.3     |         | 1.6     | ns   |

| $t_{IOC}$           |                | 0.4 |         | 0.4     |         | 0.5     | ns   |

| t <sub>IOCO</sub>   |                | 0.8 |         | 0.9     |         | 1.1     | ns   |

| $t_{IOCOMB}$        |                | 0.7 |         | 0.7     |         | 0.8     | ns   |

| t <sub>IOSU</sub>   | 2.7            |     | 3.1     |         | 3.6     |         | ns   |

| t <sub>IOH</sub>    | 0.2            |     | 0.3     |         | 0.3     |         | ns   |

| t <sub>IOCLR</sub>  |                | 1.2 |         | 1.3     |         | 1.6     | ns   |

| $t_{OD1}$           |                | 3.2 |         | 3.6     |         | 4.2     | ns   |

| $t_{OD2}$           |                | 5.9 |         | 6.7     |         | 7.8     | ns   |

| $t_{OD3}$           |                | 8.7 |         | 9.8     |         | 11.5    | ns   |

| $t_{XZ}$            |                | 3.8 |         | 4.3     |         | 5.0     | ns   |

| $t_{ZX1}$           |                | 3.8 |         | 4.3     |         | 5.0     | ns   |

| t <sub>ZX2</sub>    |                | 6.5 |         | 7.4     |         | 8.6     | ns   |

| t <sub>ZX3</sub>    |                | 9.3 |         | 10.5    |         | 12.3    | ns   |

| t <sub>INREG</sub>  |                | 8.2 |         | 9.3     |         | 10.9    | ns   |

| t <sub>IOFD</sub>   |                | 9.0 |         | 10.2    |         | 12.0    | ns   |

| t <sub>INCOMB</sub> |                | 9.0 |         | 10.2    |         | 12.0    | ns   |

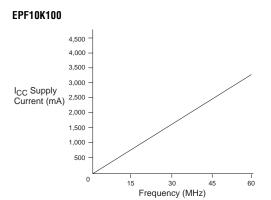

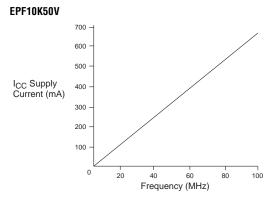

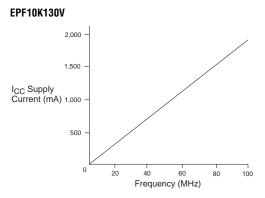

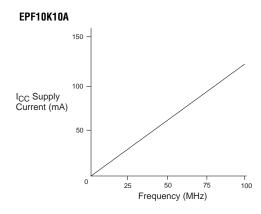

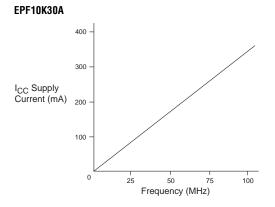

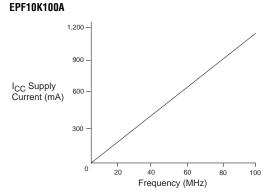

Figure 32. I<sub>CCACTIVE</sub> vs. Operating Frequency (Part 2 of 3)

101 Innovation Drive San Jose, CA 95134 (408) 544-7000 http://www.altera.com Applications Hotline: (800) 800-EPLD Customer Marketing: (408) 544-7104 Literature Services: lit\_req@altera.com

Copyright © 2003 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device designations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Altera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to

current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

I.S. EN ISO 9001