Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 216                                                        |

| Number of Logic Elements/Cells | 1728                                                       |

| Total RAM Bits                 | 12288                                                      |

| Number of I/O                  | 147                                                        |

| Number of Gates                | 69000                                                      |

| Voltage - Supply               | 4.75V ~ 5.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 70°C (TA)                                            |

| Package / Case                 | 208-BFQFP Exposed Pad                                      |

| Supplier Device Package        | 208-RQFP (28x28)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k30rc208-3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Logic functions are implemented by programming the EAB with a readonly pattern during configuration, creating a large LUT. With LUTs, combinatorial functions are implemented by looking up the results, rather than by computing them. This implementation of combinatorial functions can be faster than using algorithms implemented in general logic, a performance advantage that is further enhanced by the fast access times of EABs. The large capacity of EABs enables designers to implement complex functions in one logic level without the routing delays associated with linked LEs or field-programmable gate array (FPGA) RAM blocks. For example, a single EAB can implement a  $4 \times 4$  multiplier with eight inputs and eight outputs. Parameterized functions such as LPM functions can automatically take advantage of the EAB.

The EAB provides advantages over FPGAs, which implement on-board RAM as arrays of small, distributed RAM blocks. These FPGA RAM blocks contain delays that are less predictable as the size of the RAM increases. In addition, FPGA RAM blocks are prone to routing problems because small blocks of RAM must be connected together to make larger blocks. In contrast, EABs can be used to implement large, dedicated blocks of RAM that eliminate these timing and routing concerns.

EABs can be used to implement synchronous RAM, which is easier to use than asynchronous RAM. A circuit using asynchronous RAM must generate the RAM write enable (WE) signal, while ensuring that its data and address signals meet setup and hold time specifications relative to the WE signal. In contrast, the EAB's synchronous RAM generates its own WE signal and is self-timed with respect to the global clock. A circuit using the EAB's self-timed RAM need only meet the setup and hold time specifications of the global clock.

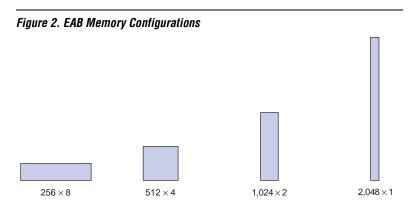

When used as RAM, each EAB can be configured in any of the following sizes:  $256 \times 8$ ,  $512 \times 4$ ,  $1,024 \times 2$ , or  $2,048 \times 1$ . See Figure 2.

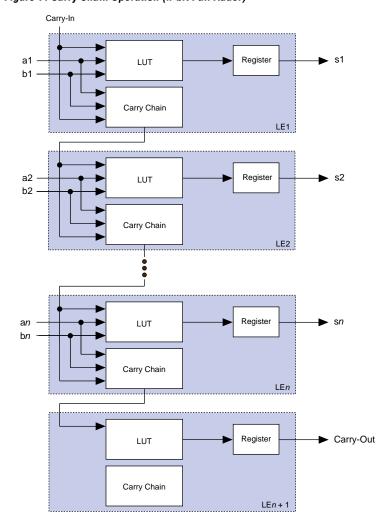

Figure 7 shows how an n-bit full adder can be implemented in n+1 LEs with the carry chain. One portion of the LUT generates the sum of two bits using the input signals and the carry-in signal; the sum is routed to the output of the LE. The register can either be bypassed for simple adders or be used for an accumulator function. The carry chain logic generates the carry-out signal, which is routed directly to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it can be used as a general-purpose signal.

Figure 7. Carry Chain Operation (n-bit Full Adder)

#### Up/Down Counter Mode

The up/down counter mode offers counter enable, clock enable, synchronous up/down control, and data loading options. These control signals are generated by the data inputs from the LAB local interconnect, the carry-in signal, and output feedback from the programmable register. The Up/down counter mode uses 2 three-input LUTs: one generates the counter data, and the other generates the fast carry bit. A 2-to-1 multiplexer provides synchronous loading. Data can also be loaded asynchronously with the clear and preset register control signals, without using the LUT resources.

#### Clearable Counter Mode

The clearable counter mode is similar to the up/down counter mode, but supports a synchronous clear instead of the up/down control. The clear function is substituted for the cascade-in signal in the up/down counter mode. Clearable counter mode uses 2 three-input LUTs: one generates the counter data, and the other generates the fast carry bit. Synchronous loading is provided by a 2-to-1 multiplexer. The output of this multiplexer is ANDed with a synchronous clear signal.

#### Internal Tri-State Emulation

Internal tri-state emulation provides internal tri-stating without the limitations of a physical tri-state bus. In a physical tri-state bus, the tri-state buffers' output enable (OE) signals select which signal drives the bus. However, if multiple OE signals are active, contending signals can be driven onto the bus. Conversely, if no OE signals are active, the bus will float. Internal tri-state emulation resolves contending tri-state buffers to a low value and floating buses to a high value, thereby eliminating these problems. The Altera software automatically implements tri-state bus functionality with a multiplexer.

#### Clear & Preset Logic Control

Logic for the programmable register's clear and preset functions is controlled by the DATA3, LABCTRL1, and LABCTRL2 inputs to the LE. The clear and preset control structure of the LE asynchronously loads signals into a register. Either LABCTRL1 or LABCTRL2 can control the asynchronous clear. Alternatively, the register can be set up so that LABCTRL1 implements an asynchronous load. The data to be loaded is driven to DATA3; when LABCTRL1 is asserted, DATA3 is loaded into the register.

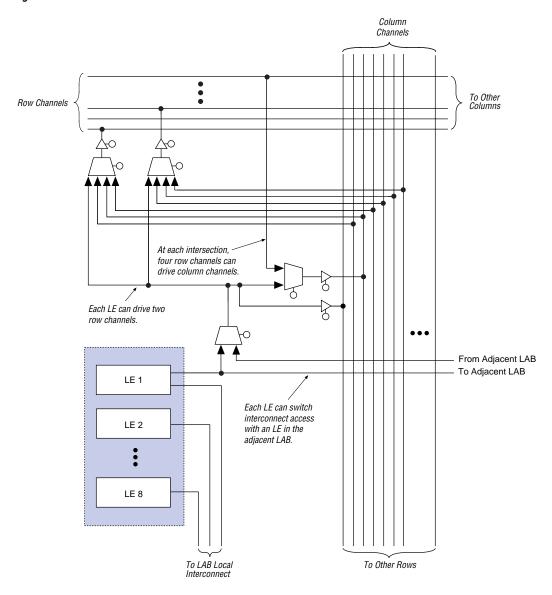

Figure 11. LAB Connections to Row & Column Interconnect

| Table 13. FLEX 10K | JTAG Instructions                                                                                                                                                                                                                     |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG Instruction   | Description                                                                                                                                                                                                                           |

| SAMPLE/PRELOAD     | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern output at the device pins.                                                            |

| EXTEST             | Allows the external circuitry and board-level interconnections to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                                |

| BYPASS             | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through a selected device to adjacent devices during normal device operation.                                          |

| USERCODE           | Selects the user electronic signature (USERCODE) register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                        |

| IDCODE             | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                 |

| ICR Instructions   | These instructions are used when configuring a FLEX 10K device via JTAG ports with a BitBlaster, or ByteBlasterMV or MasterBlaster download cable, or using a Jam File (.jam) or Jam Byte-Code File (.jbc) via an embedded processor. |

The instruction register length of FLEX 10K devices is 10 bits. The USERCODE register length in FLEX 10K devices is 32 bits; 7 bits are determined by the user, and 25 bits are predetermined. Tables 14 and 15 show the boundary-scan register length and device IDCODE information for FLEX 10K devices.

| Device                | Boundary-Scan<br>Register Length |

|-----------------------|----------------------------------|

| EPF10K10, EPF10K10A   | 480                              |

| EPF10K20              | 624                              |

| EPF10K30, EPF10K30A   | 768                              |

| EPF10K40              | 864                              |

| EPF10K50, EPF10K50V   | 960                              |

| EPF10K70              | 1,104                            |

| EPF10K100, EPF10K100A | 1,248                            |

| EPF10K130V            | 1,440                            |

| EPF10K250A            | 1,440                            |

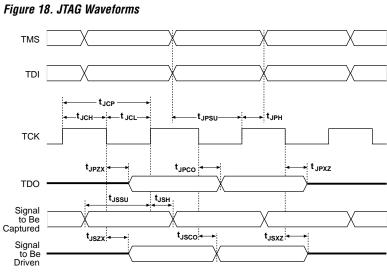

Figure 18 shows the timing requirements for the JTAG signals.

Table 16 shows the timing parameters and values for FLEX 10K devices.

| Table 1           | 6. JTAG Timing Parameters & Values             |     |     |      |

|-------------------|------------------------------------------------|-----|-----|------|

| Symbol            | Parameter                                      | Min | Max | Unit |

| t <sub>JCP</sub>  | TCK clock period                               | 100 |     | ns   |

| t <sub>JCH</sub>  | TCK clock high time                            | 50  |     | ns   |

| t <sub>JCL</sub>  | TCK clock low time                             | 50  |     | ns   |

| t <sub>JPSU</sub> | JTAG port setup time                           | 20  |     | ns   |

| t <sub>JPH</sub>  | JTAG port hold time                            | 45  |     | ns   |

| t <sub>JPCO</sub> | JTAG port clock to output                      |     | 25  | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output       |     | 25  | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance       |     | 25  | ns   |

| t <sub>JSSU</sub> | Capture register setup time                    | 20  |     | ns   |

| t <sub>JSH</sub>  | Capture register hold time                     | 45  |     | ns   |

| t <sub>JSCO</sub> | Update register clock to output                |     | 35  | ns   |

| t <sub>JSZX</sub> | Update register high-impedance to valid output |     | 35  | ns   |

| t <sub>JSXZ</sub> | Update register valid output to high impedance |     | 35  | ns   |

Figure 21 shows the typical output drive characteristics of EPF10K50V and EPF10K130V devices.

Typical I<sub>O</sub>

Output

Current (mA)

40

V<sub>CC</sub> = 3.3 V

Room Temperature

1

2

V<sub>O</sub> Output Voltage (V)

Figure 21. Output Drive Characteristics of EPF10K50V & EPF10K130V Devices

Tables 26 through 31 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 3.3-V FLEX 10K devices.

| Table 2          | Table 26. FLEX 10KA 3.3-V Device Absolute Maximum Ratings         Note (1) |                              |      |      |      |  |  |  |

|------------------|----------------------------------------------------------------------------|------------------------------|------|------|------|--|--|--|

| Symbol           | Parameter                                                                  | Conditions                   | Min  | Max  | Unit |  |  |  |

| V <sub>CC</sub>  | Supply voltage                                                             | With respect to ground (2)   | -0.5 | 4.6  | V    |  |  |  |

| V <sub>I</sub>   | DC input voltage                                                           |                              | -2.0 | 5.75 | V    |  |  |  |

| I <sub>OUT</sub> | DC output current, per pin                                                 |                              | -25  | 25   | mA   |  |  |  |

| T <sub>STG</sub> | Storage temperature                                                        | No bias                      | -65  | 150  | ° C  |  |  |  |

| T <sub>AMB</sub> | Ambient temperature                                                        | Under bias                   | -65  | 135  | °C   |  |  |  |

| TJ               | Junction temperature                                                       | Ceramic packages, under bias |      | 150  | ° C  |  |  |  |

|                  |                                                                            | PQFP, TQFP, RQFP, and BGA    |      | 135  | ° C  |  |  |  |

|                  |                                                                            | packages, under bias         |      |      |      |  |  |  |

| Symbol                 | Parameter                                                                              | Conditions |

|------------------------|----------------------------------------------------------------------------------------|------------|

| t <sub>EABAA</sub>     | EAB address access delay                                                               |            |

| t <sub>EABRCCOMB</sub> | EAB asynchronous read cycle time                                                       |            |

| t <sub>EABRCREG</sub>  | EAB synchronous read cycle time                                                        |            |

| t <sub>EABWP</sub>     | EAB write pulse width                                                                  |            |

| t <sub>EABWCCOMB</sub> | EAB asynchronous write cycle time                                                      |            |

| t <sub>EABWCREG</sub>  | EAB synchronous write cycle time                                                       |            |

| t <sub>EABDD</sub>     | EAB data-in to data-out valid delay                                                    |            |

| t <sub>EABDATACO</sub> | EAB clock-to-output delay when using output registers                                  |            |

| t <sub>EABDATASU</sub> | EAB data/address setup time before clock when using input register                     |            |

| t <sub>EABDATAH</sub>  | EAB data/address hold time after clock when using input register                       |            |

| t <sub>EABWESU</sub>   | EAB WE setup time before clock when using input register                               |            |

| t <sub>EABWEH</sub>    | EAB WE hold time after clock when using input register                                 |            |

| t <sub>EABWDSU</sub>   | EAB data setup time before falling edge of write pulse when not using input registers  |            |

| t <sub>EABWDH</sub>    | EAB data hold time after falling edge of write pulse when not using input              |            |

|                        | registers                                                                              |            |

| t <sub>EABWASU</sub>   | EAB address setup time before rising edge of write pulse when not using                |            |

|                        | input registers                                                                        |            |

| <sup>t</sup> EABWAH    | EAB address hold time after falling edge of write pulse when not using input registers |            |

| t <sub>EABWO</sub>     | EAB write enable to data output valid delay                                            |            |

| Symbol              | -3 Spee | d Grade | -4 Spee | Unit |    |

|---------------------|---------|---------|---------|------|----|

|                     | Min     | Max     | Min     | Max  |    |

| $t_{IOD}$           |         | 1.3     |         | 1.6  | ns |

| t <sub>IOC</sub>    |         | 0.5     |         | 0.7  | ns |

| t <sub>IOCO</sub>   |         | 0.2     |         | 0.2  | ns |

| t <sub>IOCOMB</sub> |         | 0.0     |         | 0.0  | ns |

| t <sub>IOSU</sub>   | 2.8     |         | 3.2     |      | ns |

| t <sub>IOH</sub>    | 1.0     |         | 1.2     |      | ns |

| t <sub>IOCLR</sub>  |         | 1.0     |         | 1.2  | ns |

| $t_{\text{OD1}}$    |         | 2.6     |         | 3.5  | ns |

| $t_{OD2}$           |         | 4.9     |         | 6.4  | ns |

| $t_{OD3}$           |         | 6.3     |         | 8.2  | ns |

| $t_{XZ}$            |         | 4.5     |         | 5.4  | ns |

| t <sub>ZX1</sub>    |         | 4.5     |         | 5.4  | ns |

| t <sub>ZX2</sub>    |         | 6.8     |         | 8.3  | ns |

| t <sub>ZX3</sub>    |         | 8.2     |         | 10.1 | ns |

| t <sub>INREG</sub>  |         | 6.0     |         | 7.5  | ns |

| t <sub>IOFD</sub>   |         | 3.1     |         | 3.5  | ns |

| t <sub>INCOMB</sub> |         | 3.1     |         | 3.5  | ns |

| Symbol                 | -3 Spee | d Grade | -4 Spee | d Grade | Unit |

|------------------------|---------|---------|---------|---------|------|

|                        | Min     | Max     | Min     | Max     |      |

| t <sub>EABDATA1</sub>  |         | 1.5     |         | 1.9     | ns   |

| t <sub>EABDATA2</sub>  |         | 4.8     |         | 6.0     | ns   |

| t <sub>EABWE1</sub>    |         | 1.0     |         | 1.2     | ns   |

| t <sub>EABWE2</sub>    |         | 5.0     |         | 6.2     | ns   |

| t <sub>EABCLK</sub>    |         | 1.0     |         | 2.2     | ns   |

| t <sub>EABCO</sub>     |         | 0.5     |         | 0.6     | ns   |

| t <sub>EABBYPASS</sub> |         | 1.5     |         | 1.9     | ns   |

| t <sub>EABSU</sub>     | 1.5     |         | 1.8     |         | ns   |

| t <sub>EABH</sub>      | 2.0     |         | 2.5     |         | ns   |

| $t_{AA}$               |         | 8.7     |         | 10.7    | ns   |

| $t_{WP}$               | 5.8     |         | 7.2     |         | ns   |

| t <sub>WDSU</sub>      | 1.6     |         | 2.0     |         | ns   |

| t <sub>WDH</sub>       | 0.3     |         | 0.4     |         | ns   |

| t <sub>WASU</sub>      | 0.5     |         | 0.6     |         | ns   |

| $t_{WAH}$              | 1.0     |         | 1.2     |         | ns   |

| $t_{WO}$               |         | 5.0     |         | 6.2     | ns   |

| $t_{DD}$               |         | 5.0     |         | 6.2     | ns   |

| t <sub>EABOUT</sub>    |         | 0.5     |         | 0.6     | ns   |

| t <sub>EABCH</sub>     | 4.0     |         | 4.0     |         | ns   |

| t <sub>EABCL</sub>     | 5.8     |         | 7.2     |         | ns   |

| Symbol                 | -3 Spee | d Grade | -4 Spee | Unit |    |

|------------------------|---------|---------|---------|------|----|

|                        | Min     | Max     | Min     | Max  |    |

| t <sub>EABAA</sub>     |         | 13.7    |         | 17.0 | ns |

| t <sub>EABRCCOMB</sub> | 13.7    |         | 17.0    |      | ns |

| t <sub>EABRCREG</sub>  | 9.7     |         | 11.9    |      | ns |

| t <sub>EABWP</sub>     | 5.8     |         | 7.2     |      | ns |

| t <sub>EABWCCOMB</sub> | 7.3     |         | 9.0     |      | ns |

| t <sub>EABWCREG</sub>  | 13.0    |         | 16.0    |      | ns |

| t <sub>EABDD</sub>     |         | 10.0    |         | 12.5 | ns |

| t <sub>EABDATACO</sub> |         | 2.0     |         | 3.4  | ns |

| t <sub>EABDATASU</sub> | 5.3     |         | 5.6     |      | ns |

| t <sub>EABDATAH</sub>  | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWESU</sub>   | 5.5     |         | 5.8     |      | ns |

| t <sub>EABWEH</sub>    | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWDSU</sub>   | 5.5     |         | 5.8     |      | ns |

| t <sub>EABWDH</sub>    | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWASU</sub>   | 2.1     |         | 2.7     |      | ns |

| t <sub>EABWAH</sub>    | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWO</sub>     |         | 9.5     |         | 11.8 | ns |

| Symbol                   | -3 Speed Grade |     | -4 Spee | Unit |    |

|--------------------------|----------------|-----|---------|------|----|

|                          | Min            | Max | Min     | Max  |    |

| t <sub>DIN2IOE</sub>     |                | 6.9 |         | 8.7  | ns |

| t <sub>DIN2LE</sub>      |                | 3.6 |         | 4.8  | ns |

| t <sub>DIN2DATA</sub>    |                | 5.5 | _       | 7.2  | ns |

| t <sub>DCLK2IOE</sub>    |                | 4.6 |         | 6.2  | ns |

| t <sub>DCLK2LE</sub>     |                | 3.6 |         | 4.8  | ns |

| t <sub>SAMELAB</sub>     |                | 0.3 |         | 0.3  | ns |

| t <sub>SAMEROW</sub>     |                | 3.3 |         | 3.7  | ns |

| t <sub>SAME</sub> COLUMN |                | 2.5 |         | 2.7  | ns |

| t <sub>DIFFROW</sub>     |                | 5.8 |         | 6.4  | ns |

| t <sub>TWOROWS</sub>     |                | 9.1 |         | 10.1 | ns |

| t <sub>LEPERIPH</sub>    |                | 6.2 |         | 7.1  | ns |

| t <sub>LABCARRY</sub>    |                | 0.4 |         | 0.6  | ns |

| t <sub>LABCASC</sub>     |                | 2.4 |         | 3.0  | ns |

| Symbol                  | -3 Spee | -3 Speed Grade |     | -4 Speed Grade |    |

|-------------------------|---------|----------------|-----|----------------|----|

|                         | Min     | Max            | Min | Max            |    |

| t <sub>DIN2IOE</sub>    |         | 7.6            |     | 9.4            | ns |

| t <sub>DIN2LE</sub>     |         | 3.6            |     | 4.8            | ns |

| t <sub>DIN2DATA</sub>   |         | 5.5            |     | 7.2            | ns |

| t <sub>DCLK2IOE</sub>   |         | 4.6            |     | 6.2            | ns |

| t <sub>DCLK2LE</sub>    |         | 3.6            |     | 4.8            | ns |

| t <sub>SAMELAB</sub>    |         | 0.3            |     | 0.3            | ns |

| t <sub>SAMEROW</sub>    |         | 3.3            |     | 3.7            | ns |

| t <sub>SAMECOLUMN</sub> |         | 3.1            |     | 3.2            | ns |

| t <sub>DIFFROW</sub>    |         | 6.4            |     | 6.4            | ns |

| t <sub>TWOROWS</sub>    |         | 9.7            |     | 10.6           | ns |

| t <sub>LEPERIPH</sub>   |         | 6.4            |     | 7.1            | ns |

| t <sub>LABCARRY</sub>   |         | 0.4            |     | 0.6            | ns |

| t <sub>LABCASC</sub>    |         | 2.4            |     | 3.0            | ns |

| Symbol              | -2 Spee | d Grade | -3 Speed Grade |     | -4 Speed Grade |      | Unit |

|---------------------|---------|---------|----------------|-----|----------------|------|------|

|                     | Min     | Max     | Min            | Max | Min            | Max  |      |

| $t_{IOD}$           |         | 0.0     |                | 0.0 |                | 0.0  | ns   |

| t <sub>IOC</sub>    |         | 0.4     |                | 0.5 |                | 0.7  | ns   |

| t <sub>IOCO</sub>   |         | 0.4     |                | 0.4 |                | 0.9  | ns   |

| t <sub>IOCOMB</sub> |         | 0.0     |                | 0.0 |                | 0.0  | ns   |

| t <sub>IOSU</sub>   | 4.5     |         | 5.0            |     | 6.2            |      | ns   |

| $t_{IOH}$           | 0.4     |         | 0.5            |     | 0.7            |      | ns   |

| t <sub>IOCLR</sub>  |         | 0.6     |                | 0.7 |                | 1.6  | ns   |

| $t_{\text{OD1}}$    |         | 3.6     |                | 4.0 |                | 5.0  | ns   |

| $t_{OD2}$           |         | 5.6     |                | 6.3 |                | 7.3  | ns   |

| $t_{OD3}$           |         | 6.9     |                | 7.7 |                | 8.7  | ns   |

| $t_{XZ}$            |         | 5.5     |                | 6.2 |                | 6.8  | ns   |

| $t_{ZX1}$           |         | 5.5     |                | 6.2 |                | 6.8  | ns   |

| t <sub>ZX2</sub>    |         | 7.5     |                | 8.5 |                | 9.1  | ns   |

| t <sub>ZX3</sub>    |         | 8.8     |                | 9.9 |                | 10.5 | ns   |

| t <sub>INREG</sub>  |         | 8.0     |                | 9.0 |                | 10.2 | ns   |

| t <sub>IOFD</sub>   |         | 7.2     |                | 8.1 |                | 10.3 | ns   |

| $t_{INCOMB}$        |         | 7.2     |                | 8.1 |                | 10.3 | ns   |

#### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

Tables  $64\,\mathrm{through}\,70\,\mathrm{show}\,EPF10K100\,\mathrm{device}$  internal and external timing parameters.

| Table 64. EPF10K100 Device LE Timing Microparameters   Note (1) |                  |     |        |          |                |     |      |

|-----------------------------------------------------------------|------------------|-----|--------|----------|----------------|-----|------|

| Symbol                                                          | -3DX Speed Grade |     | -3 Spe | ed Grade | -4 Speed Grade |     | Unit |

|                                                                 | Min              | Max | Min    | Max      | Min            | Max |      |

| $t_{LUT}$                                                       |                  | 1.5 |        | 1.5      |                | 2.0 | ns   |

| t <sub>CLUT</sub>                                               |                  | 0.4 |        | 0.4      |                | 0.5 | ns   |

| t <sub>RLUT</sub>                                               |                  | 1.6 |        | 1.6      |                | 2.0 | ns   |

| t <sub>PACKED</sub>                                             |                  | 0.9 |        | 0.9      |                | 1.3 | ns   |

| $t_{EN}$                                                        |                  | 0.9 |        | 0.9      |                | 1.2 | ns   |

| tcico                                                           |                  | 0.2 |        | 0.2      |                | 0.3 | ns   |

| t <sub>CGEN</sub>                                               |                  | 1.1 |        | 1.1      |                | 1.4 | ns   |

| t <sub>CGENR</sub>                                              |                  | 1.2 |        | 1.2      |                | 1.5 | ns   |

| t <sub>CASC</sub>                                               |                  | 1.1 |        | 1.1      |                | 1.3 | ns   |

| $t_{\mathbb{C}}$                                                |                  | 0.8 |        | 0.8      |                | 1.0 | ns   |

| $t_{CO}$                                                        |                  | 1.0 |        | 1.0      |                | 1.4 | ns   |

| t <sub>COMB</sub>                                               |                  | 0.5 |        | 0.5      |                | 0.7 | ns   |

| $t_{SU}$                                                        | 2.1              |     | 2.1    |          | 2.6            |     | ns   |

| t <sub>H</sub>                                                  | 2.3              |     | 2.3    |          | 3.1            |     | ns   |

| t <sub>PRE</sub>                                                |                  | 1.0 |        | 1.0      |                | 1.4 | ns   |

| t <sub>CLR</sub>                                                |                  | 1.0 |        | 1.0      |                | 1.4 | ns   |

| t <sub>CH</sub>                                                 | 4.0              |     | 4.0    |          | 4.0            |     | ns   |

| $t_{CL}$                                                        | 4.0              |     | 4.0    |          | 4.0            |     | ns   |

| 0                      | 4.0            | .d 0d. | O Omend Oreads |     | 0.0            | 0.0  |                | 4.0  |      |

|------------------------|----------------|--------|----------------|-----|----------------|------|----------------|------|------|

| Symbol                 | -1 Speed Grade |        | -2 Speed Grade |     | -3 Speed Grade |      | -4 Speed Grade |      | Unit |

|                        | Min            | Max    | Min            | Max | Min            | Max  | Min            | Max  |      |

| t <sub>EABDATA1</sub>  |                | 1.7    |                | 2.8 |                | 3.4  |                | 4.6  | ns   |

| t <sub>EABDATA2</sub>  |                | 4.9    |                | 3.9 |                | 4.8  |                | 5.9  | ns   |

| t <sub>EABWE1</sub>    |                | 0.0    |                | 2.5 |                | 3.0  |                | 3.7  | ns   |

| t <sub>EABWE2</sub>    |                | 4.0    |                | 4.1 |                | 5.0  |                | 6.2  | ns   |

| t <sub>EABCLK</sub>    |                | 0.4    |                | 0.8 |                | 1.0  |                | 1.2  | ns   |

| t <sub>EABCO</sub>     |                | 0.1    |                | 0.2 |                | 0.3  |                | 0.4  | ns   |

| t <sub>EABBYPASS</sub> |                | 0.9    |                | 1.1 |                | 1.3  |                | 1.6  | ns   |

| t <sub>EABSU</sub>     | 0.8            |        | 1.5            |     | 1.8            |      | 2.2            |      | ns   |

| t <sub>EABH</sub>      | 0.8            |        | 1.6            |     | 2.0            |      | 2.5            |      | ns   |

| $t_{AA}$               |                | 5.5    |                | 8.2 |                | 10.0 |                | 12.4 | ns   |

| $t_{WP}$               | 6.0            |        | 4.9            |     | 6.0            |      | 7.4            |      | ns   |

| t <sub>WDSU</sub>      | 0.1            |        | 0.8            |     | 1.0            |      | 1.2            |      | ns   |

| t <sub>WDH</sub>       | 0.1            |        | 0.2            |     | 0.3            |      | 0.4            |      | ns   |

| t <sub>WASU</sub>      | 0.1            |        | 0.4            |     | 0.5            |      | 0.6            |      | ns   |

| t <sub>WAH</sub>       | 0.1            |        | 0.8            |     | 1.0            |      | 1.2            |      | ns   |

| $t_{WO}$               |                | 2.8    |                | 4.3 |                | 5.3  |                | 6.5  | ns   |

| $t_{DD}$               |                | 2.8    |                | 4.3 |                | 5.3  |                | 6.5  | ns   |

| t <sub>EABOUT</sub>    |                | 0.5    |                | 0.4 |                | 0.5  |                | 0.6  | ns   |

| t <sub>EABCH</sub>     | 2.0            |        | 4.0            |     | 4.0            |      | 4.0            |      | ns   |

| t <sub>EABCL</sub>     | 6.0            |        | 4.9            |     | 6.0            |      | 7.4            |      | ns   |

#### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

Tables 85 through 91 show EPF10K10A device internal and external timing parameters.

| Symbol              | -1 Speed Grade |     | -2 Speed Grade |         | 2 Chood Crodo  |     | Unit |

|---------------------|----------------|-----|----------------|---------|----------------|-----|------|

|                     |                |     | -2 Spec        | u Graue | -3 Speed Grade |     | Unit |

|                     | Min            | Max | Min            | Max     | Min            | Max |      |

| t <sub>LUT</sub>    |                | 0.9 |                | 1.2     |                | 1.6 | ns   |

| t <sub>CLUT</sub>   |                | 1.2 |                | 1.4     |                | 1.9 | ns   |

| t <sub>RLUT</sub>   |                | 1.9 |                | 2.3     |                | 3.0 | ns   |

| t <sub>PACKED</sub> |                | 0.6 |                | 0.7     |                | 0.9 | ns   |

| t <sub>EN</sub>     |                | 0.5 |                | 0.6     |                | 0.8 | ns   |

| t <sub>CICO</sub>   | _              | 02  |                | 0.3     |                | 0.4 | ns   |

| t <sub>CGEN</sub>   | _              | 0.7 |                | 0.9     |                | 1.1 | ns   |

| t <sub>CGENR</sub>  |                | 0.7 |                | 0.9     |                | 1.1 | ns   |

| t <sub>CASC</sub>   |                | 1.0 |                | 1.2     |                | 1.7 | ns   |

| t <sub>C</sub>      |                | 1.2 |                | 1.4     |                | 1.9 | ns   |

| $t_{\rm CO}$        |                | 0.5 |                | 0.6     |                | 0.8 | ns   |

| t <sub>COMB</sub>   |                | 0.5 |                | 0.6     |                | 0.8 | ns   |

| t <sub>SU</sub>     | 1.1            |     | 1.3            |         | 1.7            |     | ns   |

| t <sub>H</sub>      | 0.6            |     | 0.7            |         | 0.9            |     | ns   |

| t <sub>PRE</sub>    |                | 0.5 |                | 0.6     | _              | 0.9 | ns   |

| t <sub>CLR</sub>    |                | 0.5 |                | 0.6     |                | 0.9 | ns   |

| t <sub>CH</sub>     | 3.0            |     | 3.5            |         | 4.0            |     | ns   |

| $t_{CL}$            | 3.0            |     | 3.5            |         | 4.0            |     | ns   |

| Symbol              | -1 Spee | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |    |

|---------------------|---------|----------------|-----|----------------|-----|----------------|----|

|                     | Min     | Max            | Min | Max            | Min | Max            |    |

|                     |         | 1.3            |     | 1.5            |     | 2.0            | ns |

| ioc                 |         | 0.2            |     | 0.3            |     | 0.3            | ns |

| ioco                |         | 0.2            |     | 0.3            |     | 0.4            | ns |

| <sup>t</sup> іосомв |         | 0.6            |     | 0.7            |     | 0.9            | ns |

| t <sub>iosu</sub>   | 0.8     |                | 1.0 |                | 1.3 |                | ns |

| Symbol              | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |      | Unit |

|---------------------|----------------|-----|----------------|-----|----------------|------|------|

|                     | Min            | Max | Min            | Max | Min            | Max  |      |

| $t_{IOD}$           |                | 2.5 |                | 2.9 |                | 3.4  | ns   |

| $t_{IOC}$           |                | 0.3 |                | 0.3 |                | 0.4  | ns   |

| $t_{IOCO}$          |                | 0.2 |                | 0.2 |                | 0.3  | ns   |

| $t_{IOCOMB}$        |                | 0.5 |                | 0.6 |                | 0.7  | ns   |

| $t_{IOSU}$          | 1.3            |     | 1.7            |     | 1.8            |      | ns   |

| $t_{IOH}$           | 0.2            |     | 0.2            |     | 0.3            |      | ns   |

| $t_{IOCLR}$         |                | 1.0 |                | 1.2 |                | 1.4  | ns   |

| $t_{OD1}$           |                | 2.2 |                | 2.6 |                | 3.0  | ns   |

| $t_{OD2}$           |                | 4.5 |                | 5.3 |                | 6.1  | ns   |

| t <sub>OD3</sub>    |                | 6.8 |                | 7.9 |                | 9.3  | ns   |

| $t_{XZ}$            |                | 2.7 |                | 3.1 |                | 3.7  | ns   |

| t <sub>ZX1</sub>    |                | 2.7 |                | 3.1 |                | 3.7  | ns   |

| $t_{ZX2}$           |                | 5.0 |                | 5.8 |                | 6.8  | ns   |

| $t_{ZX3}$           |                | 7.3 |                | 8.4 |                | 10.0 | ns   |

| t <sub>INREG</sub>  |                | 5.3 |                | 6.1 |                | 7.2  | ns   |

| t <sub>IOFD</sub>   |                | 4.7 |                | 5.5 |                | 6.4  | ns   |

| t <sub>INCOMB</sub> |                | 4.7 |                | 5.5 |                | 6.4  | ns   |

SRAM configuration elements allow FLEX 10K devices to be reconfigured in-circuit by loading new configuration data into the device. Real-time reconfiguration is performed by forcing the device into command mode with a device pin, loading different configuration data, reinitializing the device, and resuming user-mode operation.

The entire reconfiguration process may be completed in less than 320 ms using an EPF10K250A device with a DCLK frequency of 10 MHz. This process can be used to reconfigure an entire system dynamically. In-field upgrades can be performed by distributing new configuration files.

Refer to the configuration device data sheet to obtain the POR delay when using a configuration device method.

### **Programming Files**

Despite being function- and pin-compatible, FLEX 10KA and FLEX 10KE devices are not programming- or configuration-file compatible with FLEX 10K devices. A design should be recompiled before it is transferred from a FLEX 10K device to an equivalent FLEX 10KA or FLEX 10KE device. This recompilation should be performed to create a new programming or configuration file and to check design timing on the faster FLEX 10KA or FLEX 10KE device. The programming or configuration files for EPF10K50 devices can program or configure an EPF10K50V device. However, Altera recommends recompiling a design for the EPF10K50V device when transferring it from the EPF10K50 device.

# **Configuration Schemes**

The configuration data for a FLEX 10K device can be loaded with one of five configuration schemes (see Table 116), chosen on the basis of the target application. An EPC1, EPC2, EPC16, or EPC1441 configuration device, intelligent controller, or the JTAG port can be used to control the configuration of a FLEX 10K device, allowing automatic configuration on system power-up.

Multiple FLEX 10K devices can be configured in any of the five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

| Table 116. Data Sources for Configuration |                                                                                                                         |  |  |  |  |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Configuration Scheme                      | Data Source                                                                                                             |  |  |  |  |

| Configuration device                      | EPC1, EPC2, EPC16, or EPC1441 configuration device                                                                      |  |  |  |  |

| Passive serial (PS)                       | BitBlaster, MasterBlaster, or ByteBlasterMV download cable, or serial data source                                       |  |  |  |  |

| Passive parallel asynchronous (PPA)       | Parallel data source                                                                                                    |  |  |  |  |

| Passive parallel synchronous (PPS)        | Parallel data source                                                                                                    |  |  |  |  |

| JTAG                                      | BitBlaster, MasterBlaster, or ByteBlasterMV download cable, or microprocessor with Jam STAPL file or Jam Byte-Code file |  |  |  |  |

# Device Pin-Outs

See the Altera web site (http://www.altera.com) or the Altera Digital Library for pin-out information.

# Revision History

The information contained in the *FLEX 10K Embedded Programmable Logic Device Family Data Sheet* version 4.2 supersedes information published in previous versions.

# **Version 4.2 Changes**

The following change was made to version 4.2 of the *FLEX 10K Embedded Programmable Logic Device Family Data Sheet*: updated Figure 13.

# **Version 4.1 Changes**

The following changes were made to version 4.1 of the FLEX 10K Embedded Programmable Logic Device Family Data Sheet.

- Updated General Description section

- Updated I/O Element section

- Updated SameFrame Pin-Outs section

- Updated Figure 16

- Updated Tables 13 and 116

- Added Note 9 to Table 19

- Added Note 10 to Table 24

- Added Note 10 to Table 28