Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 288                                                        |

| Number of Logic Elements/Cells | 2304                                                       |

| Total RAM Bits                 | 16384                                                      |

| Number of I/O                  | 147                                                        |

| Number of Gates                | 93000                                                      |

| Voltage - Supply               | 4.75V ~ 5.25V                                              |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 70°C (TA)                                            |

| Package / Case                 | 208-BFQFP Exposed Pad                                      |

| Supplier Device Package        | 208-RQFP (28x28)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k40rc208-3 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Notes to tables:

- (1) FLEX 10K and FLEX 10KA device package types include plastic J-lead chip carrier (PLCC), thin quad flat pack (TQFP), plastic quad flat pack (PQFP), power quad flat pack (RQFP), ball-grid array (BGA), pin-grid array (PGA), and FineLine BGA™ packages.

- (2) This option is supported with a 256-pin FineLine BGA package. By using SameFrame pin migration, all FineLine BGA packages are pin compatible. For example, a board can be designed to support both 256-pin and 484-pin FineLine BGA packages. The Altera software automatically avoids conflicting pins when future migration is set.

# General Description

Altera's FLEX 10K devices are the industry's first embedded PLDs. Based on reconfigurable CMOS SRAM elements, the Flexible Logic Element MatriX (FLEX) architecture incorporates all features necessary to implement common gate array megafunctions. With up to 250,000 gates, the FLEX 10K family provides the density, speed, and features to integrate entire systems, including multiple 32-bit buses, into a single device.

FLEX 10K devices are reconfigurable, which allows 100% testing prior to shipment. As a result, the designer is not required to generate test vectors for fault coverage purposes. Additionally, the designer does not need to manage inventories of different ASIC designs; FLEX 10K devices can be configured on the board for the specific functionality required.

Table 6 shows FLEX 10K performance for some common designs. All performance values were obtained with Synopsys DesignWare or LPM functions. No special design technique was required to implement the applications; the designer simply inferred or instantiated a function in a Verilog HDL, VHDL, Altera Hardware Description Language (AHDL), or schematic design file.

| Application                       |     | urces<br>sed |                   | Perfor            | mance             |                   | Units |

|-----------------------------------|-----|--------------|-------------------|-------------------|-------------------|-------------------|-------|

|                                   | LEs | EABs         | -1 Speed<br>Grade | -2 Speed<br>Grade | -3 Speed<br>Grade | -4 Speed<br>Grade |       |

| 16-bit loadable counter (1)       | 16  | 0            | 204               | 166               | 125               | 95                | MHz   |

| 16-bit accumulator (1)            | 16  | 0            | 204               | 166               | 125               | 95                | MHz   |

| 16-to-1 multiplexer (2)           | 10  | 0            | 4.2               | 5.8               | 6.0               | 7.0               | ns    |

| 256 × 8 RAM read cycle speed (3)  | 0   | 1            | 172               | 145               | 108               | 84                | MHz   |

| 256 × 8 RAM write cycle speed (3) | 0   | 1            | 106               | 89                | 68                | 63                | MHz   |

#### Notes:

- (1) The speed grade of this application is limited because of clock high and low specifications.

- (2) This application uses combinatorial inputs and outputs.

- (3) This application uses registered inputs and outputs.

## FastTrack Interconnect

In the FLEX 10K architecture, connections between LEs and device I/O pins are provided by the FastTrack Interconnect, which is a series of continuous horizontal and vertical routing channels that traverse the device. This global routing structure provides predictable performance, even in complex designs. In contrast, the segmented routing in FPGAs requires switch matrices to connect a variable number of routing paths, increasing the delays between logic resources and reducing performance.

The FastTrack Interconnect consists of row and column interconnect channels that span the entire device. Each row of LABs is served by a dedicated row interconnect. The row interconnect can drive I/O pins and feed other LABs in the device. The column interconnect routes signals between rows and can drive I/O pins.

A row channel can be driven by an LE or by one of three column channels. These four signals feed dual 4-to-1 multiplexers that connect to two specific row channels. These multiplexers, which are connected to each LE, allow column channels to drive row channels even when all eight LEs in an LAB drive the row interconnect.

Each column of LABs is served by a dedicated column interconnect. The column interconnect can then drive I/O pins or another row's interconnect to route the signals to other LABs in the device. A signal from the column interconnect, which can be either the output of an LE or an input from an I/O pin, must be routed to the row interconnect before it can enter an LAB or EAB. Each row channel that is driven by an IOE or EAB can drive one specific column channel.

Access to row and column channels can be switched between LEs in adjacent pairs of LABs. For example, an LE in one LAB can drive the row and column channels normally driven by a particular LE in the adjacent LAB in the same row, and vice versa. This routing flexibility enables routing resources to be used more efficiently. See Figure 11.

Signals on the peripheral control bus can also drive the four global signals, referred to as GLOBAL0 through GLOBAL3 in Tables 8 and 9. The internally generated signal can drive the global signal, providing the same low-skew, low-delay characteristics for an internally generated signal as for a signal driven by an input. This feature is ideal for internally generated clear or clock signals with high fan-out. When a global signal is driven by internal logic, the dedicated input pin that drives that global signal cannot be used. The dedicated input pin should be driven to a known logic state (such as ground) and not be allowed to float.

When the chip-wide output enable pin is held low, it will tri-state all pins on the device. This option can be set in the Global Project Device Options menu. Additionally, the registers in the IOE can be reset by holding the chip-wide reset pin low.

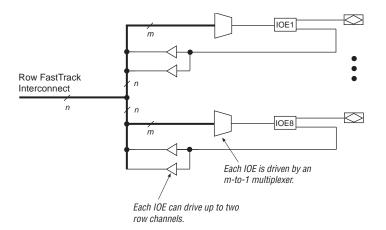

## Row-to-IOE Connections

When an IOE is used as an input signal, it can drive two separate row channels. The signal is accessible by all LEs within that row. When an IOE is used as an output, the signal is driven by a multiplexer that selects a signal from the row channels. Up to eight IOEs connect to each side of each row channel. See Figure 14.

Figure 14. FLEX 10K Row-to-IOE Connections

The values for m and n are provided in Table 10.

Table 12 describes the FLEX 10K device supply voltages and MultiVolt  $\rm I/O$  support levels.

| Devices       | Supply Vo          | oltage (V)        | MultiVolt I/O Sup | port Levels (V) |

|---------------|--------------------|-------------------|-------------------|-----------------|

|               | V <sub>CCINT</sub> | V <sub>CCIO</sub> | Input             | Output          |

| FLEX 10K (1)  | 5.0                | 5.0               | 3.3 or 5.0        | 5.0             |

|               | 5.0                | 3.3               | 3.3 or 5.0        | 3.3 or 5.0      |

| EPF10K50V (1) | 3.3                | 3.3               | 3.3 or 5.0        | 3.3 or 5.0      |

| EPF10K130V    | 3.3                | 3.3               | 3.3 or 5.0        | 3.3 or 5.0      |

| FLEX 10KA (1) | 3.3                | 3.3               | 2.5, 3.3, or 5.0  | 3.3 or 5.0      |

|               | 3.3                | 2.5               | 2.5, 3.3, or 5.0  | 2.5             |

#### Note

(1) 240-pin QFP packages do not support the MultiVolt I/O features, so they do not have separate V<sub>CCIO</sub> pins.

# Power Sequencing & Hot-Socketing

Because FLEX 10K devices can be used in a multi-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. The  $V_{\rm CCIO}$  and  $V_{\rm CCINT}$  power supplies can be powered in any order.

Signals can be driven into FLEX 10KA devices before and during power up without damaging the device. Additionally, FLEX 10KA devices do not drive out during power up. Once operating conditions are reached, FLEX 10KA devices operate as specified by the user.

IEEE Std. 1149.1 (JTAG) Boundary-Scan Support All FLEX 10K devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1-1990 specification. All FLEX 10K devices can also be configured using the JTAG pins through the BitBlaster serial download cable, or ByteBlasterMV parallel port download cable, or via hardware that uses the Jam<sup>TM</sup> programming and test language. JTAG BST can be performed before or after configuration, but not during configuration. FLEX 10K devices support the JTAG instructions shown in Table 13.

| Table 15. 32-Bit FLEX 10K Device IDCODE Note (1) |                     |                          |                                      |                  |  |  |

|--------------------------------------------------|---------------------|--------------------------|--------------------------------------|------------------|--|--|

| Device                                           |                     | IDCODE (3                | 2 Bits)                              |                  |  |  |

|                                                  | Version<br>(4 Bits) | Part Number<br>(16 Bits) | Manufacturer's Identity<br>(11 Bits) | 1 (1 Bit)<br>(2) |  |  |

| EPF10K10, EPF10K10A                              | 0000                | 0001 0000 0001 0000      | 00001101110                          | 1                |  |  |

| EPF10K20                                         | 0000                | 0001 0000 0010 0000      | 00001101110                          | 1                |  |  |

| EPF10K30, EPF10K30A                              | 0000                | 0001 0000 0011 0000      | 00001101110                          | 1                |  |  |

| EPF10K40                                         | 0000                | 0001 0000 0100 0000      | 00001101110                          | 1                |  |  |

| EPF10K50, EPF10K50V                              | 0000                | 0001 0000 0101 0000      | 00001101110                          | 1                |  |  |

| EPF10K70                                         | 0000                | 0001 0000 0111 0000      | 00001101110                          | 1                |  |  |

| EPF10K100, EPF10K100A                            | 0000                | 0000 0001 0000 0000      | 00001101110                          | 1                |  |  |

| EPF10K130V                                       | 0000                | 0000 0001 0011 0000      | 00001101110                          | 1                |  |  |

| EPF10K250A                                       | 0000                | 0000 0010 0101 0000      | 00001101110                          | 1                |  |  |

## Notes:

- (1) The most significant bit (MSB) is on the left.

- (2) The least significant bit (LSB) for all JTAG IDCODEs is 1.

FLEX 10K devices include weak pull-ups on JTAG pins.

For more information, see the following documents:

- Application Note 39 (IEEE 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices)

- BitBlaster Serial Download Cable Data Sheet

- ByteBlasterMV Parallel Port Download Cable Data Sheet

- Jam Programming & Test Language Specification

| Table 1            | 8. FLEX 10K 5.0-V Device Reco                       | mmended Operating Conditions |             |                          |      |

|--------------------|-----------------------------------------------------|------------------------------|-------------|--------------------------|------|

| Symbol             | Parameter                                           | Conditions                   | Min         | Max                      | Unit |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers | (3), (4)                     | 4.75 (4.50) | 5.25 (5.50)              | V    |

| V <sub>CCIO</sub>  | Supply voltage for output buffers, 5.0-V operation  | (3), (4)                     | 4.75 (4.50) | 5.25 (5.50)              | V    |

|                    | Supply voltage for output buffers, 3.3-V operation  | (3), (4)                     | 3.00 (3.00) | 3.60 (3.60)              | V    |

| VI                 | Input voltage                                       |                              | -0.5        | V <sub>CCINT</sub> + 0.5 | V    |

| Vo                 | Output voltage                                      |                              | 0           | V <sub>CCIO</sub>        | V    |

| T <sub>A</sub>     | Ambient temperature                                 | For commercial use           | 0           | 70                       | °C   |

|                    |                                                     | For industrial use           | -40         | 85                       | °C   |

| T <sub>J</sub>     | Operating temperature                               | For commercial use           | 0           | 85                       | °C   |

|                    |                                                     | For industrial use           | -40         | 100                      | °C   |

| t <sub>R</sub>     | Input rise time                                     |                              |             | 40                       | ns   |

| t <sub>F</sub>     | Input fall time                                     |                              |             | 40                       | ns   |

| Table 2            | able 29. 3.3-V Device Capacitance of EPF10K10A & EPF10K30A Devices |                                     | Note (12) |     |      |

|--------------------|--------------------------------------------------------------------|-------------------------------------|-----------|-----|------|

| Symbol             | Parameter                                                          | Conditions                          | Min       | Max | Unit |

| C <sub>IN</sub>    | Input capacitance                                                  | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |           | 8   | pF   |

| C <sub>INCLK</sub> | Input capacitance on dedicated clock pin                           | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |           | 12  | pF   |

| C <sub>OUT</sub>   | Output capacitance                                                 | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |           | 8   | pF   |

| Table 3            | ole 30. 3.3-V Device Capacitance of EPF10K100A Devices Note (12) |                                     |     |     |      |  |

|--------------------|------------------------------------------------------------------|-------------------------------------|-----|-----|------|--|

| Symbol             | Parameter                                                        | Conditions                          | Min | Max | Unit |  |

| C <sub>IN</sub>    | Input capacitance                                                | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 10  | pF   |  |

| C <sub>INCLK</sub> | Input capacitance on dedicated clock pin                         | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 15  | pF   |  |

| C <sub>OUT</sub>   | Output capacitance                                               | V <sub>OUT</sub> = 0 V, f = 1.0 MHz | •   | 10  | pF   |  |

| Table 3            | Table 31. 3.3-V Device Capacitance of EPF10K250A Devices Note (12) |                                     |     |     |      |  |

|--------------------|--------------------------------------------------------------------|-------------------------------------|-----|-----|------|--|

| Symbol             | Parameter                                                          | Conditions                          | Min | Max | Unit |  |

| C <sub>IN</sub>    | Input capacitance                                                  | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 10  | pF   |  |

| C <sub>INCLK</sub> | Input capacitance on dedicated clock pin                           | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 15  | pF   |  |

| C <sub>OUT</sub>   | Output capacitance                                                 | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 10  | pF   |  |

#### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC voltage input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) FLEX 10KA device inputs may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (6) Typical values are for  $T_A = 25^{\circ}$  C and  $V_{CC} = 3.3$  V.

- (7) These values are specified under the Recommended Operating Conditions shown in Table 27 on page 51.

- (8) The I<sub>OH</sub> parameter refers to high-level TTL, PCI, or CMOS output current.

- (9) The I<sub>OL</sub> parameter refers to low-level TTL, PCI, or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (10) This value is specified for normal device operation. The value may vary during power-up.

- (11) This parameter applies to all -1 speed grade commercial temperature devices and all -2 speed grade industrial-temperature devices.

- (12) Capacitance is sample-tested only.

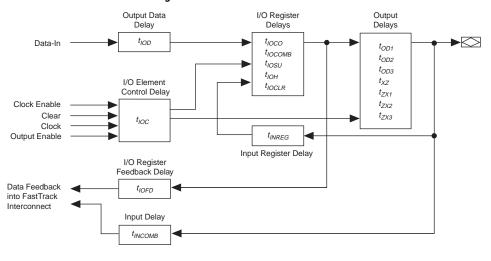

Figure 26. FLEX 10K Device IOE Timing Model

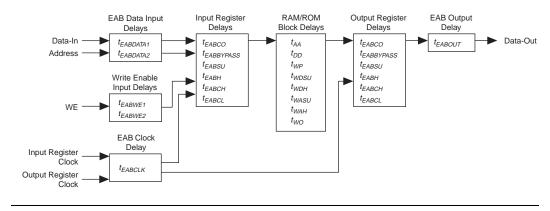

Figure 27. FLEX 10K Device EAB Timing Model

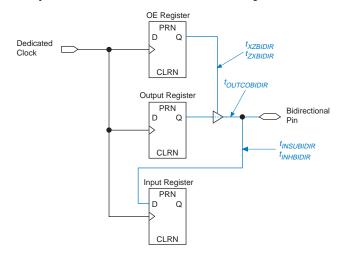

Figures 28 shows the timing model for bidirectional I/O pin timing.

Figure 28. Synchronous Bidirectional Pin External Timing Model

Tables 32 through 36 describe the FLEX 10K device internal timing parameters. These internal timing parameters are expressed as worst-case values. Using hand calculations, these parameters can be used to estimate design performance. However, before committing designs to silicon, actual worst-case performance should be modeled using timing simulation and analysis. Tables 37 through 38 describe FLEX 10K external timing parameters.

| Symbol              | Parameter                               | Conditions |

|---------------------|-----------------------------------------|------------|

| $t_{LUT}$           | LUT delay for data-in                   |            |

| t <sub>CLUT</sub>   | LUT delay for carry-in                  |            |

| t <sub>RLUT</sub>   | LUT delay for LE register feedback      |            |

| t <sub>PACKED</sub> | Data-in to packed register delay        |            |

| t <sub>EN</sub>     | LE register enable delay                |            |

| t <sub>CICO</sub>   | Carry-in to carry-out delay             |            |

| t <sub>CGEN</sub>   | Data-in to carry-out delay              |            |

| t <sub>CGENR</sub>  | LE register feedback to carry-out delay |            |

| t <sub>CASC</sub>   | Cascade-in to cascade-out delay         |            |

| $t_{\rm C}$         | LE register control signal delay        |            |

| $t_{CO}$            | LE register clock-to-output delay       |            |

| t <sub>COMB</sub>   | Combinatorial delay                     |            |

| Symbol                 | Parameter                                            | Conditions |

|------------------------|------------------------------------------------------|------------|

| t <sub>EABDATA1</sub>  | Data or address delay to EAB for combinatorial input |            |

| t <sub>EABDATA2</sub>  | Data or address delay to EAB for registered input    |            |

| t <sub>EABWE1</sub>    | Write enable delay to EAB for combinatorial input    |            |

| t <sub>EABWE2</sub>    | Write enable delay to EAB for registered input       |            |

| t <sub>EABCLK</sub>    | EAB register clock delay                             |            |

| t <sub>EABCO</sub>     | EAB register clock-to-output delay                   |            |

| t <sub>EABBYPASS</sub> | Bypass register delay                                |            |

| t <sub>EABSU</sub>     | EAB register setup time before clock                 |            |

| t <sub>EABH</sub>      | EAB register hold time after clock                   |            |

| $t_{AA}$               | Address access delay                                 |            |

| $t_{WP}$               | Write pulse width                                    |            |

| t <sub>WDSU</sub>      | Data setup time before falling edge of write pulse   | (5)        |

| t <sub>WDH</sub>       | Data hold time after falling edge of write pulse     | (5)        |

| t <sub>WASU</sub>      | Address setup time before rising edge of write pulse | (5)        |

| t <sub>WAH</sub>       | Address hold time after falling edge of write pulse  | (5)        |

| $t_{WO}$               | Write enable to data output valid delay              |            |

| t <sub>DD</sub>        | Data-in to data-out valid delay                      |            |

| t <sub>EABOUT</sub>    | Data-out delay                                       |            |

| t <sub>EABCH</sub>     | Clock high time                                      |            |

| t <sub>EABCL</sub>     | Clock low time                                       |            |

| Symbol                 | -3 Spee | d Grade | -4 Speed Grade |      | Unit |

|------------------------|---------|---------|----------------|------|------|

|                        | Min     | Max     | Min            | Max  | -    |

| t <sub>EABDATA1</sub>  |         | 1.5     |                | 1.9  | ns   |

| t <sub>EABDATA2</sub>  |         | 4.8     |                | 6.0  | ns   |

| t <sub>EABWE1</sub>    |         | 1.0     |                | 1.2  | ns   |

| t <sub>EABWE2</sub>    |         | 5.0     |                | 6.2  | ns   |

| t <sub>EABCLK</sub>    |         | 1.0     |                | 2.2  | ns   |

| t <sub>EABCO</sub>     |         | 0.5     |                | 0.6  | ns   |

| t <sub>EABBYPASS</sub> |         | 1.5     |                | 1.9  | ns   |

| t <sub>EABSU</sub>     | 1.5     |         | 1.8            |      | ns   |

| t <sub>EABH</sub>      | 2.0     |         | 2.5            |      | ns   |

| $t_{AA}$               |         | 8.7     |                | 10.7 | ns   |

| $t_{WP}$               | 5.8     |         | 7.2            |      | ns   |

| t <sub>WDSU</sub>      | 1.6     |         | 2.0            |      | ns   |

| t <sub>WDH</sub>       | 0.3     |         | 0.4            |      | ns   |

| t <sub>WASU</sub>      | 0.5     |         | 0.6            |      | ns   |

| $t_{WAH}$              | 1.0     |         | 1.2            |      | ns   |

| $t_{WO}$               |         | 5.0     |                | 6.2  | ns   |

| $t_{DD}$               |         | 5.0     |                | 6.2  | ns   |

| t <sub>EABOUT</sub>    |         | 0.5     |                | 0.6  | ns   |

| t <sub>EABCH</sub>     | 4.0     |         | 4.0            |      | ns   |

| t <sub>EABCL</sub>     | 5.8     |         | 7.2            |      | ns   |

Tables 48 through 56 show EPF10K30, EPF10K40, and EPF10K50 device internal and external timing parameters.

| Symbol              | -3 Spee | d Grade | -4 Spee | -4 Speed Grade |    |

|---------------------|---------|---------|---------|----------------|----|

|                     | Min     | Max     | Min     | Max            | 1  |

| $t_{LUT}$           |         | 1.3     |         | 1.8            | ns |

| t <sub>CLUT</sub>   |         | 0.6     |         | 0.6            | ns |

| t <sub>RLUT</sub>   |         | 1.5     |         | 2.0            | ns |

| t <sub>PACKED</sub> |         | 0.5     |         | 0.8            | ns |

| t <sub>EN</sub>     |         | 0.9     |         | 1.5            | ns |

| t <sub>CICO</sub>   |         | 0.2     |         | 0.4            | ns |

| t <sub>CGEN</sub>   |         | 0.9     |         | 1.4            | ns |

| t <sub>CGENR</sub>  |         | 0.9     |         | 1.4            | ns |

| t <sub>CASC</sub>   |         | 1.0     |         | 1.2            | ns |

| $t_{\mathbb{C}}$    |         | 1.3     |         | 1.6            | ns |

| $t_{CO}$            |         | 0.9     |         | 1.2            | ns |

| $t_{\text{COMB}}$   |         | 0.6     |         | 0.6            | ns |

| t <sub>SU</sub>     | 1.4     |         | 1.4     |                | ns |

| $t_H$               | 0.9     |         | 1.3     |                | ns |

| t <sub>PRE</sub>    |         | 0.9     |         | 1.2            | ns |

| t <sub>CLR</sub>    |         | 0.9     |         | 1.2            | ns |

| t <sub>CH</sub>     | 4.0     |         | 4.0     |                | ns |

| $t_{CL}$            | 4.0     |         | 4.0     |                | ns |

| Symbol                 | -3 Snee | d Grade | -4 Spee | Unit |       |

|------------------------|---------|---------|---------|------|-------|

| Symbol                 | -       |         |         |      | Oiiit |

|                        | Min     | Max     | Min     | Max  |       |

| t <sub>EABAA</sub>     |         | 13.7    |         | 17.0 | ns    |

| t <sub>EABRCCOMB</sub> | 13.7    |         | 17.0    |      | ns    |

| t <sub>EABRCREG</sub>  | 9.7     |         | 11.9    |      | ns    |

| t <sub>EABWP</sub>     | 5.8     |         | 7.2     |      | ns    |

| t <sub>EABWCCOMB</sub> | 7.3     |         | 9.0     |      | ns    |

| t <sub>EABWCREG</sub>  | 13.0    |         | 16.0    |      | ns    |

| t <sub>EABDD</sub>     |         | 10.0    |         | 12.5 | ns    |

| t <sub>EABDATACO</sub> |         | 2.0     |         | 3.4  | ns    |

| t <sub>EABDATASU</sub> | 5.3     |         | 5.6     |      | ns    |

| t <sub>EABDATAH</sub>  | 0.0     |         | 0.0     |      | ns    |

| t <sub>EABWESU</sub>   | 5.5     |         | 5.8     |      | ns    |

| t <sub>EABWEH</sub>    | 0.0     |         | 0.0     |      | ns    |

| t <sub>EABWDSU</sub>   | 5.5     |         | 5.8     |      | ns    |

| t <sub>EABWDH</sub>    | 0.0     |         | 0.0     |      | ns    |

| t <sub>EABWASU</sub>   | 2.1     |         | 2.7     |      | ns    |

| t <sub>EABWAH</sub>    | 0.0     |         | 0.0     |      | ns    |

| $t_{EABWO}$            |         | 9.5     |         | 11.8 | ns    |

| Symbol                                                            | -3DX Spe | ed Grade | -3 Spee | d Grade | -4 Spee | Unit |    |

|-------------------------------------------------------------------|----------|----------|---------|---------|---------|------|----|

|                                                                   | Min      | Max      | Min     | Max     | Min     | Max  |    |

| t <sub>DIN2IOE</sub>                                              |          | 10.3     |         | 10.3    |         | 12.2 | ns |

| t <sub>DIN2LE</sub>                                               |          | 4.8      |         | 4.8     |         | 6.0  | ns |

| t <sub>DIN2DATA</sub>                                             |          | 7.3      |         | 7.3     |         | 11.0 | ns |

| t <sub>DCLK2IOE</sub> without ClockLock or ClockBoost circuitry   |          | 6.2      |         | 6.2     |         | 7.7  | ns |

| $t_{DCLK2IOE}$ with ClockLock or ClockBoost circuitry             |          | 2.3      |         | _       |         | _    | ns |

| t <sub>DCLK2LE</sub> without ClockLock or<br>ClockBoost circuitry |          | 4.8      |         | 4.8     |         | 6.0  | ns |

| $t_{DCLK2LE}$ with ClockLock or ClockBoost circuitry              |          | 2.3      |         | _       |         | _    | ns |

| <sup>t</sup> SAMELAB                                              |          | 0.4      |         | 0.4     |         | 0.5  | ns |

| <sup>t</sup> SAMEROW                                              |          | 4.9      |         | 4.9     |         | 5.5  | ns |

| <sup>t</sup> SAMECOLUMN                                           |          | 5.1      |         | 5.1     |         | 5.4  | ns |

| t <sub>DIFFROW</sub>                                              |          | 10.0     |         | 10.0    |         | 10.9 | ns |

| t <sub>TWOROWS</sub>                                              |          | 14.9     |         | 14.9    |         | 16.4 | ns |

| t <sub>LEPERIPH</sub>                                             |          | 6.9      |         | 6.9     |         | 8.1  | ns |

| t <sub>LABCARRY</sub>                                             |          | 0.9      |         | 0.9     |         | 1.1  | ns |

| t <sub>LABCASC</sub>                                              |          | 3.0      |         | 3.0     |         | 3.2  | ns |

#### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

Tables 85 through 91 show EPF10K10A device internal and external timing parameters.

| Cumbal              | 1 Snoo         | d Grado | 2 Snoo  | d Grado | 2 Snor  | ed Grade | Unit |

|---------------------|----------------|---------|---------|---------|---------|----------|------|

| Symbol              | -1 Speed Grade |         | -2 Spec | d Grade | -o oper | UIIIL    |      |

|                     | Min            | Max     | Min     | Max     | Min     | Max      |      |

| t <sub>LUT</sub>    |                | 0.9     |         | 1.2     |         | 1.6      | ns   |

| t <sub>CLUT</sub>   |                | 1.2     |         | 1.4     |         | 1.9      | ns   |

| t <sub>RLUT</sub>   |                | 1.9     |         | 2.3     |         | 3.0      | ns   |

| t <sub>PACKED</sub> |                | 0.6     |         | 0.7     |         | 0.9      | ns   |

| t <sub>EN</sub>     |                | 0.5     |         | 0.6     |         | 0.8      | ns   |

| t <sub>CICO</sub>   | _              | 02      |         | 0.3     |         | 0.4      | ns   |

| t <sub>CGEN</sub>   | _              | 0.7     |         | 0.9     |         | 1.1      | ns   |

| t <sub>CGENR</sub>  |                | 0.7     |         | 0.9     |         | 1.1      | ns   |

| t <sub>CASC</sub>   |                | 1.0     |         | 1.2     |         | 1.7      | ns   |

| t <sub>C</sub>      |                | 1.2     |         | 1.4     |         | 1.9      | ns   |

| $t_{\rm CO}$        |                | 0.5     |         | 0.6     |         | 0.8      | ns   |

| t <sub>COMB</sub>   |                | 0.5     |         | 0.6     |         | 0.8      | ns   |

| t <sub>SU</sub>     | 1.1            |         | 1.3     |         | 1.7     |          | ns   |

| t <sub>H</sub>      | 0.6            |         | 0.7     |         | 0.9     |          | ns   |

| t <sub>PRE</sub>    |                | 0.5     |         | 0.6     | _       | 0.9      | ns   |

| t <sub>CLR</sub>    |                | 0.5     |         | 0.6     |         | 0.9      | ns   |

| t <sub>CH</sub>     | 3.0            |         | 3.5     |         | 4.0     |          | ns   |

| t <sub>CL</sub>     | 3.0            |         | 3.5     |         | 4.0     |          | ns   |

| Symbol              | -1 Spee | d Grade | -2 Speed Grade |     | -3 Spee | d Grade | Unit |

|---------------------|---------|---------|----------------|-----|---------|---------|------|

|                     | Min     | Max     | Min            | Max | Min     | Max     |      |

|                     |         | 1.3     |                | 1.5 |         | 2.0     | ns   |

| ioc                 |         | 0.2     |                | 0.3 |         | 0.3     | ns   |

| ioco                |         | 0.2     |                | 0.3 |         | 0.4     | ns   |

| <sup>t</sup> іосомв |         | 0.6     |                | 0.7 |         | 0.9     | ns   |

| t <sub>iosu</sub>   | 0.8     |         | 1.0            |     | 1.3     |         | ns   |

| Symbol                 | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | Unit |    |

|------------------------|----------------|-----|---------|---------|---------|------|----|

|                        | Min            | Max | Min     | Max     | Min     | Max  |    |

| t <sub>EABDATA1</sub>  |                | 3.3 |         | 3.9     |         | 5.2  | ns |

| t <sub>EABDATA2</sub>  |                | 1.0 |         | 1.3     |         | 1.7  | ns |

| t <sub>EABWE1</sub>    |                | 2.6 |         | 3.1     |         | 4.1  | ns |

| t <sub>EABWE2</sub>    |                | 2.7 |         | 3.2     |         | 4.3  | ns |

| t <sub>EABCLK</sub>    |                | 0.0 |         | 0.0     |         | 0.0  | ns |

| t <sub>EABCO</sub>     |                | 1.2 |         | 1.4     |         | 1.8  | ns |

| t <sub>EABBYPASS</sub> |                | 0.1 |         | 0.2     |         | 0.2  | ns |

| t <sub>EABSU</sub>     | 1.4            |     | 1.7     |         | 2.2     |      | ns |

| t <sub>EABH</sub>      | 0.1            |     | 0.1     |         | 0.1     |      | ns |

| $t_{AA}$               |                | 4.5 |         | 5.4     |         | 7.3  | ns |

| $t_{WP}$               | 2.0            |     | 2.4     |         | 3.2     |      | ns |

| t <sub>WDSU</sub>      | 0.7            |     | 0.8     |         | 1.1     |      | ns |

| t <sub>WDH</sub>       | 0.5            |     | 0.6     |         | 0.7     |      | ns |

| t <sub>WASU</sub>      | 0.6            |     | 0.7     |         | 0.9     |      | ns |

| t <sub>WAH</sub>       | 0.9            |     | 1.1     |         | 1.5     |      | ns |

| $t_{WO}$               |                | 3.3 |         | 3.9     |         | 5.2  | ns |

| $t_{DD}$               |                | 3.3 |         | 3.9     |         | 5.2  | ns |

| t <sub>EABOUT</sub>    |                | 0.1 |         | 0.1     |         | 0.2  | ns |

| t <sub>EABCH</sub>     | 3.0            |     | 3.5     |         | 4.0     |      | ns |

| t <sub>EABCL</sub>     | 3.03           |     | 3.5     |         | 4.0     |      | ns |

| Symbol                   | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | Unit |    |

|--------------------------|----------------|-----|---------|---------|---------|------|----|

|                          | Min            | Max | Min     | Max     | Min     | Max  |    |

| t <sub>DIN2IOE</sub>     |                | 4.2 |         | 5.0     |         | 6.5  | ns |

| t <sub>DIN2LE</sub>      |                | 2.2 |         | 2.6     |         | 3.4  | ns |

| t <sub>DIN2DATA</sub>    |                | 4.3 |         | 5.2     |         | 7.1  | ns |

| t <sub>DCLK2IOE</sub>    |                | 4.2 |         | 4.9     |         | 6.6  | ns |

| t <sub>DCLK2LE</sub>     |                | 2.2 |         | 2.6     |         | 3.4  | ns |

| t <sub>SAMELAB</sub>     |                | 0.1 |         | 0.1     |         | 0.2  | ns |

| t <sub>SAMEROW</sub>     |                | 2.2 |         | 2.4     |         | 2.9  | ns |

| t <sub>SAME</sub> COLUMN |                | 0.8 |         | 1.0     |         | 1.4  | ns |

| t <sub>DIFFROW</sub>     |                | 3.0 |         | 3.4     |         | 4.3  | ns |

| t <sub>TWOROWS</sub>     |                | 5.2 |         | 5.8     |         | 7.2  | ns |

| t <sub>LEPERIPH</sub>    |                | 1.8 |         | 2.2     |         | 2.8  | ns |

| t <sub>LABCARRY</sub>    |                | 0.5 |         | 0.5     |         | 0.7  | ns |

| t <sub>LABCASC</sub>     |                | 0.9 |         | 1.0     |         | 1.5  | ns |

| Table 90. EPF10K10A External Reference Timing Parameters Note (1) |         |          |                    |      |     |                |    |  |  |  |

|-------------------------------------------------------------------|---------|----------|--------------------|------|-----|----------------|----|--|--|--|

| Symbol                                                            | -1 Spec | ed Grade | nde -2 Speed Grade |      |     | -3 Speed Grade |    |  |  |  |

|                                                                   | Min     | Max      | Min                | Max  | Min | Max            |    |  |  |  |

| t <sub>DRR</sub>                                                  |         | 10.0     |                    | 12.0 |     | 16.0           | ns |  |  |  |

| t <sub>INSU</sub> (2), (3)                                        | 1.6     |          | 2.1                |      | 2.8 |                | ns |  |  |  |

| t <sub>INH</sub> (3)                                              | 0.0     |          | 0.0                |      | 0.0 |                | ns |  |  |  |

| t <sub>outco</sub> (3)                                            | 2.0     | 5.8      | 2.0                | 6.9  | 2.0 | 9.2            | ns |  |  |  |

| Table 91. EPF10K10A Device External Bidirectional Timing Parameters       Note (1) |         |                |     |                |     |                |    |  |  |  |

|------------------------------------------------------------------------------------|---------|----------------|-----|----------------|-----|----------------|----|--|--|--|

| Symbol                                                                             | -2 Spee | -2 Speed Grade |     | -3 Speed Grade |     | -4 Speed Grade |    |  |  |  |

|                                                                                    | Min     | Max            | Min | Max            | Min | Max            |    |  |  |  |

| t <sub>INSUBIDIR</sub>                                                             | 2.4     |                | 3.3 |                | 4.5 |                | ns |  |  |  |

| t <sub>INHBIDIR</sub>                                                              | 0.0     |                | 0.0 |                | 0.0 |                | ns |  |  |  |

| toutcobidir                                                                        | 2.0     | 5.8            | 2.0 | 6.9            | 2.0 | 9.2            | ns |  |  |  |

| t <sub>XZBIDIR</sub>                                                               |         | 6.3            |     | 7.5            |     | 9.9            | ns |  |  |  |

| t <sub>ZXBIDIR</sub>                                                               |         | 6.3            |     | 7.5            |     | 9.9            | ns |  |  |  |

| Symbol              | -1 Spee | -1 Speed Grade |     | d Grade | -3 Spee | Unit |    |

|---------------------|---------|----------------|-----|---------|---------|------|----|

|                     | Min     | Max            | Min | Max     | Min     | Max  |    |

| t <sub>IOH</sub>    | 0.9     |                | 1.1 |         | 1.4     |      | ns |

| t <sub>IOCLR</sub>  |         | 0.7            |     | 0.8     |         | 1.0  | ns |

| t <sub>OD1</sub>    |         | 1.9            |     | 2.2     |         | 2.9  | ns |

| tOD2                |         | 4.8            |     | 5.6     |         | 7.3  | ns |

| t <sub>OD3</sub>    |         | 7.0            |     | 8.2     |         | 10.8 | ns |

| XZ                  |         | 2.2            |     | 2.6     |         | 3.4  | ns |

| ZX1                 |         | 2.2            |     | 2.6     |         | 3.4  | ns |

| ZX2                 |         | 5.1            |     | 6.0     |         | 7.8  | ns |

| ZX3                 |         | 7.3            |     | 8.6     |         | 11.3 | ns |

| INREG               |         | 4.4            |     | 5.2     |         | 6.8  | ns |

| IOFD                |         | 3.8            |     | 4.5     |         | 5.9  | ns |

| t <sub>INCOMB</sub> |         | 3.8            |     | 4.5     |         | 5.9  | ns |

| Table 1               | Table 113. ClockLock & ClockBoost Parameters (Part 2 of 2)                                                   |     |     |      |      |  |  |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|------|------|--|--|--|--|--|

| Symbol                | Parameter                                                                                                    | Min | Тур | Max  | Unit |  |  |  |  |  |

| f <sub>CLKDEV1</sub>  | Input deviation from user specification in MAX+PLUS II (ClockBoost clock multiplication factor equals 1) (1) |     |     | ±1   | MHz  |  |  |  |  |  |

| f <sub>CLKDEV2</sub>  | Input deviation from user specification in MAX+PLUS II (ClockBoost clock multiplication factor equals 2) (1) |     |     | ±0.5 | MHz  |  |  |  |  |  |

| t <sub>INCLKSTB</sub> | Input clock stability (measured between adjacent clocks)                                                     |     |     | 100  | ps   |  |  |  |  |  |

| t <sub>LOCK</sub>     | Time required for ClockLock or ClockBoost to acquire lock (2)                                                |     |     | 10   | μs   |  |  |  |  |  |

| t <sub>JITTER</sub>   | Jitter on ClockLock or ClockBoost-generated clock (3)                                                        |     |     | 1    | ns   |  |  |  |  |  |

| $t_{OUTDUTY}$         | Duty cycle for ClockLock or ClockBoost-generated clock                                                       | 40  | 50  | 60   | %    |  |  |  |  |  |

#### Notes:

- (1) To implement the ClockLock and ClockBoost circuitry with the MAX+PLUS II software, designers must specify the input frequency. The MAX+PLUS II software tunes the PLL in the ClockLock and ClockBoost circuitry to this frequency. The f<sub>CLKDEV</sub> parameter specifies how much the incoming clock can differ from the specified frequency during device operation. Simulation does not reflect this parameter.

- (2) During device configuration, the ClockLock and ClockBoost circuitry is configured before the rest of the device. If the incoming clock is supplied during configuration, the ClockLock and ClockBoost circuitry locks during configuration, because the t<sub>LOCK</sub> value is less than the time required for configuration.

- (3) The  $t_{IITTER}$  specification is measured under long-term observation.

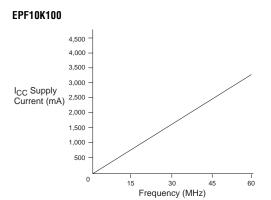

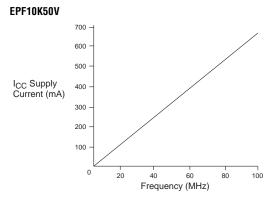

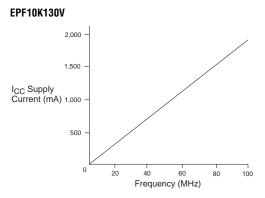

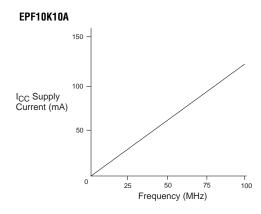

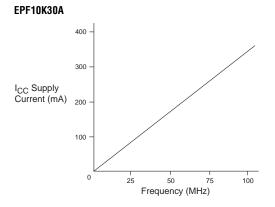

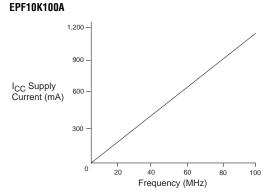

# Power Consumption

The supply power (P) for FLEX 10K devices can be calculated with the following equation:

$$P = P_{INT} + P_{IO} = (I_{CCSTANDBY} + I_{CCACTIVE}) \times V_{CC} + P_{IO}$$

Typical  $I_{CCSTANDBY}$  values are shown as  $I_{CC0}$  in the FLEX 10K device DC operating conditions tables on pages 46, 49, and 52 of this data sheet. The  $I_{CCACTIVE}$  value depends on the switching frequency and the application logic. This value is calculated based on the amount of current that each LE typically consumes. The  $P_{IO}$  value, which depends on the device output load characteristics and switching frequency, can be calculated using the guidelines given in *Application Note 74 (Evaluating Power for Altera Devices)*.

Compared to the rest of the device, the embedded array consumes a negligible amount of power. Therefore, the embedded array can be ignored when calculating supply current.

The I<sub>CCACTIVE</sub> value is calculated with the following equation:

$$I_{CCACTIVE} = K \times \mathbf{f_{MAX}} \times N \times \mathbf{tog_{LC}} \times \frac{\mu A}{MHz \times LE}$$

The parameters in this equation are shown below:

Figure 32. I<sub>CCACTIVE</sub> vs. Operating Frequency (Part 2 of 3)