# E·XFL

### Intel - EPF10K40RC240-4N Datasheet

Welcome to E-XFL.COM

### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 288                                                         |

| Number of Logic Elements/Cells | 2304                                                        |

| Total RAM Bits                 | 16384                                                       |

| Number of I/O                  | 189                                                         |

| Number of Gates                | 93000                                                       |

| Voltage - Supply               | 4.75V ~ 5.25V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 70°C (TA)                                             |

| Package / Case                 | 240-BFQFP Exposed Pad                                       |

| Supplier Device Package        | 240-RQFP (32x32)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k40rc240-4n |

|                                |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### FLEX 10K Embedded Programmable Logic Device Family Data Sheet

| Device     | 84-Pin<br>PLCC | 100-Pin<br>TQFP | 144-Pin TQFP | 208-Pin<br>PQFP<br>RQFP | 240-Pin<br>PQFP<br>RQFP |

|------------|----------------|-----------------|--------------|-------------------------|-------------------------|

| EPF10K10   | 59             |                 | 102          | 134                     |                         |

| EPF10K10A  |                | 66              | 102          | 134                     |                         |

| EPF10K20   |                |                 | 102          | 147                     | 189                     |

| EPF10K30   |                |                 |              | 147                     | 189                     |

| EPF10K30A  |                |                 | 102          | 147                     | 189                     |

| EPF10K40   |                |                 |              | 147                     | 189                     |

| EPF10K50   |                |                 |              |                         | 189                     |

| EPF10K50V  |                |                 |              |                         | 189                     |

| EPF10K70   |                |                 |              |                         | 189                     |

| EPF10K100  |                |                 |              |                         |                         |

| EPF10K100A |                |                 |              |                         | 189                     |

| EPF10K130V |                |                 |              |                         |                         |

| EPF10K250A |                |                 |              |                         |                         |

| Device     | 503-Pin | 599-Pin | 256-Pin      | 356-Pin | 484-Pin      | 600-Pin | 403-Pin |

|------------|---------|---------|--------------|---------|--------------|---------|---------|

|            | PGA     | PGA     | FineLine BGA | BGA     | FineLine BGA | BGA     | PGA     |

| EPF10K10   |         |         |              |         |              |         |         |

| EPF10K10A  |         |         | 150          |         | 150 (2)      |         |         |

| EPF10K20   |         |         |              |         |              |         |         |

| EPF10K30   |         |         |              | 246     |              |         |         |

| EPF10K30A  |         |         | 191          | 246     | 246          |         |         |

| EPF10K40   |         |         |              |         |              |         |         |

| EPF10K50   |         |         |              | 274     |              |         | 310     |

| EPF10K50V  |         |         |              | 274     |              |         |         |

| EPF10K70   | 358     |         |              |         |              |         |         |

| EPF10K100  | 406     |         |              |         |              |         |         |

| EPF10K100A |         |         |              | 274     | 369          | 406     |         |

| EPF10K130V |         | 470     |              |         |              | 470     |         |

| EPF10K250A |         | 470     |              |         |              | 470     |         |

Г

For more information, see the following documents:

- Configuration Devices for APEX & FLEX Devices Data Sheet

- BitBlaster Serial Download Cable Data Sheet

- ByteBlasterMV Parallel Port Download Cable Data Sheet

- Application Note 116 (Configuring APEX 20K, FLEX 10K & FLEX 6000 Devices)

FLEX 10K devices are supported by Altera development systems; single, integrated packages that offer schematic, text (including AHDL), and waveform design entry, compilation and logic synthesis, full simulation and worst-case timing analysis, and device configuration. The Altera software provides EDIF 2 0 0 and 3 0 0, LPM, VHDL, Verilog HDL, and other interfaces for additional design entry and simulation support from other industry-standard PC- and UNIX workstation-based EDA tools.

The Altera software works easily with common gate array EDA tools for synthesis and simulation. For example, the Altera software can generate Verilog HDL files for simulation with tools such as Cadence Verilog-XL. Additionally, the Altera software contains EDA libraries that use devicespecific features such as carry chains which are used for fast counter and arithmetic functions. For instance, the Synopsys Design Compiler library supplied with the Altera development systems include DesignWare functions that are optimized for the FLEX 10K architecture.

The Altera development systems run on Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800 workstations.

See the MAX+PLUS II Programmable Logic Development System & Software Data Sheet for more information.

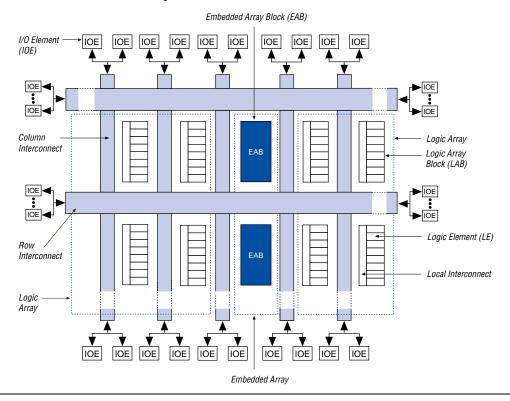

# Functional Description

Each FLEX 10K device contains an embedded array to implement memory and specialized logic functions, and a logic array to implement general logic.

The embedded array consists of a series of EABs. When implementing memory functions, each EAB provides 2,048 bits, which can be used to create RAM, ROM, dual-port RAM, or first-in first-out (FIFO) functions. When implementing logic, each EAB can contribute 100 to 600 gates towards complex logic functions, such as multipliers, microcontrollers, state machines, and DSP functions. EABs can be used independently, or multiple EABs can be combined to implement larger functions.

Figure 1. FLEX 10K Device Block Diagram

FLEX 10K devices provide six dedicated inputs that drive the flipflops' control inputs to ensure the efficient distribution of high-speed, low-skew (less than 1.5 ns) control signals. These signals use dedicated routing channels that provide shorter delays and lower skews than the FastTrack Interconnect. Four of the dedicated inputs drive four global signals. These four global signals can also be driven by internal logic, providing an ideal solution for a clock divider or an internally generated asynchronous clear signal that clears many registers in the device.

### Embedded Array Block

The EAB is a flexible block of RAM with registers on the input and output ports, and is used to implement common gate array megafunctions. The EAB is also suitable for functions such as multipliers, vector scalars, and error correction circuits, because it is large and flexible. These functions can be combined in applications such as digital filters and microcontrollers.

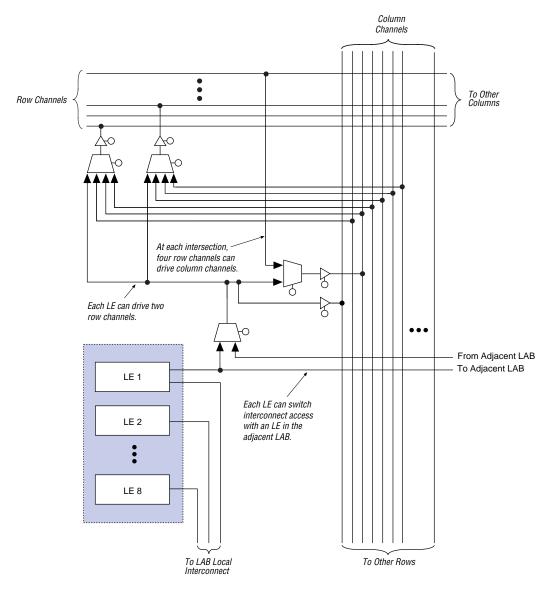

### Figure 11. LAB Connections to Row & Column Interconnect

Each IOE selects the clock, clear, clock enable, and output enable controls from a network of I/O control signals called the peripheral control bus. The peripheral control bus uses high-speed drivers to minimize signal skew across devices; it provides up to 12 peripheral control signals that can be allocated as follows:

- Up to eight output enable signals

- Up to six clock enable signals

- Up to two clock signals

- Up to two clear signals

If more than six clock enable or eight output enable signals are required, each IOE on the device can be controlled by clock enable and output enable signals driven by specific LEs. In addition to the two clock signals available on the peripheral control bus, each IOE can use one of two dedicated clock pins. Each peripheral control signal can be driven by any of the dedicated input pins or the first LE of each LAB in a particular row. In addition, an LE in a different row can drive a column interconnect, which causes a row interconnect to drive the peripheral control signal. The chip-wide reset signal will reset all IOE registers, overriding any other control signals.

Tables 8 and 9 list the sources for each peripheral control signal, and the rows that can drive global signals. These tables also show how the output enable, clock enable, clock, and clear signals share 12 peripheral control signals.

| Symbol           | Parameter                                   | Conditions                                                    | Min                     | Тур | Max                      | Unit |

|------------------|---------------------------------------------|---------------------------------------------------------------|-------------------------|-----|--------------------------|------|

| V <sub>IH</sub>  | High-level input<br>voltage                 |                                                               | 2.0                     |     | V <sub>CCINT</sub> + 0.5 | V    |

| VIL              | Low-level input voltage                     |                                                               | -0.5                    |     | 0.8                      | V    |

| V <sub>OH</sub>  | 5.0-V high-level TTL<br>output voltage      | $I_{OH} = -4 \text{ mA DC}, V_{CCIO} = 4.75 \text{ V}$<br>(7) | 2.4                     |     |                          | V    |

|                  | 3.3-V high-level TTL<br>output voltage      | I <sub>OH</sub> = -4 mA DC, V <sub>CCIO</sub> = 3.00 V<br>(7) | 2.4                     |     |                          | V    |

|                  | 3.3-V high-level CMOS output voltage        | $I_{OH} = -0.1 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V}$ (7)  | V <sub>CCIO</sub> – 0.2 |     |                          | V    |

| V <sub>OL</sub>  | 5.0-V low-level TTL<br>output voltage       | I <sub>OL</sub> = 12 mA DC, V <sub>CCIO</sub> = 4.75 V<br>(8) |                         |     | 0.45                     | V    |

|                  | 3.3-V low-level TTL<br>output voltage       | I <sub>OL</sub> = 12 mA DC, V <sub>CCIO</sub> = 3.00 V<br>(8) |                         |     | 0.45                     | V    |

|                  | 3.3-V low-level CMOS<br>output voltage      | $I_{OL} = 0.1 \text{ mA DC}, V_{CCIO} = 3.00 \text{ V}$ (8)   |                         |     | 0.2                      | V    |

| I <sub>I</sub>   | Input pin leakage<br>current                | $V_1 = V_{CC}$ or ground (9)                                  | -10                     |     | 10                       | μA   |

| I <sub>OZ</sub>  | Tri-stated I/O pin<br>leakage current       | $V_{O} = V_{CC}$ or ground<br>(9)                             | -40                     |     | 40                       | μA   |

| I <sub>CC0</sub> | V <sub>CC</sub> supply current<br>(standby) | V <sub>I</sub> = ground, no load                              |                         | 0.5 | 10                       | mA   |

| Table 2 | 0. 5.0-V Device Capacitance of | EPF10K10, EPF10K20 & EPF10K30 | ) Devices | Note (10) |      |

|---------|--------------------------------|-------------------------------|-----------|-----------|------|

| Symbol  | Parameter                      | Conditions                    | Min       | Max       | Unit |

| C <sub>IN</sub>  | Input capacitance                        | V <sub>IN</sub> = 0 V, f = 1.0 MHz  | 8  | pF |

|------------------|------------------------------------------|-------------------------------------|----|----|

| INCLIV           | Input capacitance on dedicated clock pin | V <sub>IN</sub> = 0 V, f = 1.0 MHz  | 12 | pF |

| C <sub>OUT</sub> | Output capacitance                       | V <sub>OUT</sub> = 0 V, f = 1.0 MHz | 8  | pF |

| Table 2            | Table 21. 5.0-V Device Capacitance of EPF10K40, EPF10K50, EPF10K70 & EPF10K100 Devices       Note (10) |                                     |     |     |      |  |  |  |  |  |  |

|--------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------|-----|-----|------|--|--|--|--|--|--|

| Symbol             | Parameter                                                                                              | Conditions                          | Min | Max | Unit |  |  |  |  |  |  |

| C <sub>IN</sub>    | Input capacitance                                                                                      | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 10  | pF   |  |  |  |  |  |  |

| C <sub>INCLK</sub> | Input capacitance on dedicated clock pin                                                               | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 15  | pF   |  |  |  |  |  |  |

| C <sub>OUT</sub>   | Output capacitance                                                                                     | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 10  | pF   |  |  |  |  |  |  |

#### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $\hat{V}_{CC}$  rise time is 100 ms.  $V_{CC}$  must rise monotonically.

- (5) Typical values are for  $T_A = 25^\circ \text{ C}$  and  $V_{CC} = 5.0 \text{ V}$ .

- (6) These values are specified under the Recommended Operation Condition shown in Table 18 on page 45.

- (7) The I<sub>OH</sub> parameter refers to high-level TTL or CMOS output current.

- (8) The I<sub>OL</sub> parameter refers to low-level TTL or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (9) This value is specified for normal device operation. The value may vary during power-up.

- (10) Capacitance is sample-tested only.

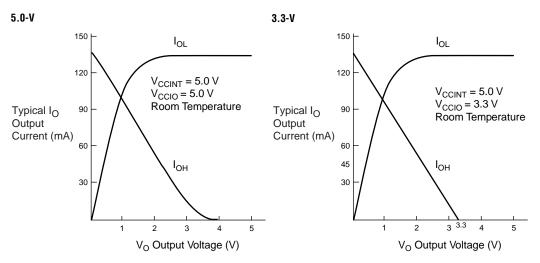

Figure 20 shows the typical output drive characteristics of FLEX 10K devices with 5.0-V and 3.3-V  $V_{CCIO}$ . The output driver is compliant with the 5.0-V *PCI Local Bus Specification, Revision 2.2* (for 5.0-V  $V_{CCIO}$ ).

Figure 20. Output Drive Characteristics of FLEX 10K Devices

Tables 22 through 25 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for EPF10K50V and EPF10K130V devices.

| Table 22. EPF10K50V & EPF10K130V Device Absolute Maximum Ratings       Note (1) |                            |                              |      |      |      |  |  |

|---------------------------------------------------------------------------------|----------------------------|------------------------------|------|------|------|--|--|

| Symbol                                                                          | Parameter                  | Conditions                   | Min  | Max  | Unit |  |  |

| V <sub>CC</sub>                                                                 | Supply voltage             | With respect to ground (2)   | -0.5 | 4.6  | V    |  |  |

| VI                                                                              | DC input voltage           |                              | -2.0 | 5.75 | V    |  |  |

| I <sub>OUT</sub>                                                                | DC output current, per pin |                              | -25  | 25   | mA   |  |  |

| T <sub>STG</sub>                                                                | Storage temperature        | No bias                      | -65  | 150  | °C   |  |  |

| T <sub>AMB</sub>                                                                | Ambient temperature        | Under bias                   | -65  | 135  | °C   |  |  |

| ТJ                                                                              | Junction temperature       | Ceramic packages, under bias |      | 150  | °C   |  |  |

|                                                                                 |                            | RQFP and BGA packages, under |      | 135  | °C   |  |  |

|                                                                                 |                            | bias                         |      |      |      |  |  |

| Table 2            | Table 23. EPF10K50V & EPF10K130V Device Recommended Operating Conditions |                    |             |                   |      |  |  |  |  |  |

|--------------------|--------------------------------------------------------------------------|--------------------|-------------|-------------------|------|--|--|--|--|--|

| Symbol             | Parameter                                                                | Conditions         | Min         | Max               | Unit |  |  |  |  |  |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers                      | (3), (4)           | 3.00 (3.00) | 3.60 (3.60)       | V    |  |  |  |  |  |

| V <sub>CCIO</sub>  | Supply voltage for output<br>buffers                                     | (3), (4)           | 3.00 (3.00) | 3.60 (3.60)       | V    |  |  |  |  |  |

| VI                 | Input voltage                                                            | (5)                | -0.5        | 5.75              | V    |  |  |  |  |  |

| Vo                 | Output voltage                                                           |                    | 0           | V <sub>CCIO</sub> | V    |  |  |  |  |  |

| Τ <sub>A</sub>     | Ambient temperature                                                      | For commercial use | 0           | 70                | °C   |  |  |  |  |  |

|                    |                                                                          | For industrial use | -40         | 85                | °C   |  |  |  |  |  |

| ΤJ                 | Operating temperature                                                    | For commercial use | 0           | 85                | °C   |  |  |  |  |  |

|                    |                                                                          | For industrial use | -40         | 100               | °C   |  |  |  |  |  |

| t <sub>R</sub>     | Input rise time                                                          |                    |             | 40                | ns   |  |  |  |  |  |

| t <sub>F</sub>     | Input fall time                                                          |                    |             | 40                | ns   |  |  |  |  |  |

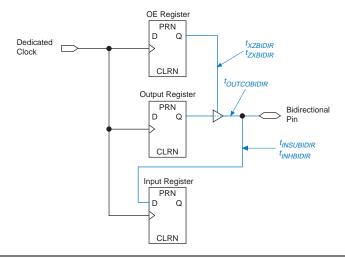

Figure 28. Synchronous Bidirectional Pin External Timing Model

Tables 32 through 36 describe the FLEX 10K device internal timing parameters. These internal timing parameters are expressed as worst-case values. Using hand calculations, these parameters can be used to estimate design performance. However, before committing designs to silicon, actual worst-case performance should be modeled using timing simulation and analysis. Tables 37 through 38 describe FLEX 10K external timing parameters.

| Symbol              | Parameter                               | Conditions |

|---------------------|-----------------------------------------|------------|

| t <sub>LUT</sub>    | LUT delay for data-in                   |            |

| t <sub>CLUT</sub>   | LUT delay for carry-in                  |            |

| t <sub>RLUT</sub>   | LUT delay for LE register feedback      |            |

| t <sub>PACKED</sub> | Data-in to packed register delay        |            |

| t <sub>EN</sub>     | LE register enable delay                |            |

| tcico               | Carry-in to carry-out delay             |            |

| t <sub>CGEN</sub>   | Data-in to carry-out delay              |            |

| t <sub>CGENR</sub>  | LE register feedback to carry-out delay |            |

| t <sub>CASC</sub>   | Cascade-in to cascade-out delay         |            |

| t <sub>C</sub>      | LE register control signal delay        |            |

| t <sub>CO</sub>     | LE register clock-to-output delay       |            |

| t <sub>COMB</sub>   | Combinatorial delay                     |            |

| Symbol                  | -2 Speed Grade |      | -3 Speed Grade |      | -4 Speed Grade |      | Unit |

|-------------------------|----------------|------|----------------|------|----------------|------|------|

|                         | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>DIN2IOE</sub>    |                | 6.6  |                | 7.3  |                | 8.8  | ns   |

| t <sub>DIN2LE</sub>     |                | 4.2  |                | 4.8  |                | 6.0  | ns   |

| t <sub>DIN2DATA</sub>   |                | 6.5  |                | 7.1  |                | 10.8 | ns   |

| t <sub>DCLK2IOE</sub>   |                | 5.5  |                | 6.2  |                | 7.7  | ns   |

| t <sub>DCLK2LE</sub>    |                | 4.2  |                | 4.8  |                | 6.0  | ns   |

| t <sub>SAMELAB</sub>    |                | 0.4  |                | 0.4  |                | 0.5  | ns   |

| t <sub>SAMEROW</sub>    |                | 4.8  |                | 4.9  |                | 5.5  | ns   |

| t <sub>SAMECOLUMN</sub> |                | 3.3  |                | 3.4  |                | 3.7  | ns   |

| t <sub>DIFFROW</sub>    |                | 8.1  |                | 8.3  |                | 9.2  | ns   |

| t <sub>TWOROWS</sub>    |                | 12.9 |                | 13.2 |                | 14.7 | ns   |

| t <sub>LEPERIPH</sub>   |                | 5.5  |                | 5.7  |                | 6.5  | ns   |

| t <sub>LABCARRY</sub>   |                | 0.8  |                | 0.9  |                | 1.1  | ns   |

| t <sub>LABCASC</sub>    |                | 2.7  |                | 3.0  |                | 3.2  | ns   |

| Table 62. EPF10K70 Device External Timing Parameters       Note (1) |         |                |     |          |                |      |      |  |  |  |  |

|---------------------------------------------------------------------|---------|----------------|-----|----------|----------------|------|------|--|--|--|--|

| Symbol                                                              | -2 Spee | -2 Speed Grade |     | ed Grade | -4 Speed Grade |      | Unit |  |  |  |  |

|                                                                     | Min     | Max            | Min | Max      | Min            | Max  |      |  |  |  |  |

| t <sub>DRR</sub>                                                    |         | 17.2           |     | 19.1     |                | 24.2 | ns   |  |  |  |  |

| t <sub>INSU</sub> (2), (3)                                          | 6.6     |                | 7.3 |          | 8.0            |      | ns   |  |  |  |  |

| t <sub>INH</sub> (3)                                                | 0.0     |                | 0.0 |          | 0.0            |      | ns   |  |  |  |  |

| t <sub>оитсо</sub> (3)                                              | 2.0     | 9.9            | 2.0 | 11.1     | 2.0            | 14.3 | ns   |  |  |  |  |

Table 63. EPF10K70 Device External Bidirectional Timing Parameters

Note (1)

| Symbol                 | -2 Speed Grade |      | -3 Spee | ed Grade | -4 Spee | Unit |    |

|------------------------|----------------|------|---------|----------|---------|------|----|

|                        | Min            | Max  | Min     | Max      | Min     | Max  |    |

| t <sub>INSUBIDIR</sub> | 7.4            |      | 8.1     |          | 10.4    |      | ns |

| t <sub>INHBIDIR</sub>  | 0.0            |      | 0.0     |          | 0.0     |      | ns |

| toutcobidir            | 2.0            | 9.9  | 2.0     | 11.1     | 2.0     | 14.3 | ns |

| t <sub>XZBIDIR</sub>   |                | 13.7 |         | 15.4     |         | 18.5 | ns |

| t <sub>ZXBIDIR</sub>   |                | 13.7 |         | 15.4     |         | 18.5 | ns |

Г

| Table 68. EPF10K100 Device Interconn                                    | -        |           | 1       | Note (1) |         |      |    |

|-------------------------------------------------------------------------|----------|-----------|---------|----------|---------|------|----|

| Symbol                                                                  | -3DX Spe | eed Grade | -3 Spee | ed Grade | -4 Spee | Unit |    |

|                                                                         | Min      | Max       | Min     | Max      | Min     | Max  |    |

| t <sub>DIN2IOE</sub>                                                    |          | 10.3      |         | 10.3     |         | 12.2 | ns |

| t <sub>DIN2LE</sub>                                                     |          | 4.8       |         | 4.8      |         | 6.0  | ns |

| t <sub>DIN2DATA</sub>                                                   |          | 7.3       |         | 7.3      |         | 11.0 | ns |

| t <sub>DCLK2IOE</sub> without ClockLock or<br>ClockBoost circuitry      |          | 6.2       |         | 6.2      |         | 7.7  | ns |

| <i>t<sub>DCLK2IOE</sub></i> with ClockLock or ClockBoost circuitry      |          | 2.3       |         | -        |         | _    | ns |

| <i>t<sub>DCLK2LE</sub></i> without ClockLock or<br>ClockBoost circuitry |          | 4.8       |         | 4.8      |         | 6.0  | ns |

| <i>t<sub>DCLK2LE</sub></i> with ClockLock or ClockBoost circuitry       |          | 2.3       |         | -        |         | _    | ns |

| t <sub>SAMELAB</sub>                                                    |          | 0.4       |         | 0.4      |         | 0.5  | ns |

| t <sub>SAMEROW</sub>                                                    |          | 4.9       |         | 4.9      |         | 5.5  | ns |

| t <sub>SAMECOLUMN</sub>                                                 |          | 5.1       |         | 5.1      |         | 5.4  | ns |

| t <sub>DIFFROW</sub>                                                    |          | 10.0      |         | 10.0     |         | 10.9 | ns |

| t <sub>TWOROWS</sub>                                                    |          | 14.9      |         | 14.9     |         | 16.4 | ns |

| t <sub>LEPERIPH</sub>                                                   |          | 6.9       |         | 6.9      |         | 8.1  | ns |

| t <sub>LABCARRY</sub>                                                   |          | 0.9       |         | 0.9      |         | 1.1  | ns |

| t <sub>LABCASC</sub>                                                    |          | 3.0       |         | 3.0      |         | 3.2  | ns |

| Symbol              | -2 Spee | d Grade | -3 Speed Grade |      | -4 Spee | Unit |    |

|---------------------|---------|---------|----------------|------|---------|------|----|

|                     | Min     | Max     | Min            | Max  | Min     | Max  |    |

| t <sub>IOD</sub>    |         | 1.3     |                | 1.6  |         | 2.0  | ns |

| t <sub>IOC</sub>    |         | 0.4     |                | 0.5  |         | 0.7  | ns |

| t <sub>IOCO</sub>   |         | 0.3     |                | 0.4  |         | 0.5  | ns |

| t <sub>IOCOMB</sub> |         | 0.0     |                | 0.0  |         | 0.0  | ns |

| t <sub>IOSU</sub>   | 2.6     |         | 3.3            |      | 3.8     |      | ns |

| t <sub>IOH</sub>    | 0.0     |         | 0.0            |      | 0.0     |      | ns |

| t <sub>IOCLR</sub>  |         | 1.7     |                | 2.2  |         | 2.7  | ns |

| t <sub>OD1</sub>    |         | 3.5     |                | 4.4  |         | 5.0  | ns |

| t <sub>OD2</sub>    |         | -       |                | -    |         | -    | ns |

| t <sub>OD3</sub>    |         | 8.2     |                | 8.1  |         | 9.7  | ns |

| t <sub>XZ</sub>     |         | 4.9     |                | 6.3  |         | 7.4  | ns |

| t <sub>ZX1</sub>    |         | 4.9     |                | 6.3  |         | 7.4  | ns |

| t <sub>ZX2</sub>    |         | _       |                | -    |         | -    | ns |

| t <sub>ZX3</sub>    |         | 9.6     |                | 10.0 |         | 12.1 | ns |

| t <sub>INREG</sub>  |         | 7.9     |                | 10.0 |         | 12.6 | ns |

| t <sub>IOFD</sub>   |         | 6.2     |                | 7.9  |         | 9.9  | ns |

| t <sub>INCOMB</sub> |         | 6.2     |                | 7.9  |         | 9.9  | ns |

### FLEX 10K Embedded Programmable Logic Device Family Data Sheet

| Symbol                 | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | ed Grade | Unit |

|------------------------|---------|---------|---------|---------|---------|----------|------|

|                        | Min     | Max     | Min     | Max     | Min     | Max      |      |

| t <sub>EABDATA1</sub>  |         | 5.5     |         | 6.5     |         | 8.5      | ns   |

| t <sub>EABDATA2</sub>  |         | 1.1     |         | 1.3     |         | 1.8      | ns   |

| t <sub>EABWE1</sub>    |         | 2.4     |         | 2.8     |         | 3.7      | ns   |

| t <sub>EABWE2</sub>    |         | 2.1     |         | 2.5     |         | 3.2      | ns   |

| t <sub>EABCLK</sub>    |         | 0.0     |         | 0.0     |         | 0.2      | ns   |

| t <sub>EABCO</sub>     |         | 1.7     |         | 2.0     |         | 2.6      | ns   |

| t <sub>EABBYPASS</sub> |         | 0.0     |         | 0.0     |         | 0.3      | ns   |

| t <sub>EABSU</sub>     | 1.2     |         | 1.4     |         | 1.9     |          | ns   |

| t <sub>EABH</sub>      | 0.1     |         | 0.1     |         | 0.3     |          | ns   |

| t <sub>AA</sub>        |         | 4.2     |         | 5.0     |         | 6.5      | ns   |

| t <sub>WP</sub>        | 3.8     |         | 4.5     |         | 5.9     |          | ns   |

| t <sub>WDSU</sub>      | 0.1     |         | 0.1     |         | 0.2     |          | ns   |

| t <sub>WDH</sub>       | 0.1     |         | 0.1     |         | 0.2     |          | ns   |

| t <sub>WASU</sub>      | 0.1     |         | 0.1     |         | 0.2     |          | ns   |

| t <sub>WAH</sub>       | 0.1     |         | 0.1     |         | 0.2     |          | ns   |

| t <sub>WO</sub>        |         | 3.7     |         | 4.4     |         | 6.4      | ns   |

| t <sub>DD</sub>        |         | 3.7     |         | 4.4     |         | 6.4      | ns   |

| t <sub>EABOUT</sub>    |         | 0.0     |         | 0.1     |         | 0.6      | ns   |

| t <sub>EABCH</sub>     | 3.0     |         | 3.5     |         | 4.0     |          | ns   |

| t <sub>EABCL</sub>     | 3.8     |         | 4.5     |         | 5.9     |          | ns   |

| Symbol                 | OK100A Device EAB Intern<br>-1 Speed Grade |     | -2 Snee | -2 Speed Grade |      | -3 Speed Grade |      |  |

|------------------------|--------------------------------------------|-----|---------|----------------|------|----------------|------|--|

|                        | Min                                        | Max | Min     | Max            | Min  | Max            | Unit |  |

| t <sub>EABAA</sub>     |                                            | 6.8 |         | 7.8            |      | 9.2            | ns   |  |

| t <sub>EABRCCOMB</sub> | 6.8                                        |     | 7.8     |                | 9.2  |                | ns   |  |

| t <sub>EABRCREG</sub>  | 5.4                                        |     | 6.2     |                | 7.4  |                | ns   |  |

| t <sub>EABWP</sub>     | 3.2                                        |     | 3.7     |                | 4.4  |                | ns   |  |

| t <sub>EABWCCOMB</sub> | 3.4                                        |     | 3.9     |                | 4.7  |                | ns   |  |

| t <sub>EABWCREG</sub>  | 9.4                                        |     | 10.8    |                | 12.8 |                | ns   |  |

| t <sub>EABDD</sub>     |                                            | 6.1 |         | 6.9            |      | 8.2            | ns   |  |

| t <sub>EABDATACO</sub> |                                            | 2.1 |         | 2.3            |      | 2.9            | ns   |  |

| t <sub>EABDATASU</sub> | 3.7                                        |     | 4.3     |                | 5.1  |                | ns   |  |

| t <sub>EABDATAH</sub>  | 0.0                                        |     | 0.0     |                | 0.0  |                | ns   |  |

| t <sub>EABWESU</sub>   | 2.8                                        |     | 3.3     |                | 3.8  |                | ns   |  |

| t <sub>EABWEH</sub>    | 0.0                                        |     | 0.0     |                | 0.0  |                | ns   |  |

| t <sub>EABWDSU</sub>   | 3.4                                        |     | 4.0     |                | 4.6  |                | ns   |  |

| t <sub>EABWDH</sub>    | 0.0                                        |     | 0.0     |                | 0.0  |                | ns   |  |

| t <sub>EABWASU</sub>   | 1.9                                        |     | 2.3     |                | 2.6  |                | ns   |  |

| t <sub>EABWAH</sub>    | 0.0                                        |     | 0.0     |                | 0.0  |                | ns   |  |

| t <sub>EABWO</sub>     |                                            | 5.1 |         | 5.7            |      | 6.9            | ns   |  |

### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

# Tables 106 through 112 show EPF10K250A device internal and external timing parameters.

| Table 106. EPF10K250A Device LE Timing Microparameters       Note (1) |         |                |     |          |         |      |    |

|-----------------------------------------------------------------------|---------|----------------|-----|----------|---------|------|----|

| Symbol                                                                | -1 Spee | -1 Speed Grade |     | ed Grade | -3 Spee | Unit |    |

|                                                                       | Min     | Max            | Min | Max      | Min     | Max  |    |

| t <sub>LUT</sub>                                                      |         | 0.9            |     | 1.0      |         | 1.4  | ns |

| t <sub>CLUT</sub>                                                     |         | 1.2            |     | 1.3      |         | 1.6  | ns |

| t <sub>RLUT</sub>                                                     |         | 2.0            |     | 2.3      |         | 2.7  | ns |

| t <sub>PACKED</sub>                                                   |         | 0.4            |     | 0.4      |         | 0.5  | ns |

| t <sub>EN</sub>                                                       |         | 1.4            |     | 1.6      |         | 1.9  | ns |

| t <sub>CICO</sub>                                                     |         | 0.2            |     | 0.3      |         | 0.3  | ns |

| t <sub>CGEN</sub>                                                     |         | 0.4            |     | 0.6      |         | 0.6  | ns |

| t <sub>CGENR</sub>                                                    |         | 0.8            |     | 1.0      |         | 1.1  | ns |

| t <sub>CASC</sub>                                                     |         | 0.7            |     | 0.8      |         | 1.0  | ns |

| t <sub>C</sub>                                                        |         | 1.2            |     | 1.3      |         | 1.6  | ns |

| t <sub>CO</sub>                                                       |         | 0.6            |     | 0.7      |         | 0.9  | ns |

| t <sub>COMB</sub>                                                     |         | 0.5            |     | 0.6      |         | 0.7  | ns |

| t <sub>SU</sub>                                                       | 1.2     |                | 1.4 |          | 1.7     |      | ns |

| t <sub>H</sub>                                                        | 1.2     |                | 1.3 |          | 1.6     |      | ns |

| t <sub>PRE</sub>                                                      |         | 0.7            |     | 0.8      |         | 0.9  | ns |

| t <sub>CLR</sub>                                                      |         | 0.7            |     | 0.8      |         | 0.9  | ns |

| t <sub>CH</sub>                                                       | 2.5     |                | 3.0 |          | 3.5     |      | ns |

| t <sub>CL</sub>                                                       | 2.5     |                | 3.0 |          | 3.5     |      | ns |

| Table 109. EPF1        | IOK250A Devi | ce EAB Intern  | al Timing Ma | acroparamete | ers Note ( | 1)   | -  |

|------------------------|--------------|----------------|--------------|--------------|------------|------|----|

| Symbol                 | -1 Spee      | -1 Speed Grade |              | d Grade      | -3 Spee    | Unit |    |

|                        | Min          | Max            | Min          | Max          | Min        | Max  |    |

| t <sub>EABAA</sub>     |              | 6.1            |              | 6.8          |            | 8.2  | ns |

| t <sub>EABRCCOMB</sub> | 6.1          |                | 6.8          |              | 8.2        |      | ns |

| t <sub>EABRCREG</sub>  | 4.6          |                | 5.1          |              | 6.1        |      | ns |

| t <sub>EABWP</sub>     | 5.6          |                | 6.4          |              | 7.5        |      | ns |

| t <sub>EABWCCOMB</sub> | 5.8          |                | 6.6          |              | 7.9        |      | ns |

| t <sub>EABWCREG</sub>  | 15.8         |                | 17.8         |              | 21.0       |      | ns |

| t <sub>EABDD</sub>     |              | 5.7            |              | 6.4          |            | 7.8  | ns |

| t <sub>EABDATACO</sub> |              | 0.7            |              | 0.8          |            | 1.0  | ns |

| t <sub>EABDATASU</sub> | 4.5          |                | 5.1          |              | 5.9        |      | ns |

| t <sub>EABDATAH</sub>  | 0.0          |                | 0.0          |              | 0.0        |      | ns |

| t <sub>EABWESU</sub>   | 8.2          |                | 9.3          |              | 10.9       |      | ns |

| t <sub>EABWEH</sub>    | 0.0          |                | 0.0          |              | 0.0        |      | ns |

| t <sub>EABWDSU</sub>   | 1.7          |                | 1.8          |              | 2.1        |      | ns |

| t <sub>EABWDH</sub>    | 0.0          |                | 0.0          |              | 0.0        |      | ns |

| t <sub>EABWASU</sub>   | 0.9          |                | 0.9          |              | 1.0        |      | ns |

| t <sub>EABWAH</sub>    | 0.0          |                | 0.0          |              | 0.0        |      | ns |

| t <sub>EABWO</sub>     |              | 5.3            |              | 6.0          |            | 7.4  | ns |

### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 37 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

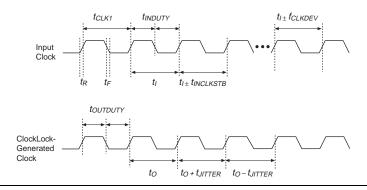

## ClockLock & ClockBoost Timing Parameters

For the ClockLock and ClockBoost circuitry to function properly, the incoming clock must meet certain requirements. If these specifications are not met, the circuitry may not lock onto the incoming clock, which generates an erroneous clock within the device. The clock generated by the ClockLock and ClockBoost circuitry must also meet certain specifications. If the incoming clock meets these requirements during configuration, the ClockLock and ClockBoost circuitry will lock onto the clock during configuration. The circuit will be ready for use immediately after configuration. Figure 31 illustrates the incoming and generated clock specifications.

### Figure 31. Specifications for the Incoming & Generated Clocks

The  $t_l$  parameter refers to the nominal input clock period; the  $t_0$  parameter refers to the nominal output clock period.

### Table 113 summarizes the ClockLock and ClockBoost parameters.

| Table 113. ClockLock & ClockBoost Parameters       (Part 1 of 2) |                                                                                  |    |  |      |      |  |  |  |

|------------------------------------------------------------------|----------------------------------------------------------------------------------|----|--|------|------|--|--|--|

| Symbol                                                           | I Parameter Min Typ Max                                                          |    |  |      | Unit |  |  |  |

| t <sub>R</sub>                                                   | Input rise time                                                                  |    |  | 2    | ns   |  |  |  |

| t <sub>F</sub>                                                   | Input fall time                                                                  |    |  | 2    | ns   |  |  |  |

| t <sub>INDUTY</sub>                                              | Input duty cycle                                                                 | 45 |  | 55   | %    |  |  |  |

| f <sub>CLK1</sub>                                                | Input clock frequency (ClockBoost clock multiplication factor equals 1)          | 30 |  | 80   | MHz  |  |  |  |

| t <sub>CLK1</sub>                                                | Input clock period (ClockBoost clock multiplication factor equals 1) 12.5 33.3 n |    |  |      | ns   |  |  |  |

| f <sub>CLK2</sub>                                                | Input clock frequency (ClockBoost clock multiplication factor equals 2)          | 16 |  | 50   | MHz  |  |  |  |

| t <sub>CLK2</sub>                                                | Input clock period (ClockBoost clock multiplication factor equals 2)             | 20 |  | 62.5 | ns   |  |  |  |

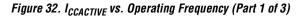

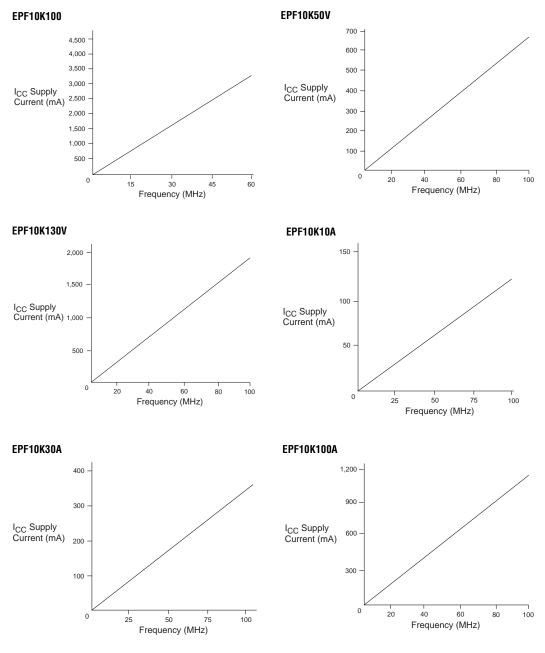

### Figure 32. I<sub>CCACTIVE</sub> vs. Operating Frequency (Part 2 of 3)

Multiple FLEX 10K devices can be configured in any of the five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

| Table 116. Data Sources for Configuration |                                                                                                                         |  |  |  |  |  |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Configuration Scheme                      | Data Source                                                                                                             |  |  |  |  |  |

| Configuration device                      | EPC1, EPC2, EPC16, or EPC1441 configuration device                                                                      |  |  |  |  |  |

| Passive serial (PS)                       | BitBlaster, MasterBlaster, or ByteBlasterMV download cable, or serial data source                                       |  |  |  |  |  |

| Passive parallel asynchronous (PPA)       | Parallel data source                                                                                                    |  |  |  |  |  |

| Passive parallel synchronous (PPS)        | Parallel data source                                                                                                    |  |  |  |  |  |

| JTAG                                      | BitBlaster, MasterBlaster, or ByteBlasterMV download cable, or microprocessor with Jam STAPL file or Jam Byte-Code file |  |  |  |  |  |

## Device Pin-Outs

### Revision History

The information contained in the *FLEX 10K Embedded Programmable Logic Device Family Data Sheet* version 4.2 supersedes information published in previous versions.

See the Altera web site (http://www.altera.com) or the Altera Digital

### Version 4.2 Changes

Library for pin-out information.

The following change was made to version 4.2 of the *FLEX 10K Embedded Programmable Logic Device Family Data Sheet*: updated Figure 13.

### Version 4.1 Changes

The following changes were made to version 4.1 of the *FLEX 10K Embedded Programmable Logic Device Family Data Sheet.*

- Updated General Description section

- Updated I/O Element section

- Updated SameFrame Pin-Outs section

- Updated Figure 16

- Updated Tables 13 and 116

- Added Note 9 to Table 19

- Added Note 10 to Table 24

- Added Note 10 to Table 28