Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 360                                                          |

| Number of Logic Elements/Cells | 2880                                                         |

| Total RAM Bits                 | 20480                                                        |

| Number of I/O                  | 274                                                          |

| Number of Gates                | 116000                                                       |

| Voltage - Supply               | 3V ~ 3.6V                                                    |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 70°C (TA)                                              |

| Package / Case                 | 356-LBGA                                                     |

| Supplier Device Package        | 356-BGA (35x35)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k50vbc356-3n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 4. FLEX 10K Pa | ackage Options & l | 1/O Pin Count   | Note (1)     |                         |                         |

|----------------------|--------------------|-----------------|--------------|-------------------------|-------------------------|

| Device               | 84-Pin<br>PLCC     | 100-Pin<br>TQFP | 144-Pin TQFP | 208-Pin<br>PQFP<br>RQFP | 240-Pin<br>PQFP<br>RQFP |

| EPF10K10             | 59                 |                 | 102          | 134                     |                         |

| EPF10K10A            |                    | 66              | 102          | 134                     |                         |

| EPF10K20             |                    |                 | 102          | 147                     | 189                     |

| EPF10K30             |                    |                 |              | 147                     | 189                     |

| EPF10K30A            |                    |                 | 102          | 147                     | 189                     |

| EPF10K40             |                    |                 |              | 147                     | 189                     |

| EPF10K50             |                    |                 |              |                         | 189                     |

| EPF10K50V            |                    |                 |              |                         | 189                     |

| EPF10K70             |                    |                 |              |                         | 189                     |

| EPF10K100            |                    |                 |              |                         |                         |

| EPF10K100A           |                    |                 |              |                         | 189                     |

| EPF10K130V           |                    |                 |              |                         |                         |

| EPF10K250A           |                    |                 |              |                         |                         |

| Device     | 503-Pin<br>PGA | 599-Pin<br>PGA | 256-Pin<br>FineLine BGA | 356-Pin<br>BGA | 484-Pin<br>FineLine BGA | 600-Pin<br>BGA | 403-Pin<br>PGA |

|------------|----------------|----------------|-------------------------|----------------|-------------------------|----------------|----------------|

| EPF10K10   |                | -              |                         |                |                         |                |                |

| EPF10K10A  |                |                | 150                     |                | 150 (2)                 |                |                |

| EPF10K20   |                |                |                         |                |                         |                |                |

| EPF10K30   |                |                |                         | 246            |                         |                |                |

| EPF10K30A  |                |                | 191                     | 246            | 246                     |                |                |

| EPF10K40   |                |                |                         |                |                         |                |                |

| EPF10K50   |                |                |                         | 274            |                         |                | 310            |

| EPF10K50V  |                |                |                         | 274            |                         |                |                |

| EPF10K70   | 358            |                |                         |                |                         |                |                |

| EPF10K100  | 406            |                |                         |                |                         |                |                |

| EPF10K100A |                |                |                         | 274            | 369                     | 406            |                |

| EPF10K130V |                | 470            |                         |                |                         | 470            |                |

| EPF10K250A |                | 470            |                         |                |                         | 470            |                |

The FLEX 10K architecture is similar to that of embedded gate arrays, the fastest-growing segment of the gate array market. As with standard gate arrays, embedded gate arrays implement general logic in a conventional "sea-of-gates" architecture. In addition, embedded gate arrays have dedicated die areas for implementing large, specialized functions. By embedding functions in silicon, embedded gate arrays provide reduced die area and increased speed compared to standard gate arrays. However, embedded megafunctions typically cannot be customized, limiting the designer's options. In contrast, FLEX 10K devices are programmable, providing the designer with full control over embedded megafunctions and general logic while facilitating iterative design changes during debugging.

Each FLEX 10K device contains an embedded array and a logic array. The embedded array is used to implement a variety of memory functions or complex logic functions, such as digital signal processing (DSP), microcontroller, wide-data-path manipulation, and data-transformation functions. The logic array performs the same function as the sea-of-gates in the gate array: it is used to implement general logic, such as counters, adders, state machines, and multiplexers. The combination of embedded and logic arrays provides the high performance and high density of embedded gate arrays, enabling designers to implement an entire system on a single device.

FLEX 10K devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers the EPC1, EPC2, EPC16, and EPC1441 configuration devices, which configure FLEX 10K devices via a serial data stream. Configuration data can also be downloaded from system RAM or from Altera's BitBlaster™ serial download cable or ByteBlasterMV™ parallel port download cable. After a FLEX 10K device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Because reconfiguration requires less than 320 ms, real-time changes can be made during system operation.

FLEX 10K devices contain an optimized interface that permits microprocessors to configure FLEX 10K devices serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat a FLEX 10K device as memory and configure the device by writing to a virtual memory location, making it very easy for the designer to reconfigure the device.

For more information, see the following documents:

- Configuration Devices for APEX & FLEX Devices Data Sheet

- BitBlaster Serial Download Cable Data Sheet

- ByteBlasterMV Parallel Port Download Cable Data Sheet

- Application Note 116 (Configuring APEX 20K, FLEX 10K & FLEX 6000 Devices)

FLEX 10K devices are supported by Altera development systems; single, integrated packages that offer schematic, text (including AHDL), and waveform design entry, compilation and logic synthesis, full simulation and worst-case timing analysis, and device configuration. The Altera software provides EDIF 2 0 0 and 3 0 0, LPM, VHDL, Verilog HDL, and other interfaces for additional design entry and simulation support from other industry-standard PC- and UNIX workstation-based EDA tools.

The Altera software works easily with common gate array EDA tools for synthesis and simulation. For example, the Altera software can generate Verilog HDL files for simulation with tools such as Cadence Verilog-XL. Additionally, the Altera software contains EDA libraries that use device-specific features such as carry chains which are used for fast counter and arithmetic functions. For instance, the Synopsys Design Compiler library supplied with the Altera development systems include DesignWare functions that are optimized for the FLEX 10K architecture.

The Altera development systems run on Windows-based PCs and Sun SPARCstation, and HP 9000 Series 700/800 workstations.

See the MAX+PLUS II Programmable Logic Development System & Software Data Sheet for more information.

# Functional Description

Each FLEX 10K device contains an embedded array to implement memory and specialized logic functions, and a logic array to implement general logic.

The embedded array consists of a series of EABs. When implementing memory functions, each EAB provides 2,048 bits, which can be used to create RAM, ROM, dual-port RAM, or first-in first-out (FIFO) functions. When implementing logic, each EAB can contribute 100 to 600 gates towards complex logic functions, such as multipliers, microcontrollers, state machines, and DSP functions. EABs can be used independently, or multiple EABs can be combined to implement larger functions.

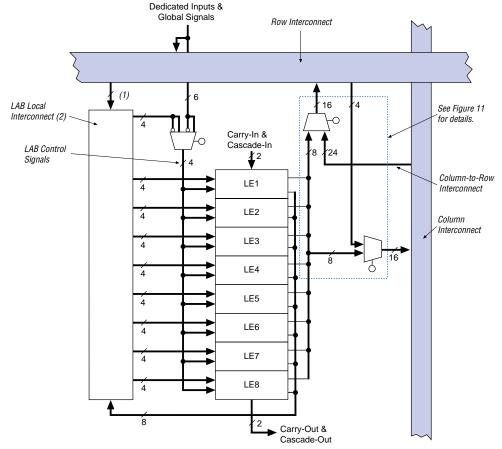

The logic array consists of logic array blocks (LABs). Each LAB contains eight LEs and a local interconnect. An LE consists of a 4-input look-up table (LUT), a programmable flipflop, and dedicated signal paths for carry and cascade functions. The eight LEs can be used to create medium-sized blocks of logic—8-bit counters, address decoders, or state machines—or combined across LABs to create larger logic blocks. Each LAB represents about 96 usable gates of logic.

Signal interconnections within FLEX 10K devices and to and from device pins are provided by the FastTrack Interconnect, a series of fast, continuous row and column channels that run the entire length and width of the device.

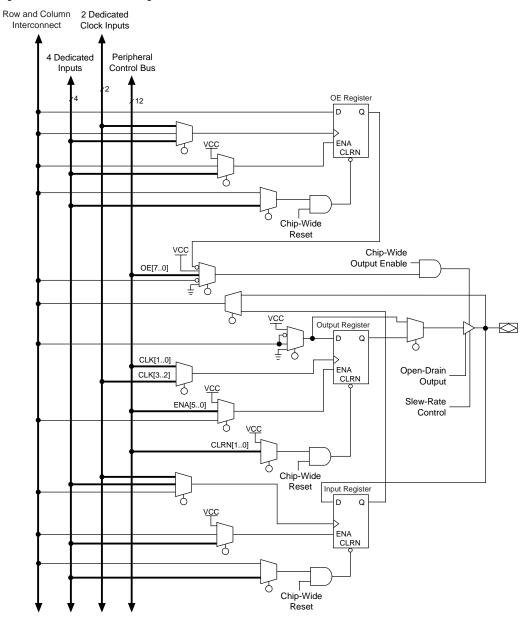

Each I/O pin is fed by an I/O element (IOE) located at the end of each row and column of the FastTrack Interconnect. Each IOE contains a bidirectional I/O buffer and a flipflop that can be used as either an output or input register to feed input, output, or bidirectional signals. When used with a dedicated clock pin, these registers provide exceptional performance. As inputs, they provide setup times as low as 1.6 ns and hold times of 0 ns; as outputs, these registers provide clock-to-output times as low as 5.3 ns. IOEs provide a variety of features, such as JTAG BST support, slew-rate control, tri-state buffers, and open-drain outputs.

Figure 1 shows a block diagram of the FLEX 10K architecture. Each group of LEs is combined into an LAB; LABs are arranged into rows and columns. Each row also contains a single EAB. The LABs and EABs are interconnected by the FastTrack Interconnect. IOEs are located at the end of each row and column of the FastTrack Interconnect.

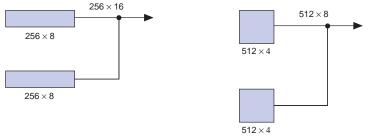

Larger blocks of RAM are created by combining multiple EABs. For example, two  $256 \times 8$  RAM blocks can be combined to form a  $256 \times 16$  RAM block; two  $512 \times 4$  blocks of RAM can be combined to form a  $512 \times 8$  RAM block. See Figure 3.

Figure 3. Examples of Combining EABs

If necessary, all EABs in a device can be cascaded to form a single RAM block. EABs can be cascaded to form RAM blocks of up to 2,048 words without impacting timing. Altera's software automatically combines EABs to meet a designer's RAM specifications.

EABs provide flexible options for driving and controlling clock signals. Different clocks can be used for the EAB inputs and outputs. Registers can be independently inserted on the data input, EAB output, or the address and WE inputs. The global signals and the EAB local interconnect can drive the WE signal. The global signals, dedicated clock pins, and EAB local interconnect can drive the EAB clock signals. Because the LEs drive the EAB local interconnect, the LEs can control the WE signal or the EAB clock signals.

Each EAB is fed by a row interconnect and can drive out to row and column interconnects. Each EAB output can drive up to two row channels and up to two column channels; the unused row channel can be driven by other LEs. This feature increases the routing resources available for EAB outputs. See Figure 4.

### **Logic Array Block**

Each LAB consists of eight LEs, their associated carry and cascade chains, LAB control signals, and the LAB local interconnect. The LAB provides the coarse-grained structure to the FLEX 10K architecture, facilitating efficient routing with optimum device utilization and high performance. See Figure 5.

Figure 5. FLEX 10K LAB

#### Notes:

- (1) EPF10K10, EPF10K10A, EPF10K20, EPF10K30, EPF10K30A, EPF10K40, EPF10K50, and EPF10K50V devices have 22 inputs to the LAB local interconnect channel from the row; EPF10K70, EPF10K100, EPF10K100A, EPF10K130V, and EPF10K250A devices have 26.

- (2) EPF10K10, EPF10K10A, EPF10K20, EPF10K30, EPF10K30A, EPF10K40, EPF10K50, and EPF10K50V devices have 30 LAB local interconnect channels; EPF10K70, EPF10K100, EPF10K100A, EPF10K130V, and EPF10K250A devices have 34 LABs.

The programmable flipflop in the LE can be configured for D, T, JK, or SR operation. The clock, clear, and preset control signals on the flipflop can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the flipflop is bypassed and the output of the LUT drives the output of the LE.

The LE has two outputs that drive the interconnect; one drives the local interconnect and the other drives either the row or column FastTrack Interconnect. The two outputs can be controlled independently. For example, the LUT can drive one output while the register drives the other output. This feature, called register packing, can improve LE utilization because the register and the LUT can be used for unrelated functions.

The FLEX 10K architecture provides two types of dedicated high-speed data paths that connect adjacent LEs without using local interconnect paths: carry chains and cascade chains. The carry chain supports high-speed counters and adders; the cascade chain implements wide-input functions with minimum delay. Carry and cascade chains connect all LEs in an LAB and all LABs in the same row. Intensive use of carry and cascade chains can reduce routing flexibility. Therefore, the use of these chains should be limited to speed-critical portions of a design.

#### Carry Chain

The carry chain provides a very fast (as low as 0.2 ns) carry-forward function between LEs. The carry-in signal from a lower-order bit drives forward into the higher-order bit via the carry chain, and feeds into both the LUT and the next portion of the carry chain. This feature allows the FLEX 10K architecture to implement high-speed counters, adders, and comparators of arbitrary width efficiently. Carry chain logic can be created automatically by the Compiler during design processing, or manually by the designer during design entry. Parameterized functions such as LPM and DesignWare functions automatically take advantage of carry chains.

Carry chains longer than eight LEs are automatically implemented by linking LABs together. For enhanced fitting, a long carry chain skips alternate LABs in a row. A carry chain longer than one LAB skips either from even-numbered LAB to even-numbered LAB, or from odd-numbered LAB to odd-numbered LAB. For example, the last LE of the first LAB in a row carries to the first LE of the third LAB in the row. The carry chain does not cross the EAB at the middle of the row. For instance, in the EPF10K50 device, the carry chain stops at the eighteenth LAB and a new one begins at the nineteenth LAB.

#### LE Operating Modes

The FLEX 10K LE can operate in the following four modes:

- Normal mode

- Arithmetic mode

- Up/down counter mode

- Clearable counter mode

Each of these modes uses LE resources differently. In each mode, seven available inputs to the LE—the four data inputs from the LAB local interconnect, the feedback from the programmable register, and the carry-in and cascade-in from the previous LE—are directed to different destinations to implement the desired logic function. Three inputs to the LE provide clock, clear, and preset control for the register. The Altera software, in conjunction with parameterized functions such as LPM and DesignWare functions, automatically chooses the appropriate mode for common functions such as counters, adders, and multipliers. If required, the designer can also create special-purpose functions which use a specific LE operating mode for optimal performance.

The architecture provides a synchronous clock enable to the register in all four modes. The Altera software can set DATA1 to enable the register synchronously, providing easy implementation of fully synchronous designs.

Figure 9 shows the LE operating modes.

Figure 13. Bidirectional I/O Registers

| Table 15. 32-Bit FLEX 10K Device | e IDCODE            | Note (1)                 |                                      |                  |  |  |  |  |  |  |

|----------------------------------|---------------------|--------------------------|--------------------------------------|------------------|--|--|--|--|--|--|

| Device                           | IDCODE (32 Bits)    |                          |                                      |                  |  |  |  |  |  |  |

|                                  | Version<br>(4 Bits) | Part Number<br>(16 Bits) | Manufacturer's Identity<br>(11 Bits) | 1 (1 Bit)<br>(2) |  |  |  |  |  |  |

| EPF10K10, EPF10K10A              | 0000                | 0001 0000 0001 0000      | 00001101110                          | 1                |  |  |  |  |  |  |

| EPF10K20                         | 0000                | 0001 0000 0010 0000      | 00001101110                          | 1                |  |  |  |  |  |  |

| EPF10K30, EPF10K30A              | 0000                | 0001 0000 0011 0000      | 00001101110                          | 1                |  |  |  |  |  |  |

| EPF10K40                         | 0000                | 0001 0000 0100 0000      | 00001101110                          | 1                |  |  |  |  |  |  |

| EPF10K50, EPF10K50V              | 0000                | 0001 0000 0101 0000      | 00001101110                          | 1                |  |  |  |  |  |  |

| EPF10K70                         | 0000                | 0001 0000 0111 0000      | 00001101110                          | 1                |  |  |  |  |  |  |

| EPF10K100, EPF10K100A            | 0000                | 0000 0001 0000 0000      | 00001101110                          | 1                |  |  |  |  |  |  |

| EPF10K130V                       | 0000                | 0000 0001 0011 0000      | 00001101110                          | 1                |  |  |  |  |  |  |

| EPF10K250A                       | 0000                | 0000 0010 0101 0000      | 00001101110                          | 1                |  |  |  |  |  |  |

#### Notes:

- (1) The most significant bit (MSB) is on the left.

- (2) The least significant bit (LSB) for all JTAG IDCODEs is 1.

FLEX 10K devices include weak pull-ups on JTAG pins.

For more information, see the following documents:

- Application Note 39 (IEEE 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices)

- BitBlaster Serial Download Cable Data Sheet

- ByteBlasterMV Parallel Port Download Cable Data Sheet

- Jam Programming & Test Language Specification

| Symbol                 | -3 Spee | d Grade | -4 Spee | Unit |    |

|------------------------|---------|---------|---------|------|----|

|                        | Min     | Max     | Min     | Max  |    |

| t <sub>EABDATA1</sub>  |         | 1.5     |         | 1.9  | ns |

| t <sub>EABDATA2</sub>  |         | 4.8     |         | 6.0  | ns |

| t <sub>EABWE1</sub>    |         | 1.0     |         | 1.2  | ns |

| t <sub>EABWE2</sub>    |         | 5.0     |         | 6.2  | ns |

| t <sub>EABCLK</sub>    |         | 1.0     |         | 2.2  | ns |

| t <sub>EABCO</sub>     |         | 0.5     |         | 0.6  | ns |

| t <sub>EABBYPASS</sub> |         | 1.5     |         | 1.9  | ns |

| t <sub>EABSU</sub>     | 1.5     |         | 1.8     |      | ns |

| t <sub>EABH</sub>      | 2.0     |         | 2.5     |      | ns |

| $t_{AA}$               |         | 8.7     |         | 10.7 | ns |

| $t_{WP}$               | 5.8     |         | 7.2     |      | ns |

| t <sub>WDSU</sub>      | 1.6     |         | 2.0     |      | ns |

| t <sub>WDH</sub>       | 0.3     |         | 0.4     |      | ns |

| t <sub>WASU</sub>      | 0.5     |         | 0.6     |      | ns |

| t <sub>WAH</sub>       | 1.0     |         | 1.2     |      | ns |

| $t_{WO}$               |         | 5.0     |         | 6.2  | ns |

| t <sub>DD</sub>        |         | 5.0     |         | 6.2  | ns |

| t <sub>EABOUT</sub>    |         | 0.5     |         | 0.6  | ns |

| t <sub>EABCH</sub>     | 4.0     |         | 4.0     |      | ns |

| t <sub>EABCL</sub>     | 5.8     |         | 7.2     |      | ns |

| Symbol                 | -3 Snee | d Grade | -4 Spee | Unit |       |

|------------------------|---------|---------|---------|------|-------|

| Symbol                 | -       |         |         |      | Oiiit |

|                        | Min     | Max     | Min     | Max  |       |

| t <sub>EABAA</sub>     |         | 13.7    |         | 17.0 | ns    |

| t <sub>EABRCCOMB</sub> | 13.7    |         | 17.0    |      | ns    |

| t <sub>EABRCREG</sub>  | 9.7     |         | 11.9    |      | ns    |

| t <sub>EABWP</sub>     | 5.8     |         | 7.2     |      | ns    |

| t <sub>EABWCCOMB</sub> | 7.3     |         | 9.0     |      | ns    |

| t <sub>EABWCREG</sub>  | 13.0    |         | 16.0    |      | ns    |

| t <sub>EABDD</sub>     |         | 10.0    |         | 12.5 | ns    |

| t <sub>EABDATACO</sub> |         | 2.0     |         | 3.4  | ns    |

| t <sub>EABDATASU</sub> | 5.3     |         | 5.6     |      | ns    |

| t <sub>EABDATAH</sub>  | 0.0     |         | 0.0     |      | ns    |

| t <sub>EABWESU</sub>   | 5.5     |         | 5.8     |      | ns    |

| t <sub>EABWEH</sub>    | 0.0     |         | 0.0     |      | ns    |

| t <sub>EABWDSU</sub>   | 5.5     |         | 5.8     |      | ns    |

| t <sub>EABWDH</sub>    | 0.0     |         | 0.0     |      | ns    |

| t <sub>EABWASU</sub>   | 2.1     |         | 2.7     |      | ns    |

| t <sub>EABWAH</sub>    | 0.0     |         | 0.0     |      | ns    |

| $t_{EABWO}$            |         | 9.5     |         | 11.8 | ns    |

#### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

Tables 57 through 63 show EPF10K70 device internal and external timing parameters.

| Symbol              | -2 Speed Grade |     | -3 Spee | d Grade | -4 Spee | Unit |    |

|---------------------|----------------|-----|---------|---------|---------|------|----|

|                     | Min            | Max | Min     | Max     | Min     | Max  |    |

| $t_{LUT}$           |                | 1.3 |         | 1.5     |         | 2.0  | ns |

| t <sub>CLUT</sub>   |                | 0.4 |         | 0.4     |         | 0.5  | ns |

| t <sub>RLUT</sub>   |                | 1.5 |         | 1.6     |         | 2.0  | ns |

| t <sub>PACKED</sub> |                | 0.8 |         | 0.9     |         | 1.3  | ns |

| t <sub>EN</sub>     |                | 0.8 |         | 0.9     |         | 1.2  | ns |

| t <sub>CICO</sub>   |                | 0.2 |         | 0.2     |         | 0.3  | ns |

| t <sub>CGEN</sub>   |                | 1.0 |         | 1.1     |         | 1.4  | ns |

| t <sub>CGENR</sub>  |                | 1.1 |         | 1.2     |         | 1.5  | ns |

| t <sub>CASC</sub>   |                | 1.0 |         | 1.1     |         | 1.3  | ns |

| $t_{\mathbb{C}}$    |                | 0.7 |         | 0.8     |         | 1.0  | ns |

| $t_{CO}$            |                | 0.9 |         | 1.0     |         | 1.4  | ns |

| t <sub>COMB</sub>   |                | 0.4 |         | 0.5     |         | 0.7  | ns |

| t <sub>SU</sub>     | 1.9            |     | 2.1     |         | 2.6     |      | ns |

| t <sub>H</sub>      | 2.1            |     | 2.3     |         | 3.1     |      | ns |

| t <sub>PRE</sub>    |                | 0.9 |         | 1.0     |         | 1.4  | ns |

| t <sub>CLR</sub>    |                | 0.9 |         | 1.0     |         | 1.4  | ns |

| t <sub>CH</sub>     | 4.0            |     | 4.0     |         | 4.0     |      | ns |

| $t_{CL}$            | 4.0            |     | 4.0     |         | 4.0     |      | ns |

| Table 66. EPF10K100    | Device EAB Int | ternal Microp | parameters | Note (1) |         |      |    |

|------------------------|----------------|---------------|------------|----------|---------|------|----|

| Symbol                 | -3DX Spe       | ed Grade      | -3 Spee    | d Grade  | -4 Spee | Unit |    |

|                        | Min            | Max           | Min        | Max      | Min     | Max  |    |

| t <sub>EABDATA1</sub>  |                | 1.5           |            | 1.5      |         | 1.9  | ns |

| t <sub>EABDATA2</sub>  |                | 4.8           |            | 4.8      |         | 6.0  | ns |

| t <sub>EABWE1</sub>    |                | 1.0           |            | 1.0      |         | 1.2  | ns |

| t <sub>EABWE2</sub>    |                | 5.0           |            | 5.0      |         | 6.2  | ns |

| t <sub>EABCLK</sub>    |                | 1.0           |            | 1.0      |         | 2.2  | ns |

| t <sub>EABCO</sub>     |                | 0.5           |            | 0.5      |         | 0.6  | ns |

| t <sub>EABBYPASS</sub> |                | 1.5           |            | 1.5      |         | 1.9  | ns |

| t <sub>EABSU</sub>     | 1.5            |               | 1.5        |          | 1.8     |      | ns |

| t <sub>EABH</sub>      | 2.0            |               | 2.0        |          | 2.5     |      | ns |

| $t_{AA}$               |                | 8.7           |            | 8.7      |         | 10.7 | ns |

| $t_{WP}$               | 5.8            |               | 5.8        |          | 7.2     |      | ns |

| t <sub>WDSU</sub>      | 1.6            |               | 1.6        |          | 2.0     |      | ns |

| t <sub>WDH</sub>       | 0.3            |               | 0.3        |          | 0.4     |      | ns |

| t <sub>WASU</sub>      | 0.5            |               | 0.5        |          | 0.6     |      | ns |

| t <sub>WAH</sub>       | 1.0            |               | 1.0        |          | 1.2     |      | ns |

| $t_{WO}$               |                | 5.0           |            | 5.0      |         | 6.2  | ns |

| $t_{DD}$               |                | 5.0           |            | 5.0      |         | 6.2  | ns |

| t <sub>EABOUT</sub>    |                | 0.5           |            | 0.5      |         | 0.6  | ns |

| t <sub>EABCH</sub>     | 4.0            |               | 4.0        |          | 4.0     |      | ns |

| t <sub>EABCL</sub>     | 5.8            |               | 5.8        |          | 7.2     |      | ns |

| Symbol                  | -1 Spee | d Grade | -2 Speed Grade |      | -3 Speed Grade |      | -4 Speed Grade |      | Unit |

|-------------------------|---------|---------|----------------|------|----------------|------|----------------|------|------|

|                         | Min     | Max     | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>EABAA</sub>      |         | 9.5     |                | 13.6 |                | 16.5 |                | 20.8 | ns   |

| t <sub>EABRCCOMB</sub>  | 9.5     |         | 13.6           |      | 16.5           |      | 20.8           |      | ns   |

| t <sub>EABRCREG</sub>   | 6.1     |         | 8.8            |      | 10.8           |      | 13.4           |      | ns   |

| t <sub>EABWP</sub>      | 6.0     |         | 4.9            |      | 6.0            |      | 7.4            |      | ns   |

| t <sub>EABWCCOMB</sub>  | 6.2     |         | 6.1            |      | 7.5            |      | 9.2            |      | ns   |

| t <sub>EABWCREG</sub>   | 12.0    |         | 11.6           |      | 14.2           |      | 17.4           |      | ns   |

| t <sub>EABDD</sub>      |         | 6.8     |                | 9.7  |                | 11.8 |                | 14.9 | ns   |

| t <sub>EABDATA</sub> CO |         | 1.0     |                | 1.4  |                | 1.8  |                | 2.2  | ns   |

| t <sub>EABDATASU</sub>  | 5.3     |         | 4.6            |      | 5.6            |      | 6.9            |      | ns   |

| t <sub>EABDATAH</sub>   | 0.0     |         | 0.0            |      | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWESU</sub>    | 4.4     |         | 4.8            |      | 5.8            |      | 7.2            |      | ns   |

| t <sub>EABWEH</sub>     | 0.0     |         | 0.0            |      | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWDSU</sub>    | 1.8     |         | 1.1            |      | 1.4            |      | 2.1            |      | ns   |

| t <sub>EABWDH</sub>     | 0.0     |         | 0.0            |      | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWASU</sub>    | 4.5     |         | 4.6            |      | 5.6            |      | 7.4            |      | ns   |

| t <sub>EABWAH</sub>     | 0.0     |         | 0.0            |      | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWO</sub>      |         | 5.1     |                | 9.4  |                | 11.4 |                | 14.0 | ns   |

| Symbol                   | -2 Spee | -2 Speed Grade |     | -3 Speed Grade |     | -4 Speed Grade |    |

|--------------------------|---------|----------------|-----|----------------|-----|----------------|----|

|                          | Min     | Max            | Min | Max            | Min | Max            |    |

| t <sub>DIN2IOE</sub>     |         | 8.0            |     | 9.0            |     | 9.5            | ns |

| t <sub>DIN2LE</sub>      |         | 2.4            |     | 3.0            |     | 3.1            | ns |

| t <sub>DIN2DATA</sub>    |         | 5.0            |     | 6.3            |     | 7.4            | ns |

| t <sub>DCLK2IOE</sub>    |         | 3.6            |     | 4.6            |     | 5.1            | ns |

| t <sub>DCLK2LE</sub>     |         | 2.4            |     | 3.0            |     | 3.1            | ns |

| t <sub>SAMELAB</sub>     |         | 0.4            |     | 0.6            |     | 0.8            | ns |

| t <sub>SAMEROW</sub>     |         | 4.5            |     | 5.3            |     | 6.5            | ns |

| t <sub>SAME</sub> COLUMN |         | 9.0            |     | 9.5            |     | 9.7            | ns |

| t <sub>DIFFROW</sub>     |         | 13.5           |     | 14.8           |     | 16.2           | ns |

| t <sub>TWOROWS</sub>     |         | 18.0           |     | 20.1           |     | 22.7           | ns |

| t <sub>LEPERIPH</sub>    |         | 8.1            |     | 8.6            |     | 9.5            | ns |

| t <sub>LABCARRY</sub>    |         | 0.6            |     | 0.8            |     | 1.0            | ns |

| t <sub>LABCASC</sub>     |         | 0.8            |     | 1.0            |     | 1.2            | ns |

| Table 83. EPF10K130V Device External Timing Parameters Note (1) |         |          |         |                            |      |      |      |  |  |  |

|-----------------------------------------------------------------|---------|----------|---------|----------------------------|------|------|------|--|--|--|

| Symbol                                                          | -2 Spec | ed Grade | -3 Spee | Speed Grade -4 Speed Grade |      |      | Unit |  |  |  |

|                                                                 | Min     | Max      | Min     | Max                        | Min  | Max  |      |  |  |  |

| t <sub>DRR</sub>                                                |         | 15.0     |         | 19.1                       |      | 24.2 | ns   |  |  |  |

| t <sub>INSU</sub> (2), (3)                                      | 6.9     |          | 8.6     |                            | 11.0 |      | ns   |  |  |  |

| t <sub>INH</sub> (3)                                            | 0.0     |          | 0.0     |                            | 0.0  |      | ns   |  |  |  |

| t <sub>outco</sub> (3)                                          | 2.0     | 7.8      | 2.0     | 9.9                        | 2.0  | 11.3 | ns   |  |  |  |

| Table 84. EPF10K130V Device External Bidirectional Timing Parameters       Note (1) |         |          |         |                             |      |      |      |  |  |

|-------------------------------------------------------------------------------------|---------|----------|---------|-----------------------------|------|------|------|--|--|

| Symbol                                                                              | -2 Spec | ed Grade | -3 Spec | -3 Speed Grade -4 Speed Gra |      |      | Unit |  |  |

|                                                                                     | Min     | Max      | Min     | Max                         | Min  | Max  |      |  |  |

| t <sub>INSUBIDIR</sub>                                                              | 6.7     |          | 8.5     |                             | 10.8 |      | ns   |  |  |

| t <sub>INHBIDIR</sub>                                                               | 0.0     |          | 0.0     |                             | 0.0  |      | ns   |  |  |

| toutcobidir                                                                         | 2.0     | 6.9      | 2.0     | 8.8                         | 2.0  | 10.2 | ns   |  |  |

| t <sub>XZBIDIR</sub>                                                                |         | 12.9     |         | 16.4                        |      | 19.3 | ns   |  |  |

| t <sub>ZXBIDIR</sub>                                                                |         | 12.9     |         | 16.4                        |      | 19.3 | ns   |  |  |

#### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

Tables 85 through 91 show EPF10K10A device internal and external timing parameters.

| Table 85. EPF10K10A Device LE Timing Microparameters   Note (1) |         |         |         |          |         |                |    |  |

|-----------------------------------------------------------------|---------|---------|---------|----------|---------|----------------|----|--|

| Symbol                                                          | -1 Spee | d Grade | -2 Spee | ed Grade | -3 Spee | -3 Speed Grade |    |  |

|                                                                 | Min     | Max     | Min     | Max      | Min     | Max            |    |  |

| $t_{LUT}$                                                       |         | 0.9     |         | 1.2      |         | 1.6            | ns |  |

| t <sub>CLUT</sub>                                               |         | 1.2     |         | 1.4      |         | 1.9            | ns |  |

| t <sub>RLUT</sub>                                               |         | 1.9     |         | 2.3      |         | 3.0            | ns |  |

| t <sub>PACKED</sub>                                             |         | 0.6     |         | 0.7      |         | 0.9            | ns |  |

| $t_{EN}$                                                        |         | 0.5     |         | 0.6      |         | 0.8            | ns |  |

| t <sub>CICO</sub>                                               |         | 02      |         | 0.3      |         | 0.4            | ns |  |

| t <sub>CGEN</sub>                                               |         | 0.7     |         | 0.9      |         | 1.1            | ns |  |

| t <sub>CGENR</sub>                                              |         | 0.7     |         | 0.9      |         | 1.1            | ns |  |

| t <sub>CASC</sub>                                               |         | 1.0     |         | 1.2      |         | 1.7            | ns |  |

| $t_{\rm C}$                                                     |         | 1.2     |         | 1.4      |         | 1.9            | ns |  |

| $t_{\rm CO}$                                                    |         | 0.5     |         | 0.6      |         | 0.8            | ns |  |

| t <sub>COMB</sub>                                               |         | 0.5     |         | 0.6      |         | 0.8            | ns |  |

| $t_{SU}$                                                        | 1.1     |         | 1.3     |          | 1.7     |                | ns |  |

| t <sub>H</sub>                                                  | 0.6     |         | 0.7     |          | 0.9     |                | ns |  |

| t <sub>PRE</sub>                                                |         | 0.5     |         | 0.6      |         | 0.9            | ns |  |

| $t_{CLR}$                                                       |         | 0.5     |         | 0.6      |         | 0.9            | ns |  |

| t <sub>CH</sub>                                                 | 3.0     |         | 3.5     |          | 4.0     |                | ns |  |

| t <sub>CL</sub>                                                 | 3.0     |         | 3.5     |          | 4.0     |                | ns |  |

| Table 86. EPF10K10A Device IOE Timing Microparameters     Note (1) (Part 1 of 2) |         |         |         |         |         |                |    |  |

|----------------------------------------------------------------------------------|---------|---------|---------|---------|---------|----------------|----|--|

| Symbol                                                                           | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | -3 Speed Grade |    |  |

|                                                                                  | Min     | Max     | Min     | Max     | Min     | Max            |    |  |

|                                                                                  |         | 1.3     |         | 1.5     |         | 2.0            | ns |  |

| t <sub>IOC</sub>                                                                 |         | 0.2     |         | 0.3     |         | 0.3            | ns |  |

| t <sub>IOCO</sub>                                                                |         | 0.2     |         | 0.3     |         | 0.4            | ns |  |

| t <sub>IOCOMB</sub>                                                              |         | 0.6     |         | 0.7     |         | 0.9            | ns |  |

| t <sub>IOSU</sub>                                                                | 0.8     |         | 1.0     |         | 1.3     |                | ns |  |

| Symbol                 | -1 Spee | d Grade | -2 Spee | ed Grade -3 Speed Grade |     | d Grade | Unit |

|------------------------|---------|---------|---------|-------------------------|-----|---------|------|

|                        | Min     | Max     | Min     | Max                     | Min | Max     |      |

| t <sub>EABDATA1</sub>  |         | 3.3     |         | 3.9                     |     | 5.2     | ns   |

| t <sub>EABDATA2</sub>  |         | 1.0     |         | 1.3                     |     | 1.7     | ns   |

| t <sub>EABWE1</sub>    |         | 2.6     |         | 3.1                     |     | 4.1     | ns   |

| t <sub>EABWE2</sub>    |         | 2.7     |         | 3.2                     |     | 4.3     | ns   |

| t <sub>EABCLK</sub>    |         | 0.0     |         | 0.0                     |     | 0.0     | ns   |

| t <sub>EABCO</sub>     |         | 1.2     |         | 1.4                     |     | 1.8     | ns   |

| t <sub>EABBYPASS</sub> |         | 0.1     |         | 0.2                     |     | 0.2     | ns   |

| t <sub>EABSU</sub>     | 1.4     |         | 1.7     |                         | 2.2 |         | ns   |

| t <sub>EABH</sub>      | 0.1     |         | 0.1     |                         | 0.1 |         | ns   |

| $t_{AA}$               |         | 4.5     |         | 5.4                     |     | 7.3     | ns   |

| $t_{WP}$               | 2.0     |         | 2.4     |                         | 3.2 |         | ns   |

| t <sub>WDSU</sub>      | 0.7     |         | 0.8     |                         | 1.1 |         | ns   |

| t <sub>WDH</sub>       | 0.5     |         | 0.6     |                         | 0.7 |         | ns   |

| t <sub>WASU</sub>      | 0.6     |         | 0.7     |                         | 0.9 |         | ns   |

| t <sub>WAH</sub>       | 0.9     |         | 1.1     |                         | 1.5 |         | ns   |

| $t_{WO}$               |         | 3.3     |         | 3.9                     |     | 5.2     | ns   |

| $t_{DD}$               |         | 3.3     |         | 3.9                     |     | 5.2     | ns   |

| t <sub>EABOUT</sub>    |         | 0.1     |         | 0.1                     |     | 0.2     | ns   |

| t <sub>EABCH</sub>     | 3.0     |         | 3.5     |                         | 4.0 |         | ns   |

| t <sub>EABCL</sub>     | 3.03    |         | 3.5     |                         | 4.0 |         | ns   |

| Symbol                   | -1 Spee | -1 Speed Grade |     | -2 Speed Grade |     | ed Grade | Unit |

|--------------------------|---------|----------------|-----|----------------|-----|----------|------|

|                          | Min     | Max            | Min | Max            | Min | Max      |      |

| t <sub>DIN2IOE</sub>     |         | 3.9            |     | 4.4            |     | 5.1      | ns   |

| t <sub>DIN2LE</sub>      |         | 1.2            |     | 1.5            |     | 1.9      | ns   |

| t <sub>DIN2DATA</sub>    |         | 3.2            |     | 3.6            |     | 4.5      | ns   |

| t <sub>DCLK2IOE</sub>    |         | 3.0            |     | 3.5            |     | 4.6      | ns   |

| t <sub>DCLK2LE</sub>     |         | 1.2            |     | 1.5            |     | 1.9      | ns   |

| t <sub>SAMELAB</sub>     |         | 0.1            |     | 0.1            |     | 0.2      | ns   |

| t <sub>SAMEROW</sub>     |         | 2.3            |     | 2.4            |     | 2.7      | ns   |

| t <sub>SAME</sub> COLUMN |         | 1.3            |     | 1.4            |     | 1.9      | ns   |

| t <sub>DIFFROW</sub>     |         | 3.6            |     | 3.8            |     | 4.6      | ns   |

| t <sub>TWOROWS</sub>     |         | 5.9            |     | 6.2            |     | 7.3      | ns   |

| t <sub>LEPERIPH</sub>    |         | 3.5            |     | 3.8            |     | 4.1      | ns   |

| t <sub>LABCARRY</sub>    |         | 0.3            |     | 0.4            |     | 0.5      | ns   |

| t <sub>LABCASC</sub>     |         | 0.9            |     | 1.1            |     | 1.4      | ns   |

| Table 97. EPF10K30A External Reference Timing Parameters Note (1) |         |          |         |          |         |      |    |  |  |

|-------------------------------------------------------------------|---------|----------|---------|----------|---------|------|----|--|--|

| Symbol                                                            | -1 Spec | ed Grade | -2 Spec | ed Grade | -3 Spee | Unit |    |  |  |

|                                                                   | Min     | Max      | Min     | Max      | Min     | Max  |    |  |  |

| t <sub>DRR</sub>                                                  |         | 11.0     |         | 13.0     |         | 17.0 | ns |  |  |

| t <sub>INSU</sub> (2), (3)                                        | 2.5     |          | 3.1     |          | 3.9     |      | ns |  |  |

| t <sub>INH</sub> (3)                                              | 0.0     |          | 0.0     |          | 0.0     |      | ns |  |  |

| t <sub>оитсо</sub> (3)                                            | 2.0     | 5.4      | 2.0     | 6.2      | 2.0     | 8.3  | ns |  |  |

| Table 98. EPF10K30A Device External Bidirectional Timing Parameters       Note (1) |         |          |         |          |         |      |    |  |

|------------------------------------------------------------------------------------|---------|----------|---------|----------|---------|------|----|--|

| Symbol                                                                             | -1 Spec | ed Grade | -2 Spec | ed Grade | -3 Spee | Unit |    |  |

|                                                                                    | Min     | Max      | Min     | Max      | Min     | Max  |    |  |

| t <sub>INSUBIDIR</sub>                                                             | 4.2     |          | 4.9     |          | 6.8     |      | ns |  |

| t <sub>INHBIDIR</sub>                                                              | 0.0     |          | 0.0     |          | 0.0     |      | ns |  |

| t <sub>OUTCOBIDIR</sub>                                                            | 2.0     | 5.4      | 2.0     | 6.2      | 2.0     | 8.3  | ns |  |

| t <sub>XZBIDIR</sub>                                                               |         | 6.2      |         | 7.5      |         | 9.8  | ns |  |

| t <sub>ZXBIDIR</sub>                                                               |         | 6.2      |         | 7.5      |         | 9.8  | ns |  |

| Symbol              | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | d Grade | Unit |

|---------------------|----------------|-----|---------|---------|---------|---------|------|

|                     | Min            | Max | Min     | Max     | Min     | Max     |      |

| $t_{IOD}$           |                | 1.2 |         | 1.3     |         | 1.6     | ns   |

| $t_{IOC}$           |                | 0.4 |         | 0.4     |         | 0.5     | ns   |

| t <sub>IOCO</sub>   |                | 0.8 |         | 0.9     |         | 1.1     | ns   |

| $t_{IOCOMB}$        |                | 0.7 |         | 0.7     |         | 0.8     | ns   |

| t <sub>IOSU</sub>   | 2.7            |     | 3.1     |         | 3.6     |         | ns   |

| t <sub>IOH</sub>    | 0.2            |     | 0.3     |         | 0.3     |         | ns   |

| t <sub>IOCLR</sub>  |                | 1.2 |         | 1.3     |         | 1.6     | ns   |

| $t_{OD1}$           |                | 3.2 |         | 3.6     |         | 4.2     | ns   |

| $t_{OD2}$           |                | 5.9 |         | 6.7     |         | 7.8     | ns   |

| $t_{OD3}$           |                | 8.7 |         | 9.8     |         | 11.5    | ns   |

| $t_{XZ}$            |                | 3.8 |         | 4.3     |         | 5.0     | ns   |

| $t_{ZX1}$           |                | 3.8 |         | 4.3     |         | 5.0     | ns   |

| t <sub>ZX2</sub>    |                | 6.5 |         | 7.4     |         | 8.6     | ns   |

| t <sub>ZX3</sub>    |                | 9.3 |         | 10.5    |         | 12.3    | ns   |

| t <sub>INREG</sub>  |                | 8.2 |         | 9.3     |         | 10.9    | ns   |

| t <sub>IOFD</sub>   |                | 9.0 |         | 10.2    |         | 12.0    | ns   |

| t <sub>INCOMB</sub> |                | 9.0 |         | 10.2    |         | 12.0    | ns   |