Welcome to **E-XFL.COM**

### Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 360                                                          |

| Number of Logic Elements/Cells | 2880                                                         |

| Total RAM Bits                 | 20480                                                        |

| Number of I/O                  | 274                                                          |

| Number of Gates                | 116000                                                       |

| Voltage - Supply               | 3V ~ 3.6V                                                    |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 70°C (TA)                                              |

| Package / Case                 | 356-LBGA                                                     |

| Supplier Device Package        | 356-BGA (35x35)                                              |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k50vbc356-4n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### LE Operating Modes

The FLEX 10K LE can operate in the following four modes:

- Normal mode

- Arithmetic mode

- Up/down counter mode

- Clearable counter mode

Each of these modes uses LE resources differently. In each mode, seven available inputs to the LE—the four data inputs from the LAB local interconnect, the feedback from the programmable register, and the carry-in and cascade-in from the previous LE—are directed to different destinations to implement the desired logic function. Three inputs to the LE provide clock, clear, and preset control for the register. The Altera software, in conjunction with parameterized functions such as LPM and DesignWare functions, automatically chooses the appropriate mode for common functions such as counters, adders, and multipliers. If required, the designer can also create special-purpose functions which use a specific LE operating mode for optimal performance.

The architecture provides a synchronous clock enable to the register in all four modes. The Altera software can set DATA1 to enable the register synchronously, providing easy implementation of fully synchronous designs.

Figure 9 shows the LE operating modes.

| Table 8. EPF10K10, EPF10K20, | EPF10K30, EPF         | 10K40 & EPF10 | K50 Periphera         | l Bus Sources |                       |

|------------------------------|-----------------------|---------------|-----------------------|---------------|-----------------------|

| Peripheral<br>Control Signal | EPF10K10<br>EPF10K10A | EPF10K20      | EPF10K30<br>EPF10K30A | EPF10K40      | EPF10K50<br>EPF10K50V |

| OE0                          | Row A                 | Row A         | Row A                 | Row A         | Row A                 |

| OE1                          | Row A                 | Row B         | Row B                 | Row C         | Row B                 |

| OE2                          | Row B                 | Row C         | Row C                 | Row D         | Row D                 |

| OE3                          | Row B                 | Row D         | Row D                 | Row E         | Row F                 |

| OE4                          | Row C                 | Row E         | Row E                 | Row F         | Row H                 |

| OE5                          | Row C                 | Row F         | Row F                 | Row G         | Row J                 |

| CLKENA0/CLK0/GLOBAL0         | Row A                 | Row A         | Row A                 | Row B         | Row A                 |

| CLKENA1/OE6/GLOBAL1          | Row A                 | Row B         | Row B                 | Row C         | Row C                 |

| CLKENA2/CLR0                 | Row B                 | Row C         | Row C                 | Row D         | Row E                 |

| CLKENA3/OE7/GLOBAL2          | Row B                 | Row D         | Row D                 | Row E         | Row G                 |

| CLKENA4/CLR1                 | Row C                 | Row E         | Row E                 | Row F         | Row I                 |

| CLKENA5/CLK1/GLOBAL3         | Row C                 | Row F         | Row F                 | Row H         | Row J                 |

| Peripheral<br>Control Signal | EPF10K70 | EPF10K100<br>EPF10K100A | EPF10K130V | EPF10K250A |

|------------------------------|----------|-------------------------|------------|------------|

| OE 0                         | Row A    | Row A                   | Row C      | Row E      |

| OE1                          | Row B    | Row C                   | Row E      | Row G      |

| OE2                          | Row D    | Row E                   | Row G      | Row I      |

| OE3                          | Row I    | Row L                   | Row N      | Row P      |

| OE 4                         | Row G    | Row I                   | Row K      | Row M      |

| OE5                          | Row H    | Row K                   | Row M      | Row O      |

| CLKENA0/CLK0/GLOBAL0         | Row E    | Row F                   | Row H      | Row J      |

| CLKENA1/OE6/GLOBAL1          | Row C    | Row D                   | Row F      | Row H      |

| CLKENA2/CLR0                 | Row B    | Row B                   | Row D      | Row F      |

| CLKENA3/OE7/GLOBAL2          | Row F    | Row H                   | Row J      | Row L      |

| CLKENA4/CLR1                 | Row H    | Row J                   | Row L      | Row N      |

| CLKENA5/CLK1/GLOBAL3         | Row E    | Row G                   | Row I      | Row K      |

Table 10 lists the FLEX 10K row-to-IOE interconnect resources.

| Device                  | Channels per Row (n) | Row Channels per Pin ( <i>m</i> ) |

|-------------------------|----------------------|-----------------------------------|

| EPF10K10<br>EPF10K10A   | 144                  | 18                                |

| EPF10K20                | 144                  | 18                                |

| EPF10K30<br>EPF10K30A   | 216                  | 27                                |

| EPF10K40                | 216                  | 27                                |

| EPF10K50<br>EPF10K50V   | 216                  | 27                                |

| EPF10K70                | 312                  | 39                                |

| EPF10K100<br>EPF10K100A | 312                  | 39                                |

| EPF10K130V              | 312                  | 39                                |

| EPF10K250A              | 456                  | 57                                |

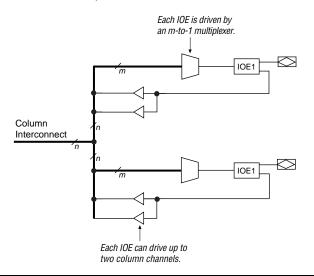

#### Column-to-IOE Connections

When an IOE is used as an input, it can drive up to two separate column channels. When an IOE is used as an output, the signal is driven by a multiplexer that selects a signal from the column channels. Two IOEs connect to each side of the column channels. Each IOE can be driven by column channels via a multiplexer. The set of column channels that each IOE can access is different for each IOE. See Figure 15.

Figure 15. FLEX 10K Column-to-IOE Connections

The values for m and n are provided in Table 11.

Table 11 lists the FLEX 10K column-to-IOE interconnect resources.

| Table 11. FLEX 10       | OK Column-to-IOE Interconnec | ct Resources               |

|-------------------------|------------------------------|----------------------------|

| Device                  | Channels per Column (n)      | Column Channel per Pin (m) |

| EPF10K10<br>EPF10K10A   | 24                           | 16                         |

| EPF10K20                | 24                           | 16                         |

| EPF10K30<br>EPF10K30A   | 24                           | 16                         |

| EPF10K40                | 24                           | 16                         |

| EPF10K50<br>EPF10K50V   | 24                           | 16                         |

| EPF10K70                | 24                           | 16                         |

| EPF10K100<br>EPF10K100A | 24                           | 16                         |

| EPF10K130V              | 32                           | 24                         |

| EPF10K250A              | 40                           | 32                         |

Table 12 describes the FLEX 10K device supply voltages and MultiVolt  $\rm I/O$  support levels.

| Devices       | Supply Voltage (V) |                   | MultiVolt I/O Support Levels (V) |            |

|---------------|--------------------|-------------------|----------------------------------|------------|

|               | V <sub>CCINT</sub> | V <sub>CCIO</sub> | Input                            | Output     |

| FLEX 10K (1)  | 5.0                | 5.0               | 3.3 or 5.0                       | 5.0        |

|               | 5.0                | 3.3               | 3.3 or 5.0                       | 3.3 or 5.0 |

| EPF10K50V (1) | 3.3                | 3.3               | 3.3 or 5.0                       | 3.3 or 5.0 |

| EPF10K130V    | 3.3                | 3.3               | 3.3 or 5.0                       | 3.3 or 5.0 |

| FLEX 10KA (1) | 3.3                | 3.3               | 2.5, 3.3, or 5.0                 | 3.3 or 5.0 |

|               | 3.3                | 2.5               | 2.5, 3.3, or 5.0                 | 2.5        |

#### Note

(1) 240-pin QFP packages do not support the MultiVolt I/O features, so they do not have separate V<sub>CCIO</sub> pins.

#### Power Sequencing & Hot-Socketing

Because FLEX 10K devices can be used in a multi-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. The  $V_{\rm CCIO}$  and  $V_{\rm CCINT}$  power supplies can be powered in any order.

Signals can be driven into FLEX 10KA devices before and during power up without damaging the device. Additionally, FLEX 10KA devices do not drive out during power up. Once operating conditions are reached, FLEX 10KA devices operate as specified by the user.

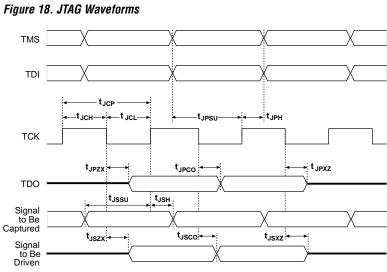

IEEE Std. 1149.1 (JTAG) Boundary-Scan Support All FLEX 10K devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1-1990 specification. All FLEX 10K devices can also be configured using the JTAG pins through the BitBlaster serial download cable, or ByteBlasterMV parallel port download cable, or via hardware that uses the Jam<sup>TM</sup> programming and test language. JTAG BST can be performed before or after configuration, but not during configuration. FLEX 10K devices support the JTAG instructions shown in Table 13.

Figure 18 shows the timing requirements for the JTAG signals.

Table 16 shows the timing parameters and values for FLEX 10K devices.

| Table 1           | Table 16. JTAG Timing Parameters & Values      |     |     |      |  |  |  |

|-------------------|------------------------------------------------|-----|-----|------|--|--|--|

| Symbol            | Parameter                                      | Min | Max | Unit |  |  |  |

| t <sub>JCP</sub>  | TCK clock period                               | 100 |     | ns   |  |  |  |

| t <sub>JCH</sub>  | TCK clock high time                            | 50  |     | ns   |  |  |  |

| t <sub>JCL</sub>  | TCK clock low time                             | 50  |     | ns   |  |  |  |

| t <sub>JPSU</sub> | JTAG port setup time                           | 20  |     | ns   |  |  |  |

| t <sub>JPH</sub>  | JTAG port hold time                            | 45  |     | ns   |  |  |  |

| t <sub>JPCO</sub> | JTAG port clock to output                      |     | 25  | ns   |  |  |  |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output       |     | 25  | ns   |  |  |  |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance       |     | 25  | ns   |  |  |  |

| t <sub>JSSU</sub> | Capture register setup time                    | 20  |     | ns   |  |  |  |

| t <sub>JSH</sub>  | Capture register hold time                     | 45  |     | ns   |  |  |  |

| t <sub>JSCO</sub> | Update register clock to output                |     | 35  | ns   |  |  |  |

| t <sub>JSZX</sub> | Update register high-impedance to valid output |     | 35  | ns   |  |  |  |

| t <sub>JSXZ</sub> | Update register valid output to high impedance |     | 35  | ns   |  |  |  |

### **Generic Testing**

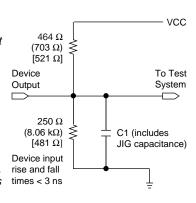

Each FLEX 10K device is functionally tested. Complete testing of each configurable SRAM bit and all logic functionality ensures 100% yield. AC test measurements for FLEX 10K devices are made under conditions equivalent to those shown in Figure 19. Multiple test patterns can be used to configure devices during all stages of the production flow.

#### Figure 19. FLEX 10K AC Test Conditions

Power supply transients can affect AC measurements. Simultaneous transitions of multiple outputs should be avoided for accurate measurement. Threshold tests must not be performed under AC conditions. Large-amplitude, fast-ground-current transients normally occur as the device outputs discharge the load capacitances. When these transients flow through the parasitic inductance between the device ground pin and the test system ground, significant reductions in observable noise immunity can result. Numbers without parentheses are for 5.0-V devices or outputs. Numbers in parentheses are for 3.3-V devices or outputs. Numbers in brackets are for 2.5-V devices or outputs.

## Operating Conditions

Tables 17 through 21 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 5.0-V FLEX 10K devices.

| Table 17. FLEX 10K 5.0-V Device Absolute Maximum Ratings     Note (1) |                            |                              |      |     |      |

|-----------------------------------------------------------------------|----------------------------|------------------------------|------|-----|------|

| Symbol                                                                | Parameter                  | Conditions                   | Min  | Max | Unit |

| V <sub>CC</sub>                                                       | Supply voltage             | With respect to ground (2)   | -2.0 | 7.0 | V    |

| V <sub>I</sub>                                                        | DC input voltage           |                              | -2.0 | 7.0 | V    |

| I <sub>OUT</sub>                                                      | DC output current, per pin |                              | -25  | 25  | mA   |

| T <sub>STG</sub>                                                      | Storage temperature        | No bias                      | -65  | 150 | ° C  |

| T <sub>AMB</sub>                                                      | Ambient temperature        | Under bias                   | -65  | 135 | ° C  |

| T <sub>J</sub>                                                        | Junction temperature       | Ceramic packages, under bias |      | 150 | ° C  |

|                                                                       |                            | PQFP, TQFP, RQFP, and BGA    |      | 135 | ° C  |

|                                                                       |                            | packages, under bias         |      |     |      |

Tables 22 through 25 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for EPF10K50V and EPF10K130V devices.

| Table 22. EPF10K50V & EPF10K130V Device Absolute Maximum Ratings       Note (1) |                            |                                   |      |      |      |

|---------------------------------------------------------------------------------|----------------------------|-----------------------------------|------|------|------|

| Symbol                                                                          | Parameter                  | Conditions                        | Min  | Max  | Unit |

| V <sub>CC</sub>                                                                 | Supply voltage             | With respect to ground (2)        | -0.5 | 4.6  | V    |

| VI                                                                              | DC input voltage           |                                   | -2.0 | 5.75 | V    |

| I <sub>OUT</sub>                                                                | DC output current, per pin |                                   | -25  | 25   | mA   |

| T <sub>STG</sub>                                                                | Storage temperature        | No bias                           | -65  | 150  | ° C  |

| T <sub>AMB</sub>                                                                | Ambient temperature        | Under bias                        | -65  | 135  | ° C  |

| TJ                                                                              | Junction temperature       | Ceramic packages, under bias      |      | 150  | ° C  |

|                                                                                 |                            | RQFP and BGA packages, under bias |      | 135  | ° C  |

| Symbol             | Parameter                                           | Conditions         | Min         | Max               | Unit |

|--------------------|-----------------------------------------------------|--------------------|-------------|-------------------|------|

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers | (3), (4)           | 3.00 (3.00) | 3.60 (3.60)       | V    |

| V <sub>CCIO</sub>  | Supply voltage for output buffers                   | (3), (4)           | 3.00 (3.00) | 3.60 (3.60)       | V    |

| V <sub>I</sub>     | Input voltage                                       | (5)                | -0.5        | 5.75              | V    |

| Vo                 | Output voltage                                      |                    | 0           | V <sub>CCIO</sub> | V    |

| T <sub>A</sub>     | Ambient temperature                                 | For commercial use | 0           | 70                | °C   |

|                    |                                                     | For industrial use | -40         | 85                | ° C  |

| TJ                 | Operating temperature                               | For commercial use | 0           | 85                | ° C  |

|                    |                                                     | For industrial use | -40         | 100               | ° C  |

| t <sub>R</sub>     | Input rise time                                     |                    |             | 40                | ns   |

| t <sub>F</sub>     | Input fall time                                     |                    |             | 40                | ns   |

| Symbol           | Parameter                                | Conditions                                     | Min                     | Typ | Max  | Unit |

|------------------|------------------------------------------|------------------------------------------------|-------------------------|-----|------|------|

| V <sub>IH</sub>  | High-level input voltage                 |                                                | 2.0                     |     | 5.75 | V    |

| V <sub>IL</sub>  | Low-level input voltage                  |                                                | -0.5                    |     | 0.8  | V    |

| V <sub>OH</sub>  | 3.3-V high-level TTL output voltage      | $I_{OH} = -8 \text{ mA DC } (8)$               | 2.4                     |     |      | V    |

|                  | 3.3-V high-level CMOS output voltage     | $I_{OH} = -0.1 \text{ mA DC } (8)$             | V <sub>CCIO</sub> - 0.2 |     |      | V    |

| V <sub>OL</sub>  | 3.3-V low-level TTL output voltage       | I <sub>OL</sub> = 8 mA DC (9)                  |                         |     | 0.45 | V    |

|                  | 3.3-V low-level CMOS output voltage      | I <sub>OL</sub> = 0.1 mA DC (9)                |                         |     | 0.2  | V    |

| I <sub>I</sub>   | Input pin leakage current                | $V_1 = 5.3 \text{ V to } -0.3 \text{ V } (10)$ | -10                     |     | 10   | μА   |

| I <sub>OZ</sub>  | Tri-stated I/O pin leakage current       | $V_O = 5.3 \text{ V to } -0.3 \text{ V } (10)$ | -10                     |     | 10   | μΑ   |

| I <sub>CC0</sub> | V <sub>CC</sub> supply current (standby) | V <sub>I</sub> = ground, no load               |                         | 0.3 | 10   | mA   |

|                  |                                          | $V_I$ = ground, no load (11)                   |                         | 10  |      | mA   |

| Table 25. EPF10K50V & EPF10K130V Device Capacitance (12) |                                          |                                     |     |     |      |  |

|----------------------------------------------------------|------------------------------------------|-------------------------------------|-----|-----|------|--|

| Symbol                                                   | Parameter                                | Conditions                          | Min | Max | Unit |  |

| C <sub>IN</sub>                                          | Input capacitance                        | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 10  | pF   |  |

| C <sub>INCLK</sub>                                       | Input capacitance on dedicated clock pin | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 15  | pF   |  |

| C <sub>OUT</sub>                                         | Output capacitance                       | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 10  | pF   |  |

#### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $V_{CC}$  rise time is 100 ms.  $V_{CC}$  must rise monotonically.

- (5) EPF10K50V and EPF10K130V device inputs may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (6) Typical values are for  $T_A = 25^{\circ}$  C and  $V_{CC} = 3.3$  V.

- (7) These values are specified under the EPF10K50V and EPF10K130V device Recommended Operating Conditions in Table 23 on page 48.

- (8) The I<sub>OH</sub> parameter refers to high-level TTL or CMOS output current.

- (9) The I<sub>OL</sub> parameter refers to low-level TTL or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (10) This value is specified for normal device operation. The value may vary during power-up.

- (11) This parameter applies to -1 speed grade EPF10K50V devices, -2 speed grade EPF10K50V industrial temperature devices, and -2 speed grade EPF10K130V devices.

- (12) Capacitance is sample-tested only.

Figure 22 shows the typical output drive characteristics of EPF10K10A, EPF10K30A, EPF10K100A, and EPF10K250A devices with 3.3-V and 2.5-V V<sub>CCIO</sub>. The output driver is compliant with the 3.3-V *PCI Local Bus Specification, Revision 2.2* (with 3.3-V V<sub>CCIO</sub>). Moreover, device analysis shows that the EPF10K10A, EPF10K30A, and EPF 10K100A devices can drive a 5.0-V PCI bus with eight or fewer loads.

60 H 60 H  $I_{OL}$  $I_{OL}$ 50 50 40 40  $V_{CCINT} = 3.3 V$  $V_{CCINT} = 3.3 V$  $V_{CCIO} = 3.3 V$  $V_{CCIO} = 2.5 V$ Typical I<sub>O</sub> Typical I<sub>O</sub> Room Temperature Room Temperature 30 30 Output Output Current (mA) Current (mA) 20 20 10 10  $I_{OH}$  $I_{OH}$ V<sub>O</sub> Output Voltage (V) Vo Output Voltage (V)

Figure 22. Output Drive Characteristics for EPF10K10A, EPF10K30A & EPF10K100A Devices

Figure 23 shows the typical output drive characteristics of the EPF10K250A device with 3.3-V and 2.5-V  $V_{\rm CCIO}$ .

| Symbol                 | -3 Spee | d Grade | -4 Spee | d Grade | Unit |

|------------------------|---------|---------|---------|---------|------|

|                        | Min     | Max     | Min     | Max     |      |

| t <sub>EABDATA1</sub>  |         | 1.5     |         | 1.9     | ns   |

| t <sub>EABDATA2</sub>  |         | 4.8     |         | 6.0     | ns   |

| t <sub>EABWE1</sub>    |         | 1.0     |         | 1.2     | ns   |

| t <sub>EABWE2</sub>    |         | 5.0     |         | 6.2     | ns   |

| t <sub>EABCLK</sub>    |         | 1.0     |         | 2.2     | ns   |

| t <sub>EABCO</sub>     |         | 0.5     |         | 0.6     | ns   |

| t <sub>EABBYPASS</sub> |         | 1.5     |         | 1.9     | ns   |

| t <sub>EABSU</sub>     | 1.5     |         | 1.8     |         | ns   |

| t <sub>EABH</sub>      | 2.0     |         | 2.5     |         | ns   |

| $t_{AA}$               |         | 8.7     |         | 10.7    | ns   |

| $t_{WP}$               | 5.8     |         | 7.2     |         | ns   |

| t <sub>WDSU</sub>      | 1.6     |         | 2.0     |         | ns   |

| t <sub>WDH</sub>       | 0.3     |         | 0.4     |         | ns   |

| t <sub>WASU</sub>      | 0.5     |         | 0.6     |         | ns   |

| $t_{WAH}$              | 1.0     |         | 1.2     |         | ns   |

| $t_{WO}$               |         | 5.0     |         | 6.2     | ns   |

| $t_{DD}$               |         | 5.0     |         | 6.2     | ns   |

| t <sub>EABOUT</sub>    |         | 0.5     |         | 0.6     | ns   |

| t <sub>EABCH</sub>     | 4.0     |         | 4.0     |         | ns   |

| t <sub>EABCL</sub>     | 5.8     |         | 7.2     |         | ns   |

| Table 45. EPF10K10 & EPF1  | OK20 Device Exter | nal Timing Para | ameters No | te (1)   |      |

|----------------------------|-------------------|-----------------|------------|----------|------|

| Symbol                     | -3 Spe            | ed Grade        | -4 Spee    | ed Grade | Unit |

|                            | Min               | Max             | Min        | Max      |      |

| t <sub>DRR</sub>           |                   | 16.1            |            | 20.0     | ns   |

| t <sub>INSU</sub> (2), (3) | 5.5               |                 | 6.0        |          | ns   |

| t <sub>INH</sub> (3)       | 0.0               |                 | 0.0        |          | ns   |

| t <sub>оитсо</sub> (3)     | 2.0               | 6.7             | 2.0        | 8.4      | ns   |

| Table 46. EPF10K10 Device | External Bidirectio | nal Timing Par | <b>ameters</b> No | te (1)   |      |

|---------------------------|---------------------|----------------|-------------------|----------|------|

| Symbol                    | -3 Spe              | ed Grade       | -4 Spee           | ed Grade | Unit |

|                           | Min                 | Max            | Min               | Max      |      |

| t <sub>INSUBIDIR</sub>    | 4.5                 |                | 5.6               |          | ns   |

| t <sub>INHBIDIR</sub>     | 0.0                 |                | 0.0               |          | ns   |

| t <sub>OUTCOBIDIR</sub>   | 2.0                 | 6.7            | 2.0               | 8.4      | ns   |

| t <sub>XZBIDIR</sub>      |                     | 10.5           |                   | 13.4     | ns   |

| t <sub>ZXBIDIR</sub>      |                     | 10.5           |                   | 13.4     | ns   |

| Symbol                  | -3 Spec | ed Grade | -4 Spee | d Grade | Unit |

|-------------------------|---------|----------|---------|---------|------|

|                         | Min     | Max      | Min     | Max     |      |

| t <sub>INSUBIDIR</sub>  | 4.6     |          | 5.7     |         | ns   |

| t <sub>INHBIDIR</sub>   | 0.0     |          | 0.0     |         | ns   |

| t <sub>OUTCOBIDIR</sub> | 2.0     | 6.7      | 2.0     | 8.4     | ns   |

| t <sub>XZBIDIR</sub>    |         | 10.5     |         | 13.4    | ns   |

| t <sub>ZXBIDIR</sub>    |         | 10.5     |         | 13.4    | ns   |

#### Notes to tables:

- All timing parameters are described in Tables 32 through 38 in this data sheet.

Using an LE to register the signal may provide a lower setup time.

This parameter is specified by characterization.

| Symbol                 | -3 Snee | d Grade | -4 Spee | Unit |       |

|------------------------|---------|---------|---------|------|-------|

| Symbol                 | -       |         |         |      | Oiiit |

|                        | Min     | Max     | Min     | Max  |       |

| t <sub>EABAA</sub>     |         | 13.7    |         | 17.0 | ns    |

| t <sub>EABRCCOMB</sub> | 13.7    |         | 17.0    |      | ns    |

| t <sub>EABRCREG</sub>  | 9.7     |         | 11.9    |      | ns    |

| t <sub>EABWP</sub>     | 5.8     |         | 7.2     |      | ns    |

| t <sub>EABWCCOMB</sub> | 7.3     |         | 9.0     |      | ns    |

| t <sub>EABWCREG</sub>  | 13.0    |         | 16.0    |      | ns    |

| t <sub>EABDD</sub>     |         | 10.0    |         | 12.5 | ns    |

| t <sub>EABDATACO</sub> |         | 2.0     |         | 3.4  | ns    |

| t <sub>EABDATASU</sub> | 5.3     |         | 5.6     |      | ns    |

| t <sub>EABDATAH</sub>  | 0.0     |         | 0.0     |      | ns    |

| t <sub>EABWESU</sub>   | 5.5     |         | 5.8     |      | ns    |

| t <sub>EABWEH</sub>    | 0.0     |         | 0.0     |      | ns    |

| t <sub>EABWDSU</sub>   | 5.5     |         | 5.8     |      | ns    |

| t <sub>EABWDH</sub>    | 0.0     |         | 0.0     |      | ns    |

| t <sub>EABWASU</sub>   | 2.1     |         | 2.7     |      | ns    |

| t <sub>EABWAH</sub>    | 0.0     |         | 0.0     |      | ns    |

| $t_{EABWO}$            |         | 9.5     |         | 11.8 | ns    |

Tables 71 through 77 show EPF10K50V device internal and external timing parameters.

| Symbol              | -1 Spee | ed Grade | -2 Spee | d Grade | -3 Spee | ed Grade | -4 Spee | d Grade | Unit |

|---------------------|---------|----------|---------|---------|---------|----------|---------|---------|------|

|                     | Min     | Max      | Min     | Max     | Min     | Max      | Min     | Max     |      |

| t <sub>LUT</sub>    |         | 0.9      |         | 1.0     |         | 1.3      |         | 1.6     | ns   |

| t <sub>CLUT</sub>   |         | 0.1      |         | 0.5     |         | 0.6      |         | 0.6     | ns   |

| t <sub>RLUT</sub>   |         | 0.5      |         | 8.0     |         | 0.9      |         | 1.0     | ns   |

| t <sub>PACKED</sub> |         | 0.4      |         | 0.4     |         | 0.5      |         | 0.7     | ns   |

| t <sub>EN</sub>     |         | 0.7      |         | 0.9     |         | 1.1      |         | 1.4     | ns   |

| t <sub>CICO</sub>   |         | 0.2      |         | 0.2     |         | 0.2      |         | 0.3     | ns   |

| t <sub>CGEN</sub>   |         | 0.8      |         | 0.7     |         | 8.0      |         | 1.2     | ns   |

| t <sub>CGENR</sub>  |         | 0.4      |         | 0.3     |         | 0.3      |         | 0.4     | ns   |

| t <sub>CASC</sub>   |         | 0.7      |         | 0.7     |         | 8.0      |         | 0.9     | ns   |

| $t_{C}$             |         | 0.3      |         | 1.0     |         | 1.3      |         | 1.5     | ns   |

| $t_{\rm CO}$        |         | 0.5      |         | 0.7     |         | 0.9      |         | 1.0     | ns   |

| t <sub>COMB</sub>   |         | 0.4      |         | 0.4     |         | 0.5      |         | 0.6     | ns   |

| $t_{SU}$            | 0.8     |          | 1.6     |         | 2.2     |          | 2.5     |         | ns   |

| $t_H$               | 0.5     |          | 0.8     |         | 1.0     |          | 1.4     |         | ns   |

| t <sub>PRE</sub>    |         | 0.8      |         | 0.4     |         | 0.5      |         | 0.5     | ns   |

| t <sub>CLR</sub>    |         | 0.8      |         | 0.4     |         | 0.5      |         | 0.5     | ns   |

| t <sub>CH</sub>     | 2.0     |          | 4.0     |         | 4.0     |          | 4.0     |         | ns   |

| $t_{CL}$            | 2.0     |          | 4.0     |         | 4.0     |          | 4.0     |         | ns   |

| Symbol                   | -1 Spee | ed Grade | -2 Spee | d Grade | -3 Spee | ed Grade | -4 Spee | d Grade | Unit |

|--------------------------|---------|----------|---------|---------|---------|----------|---------|---------|------|

| •,                       | Min     | Max      | Min     | Max     | Min     | Max      | Min     | Max     | -    |

| t <sub>DIN2IOE</sub>     |         | 4.7      |         | 6.0     |         | 7.1      |         | 8.2     | ns   |

| t <sub>DIN2LE</sub>      |         | 2.5      |         | 2.6     |         | 3.1      |         | 3.9     | ns   |

| t <sub>DIN2DATA</sub>    |         | 4.4      |         | 5.9     |         | 6.8      |         | 7.7     | ns   |

| t <sub>DCLK2IOE</sub>    |         | 2.5      |         | 3.9     |         | 4.7      |         | 5.5     | ns   |

| t <sub>DCLK2LE</sub>     |         | 2.5      |         | 2.6     |         | 3.1      |         | 3.9     | ns   |

| t <sub>SAMELAB</sub>     |         | 0.2      |         | 0.2     |         | 0.3      |         | 0.3     | ns   |

| t <sub>SAMEROW</sub>     |         | 2.8      |         | 3.0     |         | 3.2      |         | 3.4     | ns   |

| t <sub>SAME</sub> COLUMN |         | 3.0      |         | 3.2     |         | 3.4      |         | 3.6     | ns   |

| t <sub>DIFFROW</sub>     |         | 5.8      |         | 6.2     |         | 6.6      |         | 7.0     | ns   |

| t <sub>TWOROWS</sub>     |         | 8.6      |         | 9.2     |         | 9.8      |         | 10.4    | ns   |

| t <sub>LEPERIPH</sub>    |         | 4.5      |         | 5.5     |         | 6.1      |         | 7.0     | ns   |

| t <sub>LABCARRY</sub>    |         | 0.3      |         | 0.4     |         | 0.5      |         | 0.7     | ns   |

| t <sub>LABCASC</sub>     |         | 0.0      |         | 1.3     |         | 1.6      |         | 2.0     | ns   |

| Table 76. EPF              | 10K50V De | vice Exter | nal Timing | Paramete | ers Not | e (1)   |         |         |      |

|----------------------------|-----------|------------|------------|----------|---------|---------|---------|---------|------|

| Symbol                     | -1 Spee   | d Grade    | -2 Spee    | d Grade  | -3 Spee | d Grade | -4 Spee | d Grade | Unit |

|                            | Min       | Max        | Min        | Max      | Min     | Max     | Min     | Max     |      |

| t <sub>DRR</sub>           |           | 11.2       |            | 14.0     |         | 17.2    |         | 21.1    | ns   |

| t <sub>INSU</sub> (2), (3) | 5.5       |            | 4.2        |          | 5.2     |         | 6.9     |         | ns   |

| t <sub>INH</sub> (3)       | 0.0       |            | 0.0        |          | 0.0     |         | 0.0     |         | ns   |

| t <sub>оитсо</sub> (3)     | 2.0       | 5.9        | 2.0        | 7.8      | 2.0     | 9.5     | 2.0     | 11.1    | ns   |

| Table 77. EPF           | 10K50V De | vice Exter     | nal Bidired | ctional Tim       | ing Param | neters  | Vote (1) |                |    |

|-------------------------|-----------|----------------|-------------|-------------------|-----------|---------|----------|----------------|----|

| Symbol                  | -1 Spee   | -1 Speed Grade |             | ed Grade -3 Speed |           | d Grade | -4 Spee  | -4 Speed Grade |    |

|                         | Min       | Max            | Min         | Max               | Min       | Max     | Min      | Max            | ]  |

| t <sub>INSUBIDIR</sub>  | 2.0       |                | 2.8         |                   | 3.5       |         | 4.1      |                | ns |

| t <sub>INHBIDIR</sub>   | 0.0       |                | 0.0         |                   | 0.0       |         | 0.0      |                | ns |

| t <sub>OUTCOBIDIR</sub> | 2.0       | 5.9            | 2.0         | 7.8               | 2.0       | 9.5     | 2.0      | 11.1           | ns |

| t <sub>XZBIDIR</sub>    |           | 8.0            |             | 9.8               |           | 11.8    |          | 14.3           | ns |

| t <sub>ZXBIDIR</sub>    |           | 8.0            |             | 9.8               |           | 11.8    |          | 14.3           | ns |

| Symbol                 | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | d Grade | Unit |

|------------------------|---------|---------|---------|---------|---------|---------|------|

|                        | Min     | Max     | Min     | Max     | Min     | Max     |      |

| t <sub>EABDATA1</sub>  |         | 1.8     |         | 2.1     |         | 2.4     | ns   |

| t <sub>EABDATA2</sub>  |         | 3.2     |         | 3.7     |         | 4.4     | ns   |

| t <sub>EABWE1</sub>    |         | 0.8     |         | 0.9     |         | 1.1     | ns   |

| t <sub>EABWE2</sub>    |         | 2.3     |         | 2.7     |         | 3.1     | ns   |

| t <sub>EABCLK</sub>    |         | 0.8     |         | 0.9     |         | 1.1     | ns   |

| t <sub>EABCO</sub>     |         | 1.0     |         | 1.1     |         | 1.4     | ns   |

| t <sub>EABBYPASS</sub> |         | 0.3     |         | 0.3     |         | 0.4     | ns   |

| t <sub>EABSU</sub>     | 1.3     |         | 1.5     |         | 1.8     |         | ns   |

| t <sub>EABH</sub>      | 0.4     |         | 0.5     |         | 0.5     |         | ns   |

| $t_{AA}$               |         | 4.1     |         | 4.8     |         | 5.6     | ns   |

| $t_{WP}$               | 3.2     |         | 3.7     |         | 4.4     |         | ns   |

| t <sub>WDSU</sub>      | 2.4     |         | 2.8     |         | 3.3     |         | ns   |

| $t_{WDH}$              | 0.2     |         | 0.2     |         | 0.3     |         | ns   |

| t <sub>WASU</sub>      | 0.2     |         | 0.2     |         | 0.3     |         | ns   |

| t <sub>WAH</sub>       | 0.0     |         | 0.0     |         | 0.0     |         | ns   |

| $t_{WO}$               |         | 3.4     |         | 3.9     |         | 4.6     | ns   |

| $t_{DD}$               |         | 3.4     |         | 3.9     |         | 4.6     | ns   |

| t <sub>EABOUT</sub>    |         | 0.3     |         | 0.3     |         | 0.4     | ns   |

| t <sub>EABCH</sub>     | 2.5     |         | 3.5     |         | 4.0     |         | ns   |

| t <sub>EABCL</sub>     | 3.2     |         | 3.7     |         | 4.4     |         | ns   |

| Symbol                 | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | Unit |    |

|------------------------|----------------|-----|---------|---------|---------|------|----|

|                        | Min            | Max | Min     | Max     | Min     | Max  |    |

| t <sub>EABAA</sub>     |                | 6.8 |         | 7.8     |         | 9.2  | ns |

| t <sub>EABRCCOMB</sub> | 6.8            |     | 7.8     |         | 9.2     |      | ns |

| t <sub>EABRCREG</sub>  | 5.4            |     | 6.2     |         | 7.4     |      | ns |

| t <sub>EABWP</sub>     | 3.2            |     | 3.7     |         | 4.4     |      | ns |

| t <sub>EABWCCOMB</sub> | 3.4            |     | 3.9     |         | 4.7     |      | ns |

| t <sub>EABWCREG</sub>  | 9.4            |     | 10.8    |         | 12.8    |      | ns |

| t <sub>EABDD</sub>     |                | 6.1 |         | 6.9     |         | 8.2  | ns |

| t <sub>EABDATACO</sub> |                | 2.1 |         | 2.3     |         | 2.9  | ns |

| t <sub>EABDATASU</sub> | 3.7            |     | 4.3     |         | 5.1     |      | ns |

| t <sub>EABDATAH</sub>  | 0.0            |     | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWESU</sub>   | 2.8            |     | 3.3     |         | 3.8     |      | ns |

| t <sub>EABWEH</sub>    | 0.0            |     | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWDSU</sub>   | 3.4            |     | 4.0     |         | 4.6     |      | ns |

| t <sub>EABWDH</sub>    | 0.0            |     | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWASU</sub>   | 1.9            |     | 2.3     |         | 2.6     |      | ns |

| t <sub>EABWAH</sub>    | 0.0            |     | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWO</sub>     |                | 5.1 |         | 5.7     |         | 6.9  | ns |

| Symbol                   | -1 Spee | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |    |  |

|--------------------------|---------|----------------|-----|----------------|-----|----------------|----|--|

|                          | Min     | Max            | Min | Max            | Min | Max            |    |  |

| t <sub>DIN2IOE</sub>     |         | 4.8            |     | 5.4            |     | 6.0            | ns |  |

| t <sub>DIN2LE</sub>      |         | 2.0            |     | 2.4            |     | 2.7            | ns |  |

| t <sub>DIN2DATA</sub>    |         | 2.4            |     | 2.7            |     | 2.9            | ns |  |

| t <sub>DCLK2IOE</sub>    |         | 2.6            |     | 3.0            |     | 3.5            | ns |  |

| t <sub>DCLK2LE</sub>     |         | 2.0            |     | 2.4            |     | 2.7            | ns |  |

| t <sub>SAMELAB</sub>     |         | 0.1            |     | 0.1            |     | 0.1            | ns |  |

| t <sub>SAMEROW</sub>     |         | 1.5            |     | 1.7            |     | 1.9            | ns |  |

| t <sub>SAME</sub> COLUMN |         | 5.5            |     | 6.5            |     | 7.4            | ns |  |

| t <sub>DIFFROW</sub>     |         | 7.0            |     | 8.2            |     | 9.3            | ns |  |

| t <sub>TWOROWS</sub>     |         | 8.5            |     | 9.9            |     | 11.2           | ns |  |

| t <sub>LEPERIPH</sub>    |         | 3.9            |     | 4.2            |     | 4.5            | ns |  |

| t <sub>LABCARRY</sub>    |         | 0.2            |     | 0.2            |     | 0.3            | ns |  |

| t <sub>LABCASC</sub>     |         | 0.4            |     | 0.5            |     | 0.6            | ns |  |

| Table 104. EPF10K100A Device External Timing Parameters Note (1) |                |      |                |      |                |      |      |  |  |

|------------------------------------------------------------------|----------------|------|----------------|------|----------------|------|------|--|--|

| Symbol                                                           | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |  |  |

|                                                                  | Min            | Max  | Min            | Max  | Min            | Max  |      |  |  |

| t <sub>DRR</sub>                                                 |                | 12.5 |                | 14.5 |                | 17.0 | ns   |  |  |

| t <sub>INSU</sub> (2), (3)                                       | 3.7            |      | 4.5            |      | 5.1            |      | ns   |  |  |

| t <sub>INH</sub> (3)                                             | 0.0            |      | 0.0            |      | 0.0            |      | ns   |  |  |

| t <sub>outco</sub> (3)                                           | 2.0            | 5.3  | 2.0            | 6.1  | 2.0            | 7.2  | ns   |  |  |

| Table 105. EPF10K100A Device External Bidirectional Timing Parameters       Note (1) |                |     |                |     |                |      |      |  |  |

|--------------------------------------------------------------------------------------|----------------|-----|----------------|-----|----------------|------|------|--|--|

| Symbol                                                                               | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |      | Unit |  |  |

|                                                                                      | Min            | Max | Min            | Max | Min            | Max  |      |  |  |

| t <sub>INSUBIDIR</sub>                                                               | 4.9            |     | 5.8            |     | 6.8            |      | ns   |  |  |

| t <sub>INHBIDIR</sub>                                                                | 0.0            |     | 0.0            |     | 0.0            |      | ns   |  |  |

| toutcobidir                                                                          | 2.0            | 5.3 | 2.0            | 6.1 | 2.0            | 7.2  | ns   |  |  |

| t <sub>XZBIDIR</sub>                                                                 |                | 7.4 |                | 8.6 |                | 10.1 | ns   |  |  |

| t <sub>ZXBIDIR</sub>                                                                 |                | 7.4 |                | 8.6 |                | 10.1 | ns   |  |  |

| Symbol                 | -1 Speed Grade |     | -2 Speed Grade |     | -3 Speed Grade |     | Unit |  |

|------------------------|----------------|-----|----------------|-----|----------------|-----|------|--|

|                        | Min            | Max | Min            | Max | Min            | Max |      |  |

| t <sub>EABAA</sub>     |                | 6.1 |                | 6.8 |                | 8.2 | ns   |  |

| t <sub>EABRCCOMB</sub> | 6.1            |     | 6.8            |     | 8.2            |     | ns   |  |

| t <sub>EABRCREG</sub>  | 4.6            |     | 5.1            |     | 6.1            |     | ns   |  |

| t <sub>EABWP</sub>     | 5.6            |     | 6.4            |     | 7.5            |     | ns   |  |

| t <sub>EABWCCOMB</sub> | 5.8            |     | 6.6            |     | 7.9            |     | ns   |  |

| t <sub>EABWCREG</sub>  | 15.8           |     | 17.8           |     | 21.0           |     | ns   |  |

| t <sub>EABDD</sub>     |                | 5.7 |                | 6.4 |                | 7.8 | ns   |  |

| t <sub>EABDATACO</sub> |                | 0.7 |                | 0.8 |                | 1.0 | ns   |  |

| t <sub>EABDATASU</sub> | 4.5            |     | 5.1            |     | 5.9            |     | ns   |  |

| t <sub>EABDATAH</sub>  | 0.0            |     | 0.0            |     | 0.0            |     | ns   |  |

| t <sub>EABWESU</sub>   | 8.2            |     | 9.3            |     | 10.9           |     | ns   |  |

| t <sub>EABWEH</sub>    | 0.0            |     | 0.0            |     | 0.0            |     | ns   |  |

| t <sub>EABWDSU</sub>   | 1.7            |     | 1.8            |     | 2.1            |     | ns   |  |

| t <sub>EABWDH</sub>    | 0.0            |     | 0.0            |     | 0.0            |     | ns   |  |

| t <sub>EABWASU</sub>   | 0.9            |     | 0.9            |     | 1.0            |     | ns   |  |

| t <sub>EABWAH</sub>    | 0.0            |     | 0.0            |     | 0.0            |     | ns   |  |

| t <sub>EABWO</sub>     |                | 5.3 |                | 6.0 |                | 7.4 | ns   |  |

| Table 113. ClockLock & ClockBoost Parameters (Part 2 of 2) |                                                                                                              |     |     |      |      |  |  |  |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|------|------|--|--|--|

| Symbol                                                     | Parameter                                                                                                    | Min | Тур | Max  | Unit |  |  |  |

| f <sub>CLKDEV1</sub>                                       | Input deviation from user specification in MAX+PLUS II (ClockBoost clock multiplication factor equals 1) (1) |     |     | ±1   | MHz  |  |  |  |

| f <sub>CLKDEV2</sub>                                       | Input deviation from user specification in MAX+PLUS II (ClockBoost clock multiplication factor equals 2) (1) |     |     | ±0.5 | MHz  |  |  |  |

| t <sub>INCLKSTB</sub>                                      | Input clock stability (measured between adjacent clocks)                                                     |     |     | 100  | ps   |  |  |  |

| t <sub>LOCK</sub>                                          | Time required for ClockLock or ClockBoost to acquire lock (2)                                                |     |     | 10   | μs   |  |  |  |

| t <sub>JITTER</sub>                                        | Jitter on ClockLock or ClockBoost-generated clock (3)                                                        |     |     | 1    | ns   |  |  |  |

| $t_{OUTDUTY}$                                              | Duty cycle for ClockLock or ClockBoost-generated clock                                                       | 40  | 50  | 60   | %    |  |  |  |

#### Notes:

- (1) To implement the ClockLock and ClockBoost circuitry with the MAX+PLUS II software, designers must specify the input frequency. The MAX+PLUS II software tunes the PLL in the ClockLock and ClockBoost circuitry to this frequency. The f<sub>CLKDEV</sub> parameter specifies how much the incoming clock can differ from the specified frequency during device operation. Simulation does not reflect this parameter.

- (2) During device configuration, the ClockLock and ClockBoost circuitry is configured before the rest of the device. If the incoming clock is supplied during configuration, the ClockLock and ClockBoost circuitry locks during configuration, because the t<sub>LOCK</sub> value is less than the time required for configuration.

- (3) The  $t_{IITTER}$  specification is measured under long-term observation.

# Power Consumption

The supply power (P) for FLEX 10K devices can be calculated with the following equation:

$$P = P_{INT} + P_{IO} = (I_{CCSTANDBY} + I_{CCACTIVE}) \times V_{CC} + P_{IO}$$

Typical  $I_{CCSTANDBY}$  values are shown as  $I_{CC0}$  in the FLEX 10K device DC operating conditions tables on pages 46, 49, and 52 of this data sheet. The  $I_{CCACTIVE}$  value depends on the switching frequency and the application logic. This value is calculated based on the amount of current that each LE typically consumes. The  $P_{IO}$  value, which depends on the device output load characteristics and switching frequency, can be calculated using the guidelines given in *Application Note 74 (Evaluating Power for Altera Devices)*.

Compared to the rest of the device, the embedded array consumes a negligible amount of power. Therefore, the embedded array can be ignored when calculating supply current.

The I<sub>CCACTIVE</sub> value is calculated with the following equation:

$$I_{CCACTIVE} = K \times \mathbf{f_{MAX}} \times N \times \mathbf{tog_{LC}} \times \frac{\mu A}{MHz \times LE}$$

The parameters in this equation are shown below: