# E·XFI

### Altera - EPF10K50VQC240-1N Datasheet

Welcome to <u>E-XFL.COM</u>

### Understanding Embedded - FPGAs (Field Programmable Gate Array)

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                |

|--------------------------------|----------------------------------------------------------------|

| Product Status                 | Active                                                         |

| Number of LABs/CLBs            | 360                                                            |

| Number of Logic Elements/Cells | -                                                              |

| Total RAM Bits                 | -                                                              |

| Number of I/O                  | 189                                                            |

| Number of Gates                | -                                                              |

| Voltage - Supply               | 3V ~ 3.6V                                                      |

| Mounting Type                  | Surface Mount                                                  |

| Operating Temperature          | 0°C ~ 70°C (TA)                                                |

| Package / Case                 | 240-BQFP                                                       |

| Supplier Device Package        | 240-PQFP (32x32)                                               |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=epf10k50vqc240-1n |

|                                |                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

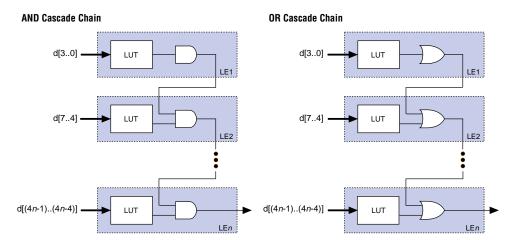

### Cascade Chain

With the cascade chain, the FLEX 10K architecture can implement functions that have a very wide fan-in. Adjacent LUTs can be used to compute portions of the function in parallel; the cascade chain serially connects the intermediate values. The cascade chain can use a logical AND or logical OR (via De Morgan's inversion) to connect the outputs of adjacent LEs. Each additional LE provides four more inputs to the effective width of a function, with a delay as low as 0.7 ns per LE. Cascade chain logic can be created automatically by the Compiler during design processing, or manually by the designer during design entry.

Cascade chains longer than eight bits are implemented automatically by linking several LABs together. For easier routing, a long cascade chain skips every other LAB in a row. A cascade chain longer than one LAB skips either from even-numbered LAB to even-numbered LAB, or from odd-numbered LAB to odd-numbered LAB (e.g., the last LE of the first LAB in a row cascades to the first LE of the third LAB). The cascade chain does not cross the center of the row (e.g., in the EPF10K50 device, the cascade chain stops at the eighteenth LAB and a new one begins at the nineteenth LAB). This break is due to the EAB's placement in the middle of the row.

Figure 8 shows how the cascade function can connect adjacent LEs to form functions with a wide fan-in. These examples show functions of 4n variables implemented with n LEs. The LE delay is as low as 1.6 ns; the cascade chain delay is as low as 0.7 ns. With the cascade chain, 3.7 ns is needed to decode a 16-bit address.

### Figure 8. Cascade Chain Operation

Altera Corporation

### Normal Mode

The normal mode is suitable for general logic applications and wide decoding functions that can take advantage of a cascade chain. In normal mode, four data inputs from the LAB local interconnect and the carry-in are inputs to a four-input LUT. The Compiler automatically selects the carry-in or the DATA3 signal as one of the inputs to the LUT. The LUT output can be combined with the cascade-in signal to form a cascade chain through the cascade-out signal. Either the register or the LUT can be used to drive both the local interconnect and the FastTrack Interconnect at the same time.

The LUT and the register in the LE can be used independently; this feature is known as register packing. To support register packing, the LE has two outputs; one drives the local interconnect and the other drives the FastTrack Interconnect. The DATA4 signal can drive the register directly, allowing the LUT to compute a function that is independent of the registered signal; a three-input function can be computed in the LUT, and a fourth independent signal can be registered. Alternatively, a four-input function can be generated, and one of the inputs to this function can be used to drive the register. The register in a packed LE can still use the clock enable, clear, and preset signals in the LE. In a packed LE, the register can drive the FastTrack Interconnect while the LUT drives the local interconnect, or vice versa.

### Arithmetic Mode

The arithmetic mode offers 2 three-input LUTs that are ideal for implementing adders, accumulators, and comparators. One LUT computes a three-input function, and the other generates a carry output. As shown in Figure 9 on page 19, the first LUT uses the carry-in signal and two data inputs from the LAB local interconnect to generate a combinatorial or registered output. For example, in an adder, this output is the sum of three signals: a, b, and carry-in. The second LUT uses the same three signals to generate a carry-out signal, thereby creating a carry chain. The arithmetic mode also supports simultaneous use of the cascade chain.

| Device     | Channels per Row ( <i>n</i> ) | Row Channels per Pin (m) |

|------------|-------------------------------|--------------------------|

| EPF10K10   | 144                           | 18                       |

| EPF10K10A  |                               |                          |

| EPF10K20   | 144                           | 18                       |

| EPF10K30   | 216                           | 27                       |

| EPF10K30A  |                               |                          |

| EPF10K40   | 216                           | 27                       |

| EPF10K50   | 216                           | 27                       |

| EPF10K50V  |                               |                          |

| EPF10K70   | 312                           | 39                       |

| EPF10K100  | 312                           | 39                       |

| EPF10K100A |                               |                          |

| EPF10K130V | 312                           | 39                       |

| EPF10K250A | 456                           | 57                       |

Table 10 lists the FLEX 10K row-to-IOE interconnect resources.

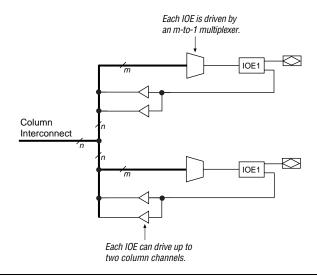

### Column-to-IOE Connections

When an IOE is used as an input, it can drive up to two separate column channels. When an IOE is used as an output, the signal is driven by a multiplexer that selects a signal from the column channels. Two IOEs connect to each side of the column channels. Each IOE can be driven by column channels via a multiplexer. The set of column channels that each IOE can access is different for each IOE. See Figure 15.

### Figure 15. FLEX 10K Column-to-IOE Connections

The values for m and n are provided in Table 11.

### Table 11 lists the FLEX 10K column-to-IOE interconnect resources.

| Table 11. FLEX 10       | Table 11. FLEX 10K Column-to-IOE Interconnect Resources |                                     |  |  |  |  |  |

|-------------------------|---------------------------------------------------------|-------------------------------------|--|--|--|--|--|

| Device                  | Channels per Column ( <i>n</i> )                        | Column Channel per Pin ( <i>m</i> ) |  |  |  |  |  |

| EPF10K10<br>EPF10K10A   | 24                                                      | 16                                  |  |  |  |  |  |

| EPF10K20                | 24                                                      | 16                                  |  |  |  |  |  |

| EPF10K30<br>EPF10K30A   | 24                                                      | 16                                  |  |  |  |  |  |

| EPF10K40                | 24                                                      | 16                                  |  |  |  |  |  |

| EPF10K50<br>EPF10K50V   | 24                                                      | 16                                  |  |  |  |  |  |

| EPF10K70                | 24                                                      | 16                                  |  |  |  |  |  |

| EPF10K100<br>EPF10K100A | 24                                                      | 16                                  |  |  |  |  |  |

| EPF10K130V              | 32                                                      | 24                                  |  |  |  |  |  |

| EPF10K250A              | 40                                                      | 32                                  |  |  |  |  |  |

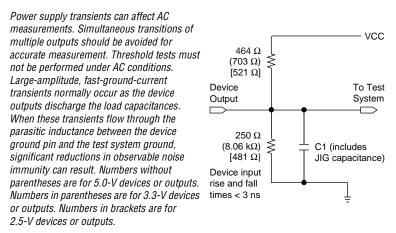

### **Generic Testing**

Each FLEX 10K device is functionally tested. Complete testing of each configurable SRAM bit and all logic functionality ensures 100% yield. AC test measurements for FLEX 10K devices are made under conditions equivalent to those shown in Figure 19. Multiple test patterns can be used to configure devices during all stages of the production flow.

### Figure 19. FLEX 10K AC Test Conditions

## Operating Conditions

Tables 17 through 21 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 5.0-V FLEX 10K devices.

| Table 1          | Table 17. FLEX 10K 5.0-V Device Absolute Maximum Ratings       Note (1) |                              |      |     |      |  |  |

|------------------|-------------------------------------------------------------------------|------------------------------|------|-----|------|--|--|

| Symbol           | Parameter                                                               | Conditions                   | Min  | Max | Unit |  |  |

| V <sub>CC</sub>  | Supply voltage                                                          | With respect to ground (2)   | -2.0 | 7.0 | V    |  |  |

| VI               | DC input voltage                                                        |                              | -2.0 | 7.0 | V    |  |  |

| I <sub>OUT</sub> | DC output current, per pin                                              |                              | -25  | 25  | mA   |  |  |

| T <sub>STG</sub> | Storage temperature                                                     | No bias                      | -65  | 150 | °C   |  |  |

| Т <sub>АМВ</sub> | Ambient temperature                                                     | Under bias                   | -65  | 135 | °C   |  |  |

| Τ <sub>J</sub>   | Junction temperature                                                    | Ceramic packages, under bias |      | 150 | °C   |  |  |

|                  |                                                                         | PQFP, TQFP, RQFP, and BGA    |      | 135 | °C   |  |  |

|                  |                                                                         | packages, under bias         |      |     |      |  |  |

### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $\hat{V}_{CC}$  rise time is 100 ms.  $V_{CC}$  must rise monotonically.

- (5) Typical values are for  $T_A = 25^\circ \text{ C}$  and  $V_{CC} = 5.0 \text{ V}$ .

- (6) These values are specified under the Recommended Operation Condition shown in Table 18 on page 45.

- (7) The I<sub>OH</sub> parameter refers to high-level TTL or CMOS output current.

- (8) The I<sub>OL</sub> parameter refers to low-level TTL or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (9) This value is specified for normal device operation. The value may vary during power-up.

- (10) Capacitance is sample-tested only.

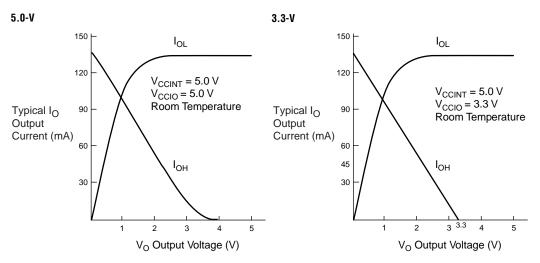

Figure 20 shows the typical output drive characteristics of FLEX 10K devices with 5.0-V and 3.3-V  $V_{CCIO}$ . The output driver is compliant with the 5.0-V *PCI Local Bus Specification, Revision 2.2* (for 5.0-V  $V_{CCIO}$ ).

Figure 20. Output Drive Characteristics of FLEX 10K Devices

| Table 2            | Table 27. FLEX 10KA 3.3-V Device Recommended Operating Conditions |                    |             |                   |      |  |  |

|--------------------|-------------------------------------------------------------------|--------------------|-------------|-------------------|------|--|--|

| Symbol             | Parameter                                                         | Conditions         | Min         | Max               | Unit |  |  |

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers               | (3), (4)           | 3.00 (3.00) | 3.60 (3.60)       | V    |  |  |

| V <sub>CCIO</sub>  | Supply voltage for output<br>buffers, 3.3-V operation             | (3), (4)           | 3.00 (3.00) | 3.60 (3.60)       | V    |  |  |

|                    | Supply voltage for output<br>buffers, 2.5-V operation             | (3), (4)           | 2.30 (2.30) | 2.70 (2.70)       | V    |  |  |

| VI                 | Input voltage                                                     | (5)                | -0.5        | 5.75              | V    |  |  |

| Vo                 | Output voltage                                                    |                    | 0           | V <sub>CCIO</sub> | V    |  |  |

| Τ <sub>Α</sub>     | Ambient temperature                                               | For commercial use | 0           | 70                | °C   |  |  |

|                    |                                                                   | For industrial use | -40         | 85                | °C   |  |  |

| ТJ                 | Operating temperature                                             | For commercial use | 0           | 85                | °C   |  |  |

|                    |                                                                   | For industrial use | -40         | 100               | °C   |  |  |

| t <sub>R</sub>     | Input rise time                                                   |                    |             | 40                | ns   |  |  |

| t <sub>F</sub>     | Input fall time                                                   |                    |             | 40                | ns   |  |  |

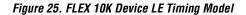

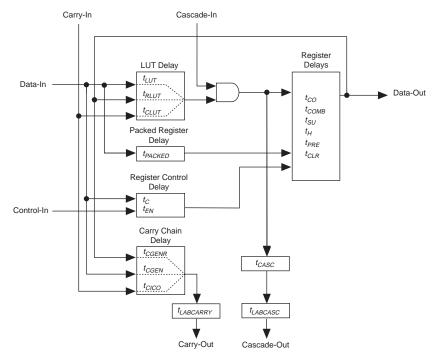

Figures 25 through 27 show the delays that correspond to various paths and functions within the LE, IOE, and EAB timing models.

Figure 28. Synchronous Bidirectional Pin External Timing Model

Tables 32 through 36 describe the FLEX 10K device internal timing parameters. These internal timing parameters are expressed as worst-case values. Using hand calculations, these parameters can be used to estimate design performance. However, before committing designs to silicon, actual worst-case performance should be modeled using timing simulation and analysis. Tables 37 through 38 describe FLEX 10K external timing parameters.

| Symbol              | Parameter                               | Conditions |

|---------------------|-----------------------------------------|------------|

| t <sub>LUT</sub>    | LUT delay for data-in                   |            |

| t <sub>CLUT</sub>   | LUT delay for carry-in                  |            |

| t <sub>RLUT</sub>   | LUT delay for LE register feedback      |            |

| t <sub>PACKED</sub> | Data-in to packed register delay        |            |

| t <sub>EN</sub>     | LE register enable delay                |            |

| tcico               | Carry-in to carry-out delay             |            |

| t <sub>CGEN</sub>   | Data-in to carry-out delay              |            |

| t <sub>CGENR</sub>  | LE register feedback to carry-out delay |            |

| t <sub>CASC</sub>   | Cascade-in to cascade-out delay         |            |

| t <sub>C</sub>      | LE register control signal delay        |            |

| t <sub>CO</sub>     | LE register clock-to-output delay       |            |

| t <sub>COMB</sub>   | Combinatorial delay                     |            |

### FLEX 10K Embedded Programmable Logic Device Family Data Sheet

#### Notes to tables:

(1) Microparameters are timing delays contributed by individual architectural elements. These parameters cannot be measured explicitly.

| (2) | Operating conditions: V <sub>CC</sub> | $_{\text{TO}}$ = 5.0 V ± 5% for commercial use in FLEX 10K devices.                     |

|-----|---------------------------------------|-----------------------------------------------------------------------------------------|

|     | V <sub>CC</sub>                       | $_{TO} = 5.0 \text{ V} \pm 10\%$ for industrial use in FLEX 10K devices.                |

|     | V <sub>CC</sub>                       | $_{TO}$ = 3.3 V ± 10% for commercial or industrial use in FLEX 10KA devices.            |

| (3) | Operating conditions: V <sub>CC</sub> | $_{TO}$ = 3.3 V ± 10% for commercial or industrial use in FLEX 10K devices.             |

|     | V <sub>CC</sub>                       | $_{\text{TO}}$ = 2.5 V ± 0.2 V for commercial or industrial use in FLEX 10KA devices.   |

| (4) | Operating conditions: V <sub>CC</sub> | $_{\rm TO} = 2.5 \text{ V}, 3.3 \text{ V}, \text{ or } 5.0 \text{ V}.$                  |

| (5) | Because the RAM in the EA             | B is self-timed, this parameter can be ignored when the WE signal is registered.        |

| (6) | EAB macroparameters are i             | nternal parameters that can simplify predicting the behavior of an EAB at its boundary; |

|     | these parameters are calcul           | ated by summing selected microparameters.                                               |

| (7) | These parameters are wors             | t-case values for typical applications. Post-compilation timing simulation and timing   |

|     | analysis are required to det          | ermine actual worst-case performance.                                                   |

| (8) | External reference timing p           | arameters are factory-tested, worst-case values specified by Altera. A representative   |

- subset of signal paths is tested to approximate typical device applications.

- (9) Contact Altera Applications for test circuit specifications and test conditions.

- (10) These timing parameters are sample-tested only.

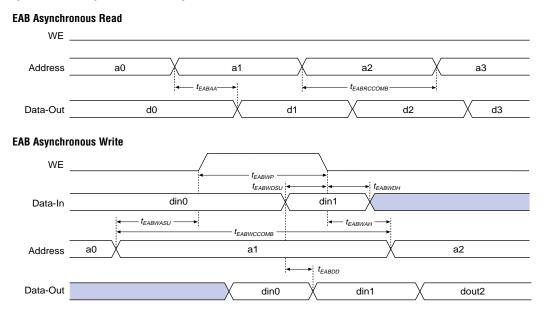

Figures 29 and 30 show the asynchronous and synchronous timing waveforms, respectively, for the EAB macroparameters in Table 34.

### Figure 29. EAB Asynchronous Timing Waveforms

Tables 39 through 47 show EPF10K10 and EPF10K20 device internal and external timing parameters.

| Table 39. EPF10K10 & EPF10K20 Device LE Timing Microparameters       Note (1) |         |         |         |      |    |  |

|-------------------------------------------------------------------------------|---------|---------|---------|------|----|--|

| Symbol                                                                        | -3 Spee | d Grade | -4 Spee | Unit |    |  |

|                                                                               | Min     | Мах     | Min     | Max  |    |  |

| t <sub>LUT</sub>                                                              |         | 1.4     |         | 1.7  | ns |  |

| t <sub>CLUT</sub>                                                             |         | 0.6     |         | 0.7  | ns |  |

| t <sub>RLUT</sub>                                                             |         | 1.5     |         | 1.9  | ns |  |

| t <sub>PACKED</sub>                                                           |         | 0.6     |         | 0.9  | ns |  |

| t <sub>EN</sub>                                                               |         | 1.0     |         | 1.2  | ns |  |

| t <sub>CICO</sub>                                                             |         | 0.2     |         | 0.3  | ns |  |

| t <sub>CGEN</sub>                                                             |         | 0.9     |         | 1.2  | ns |  |

| t <sub>CGENR</sub>                                                            |         | 0.9     |         | 1.2  | ns |  |

| t <sub>CASC</sub>                                                             |         | 0.8     |         | 0.9  | ns |  |

| t <sub>C</sub>                                                                |         | 1.3     |         | 1.5  | ns |  |

| t <sub>CO</sub>                                                               |         | 0.9     |         | 1.1  | ns |  |

| t <sub>COMB</sub>                                                             |         | 0.5     |         | 0.6  | ns |  |

| t <sub>SU</sub>                                                               | 1.3     |         | 2.5     |      | ns |  |

| t <sub>H</sub>                                                                | 1.4     |         | 1.6     |      | ns |  |

| t <sub>PRE</sub>                                                              |         | 1.0     |         | 1.2  | ns |  |

| t <sub>CLR</sub>                                                              |         | 1.0     |         | 1.2  | ns |  |

| t <sub>CH</sub>                                                               | 4.0     |         | 4.0     |      | ns |  |

| t <sub>CL</sub>                                                               | 4.0     |         | 4.0     |      | ns |  |

| Symbol                 | -3 Speed Grade |      | -4 Spee | ed Grade | Unit |

|------------------------|----------------|------|---------|----------|------|

|                        | Min            | Max  | Min     | Max      |      |

| t <sub>EABAA</sub>     |                | 13.7 |         | 17.0     | ns   |

| t <sub>EABRCCOMB</sub> | 13.7           |      | 17.0    |          | ns   |

| t <sub>EABRCREG</sub>  | 9.7            |      | 11.9    |          | ns   |

| t <sub>EABWP</sub>     | 5.8            |      | 7.2     |          | ns   |

| t <sub>EABWCCOMB</sub> | 7.3            |      | 9.0     |          | ns   |

| t <sub>EABWCREG</sub>  | 13.0           |      | 16.0    |          | ns   |

| t <sub>EABDD</sub>     |                | 10.0 |         | 12.5     | ns   |

| t <sub>EABDATACO</sub> |                | 2.0  |         | 3.4      | ns   |

| t <sub>EABDATASU</sub> | 5.3            |      | 5.6     |          | ns   |

| t <sub>EABDATAH</sub>  | 0.0            |      | 0.0     |          | ns   |

| t <sub>EABWESU</sub>   | 5.5            |      | 5.8     |          | ns   |

| t <sub>EABWEH</sub>    | 0.0            |      | 0.0     |          | ns   |

| t <sub>EABWDSU</sub>   | 5.5            |      | 5.8     |          | ns   |

| t <sub>EABWDH</sub>    | 0.0            |      | 0.0     |          | ns   |

| t <sub>EABWASU</sub>   | 2.1            |      | 2.7     |          | ns   |

| t <sub>EABWAH</sub>    | 0.0            |      | 0.0     |          | ns   |

| t <sub>EABWO</sub>     |                | 9.5  |         | 11.8     | ns   |

### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

Tables 64 through  $70\,show\,EPF10K100\,device$  internal and external timing parameters.

| Table 64. EPF10K100 Device LE Timing Microparameters       Note (1) |         |           |        |          |         |          |      |

|---------------------------------------------------------------------|---------|-----------|--------|----------|---------|----------|------|

| Symbol                                                              | -3DX Sp | eed Grade | -3 Spe | ed Grade | -4 Spee | ed Grade | Unit |

|                                                                     | Min     | Max       | Min    | Max      | Min     | Max      |      |

| t <sub>LUT</sub>                                                    |         | 1.5       |        | 1.5      |         | 2.0      | ns   |

| t <sub>CLUT</sub>                                                   |         | 0.4       |        | 0.4      |         | 0.5      | ns   |

| t <sub>RLUT</sub>                                                   |         | 1.6       |        | 1.6      |         | 2.0      | ns   |

| t <sub>PACKED</sub>                                                 |         | 0.9       |        | 0.9      |         | 1.3      | ns   |

| t <sub>EN</sub>                                                     |         | 0.9       |        | 0.9      |         | 1.2      | ns   |

| t <sub>CICO</sub>                                                   |         | 0.2       |        | 0.2      |         | 0.3      | ns   |

| t <sub>CGEN</sub>                                                   |         | 1.1       |        | 1.1      |         | 1.4      | ns   |

| t <sub>CGENR</sub>                                                  |         | 1.2       |        | 1.2      |         | 1.5      | ns   |

| t <sub>CASC</sub>                                                   |         | 1.1       |        | 1.1      |         | 1.3      | ns   |

| t <sub>C</sub>                                                      |         | 0.8       |        | 0.8      |         | 1.0      | ns   |

| t <sub>CO</sub>                                                     |         | 1.0       |        | 1.0      |         | 1.4      | ns   |

| t <sub>COMB</sub>                                                   |         | 0.5       |        | 0.5      |         | 0.7      | ns   |

| t <sub>SU</sub>                                                     | 2.1     |           | 2.1    |          | 2.6     |          | ns   |

| t <sub>H</sub>                                                      | 2.3     |           | 2.3    |          | 3.1     |          | ns   |

| t <sub>PRE</sub>                                                    |         | 1.0       |        | 1.0      |         | 1.4      | ns   |

| t <sub>CLR</sub>                                                    |         | 1.0       |        | 1.0      |         | 1.4      | ns   |

| t <sub>CH</sub>                                                     | 4.0     |           | 4.0    |          | 4.0     |          | ns   |

| t <sub>CL</sub>                                                     | 4.0     |           | 4.0    |          | 4.0     |          | ns   |

### FLEX 10K Embedded Programmable Logic Device Family Data Sheet

| Symbol                                                          | -3DX Speed Grade |     | -3 Speed Grade |     | -4 Speed Grade |      | Unit |

|-----------------------------------------------------------------|------------------|-----|----------------|-----|----------------|------|------|

|                                                                 | Min              | Max | Min            | Max | Min            | Max  |      |

| t <sub>IOD</sub>                                                |                  | 0.0 |                | 0.0 |                | 0.0  | ns   |

| t <sub>IOC</sub>                                                |                  | 0.5 |                | 0.5 |                | 0.7  | ns   |

| t <sub>IOCO</sub>                                               |                  | 0.4 |                | 0.4 |                | 0.9  | ns   |

| t <sub>IOCOMB</sub>                                             |                  | 0.0 |                | 0.0 |                | 0.0  | ns   |

| t <sub>IOSU</sub>                                               | 5.5              |     | 5.5            |     | 6.7            |      | ns   |

| t <sub>IOH</sub>                                                | 0.5              |     | 0.5            |     | 0.7            |      | ns   |

| t <sub>IOCLR</sub>                                              |                  | 0.7 |                | 0.7 |                | 1.6  | ns   |

| t <sub>OD1</sub>                                                |                  | 4.0 |                | 4.0 |                | 5.0  | ns   |

| t <sub>OD2</sub>                                                |                  | 6.3 |                | 6.3 |                | 7.3  | ns   |

| t <sub>OD3</sub>                                                |                  | 7.7 |                | 7.7 |                | 8.7  | ns   |

| t <sub>XZ</sub>                                                 |                  | 6.2 |                | 6.2 |                | 6.8  | ns   |

| t <sub>ZX1</sub>                                                |                  | 6.2 |                | 6.2 |                | 6.8  | ns   |

| t <sub>ZX2</sub>                                                |                  | 8.5 |                | 8.5 |                | 9.1  | ns   |

| t <sub>ZX3</sub>                                                |                  | 9.9 |                | 9.9 |                | 10.5 | ns   |

| t <sub>INREG</sub> without ClockLock or<br>ClockBoost circuitry |                  | 9.0 |                | 9.0 |                | 10.5 | ns   |

| t <sub>INREG</sub> with ClockLock or<br>ClockBoost circuitry    |                  | 3.0 |                | -   |                | -    | ns   |

| t <sub>IOFD</sub>                                               |                  | 8.1 |                | 8.1 |                | 10.3 | ns   |

| t <sub>INCOMB</sub>                                             |                  | 8.1 |                | 8.1 |                | 10.3 | ns   |

| Symbol                  | -2 Spee | -2 Speed Grade |     | -3 Speed Grade |     | -4 Speed Grade |    |

|-------------------------|---------|----------------|-----|----------------|-----|----------------|----|

|                         | Min     | Max            | Min | Мах            | Min | Max            |    |

| t <sub>DIN2IOE</sub>    |         | 8.0            |     | 9.0            |     | 9.5            | ns |

| t <sub>DIN2LE</sub>     |         | 2.4            |     | 3.0            |     | 3.1            | ns |

| t <sub>DIN2DATA</sub>   |         | 5.0            |     | 6.3            |     | 7.4            | ns |

| t <sub>DCLK2IOE</sub>   |         | 3.6            |     | 4.6            |     | 5.1            | ns |

| t <sub>DCLK2LE</sub>    |         | 2.4            |     | 3.0            |     | 3.1            | ns |

| t <sub>SAMELAB</sub>    |         | 0.4            |     | 0.6            |     | 0.8            | ns |

| t <sub>SAMEROW</sub>    |         | 4.5            |     | 5.3            |     | 6.5            | ns |

| t <sub>SAMECOLUMN</sub> |         | 9.0            |     | 9.5            |     | 9.7            | ns |

| t <sub>DIFFROW</sub>    |         | 13.5           |     | 14.8           |     | 16.2           | ns |

| t <sub>TWOROWS</sub>    |         | 18.0           |     | 20.1           |     | 22.7           | ns |

| t <sub>LEPERIPH</sub>   |         | 8.1            |     | 8.6            |     | 9.5            | ns |

| t <sub>LABCARRY</sub>   |         | 0.6            |     | 0.8            |     | 1.0            | ns |

| t <sub>LABCASC</sub>    |         | 0.8            |     | 1.0            |     | 1.2            | ns |

#### Table 83. EPF10K130V Device External Timing Parameters Note (1)

| Symbol                     | -2 Spee | -2 Speed Grade |     | -3 Speed Grade |      | d Grade | Unit |  |

|----------------------------|---------|----------------|-----|----------------|------|---------|------|--|

|                            | Min     | Max            | Min | Max            | Min  | Max     |      |  |

| t <sub>DRR</sub>           |         | 15.0           |     | 19.1           |      | 24.2    | ns   |  |

| t <sub>INSU</sub> (2), (3) | 6.9     |                | 8.6 |                | 11.0 |         | ns   |  |

| t <sub>INH</sub> (3)       | 0.0     |                | 0.0 |                | 0.0  |         | ns   |  |

| t <sub>оитсо</sub> (3)     | 2.0     | 7.8            | 2.0 | 9.9            | 2.0  | 11.3    | ns   |  |

### Table 84. EPF10K130V Device External Bidirectional Timing Parameters Note (1)

| Symbol                 | -2 Spee | -2 Speed Grade |     | ed Grade | -4 Spee | Unit |    |

|------------------------|---------|----------------|-----|----------|---------|------|----|

|                        | Min     | Max            | Min | Max      | Min     | Max  |    |

| t <sub>INSUBIDIR</sub> | 6.7     |                | 8.5 |          | 10.8    |      | ns |

| t <sub>INHBIDIR</sub>  | 0.0     |                | 0.0 |          | 0.0     |      | ns |

| toutcobidir            | 2.0     | 6.9            | 2.0 | 8.8      | 2.0     | 10.2 | ns |

| t <sub>XZBIDIR</sub>   |         | 12.9           |     | 16.4     |         | 19.3 | ns |

| t <sub>ZXBIDIR</sub>   |         | 12.9           |     | 16.4     |         | 19.3 | ns |

| Symbol                 | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | d Grade | Unit |

|------------------------|---------|---------|---------|---------|---------|---------|------|

|                        | Min     | Max     | Min     | Max     | Min     | Max     |      |

| t <sub>EABDATA1</sub>  |         | 3.3     |         | 3.9     |         | 5.2     | ns   |

| t <sub>EABDATA2</sub>  |         | 1.0     |         | 1.3     |         | 1.7     | ns   |

| t <sub>EABWE1</sub>    |         | 2.6     |         | 3.1     |         | 4.1     | ns   |

| t <sub>EABWE2</sub>    |         | 2.7     |         | 3.2     |         | 4.3     | ns   |

| t <sub>EABCLK</sub>    |         | 0.0     |         | 0.0     |         | 0.0     | ns   |

| t <sub>EABCO</sub>     |         | 1.2     |         | 1.4     |         | 1.8     | ns   |

| t <sub>EABBYPASS</sub> |         | 0.1     |         | 0.2     |         | 0.2     | ns   |

| t <sub>EABSU</sub>     | 1.4     |         | 1.7     |         | 2.2     |         | ns   |

| t <sub>EABH</sub>      | 0.1     |         | 0.1     |         | 0.1     |         | ns   |

| t <sub>AA</sub>        |         | 4.5     |         | 5.4     |         | 7.3     | ns   |

| t <sub>WP</sub>        | 2.0     |         | 2.4     |         | 3.2     |         | ns   |

| t <sub>WDSU</sub>      | 0.7     |         | 0.8     |         | 1.1     |         | ns   |

| t <sub>WDH</sub>       | 0.5     |         | 0.6     |         | 0.7     |         | ns   |

| t <sub>WASU</sub>      | 0.6     |         | 0.7     |         | 0.9     |         | ns   |

| t <sub>WAH</sub>       | 0.9     |         | 1.1     |         | 1.5     |         | ns   |

| t <sub>WO</sub>        |         | 3.3     |         | 3.9     |         | 5.2     | ns   |

| t <sub>DD</sub>        |         | 3.3     |         | 3.9     |         | 5.2     | ns   |

| t<br>EABOUT            |         | 0.1     |         | 0.1     |         | 0.2     | ns   |

| t <sub>EABCH</sub>     | 3.0     |         | 3.5     |         | 4.0     |         | ns   |

| t <sub>EABCL</sub>     | 3.03    |         | 3.5     |         | 4.0     |         | ns   |

| Symbol                 | -1 Spee | d Grade | -2 Spee | d Grade | -3 Spee | d Grade | Unit |

|------------------------|---------|---------|---------|---------|---------|---------|------|

|                        | Min     | Max     | Min     | Max     | Min     | Max     |      |

| t <sub>EABAA</sub>     |         | 9.7     |         | 11.6    |         | 16.2    | ns   |

| t <sub>EABRCCOMB</sub> | 9.7     |         | 11.6    |         | 16.2    |         | ns   |

| t <sub>EABRCREG</sub>  | 5.9     |         | 7.1     |         | 9.7     |         | ns   |

| t <sub>EABWP</sub>     | 3.8     |         | 4.5     |         | 5.9     |         | ns   |

| t <sub>EABWCCOMB</sub> | 4.0     |         | 4.7     |         | 6.3     |         | ns   |

| t <sub>EABWCREG</sub>  | 9.8     |         | 11.6    |         | 16.6    |         | ns   |

| t <sub>EABDD</sub>     |         | 9.2     |         | 11.0    |         | 16.1    | ns   |

| t <sub>EABDATACO</sub> |         | 1.7     |         | 2.1     |         | 3.4     | ns   |

| t <sub>EABDATASU</sub> | 2.3     |         | 2.7     |         | 3.5     |         | ns   |

| t <sub>EABDATAH</sub>  | 0.0     |         | 0.0     |         | 0.0     |         | ns   |

| t <sub>EABWESU</sub>   | 3.3     |         | 3.9     |         | 4.9     |         | ns   |

| t <sub>EABWEH</sub>    | 0.0     |         | 0.0     |         | 0.0     |         | ns   |

| t <sub>EABWDSU</sub>   | 3.2     |         | 3.8     |         | 5.0     |         | ns   |

| t <sub>EABWDH</sub>    | 0.0     |         | 0.0     |         | 0.0     |         | ns   |

| t <sub>EABWASU</sub>   | 3.7     |         | 4.4     |         | 5.1     |         | ns   |

| t <sub>EABWAH</sub>    | 0.0     |         | 0.0     |         | 0.0     |         | ns   |

| t <sub>EABWO</sub>     |         | 6.1     |         | 7.3     |         | 11.3    | ns   |

| Symbol                   | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | ed Grade | Unit |  |

|--------------------------|----------------|-----|---------|---------|---------|----------|------|--|

|                          | Min            | Max | Min     | Max     | Min     | Max      |      |  |

| t <sub>DIN2IOE</sub>     |                | 4.8 |         | 5.4     |         | 6.0      | ns   |  |

| t <sub>DIN2LE</sub>      |                | 2.0 |         | 2.4     |         | 2.7      | ns   |  |

| t <sub>DIN2DATA</sub>    |                | 2.4 |         | 2.7     |         | 2.9      | ns   |  |

| t <sub>DCLK2IOE</sub>    |                | 2.6 |         | 3.0     |         | 3.5      | ns   |  |

| t <sub>DCLK2LE</sub>     |                | 2.0 |         | 2.4     |         | 2.7      | ns   |  |

| t <sub>SAMELAB</sub>     |                | 0.1 |         | 0.1     |         | 0.1      | ns   |  |

| t <sub>SAMEROW</sub>     |                | 1.5 |         | 1.7     |         | 1.9      | ns   |  |

| t <sub>SAME</sub> COLUMN |                | 5.5 |         | 6.5     |         | 7.4      | ns   |  |

| t <sub>DIFFROW</sub>     |                | 7.0 |         | 8.2     |         | 9.3      | ns   |  |

| t <sub>TWOROWS</sub>     |                | 8.5 |         | 9.9     |         | 11.2     | ns   |  |

| t <sub>LEPERIPH</sub>    |                | 3.9 |         | 4.2     |         | 4.5      | ns   |  |

| t <sub>LABCARRY</sub>    |                | 0.2 |         | 0.2     |         | 0.3      | ns   |  |

| t <sub>LABCASC</sub>     |                | 0.4 |         | 0.5     |         | 0.6      | ns   |  |

#### Table 104. EPF10K100A Device External Timing Parameters Note (1)

| Symbol                            | -1 Spee | -1 Speed Grade |     | ed Grade | -3 Spee | d Grade | Unit |

|-----------------------------------|---------|----------------|-----|----------|---------|---------|------|

|                                   | Min     | Max            | Min | Max      | Min     | Max     |      |

| t <sub>DRR</sub>                  |         | 12.5           |     | 14.5     |         | 17.0    | ns   |

| t <sub>INSU</sub> (2), (3)        | 3.7     |                | 4.5 |          | 5.1     |         | ns   |

| t <sub>INH</sub> (3)              | 0.0     |                | 0.0 |          | 0.0     |         | ns   |

| <sup>t</sup> оитсо <sup>(3)</sup> | 2.0     | 5.3            | 2.0 | 6.1      | 2.0     | 7.2     | ns   |

7.4

| Table 105. EPF10K100A Device External Bidirectional Timing Parameters         Note (1) |         |          |                              |     |     |      |      |

|----------------------------------------------------------------------------------------|---------|----------|------------------------------|-----|-----|------|------|

| Symbol                                                                                 | -1 Spec | ed Grade | rade -2 Speed Grade -3 Speed |     |     |      | Unit |

|                                                                                        | Min     | Max      | Min                          | Max | Min | Max  |      |

| t <sub>INSUBIDIR</sub>                                                                 | 4.9     |          | 5.8                          |     | 6.8 |      | ns   |

| t <sub>INHBIDIR</sub>                                                                  | 0.0     |          | 0.0                          |     | 0.0 |      | ns   |

| toutcobidir                                                                            | 2.0     | 5.3      | 2.0                          | 6.1 | 2.0 | 7.2  | ns   |

| t <sub>XZBIDIR</sub>                                                                   |         | 7.4      |                              | 8.6 |     | 10.1 | ns   |

8.6

t<sub>ZXBIDIR</sub>

ns

10.1

| Symbol                  | -1 Speed Grade |      | -2 Spee | d Grade | -3 Spee | d Grade | Unit |

|-------------------------|----------------|------|---------|---------|---------|---------|------|

|                         | Min            | Max  | Min     | Max     | Min     | Max     |      |

| t <sub>DIN2IOE</sub>    |                | 7.8  |         | 8.5     |         | 9.4     | ns   |

| t <sub>DIN2LE</sub>     |                | 2.7  |         | 3.1     |         | 3.5     | ns   |

| t <sub>DIN2DATA</sub>   |                | 1.6  |         | 1.6     |         | 1.7     | ns   |

| t <sub>DCLK2IOE</sub>   |                | 3.6  |         | 4.0     |         | 4.6     | ns   |

| t <sub>DCLK2LE</sub>    |                | 2.7  |         | 3.1     |         | 3.5     | ns   |

| t <sub>SAMELAB</sub>    |                | 0.2  |         | 0.3     |         | 0.3     | ns   |

| t <sub>SAMEROW</sub>    |                | 6.7  |         | 7.3     |         | 8.2     | ns   |

| t <sub>SAMECOLUMN</sub> |                | 2.5  |         | 2.7     |         | 3.0     | ns   |

| t <sub>DIFFROW</sub>    |                | 9.2  |         | 10.0    |         | 11.2    | ns   |

| t <sub>TWOROWS</sub>    |                | 15.9 |         | 17.3    |         | 19.4    | ns   |

| t <sub>LEPERIPH</sub>   |                | 7.5  |         | 8.1     |         | 8.9     | ns   |

| t <sub>LABCARRY</sub>   |                | 0.3  |         | 0.4     |         | 0.5     | ns   |

| t <sub>LABCASC</sub>    |                | 0.4  |         | 0.4     |         | 0.5     | ns   |

| Symbol                     | -1 Spee | d Grade | -2 Speed Grade -3 Speed Grade |      |     |      | Unit |

|----------------------------|---------|---------|-------------------------------|------|-----|------|------|

|                            | Min     | Max     | Min                           | Max  | Min | Max  |      |

| t <sub>DRR</sub>           |         | 15.0    |                               | 17.0 |     | 20.0 | ns   |

| t <sub>INSU</sub> (2), (3) | 6.9     |         | 8.0                           |      | 9.4 |      | ns   |

| t <sub>INH</sub> (3)       | 0.0     |         | 0.0                           |      | 0.0 |      | ns   |

| t <sub>оитсо</sub> (3)     | 2.0     | 8.0     | 2.0                           | 8.9  | 2.0 | 10.4 | ns   |

| Table 112. EPF1UK25UA Device External Bidirectional Timing Parameters Note ( |  | Table 112. EPF10K250A Device External Bidirectional Timing Parameters | Note (1) |

|------------------------------------------------------------------------------|--|-----------------------------------------------------------------------|----------|

|------------------------------------------------------------------------------|--|-----------------------------------------------------------------------|----------|

| Symbol                 | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |      | Unit |  |

|------------------------|----------------|------|----------------|------|----------------|------|------|--|

|                        | Min            | Max  | Min            | Max  | Min            | Max  |      |  |

| t <sub>INSUBIDIR</sub> | 9.3            |      | 10.6           |      | 12.7           |      | ns   |  |

| t <sub>INHBIDIR</sub>  | 0.0            |      | 0.0            |      | 0.0            |      | ns   |  |

| toutcobidir            | 2.0            | 8.0  | 2.0            | 8.9  | 2.0            | 10.4 | ns   |  |

| t <sub>XZBIDIR</sub>   |                | 10.8 |                | 12.2 |                | 14.2 | ns   |  |

| t <sub>ZXBIDIR</sub>   |                | 10.8 |                | 12.2 |                | 14.2 | ns   |  |

| Table 113. ClockLock & ClockBoost Parameters       (Part 2 of 2) |                                                                                                              |     |     |      |      |  |  |  |  |  |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|------|------|--|--|--|--|--|

| Symbol                                                           | Parameter                                                                                                    | Min | Тур | Max  | Unit |  |  |  |  |  |

| f <sub>CLKDEV1</sub>                                             | Input deviation from user specification in MAX+PLUS II (ClockBoost clock multiplication factor equals 1) (1) |     |     | ±1   | MHz  |  |  |  |  |  |

| f <sub>CLKDEV2</sub>                                             | Input deviation from user specification in MAX+PLUS II (ClockBoost clock multiplication factor equals 2) (1) |     |     | ±0.5 | MHz  |  |  |  |  |  |

| t <sub>INCLKSTB</sub>                                            | Input clock stability (measured between adjacent clocks)                                                     |     |     | 100  | ps   |  |  |  |  |  |

| t <sub>LOCK</sub>                                                | Time required for ClockLock or ClockBoost to acquire lock (2)                                                |     |     | 10   | μs   |  |  |  |  |  |

| t <sub>JITTER</sub>                                              | Jitter on ClockLock or ClockBoost-generated clock (3)                                                        |     |     | 1    | ns   |  |  |  |  |  |

| t <sub>OUTDUTY</sub>                                             | Duty cycle for ClockLock or ClockBoost-generated clock                                                       | 40  | 50  | 60   | %    |  |  |  |  |  |

Notes:

(1) To implement the ClockLock and ClockBoost circuitry with the MAX+PLUS II software, designers must specify the input frequency. The MAX+PLUS II software tunes the PLL in the ClockLock and ClockBoost circuitry to this frequency. The *f<sub>CLKDEV</sub>* parameter specifies how much the incoming clock can differ from the specified frequency during device operation. Simulation does not reflect this parameter.

(2) During device configuration, the ClockLock and ClockBoost circuitry is configured before the rest of the device. If the incoming clock is supplied during configuration, the ClockLock and ClockBoost circuitry locks during configuration, because the t<sub>LOCK</sub> value is less than the time required for configuration.

(3) The  $t_{IITTER}$  specification is measured under long-term observation.

# Power Consumption

The supply power (P) for FLEX 10K devices can be calculated with the following equation:

$P = P_{INT} + P_{IO} = (I_{CCSTANDBY} + I_{CCACTIVE}) \times V_{CC} + P_{IO}$

Typical I<sub>CCSTANDBY</sub> values are shown as I<sub>CC0</sub> in the FLEX 10K device DC operating conditions tables on pages 46, 49, and 52 of this data sheet. The I<sub>CCACTIVE</sub> value depends on the switching frequency and the application logic. This value is calculated based on the amount of current that each LE typically consumes. The P<sub>IO</sub> value, which depends on the device output load characteristics and switching frequency, can be calculated using the guidelines given in *Application Note* 74 (Evaluating Power for Altera Devices).

Compared to the rest of the device, the embedded array consumes a negligible amount of power. Therefore, the embedded array can be ignored when calculating supply current.

The I<sub>CCACTIVE</sub> value is calculated with the following equation:

$$I_{CCACTIVE} = K \times f_{MAX} \times N \times tog_{LC} \times \frac{\mu A}{MHz \times LE}$$

The parameters in this equation are shown below: