Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 360                                                          |

| Number of Logic Elements/Cells | 2880                                                         |

| Total RAM Bits                 | 20480                                                        |

| Number of I/O                  | 189                                                          |

| Number of Gates                | 116000                                                       |

| Voltage - Supply               | 3V ~ 3.6V                                                    |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | -40°C ~ 85°C (TA)                                            |

| Package / Case                 | 240-BFQFP                                                    |

| Supplier Device Package        | 240-PQFP (32x32)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k50vqi240-2n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Logic Array Block**

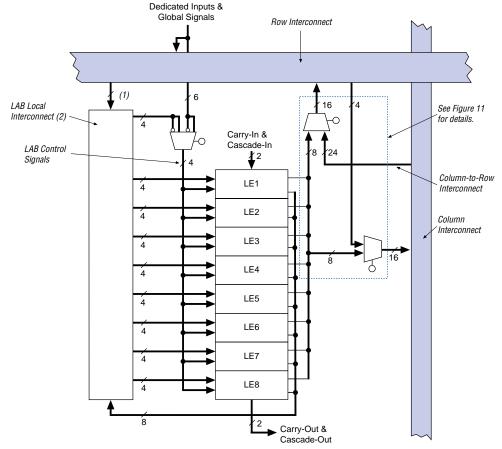

Each LAB consists of eight LEs, their associated carry and cascade chains, LAB control signals, and the LAB local interconnect. The LAB provides the coarse-grained structure to the FLEX 10K architecture, facilitating efficient routing with optimum device utilization and high performance. See Figure 5.

Figure 5. FLEX 10K LAB

#### Notes:

- (1) EPF10K10, EPF10K10A, EPF10K20, EPF10K30, EPF10K30A, EPF10K40, EPF10K50, and EPF10K50V devices have 22 inputs to the LAB local interconnect channel from the row; EPF10K70, EPF10K100, EPF10K100A, EPF10K130V, and EPF10K250A devices have 26.

- (2) EPF10K10, EPF10K10A, EPF10K20, EPF10K30, EPF10K30A, EPF10K40, EPF10K50, and EPF10K50V devices have 30 LAB local interconnect channels; EPF10K70, EPF10K100, EPF10K100A, EPF10K130V, and EPF10K250A devices have 34 LABs.

#### Up/Down Counter Mode

The up/down counter mode offers counter enable, clock enable, synchronous up/down control, and data loading options. These control signals are generated by the data inputs from the LAB local interconnect, the carry-in signal, and output feedback from the programmable register. The Up/down counter mode uses 2 three-input LUTs: one generates the counter data, and the other generates the fast carry bit. A 2-to-1 multiplexer provides synchronous loading. Data can also be loaded asynchronously with the clear and preset register control signals, without using the LUT resources.

#### Clearable Counter Mode

The clearable counter mode is similar to the up/down counter mode, but supports a synchronous clear instead of the up/down control. The clear function is substituted for the cascade-in signal in the up/down counter mode. Clearable counter mode uses 2 three-input LUTs: one generates the counter data, and the other generates the fast carry bit. Synchronous loading is provided by a 2-to-1 multiplexer. The output of this multiplexer is ANDed with a synchronous clear signal.

#### Internal Tri-State Emulation

Internal tri-state emulation provides internal tri-stating without the limitations of a physical tri-state bus. In a physical tri-state bus, the tri-state buffers' output enable (OE) signals select which signal drives the bus. However, if multiple OE signals are active, contending signals can be driven onto the bus. Conversely, if no OE signals are active, the bus will float. Internal tri-state emulation resolves contending tri-state buffers to a low value and floating buses to a high value, thereby eliminating these problems. The Altera software automatically implements tri-state bus functionality with a multiplexer.

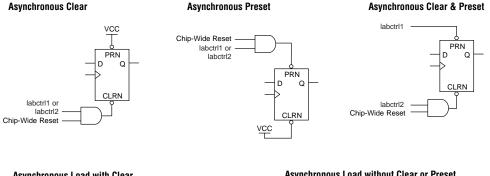

#### Clear & Preset Logic Control

Logic for the programmable register's clear and preset functions is controlled by the DATA3, LABCTRL1, and LABCTRL2 inputs to the LE. The clear and preset control structure of the LE asynchronously loads signals into a register. Either LABCTRL1 or LABCTRL2 can control the asynchronous clear. Alternatively, the register can be set up so that LABCTRL1 implements an asynchronous load. The data to be loaded is driven to DATA3; when LABCTRL1 is asserted, DATA3 is loaded into the register.

Figure 10. LE Clear & Preset Modes

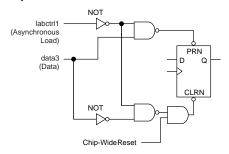

## **Asynchronous Load with Clear**

#### labctrl1 (Asynchronous Load) PRN data3 (Data) NOT CLRN labctrl2 (Clear) Chip-Wide Reset

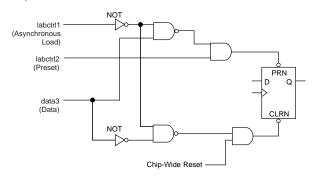

#### **Asynchronous Load without Clear or Preset**

#### **Asynchronous Load with Preset**

#### Asynchronous Clear

The flipflop can be cleared by either LABCTRL1 or LABCTRL2. In this mode, the preset signal is tied to V<sub>CC</sub> to deactivate it.

Tables 22 through 25 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for EPF10K50V and EPF10K130V devices.

| Table 2          | Table 22. EPF10K50V & EPF10K130V Device Absolute Maximum Ratings       Note (1) |                                   |      |      |      |

|------------------|---------------------------------------------------------------------------------|-----------------------------------|------|------|------|

| Symbol           | Parameter                                                                       | Conditions                        | Min  | Max  | Unit |

| V <sub>CC</sub>  | Supply voltage                                                                  | With respect to ground (2)        | -0.5 | 4.6  | V    |

| VI               | DC input voltage                                                                |                                   | -2.0 | 5.75 | V    |

| I <sub>OUT</sub> | DC output current, per pin                                                      |                                   | -25  | 25   | mA   |

| T <sub>STG</sub> | Storage temperature                                                             | No bias                           | -65  | 150  | ° C  |

| T <sub>AMB</sub> | Ambient temperature                                                             | Under bias                        | -65  | 135  | ° C  |

| TJ               | Junction temperature                                                            | Ceramic packages, under bias      |      | 150  | ° C  |

|                  |                                                                                 | RQFP and BGA packages, under bias |      | 135  | ° C  |

| Symbol             | Parameter                                           | Conditions         | Min         | Max               | Unit |

|--------------------|-----------------------------------------------------|--------------------|-------------|-------------------|------|

| V <sub>CCINT</sub> | Supply voltage for internal logic and input buffers | (3), (4)           | 3.00 (3.00) | 3.60 (3.60)       | V    |

| V <sub>CCIO</sub>  | Supply voltage for output buffers                   | (3), (4)           | 3.00 (3.00) | 3.60 (3.60)       | V    |

| V <sub>I</sub>     | Input voltage                                       | (5)                | -0.5        | 5.75              | V    |

| Vo                 | Output voltage                                      |                    | 0           | V <sub>CCIO</sub> | V    |

| T <sub>A</sub>     | Ambient temperature                                 | For commercial use | 0           | 70                | °C   |

|                    |                                                     | For industrial use | -40         | 85                | ° C  |

| TJ                 | Operating temperature                               | For commercial use | 0           | 85                | ° C  |

|                    |                                                     | For industrial use | -40         | 100               | ° C  |

| t <sub>R</sub>     | Input rise time                                     |                    |             | 40                | ns   |

| t <sub>F</sub>     | Input fall time                                     |                    |             | 40                | ns   |

| Symbol           | Parameter                                | Conditions                                     | Min                     | Typ | Max  | Unit |

|------------------|------------------------------------------|------------------------------------------------|-------------------------|-----|------|------|

| V <sub>IH</sub>  | High-level input voltage                 |                                                | 2.0                     |     | 5.75 | V    |

| V <sub>IL</sub>  | Low-level input voltage                  |                                                | -0.5                    |     | 0.8  | V    |

| V <sub>OH</sub>  | 3.3-V high-level TTL output voltage      | $I_{OH} = -8 \text{ mA DC } (8)$               | 2.4                     |     |      | V    |

|                  | 3.3-V high-level CMOS output voltage     | $I_{OH} = -0.1 \text{ mA DC } (8)$             | V <sub>CCIO</sub> - 0.2 |     |      | V    |

| V <sub>OL</sub>  | 3.3-V low-level TTL output voltage       | I <sub>OL</sub> = 8 mA DC (9)                  |                         |     | 0.45 | V    |

|                  | 3.3-V low-level CMOS output voltage      | I <sub>OL</sub> = 0.1 mA DC (9)                |                         |     | 0.2  | V    |

| I <sub>I</sub>   | Input pin leakage current                | $V_1 = 5.3 \text{ V to } -0.3 \text{ V } (10)$ | -10                     |     | 10   | μА   |

| I <sub>OZ</sub>  | Tri-stated I/O pin leakage current       | $V_O = 5.3 \text{ V to } -0.3 \text{ V } (10)$ | -10                     |     | 10   | μΑ   |

| I <sub>CC0</sub> | V <sub>CC</sub> supply current (standby) | V <sub>I</sub> = ground, no load               |                         | 0.3 | 10   | mA   |

|                  |                                          | $V_I$ = ground, no load (11)                   |                         | 10  |      | mA   |

| Table 2            | Table 25. EPF10K50V & EPF10K130V Device Capacitance(12) |                                     |     |     |      |  |  |

|--------------------|---------------------------------------------------------|-------------------------------------|-----|-----|------|--|--|

| Symbol             | Parameter                                               | Conditions                          | Min | Max | Unit |  |  |

| C <sub>IN</sub>    | Input capacitance                                       | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 10  | pF   |  |  |

| C <sub>INCLK</sub> | Input capacitance on dedicated clock pin                | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 15  | pF   |  |  |

| C <sub>OUT</sub>   | Output capacitance                                      | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 10  | pF   |  |  |

#### Notes to tables:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input voltage is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 5.75 V for input currents less than 100 mA and periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $V_{CC}$  rise time is 100 ms.  $V_{CC}$  must rise monotonically.

- (5) EPF10K50V and EPF10K130V device inputs may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (6) Typical values are for  $T_A = 25^{\circ}$  C and  $V_{CC} = 3.3$  V.

- (7) These values are specified under the EPF10K50V and EPF10K130V device Recommended Operating Conditions in Table 23 on page 48.

- (8) The  $I_{OH}$  parameter refers to high-level TTL or CMOS output current.

- (9) The I<sub>OL</sub> parameter refers to low-level TTL or CMOS output current. This parameter applies to open-drain pins as well as output pins.

- (10) This value is specified for normal device operation. The value may vary during power-up.

- (11) This parameter applies to -1 speed grade EPF10K50V devices, -2 speed grade EPF10K50V industrial temperature devices, and -2 speed grade EPF10K130V devices.

- (12) Capacitance is sample-tested only.

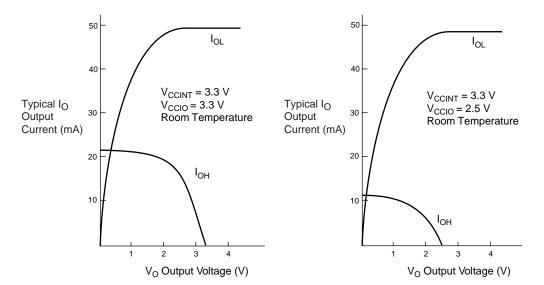

Figure 23. Output Drive Characteristics for EPF10K250A Device

# **Timing Model**

The continuous, high-performance FastTrack Interconnect routing resources ensure predictable performance and accurate simulation and timing analysis. This predictable performance contrasts with that of FPGAs, which use a segmented connection scheme and therefore have unpredictable performance.

Device performance can be estimated by following the signal path from a source, through the interconnect, to the destination. For example, the registered performance between two LEs on the same row can be calculated by adding the following parameters:

- LE register clock-to-output delay ( $t_{CO}$ )

- Interconnect delay ( $t_{SAMEROW}$ )

- LE look-up table delay ( $t_{LIIT}$ )

- LE register setup time ( $t_{SU}$ )

The routing delay depends on the placement of the source and destination LEs. A more complex registered path may involve multiple combinatorial LEs between the source and destination LEs.

| Table 32. LE Timing Microparameters (Part 2 of 2) Note (1) |                                                                                                                                      |            |  |  |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|

| Symbol                                                     | Parameter                                                                                                                            | Conditions |  |  |

| t <sub>SU</sub>                                            | LE register setup time for data and enable signals before clock; LE register recovery time after asynchronous clear, preset, or load |            |  |  |

| t <sub>H</sub>                                             | LE register hold time for data and enable signals after clock                                                                        |            |  |  |

| t <sub>PRE</sub>                                           | LE register preset delay                                                                                                             |            |  |  |

| t <sub>CLR</sub>                                           | LE register clear delay                                                                                                              |            |  |  |

| t <sub>CH</sub>                                            | Minimum clock high time from clock pin                                                                                               |            |  |  |

| $t_{CL}$                                                   | Minimum clock low time from clock pin                                                                                                |            |  |  |

| Table 33. IOE       | E Timing Microparameters Note (1)                                                                                     |                |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|----------------|

| Symbol              | Parameter                                                                                                             | Conditions     |

| $t_{IOD}$           | IOE data delay                                                                                                        |                |

| t <sub>IOC</sub>    | IOE register control signal delay                                                                                     |                |

| t <sub>IOCO</sub>   | IOE register clock-to-output delay                                                                                    |                |

| t <sub>IOCOMB</sub> | IOE combinatorial delay                                                                                               |                |

| t <sub>IOSU</sub>   | IOE register setup time for data and enable signals before clock; IOE register recovery time after asynchronous clear |                |

| t <sub>IOH</sub>    | IOE register hold time for data and enable signals after clock                                                        |                |

| t <sub>IOCLR</sub>  | IOE register clear time                                                                                               |                |

| t <sub>OD1</sub>    | Output buffer and pad delay, slow slew rate = off, $V_{CCIO} = V_{CCINT}$                                             | C1 = 35 pF (2) |

| $t_{OD2}$           | Output buffer and pad delay, slow slew rate = off, $V_{CCIO}$ = low voltage                                           | C1 = 35 pF (3) |

| t <sub>OD3</sub>    | Output buffer and pad delay, slow slew rate = on                                                                      | C1 = 35 pF (4) |

| $t_{XZ}$            | IOE output buffer disable delay                                                                                       |                |

| $t_{ZX1}$           | IOE output buffer enable delay, slow slew rate = off, $V_{CCIO} = V_{CCINT}$                                          | C1 = 35 pF (2) |

| $t_{ZX2}$           | IOE output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = low voltage                                 | C1 = 35 pF (3) |

| $t_{ZX3}$           | IOE output buffer enable delay, slow slew rate = on                                                                   | C1 = 35 pF (4) |

| t <sub>INREG</sub>  | IOE input pad and buffer to IOE register delay                                                                        |                |

| $t_{IOFD}$          | IOE register feedback delay                                                                                           |                |

| t <sub>INCOMB</sub> | IOE input pad and buffer to FastTrack Interconnect delay                                                              |                |

| Symbol                   | Parameter                                                                                                            | Conditions |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------|------------|--|

| t <sub>DIN2IOE</sub>     | Delay from dedicated input pin to IOE control input                                                                  | (7)        |  |

| t <sub>DCLK2LE</sub>     | Delay from dedicated clock pin to LE or EAB clock                                                                    | (7)        |  |

| t <sub>DIN2DATA</sub>    | Delay from dedicated input or clock to LE or EAB data                                                                | (7)        |  |

| t <sub>DCLK2IOE</sub>    | Delay from dedicated clock pin to IOE clock                                                                          | (7)        |  |

| t <sub>DIN2LE</sub>      | Delay from dedicated input pin to LE or EAB control input                                                            | (7)        |  |

| t <sub>SAMELAB</sub>     | Routing delay for an LE driving another LE in the same LAB                                                           |            |  |

| t <sub>SAMEROW</sub>     | Routing delay for a row IOE, LE, or EAB driving a row IOE, LE, or EAB in the same row                                |            |  |

| t <sub>SAME</sub> COLUMN | Routing delay for an LE driving an IOE in the same column                                                            | (7)        |  |

| t <sub>DIFFROW</sub>     | Routing delay for a column IOE, LE, or EAB driving an LE or EAB in a different row                                   | (7)        |  |

| t <sub>TWOROWS</sub>     | Routing delay for a row IOE or EAB driving an LE or EAB in a different row                                           | (7)        |  |

| t <sub>LEPERIPH</sub>    | Routing delay for an LE driving a control signal of an IOE via the peripheral control bus                            | (7)        |  |

| t <sub>LABCARRY</sub>    | Routing delay for the carry-out signal of an LE driving the carry-in signal of a different LE in a different LAB     |            |  |

| t <sub>LABCASC</sub>     | Routing delay for the cascade-out signal of an LE driving the cascade-in signal of a different LE in a different LAB |            |  |

| Table 37. External Timing Parameters Notes (8), (10) |                                                                                                |            |  |  |

|------------------------------------------------------|------------------------------------------------------------------------------------------------|------------|--|--|

| Symbol                                               | Parameter                                                                                      | Conditions |  |  |

| t <sub>DRR</sub>                                     | Register-to-register delay via four LEs, three row interconnects, and four local interconnects | (9)        |  |  |

| t <sub>INSU</sub>                                    | Setup time with global clock at IOE register                                                   |            |  |  |

| t <sub>INH</sub>                                     | Hold time with global clock at IOE register                                                    |            |  |  |

| t <sub>OUTCO</sub>                                   | Clock-to-output delay with global clock at IOE register                                        |            |  |  |

| Table 38. External Bidirectional Timing Parameters       Note (10) |                                                                                |           |  |  |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------|--|--|

| Symbol                                                             | Parameter                                                                      | Condition |  |  |

| t <sub>INSUBIDIR</sub>                                             | Setup time for bidirectional pins with global clock at adjacent LE register    |           |  |  |

| t <sub>INHBIDIR</sub>                                              | Hold time for bidirectional pins with global clock at adjacent LE register     |           |  |  |

| t <sub>OUTCOBIDIR</sub>                                            | Clock-to-output delay for bidirectional pins with global clock at IOE register |           |  |  |

| t <sub>XZBIDIR</sub>                                               | Synchronous IOE output buffer disable delay                                    |           |  |  |

| t <sub>ZXBIDIR</sub>                                               | Synchronous IOE output buffer enable delay, slow slew rate = off               |           |  |  |

Tables 39 through 47 show EPF10K10 and EPF10K20 device internal and external timing parameters.

| Symbol              | -3 Spee | d Grade | -4 Speed Grade |     | Unit |

|---------------------|---------|---------|----------------|-----|------|

|                     | Min     | Max     | Min            | Max |      |

| $t_{LUT}$           |         | 1.4     |                | 1.7 | ns   |

| t <sub>CLUT</sub>   |         | 0.6     |                | 0.7 | ns   |

| t <sub>RLUT</sub>   |         | 1.5     |                | 1.9 | ns   |

| t <sub>PACKED</sub> |         | 0.6     |                | 0.9 | ns   |

| $t_{EN}$            |         | 1.0     |                | 1.2 | ns   |

| t <sub>CICO</sub>   |         | 0.2     |                | 0.3 | ns   |

| t <sub>CGEN</sub>   |         | 0.9     |                | 1.2 | ns   |

| t <sub>CGENR</sub>  |         | 0.9     |                | 1.2 | ns   |

| t <sub>CASC</sub>   |         | 0.8     |                | 0.9 | ns   |

| $t_{\mathbb{C}}$    |         | 1.3     |                | 1.5 | ns   |

| $t_{CO}$            |         | 0.9     |                | 1.1 | ns   |

| $t_{\text{COMB}}$   |         | 0.5     |                | 0.6 | ns   |

| t <sub>SU</sub>     | 1.3     |         | 2.5            |     | ns   |

| $t_H$               | 1.4     |         | 1.6            |     | ns   |

| t <sub>PRE</sub>    |         | 1.0     |                | 1.2 | ns   |

| t <sub>CLR</sub>    |         | 1.0     |                | 1.2 | ns   |

| t <sub>CH</sub>     | 4.0     |         | 4.0            |     | ns   |

| $t_{CL}$            | 4.0     |         | 4.0            |     | ns   |

| Symbol              | -3 Speed Grade |     | -4 Spee | d Grade | Unit |

|---------------------|----------------|-----|---------|---------|------|

|                     | Min            | Max | Min     | Max     |      |

| $t_{IOD}$           |                | 1.3 |         | 1.6     | ns   |

| t <sub>IOC</sub>    |                | 0.5 |         | 0.7     | ns   |

| t <sub>IOCO</sub>   |                | 0.2 |         | 0.2     | ns   |

| t <sub>IOCOMB</sub> |                | 0.0 |         | 0.0     | ns   |

| t <sub>IOSU</sub>   | 2.8            |     | 3.2     |         | ns   |

| t <sub>IOH</sub>    | 1.0            |     | 1.2     |         | ns   |

| t <sub>IOCLR</sub>  |                | 1.0 |         | 1.2     | ns   |

| t <sub>OD1</sub>    |                | 2.6 |         | 3.5     | ns   |

| $t_{\text{OD2}}$    |                | 4.9 |         | 6.4     | ns   |

| $t_{OD3}$           |                | 6.3 |         | 8.2     | ns   |

| $t_{XZ}$            |                | 4.5 |         | 5.4     | ns   |

| t <sub>ZX1</sub>    |                | 4.5 |         | 5.4     | ns   |

| t <sub>ZX2</sub>    |                | 6.8 |         | 8.3     | ns   |

| t <sub>ZX3</sub>    |                | 8.2 |         | 10.1    | ns   |

| t <sub>INREG</sub>  |                | 6.0 |         | 7.5     | ns   |

| t <sub>IOFD</sub>   |                | 3.1 |         | 3.5     | ns   |

| t <sub>INCOMB</sub> |                | 3.1 |         | 3.5     | ns   |

| Symbol                 | -3 Spee | d Grade | -4 Spee | Unit |    |

|------------------------|---------|---------|---------|------|----|

|                        | Min     | Max     | Min     | Max  |    |

| $t_{EABAA}$            |         | 13.7    |         | 17.0 | ns |

| t <sub>EABRCCOMB</sub> | 13.7    |         | 17.0    |      | ns |

| t <sub>EABRCREG</sub>  | 9.7     |         | 11.9    |      | ns |

| t <sub>EABWP</sub>     | 5.8     |         | 7.2     |      | ns |

| t <sub>EABWCCOMB</sub> | 7.3     |         | 9.0     |      | ns |

| t <sub>EABWCREG</sub>  | 13.0    |         | 16.0    |      | ns |

| t <sub>EABDD</sub>     |         | 10.0    |         | 12.5 | ns |

| t <sub>EABDATACO</sub> |         | 2.0     |         | 3.4  | ns |

| t <sub>EABDATASU</sub> | 5.3     |         | 5.6     |      | ns |

| t <sub>EABDATAH</sub>  | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWESU</sub>   | 5.5     |         | 5.8     |      | ns |

| t <sub>EABWEH</sub>    | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWDSU</sub>   | 5.5     |         | 5.8     |      | ns |

| t <sub>EABWDH</sub>    | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWASU</sub>   | 2.1     |         | 2.7     |      | ns |

| t <sub>EABWAH</sub>    | 0.0     |         | 0.0     |      | ns |

| t <sub>EABWO</sub>     |         | 9.5     |         | 11.8 | ns |

Tables 48 through 56 show EPF10K30, EPF10K40, and EPF10K50 device internal and external timing parameters.

| Symbol              | -3 Spee | d Grade | -4 Spee | Unit |    |

|---------------------|---------|---------|---------|------|----|

|                     | Min     | Max     | Min     | Max  |    |

| $t_{LUT}$           |         | 1.3     |         | 1.8  | ns |

| t <sub>CLUT</sub>   |         | 0.6     |         | 0.6  | ns |

| t <sub>RLUT</sub>   |         | 1.5     |         | 2.0  | ns |

| t <sub>PACKED</sub> |         | 0.5     |         | 0.8  | ns |

| t <sub>EN</sub>     |         | 0.9     |         | 1.5  | ns |

| tcico               |         | 0.2     |         | 0.4  | ns |

| t <sub>CGEN</sub>   |         | 0.9     |         | 1.4  | ns |

| t <sub>CGENR</sub>  |         | 0.9     |         | 1.4  | ns |

| t <sub>CASC</sub>   |         | 1.0     |         | 1.2  | ns |

| $t_{\mathbb{C}}$    |         | 1.3     |         | 1.6  | ns |

| $t_{CO}$            |         | 0.9     |         | 1.2  | ns |

| t <sub>COMB</sub>   |         | 0.6     |         | 0.6  | ns |

| $t_{SU}$            | 1.4     |         | 1.4     |      | ns |

| $t_H$               | 0.9     |         | 1.3     |      | ns |

| t <sub>PRE</sub>    |         | 0.9     |         | 1.2  | ns |

| t <sub>CLR</sub>    |         | 0.9     |         | 1.2  | ns |

| t <sub>CH</sub>     | 4.0     |         | 4.0     |      | ns |

| $t_{CL}$            | 4.0     |         | 4.0     |      | ns |

| Symbol                          | -3DX Spe | -3DX Speed Grade |     | d Grade | -4 Spee | Unit |    |

|---------------------------------|----------|------------------|-----|---------|---------|------|----|

|                                 | Min      | Max              | Min | Max     | Min     | Max  | 1  |

| t <sub>DRR</sub>                |          | 19.1             |     | 19.1    |         | 24.2 | ns |

| t <sub>INSU</sub> (2), (3), (4) | 7.8      |                  | 7.8 |         | 8.5     |      | ns |

| t <sub>OUTCO</sub> (3), (4)     | 2.0      | 11.1             | 2.0 | 11.1    | 2.0     | 14.3 | ns |

| t <sub>INH</sub> (3)            | 0.0      |                  | 0.0 |         | 0.0     |      | ns |

| t <sub>INSU</sub> (2), (3), (5) | 6.2      |                  | -   |         | -       |      | ns |

| t <sub>OUTCO</sub> (3), (5)     | 2.0      | 6.7              |     | _       |         | _    | ns |

| Symbol                     | -3DX Speed Grade |      | -3 Spee | d Grade | -4 Spee | Unit |    |

|----------------------------|------------------|------|---------|---------|---------|------|----|

|                            | Min              | Max  | Min     | Max     | Min     | Max  | 1  |

| t <sub>INSUBIDIR</sub> (4) | 8.1              |      | 8.1     |         | 10.4    |      | ns |

| t <sub>INHBIDIR</sub> (4)  | 0.0              |      | 0.0     |         | 0.0     |      | ns |

| toutcobidir (4)            | 2.0              | 11.1 | 2.0     | 11.1    | 2.0     | 14.3 | ns |

| t <sub>XZBIDIR</sub> (4)   |                  | 15.3 |         | 15.3    |         | 18.4 | ns |

| t <sub>ZXBIDIR</sub> (4)   |                  | 15.3 |         | 15.3    |         | 18.4 | ns |

| t <sub>INSUBIDIR</sub> (5) | 9.1              |      | -       |         | -       |      | ns |

| t <sub>INHBIDIR</sub> (5)  | 0.0              |      | _       |         | -       |      | ns |

| toutcobidir (5)            | 2.0              | 7.2  | -       | -       | _       | _    | ns |

| t <sub>XZBIDIR</sub> (5)   |                  | 14.3 |         | -       |         | -    | ns |

| t <sub>ZXBIDIR</sub> (5)   |                  | 14.3 |         | -       |         | _    | ns |

#### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

- (4) This parameter is measured without the use of the ClockLock or ClockBoost circuits.

- (5) This parameter is measured with the use of the ClockLock or ClockBoost circuits.

| Symbol                 | 1 Cnood Crodo |                | 2 Cnood Crodo |                | 2 Chood Crode |                | 4 Onesad Oreada |                | Unit |

|------------------------|---------------|----------------|---------------|----------------|---------------|----------------|-----------------|----------------|------|

| Symbol                 | -1 Spee       | -1 Speed Grade |               | -2 Speed Grade |               | -3 Speed Grade |                 | -4 Speed Grade |      |

|                        | Min           | Max            | Min           | Max            | Min           | Max            | Min             | Max            |      |

| t <sub>EABDATA1</sub>  |               | 1.7            |               | 2.8            |               | 3.4            |                 | 4.6            | ns   |

| t <sub>EABDATA2</sub>  |               | 4.9            |               | 3.9            |               | 4.8            |                 | 5.9            | ns   |

| t <sub>EABWE1</sub>    |               | 0.0            |               | 2.5            |               | 3.0            |                 | 3.7            | ns   |

| t <sub>EABWE2</sub>    |               | 4.0            |               | 4.1            |               | 5.0            |                 | 6.2            | ns   |

| t <sub>EABCLK</sub>    |               | 0.4            |               | 0.8            |               | 1.0            |                 | 1.2            | ns   |

| t <sub>EABCO</sub>     |               | 0.1            |               | 0.2            |               | 0.3            |                 | 0.4            | ns   |

| t <sub>EABBYPASS</sub> |               | 0.9            |               | 1.1            |               | 1.3            |                 | 1.6            | ns   |

| t <sub>EABSU</sub>     | 0.8           |                | 1.5           |                | 1.8           |                | 2.2             |                | ns   |

| t <sub>EABH</sub>      | 0.8           |                | 1.6           |                | 2.0           |                | 2.5             |                | ns   |

| $t_{AA}$               |               | 5.5            |               | 8.2            |               | 10.0           |                 | 12.4           | ns   |

| $t_{WP}$               | 6.0           |                | 4.9           |                | 6.0           |                | 7.4             |                | ns   |

| t <sub>WDSU</sub>      | 0.1           |                | 0.8           |                | 1.0           |                | 1.2             |                | ns   |

| t <sub>WDH</sub>       | 0.1           |                | 0.2           |                | 0.3           |                | 0.4             |                | ns   |

| t <sub>WASU</sub>      | 0.1           |                | 0.4           |                | 0.5           |                | 0.6             |                | ns   |

| t <sub>WAH</sub>       | 0.1           |                | 0.8           |                | 1.0           |                | 1.2             |                | ns   |

| $t_{WO}$               |               | 2.8            |               | 4.3            |               | 5.3            |                 | 6.5            | ns   |

| $t_{DD}$               |               | 2.8            |               | 4.3            |               | 5.3            |                 | 6.5            | ns   |

| t <sub>EABOUT</sub>    |               | 0.5            |               | 0.4            |               | 0.5            |                 | 0.6            | ns   |

| t <sub>EABCH</sub>     | 2.0           |                | 4.0           |                | 4.0           |                | 4.0             |                | ns   |

| t <sub>EABCL</sub>     | 6.0           |                | 4.9           |                | 6.0           |                | 7.4             |                | ns   |

| Symbol              | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | Unit |    |

|---------------------|----------------|-----|---------|---------|---------|------|----|

|                     | Min            | Max | Min     | Max     | Min     | Max  |    |

| t <sub>IOH</sub>    | 0.8            |     | 1.0     |         | 1.3     |      | ns |

| t <sub>IOCLR</sub>  |                | 1.2 |         | 1.4     |         | 1.9  | ns |

| t <sub>OD1</sub>    |                | 1.2 |         | 1.4     |         | 1.9  | ns |

| $t_{OD2}$           |                | 2.9 |         | 3.5     |         | 4.7  | ns |

| $t_{OD3}$           |                | 6.6 |         | 7.8     |         | 10.5 | ns |

| $t_{XZ}$            |                | 1.2 |         | 1.4     |         | 1.9  | ns |

| $t_{ZX1}$           |                | 1.2 |         | 1.4     |         | 1.9  | ns |

| $t_{ZX2}$           |                | 2.9 |         | 3.5     |         | 4.7  | ns |

| $t_{ZX3}$           |                | 6.6 |         | 7.8     |         | 10.5 | ns |

| t <sub>INREG</sub>  |                | 5.2 |         | 6.3     |         | 8.4  | ns |

| t <sub>IOFD</sub>   |                | 3.1 |         | 3.8     |         | 5.0  | ns |

| t <sub>INCOMB</sub> |                | 3.1 |         | 3.8     |         | 5.0  | ns |

| Symbol              | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | Unit |    |

|---------------------|----------------|-----|---------|---------|---------|------|----|

|                     | Min            | Max | Min     | Max     | Min     | Max  |    |

| $t_{IOD}$           |                | 1.2 |         | 1.3     |         | 1.6  | ns |

| $t_{IOC}$           |                | 0.4 |         | 0.4     |         | 0.5  | ns |

| t <sub>IOCO</sub>   |                | 0.8 |         | 0.9     |         | 1.1  | ns |

| $t_{IOCOMB}$        |                | 0.7 |         | 0.7     |         | 0.8  | ns |

| t <sub>IOSU</sub>   | 2.7            |     | 3.1     |         | 3.6     |      | ns |

| $t_{IOH}$           | 0.2            |     | 0.3     |         | 0.3     |      | ns |

| t <sub>IOCLR</sub>  |                | 1.2 |         | 1.3     |         | 1.6  | ns |

| t <sub>OD1</sub>    |                | 3.2 |         | 3.6     |         | 4.2  | ns |

| t <sub>OD2</sub>    |                | 5.9 |         | 6.7     |         | 7.8  | ns |

| $t_{OD3}$           |                | 8.7 |         | 9.8     |         | 11.5 | ns |

| $t_{XZ}$            |                | 3.8 |         | 4.3     |         | 5.0  | ns |

| $t_{ZX1}$           |                | 3.8 |         | 4.3     |         | 5.0  | ns |

| t <sub>ZX2</sub>    |                | 6.5 |         | 7.4     |         | 8.6  | ns |

| t <sub>ZX3</sub>    |                | 9.3 |         | 10.5    |         | 12.3 | ns |

| t <sub>INREG</sub>  |                | 8.2 |         | 9.3     |         | 10.9 | ns |

| t <sub>IOFD</sub>   |                | 9.0 |         | 10.2    |         | 12.0 | ns |

| t <sub>INCOMB</sub> |                | 9.0 |         | 10.2    |         | 12.0 | ns |

| Symbol                 | -1 Spee | -1 Speed Grade |      | -2 Speed Grade |      | -3 Speed Grade |    |

|------------------------|---------|----------------|------|----------------|------|----------------|----|

|                        | Min     | Max            | Min  | Max            | Min  | Max            |    |

| t <sub>EABAA</sub>     |         | 6.1            |      | 6.8            |      | 8.2            | ns |

| t <sub>EABRCCOMB</sub> | 6.1     |                | 6.8  |                | 8.2  |                | ns |

| t <sub>EABRCREG</sub>  | 4.6     |                | 5.1  |                | 6.1  |                | ns |

| t <sub>EABWP</sub>     | 5.6     |                | 6.4  |                | 7.5  |                | ns |

| t <sub>EABWCCOMB</sub> | 5.8     |                | 6.6  |                | 7.9  |                | ns |

| t <sub>EABWCREG</sub>  | 15.8    |                | 17.8 |                | 21.0 |                | ns |

| t <sub>EABDD</sub>     |         | 5.7            |      | 6.4            |      | 7.8            | ns |

| t <sub>EABDATACO</sub> |         | 0.7            |      | 0.8            |      | 1.0            | ns |

| t <sub>EABDATASU</sub> | 4.5     |                | 5.1  |                | 5.9  |                | ns |

| t <sub>EABDATAH</sub>  | 0.0     |                | 0.0  |                | 0.0  |                | ns |

| t <sub>EABWESU</sub>   | 8.2     |                | 9.3  |                | 10.9 |                | ns |

| t <sub>EABWEH</sub>    | 0.0     |                | 0.0  |                | 0.0  |                | ns |

| t <sub>EABWDSU</sub>   | 1.7     |                | 1.8  |                | 2.1  |                | ns |

| t <sub>EABWDH</sub>    | 0.0     |                | 0.0  |                | 0.0  |                | ns |

| t <sub>EABWASU</sub>   | 0.9     |                | 0.9  |                | 1.0  |                | ns |

| t <sub>EABWAH</sub>    | 0.0     |                | 0.0  |                | 0.0  |                | ns |

| t <sub>EABWO</sub>     |         | 5.3            |      | 6.0            |      | 7.4            | ns |

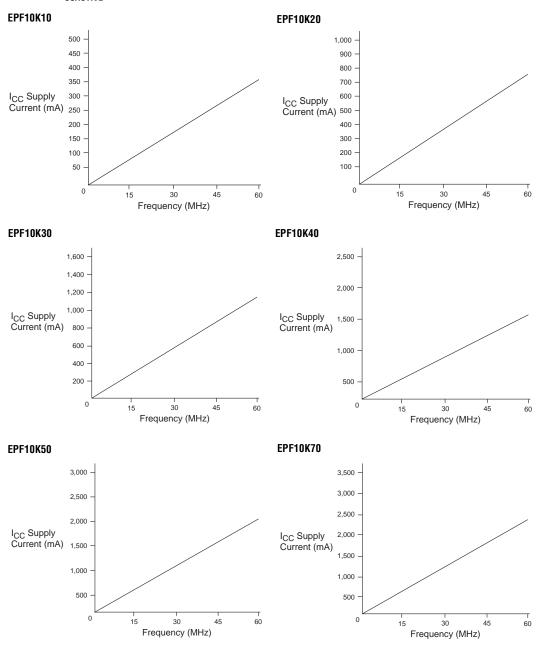

Figure 32. I<sub>CCACTIVE</sub> vs. Operating Frequency (Part 1 of 3)

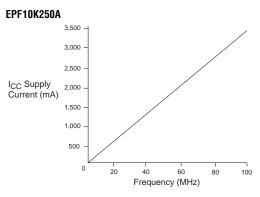

Figure 32. I<sub>CCACTIVE</sub> vs. Operating Frequency (Part 3 of 3)

# Configuration & Operation

The FLEX 10K architecture supports several configuration schemes. This section summarizes the device operating modes and available device configuration schemes.

See Application Note 116 (Configuring APEX 20K, FLEX 10K & FLEX 6000 Devices) for detailed descriptions of device configuration options, device configuration pins, and for information on configuring FLEX 10K devices, including sample schematics, timing diagrams, and configuration parameters.

# **Operating Modes**

The FLEX 10K architecture uses SRAM configuration elements that require configuration data to be loaded every time the circuit powers up. The process of physically loading the SRAM data into the device is called *configuration*. Before configuration, as VCC rises, the device initiates a Power-On Reset (POR). This POR event clears the device and prepares it for configuration. The FLEX 10K POR time does not exceed 50  $\mu s$ .

During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called *command mode*; normal device operation is called *user mode*.

SRAM configuration elements allow FLEX 10K devices to be reconfigured in-circuit by loading new configuration data into the device. Real-time reconfiguration is performed by forcing the device into command mode with a device pin, loading different configuration data, reinitializing the device, and resuming user-mode operation.

The entire reconfiguration process may be completed in less than 320 ms using an EPF10K250A device with a DCLK frequency of 10 MHz. This process can be used to reconfigure an entire system dynamically. In-field upgrades can be performed by distributing new configuration files.

Refer to the configuration device data sheet to obtain the POR delay when using a configuration device method.

# **Programming Files**

Despite being function- and pin-compatible, FLEX 10KA and FLEX 10KE devices are not programming- or configuration-file compatible with FLEX 10K devices. A design should be recompiled before it is transferred from a FLEX 10K device to an equivalent FLEX 10KA or FLEX 10KE device. This recompilation should be performed to create a new programming or configuration file and to check design timing on the faster FLEX 10KA or FLEX 10KE device. The programming or configuration files for EPF10K50 devices can program or configure an EPF10K50V device. However, Altera recommends recompiling a design for the EPF10K50V device when transferring it from the EPF10K50 device.

# **Configuration Schemes**

The configuration data for a FLEX 10K device can be loaded with one of five configuration schemes (see Table 116), chosen on the basis of the target application. An EPC1, EPC2, EPC16, or EPC1441 configuration device, intelligent controller, or the JTAG port can be used to control the configuration of a FLEX 10K device, allowing automatic configuration on system power-up.