Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

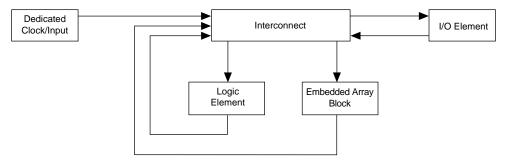

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 360                                                         |

| Number of Logic Elements/Cells | 2880                                                        |

| Total RAM Bits                 | 20480                                                       |

| Number of I/O                  | 189                                                         |

| Number of Gates                | 116000                                                      |

| Voltage - Supply               | 3V ~ 3.6V                                                   |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 70°C (TA)                                             |

| Package / Case                 | 240-BFQFP Exposed Pad                                       |

| Supplier Device Package        | 240-RQFP (32x32)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/epf10k50vrc240-2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Logic functions are implemented by programming the EAB with a readonly pattern during configuration, creating a large LUT. With LUTs, combinatorial functions are implemented by looking up the results, rather than by computing them. This implementation of combinatorial functions can be faster than using algorithms implemented in general logic, a performance advantage that is further enhanced by the fast access times of EABs. The large capacity of EABs enables designers to implement complex functions in one logic level without the routing delays associated with linked LEs or field-programmable gate array (FPGA) RAM blocks. For example, a single EAB can implement a  $4 \times 4$  multiplier with eight inputs and eight outputs. Parameterized functions such as LPM functions can automatically take advantage of the EAB.

The EAB provides advantages over FPGAs, which implement on-board RAM as arrays of small, distributed RAM blocks. These FPGA RAM blocks contain delays that are less predictable as the size of the RAM increases. In addition, FPGA RAM blocks are prone to routing problems because small blocks of RAM must be connected together to make larger blocks. In contrast, EABs can be used to implement large, dedicated blocks of RAM that eliminate these timing and routing concerns.

EABs can be used to implement synchronous RAM, which is easier to use than asynchronous RAM. A circuit using asynchronous RAM must generate the RAM write enable (WE) signal, while ensuring that its data and address signals meet setup and hold time specifications relative to the WE signal. In contrast, the EAB's synchronous RAM generates its own WE signal and is self-timed with respect to the global clock. A circuit using the EAB's self-timed RAM need only meet the setup and hold time specifications of the global clock.

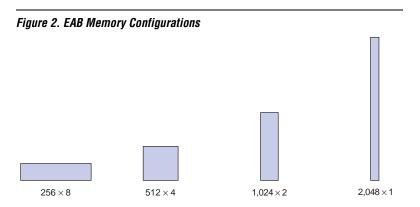

When used as RAM, each EAB can be configured in any of the following sizes:  $256 \times 8$ ,  $512 \times 4$ ,  $1,024 \times 2$ , or  $2,048 \times 1$ . See Figure 2.

## **Logic Array Block**

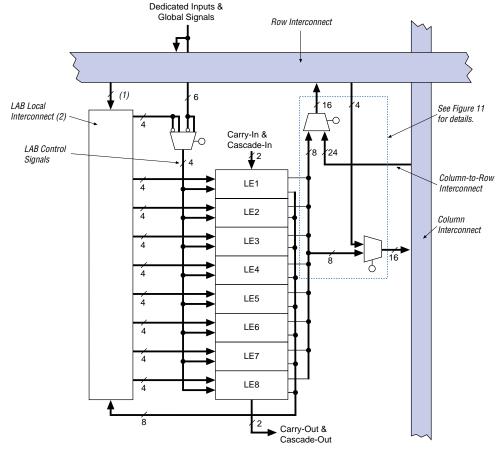

Each LAB consists of eight LEs, their associated carry and cascade chains, LAB control signals, and the LAB local interconnect. The LAB provides the coarse-grained structure to the FLEX 10K architecture, facilitating efficient routing with optimum device utilization and high performance. See Figure 5.

Figure 5. FLEX 10K LAB

#### Notes:

- (1) EPF10K10, EPF10K10A, EPF10K20, EPF10K30, EPF10K30A, EPF10K40, EPF10K50, and EPF10K50V devices have 22 inputs to the LAB local interconnect channel from the row; EPF10K70, EPF10K100, EPF10K100A, EPF10K130V, and EPF10K250A devices have 26.

- (2) EPF10K10, EPF10K10A, EPF10K20, EPF10K30, EPF10K30A, EPF10K40, EPF10K50, and EPF10K50V devices have 30 LAB local interconnect channels; EPF10K70, EPF10K100, EPF10K100A, EPF10K130V, and EPF10K250A devices have 34 LABs.

## LE Operating Modes

The FLEX 10K LE can operate in the following four modes:

- Normal mode

- Arithmetic mode

- Up/down counter mode

- Clearable counter mode

Each of these modes uses LE resources differently. In each mode, seven available inputs to the LE—the four data inputs from the LAB local interconnect, the feedback from the programmable register, and the carry-in and cascade-in from the previous LE—are directed to different destinations to implement the desired logic function. Three inputs to the LE provide clock, clear, and preset control for the register. The Altera software, in conjunction with parameterized functions such as LPM and DesignWare functions, automatically chooses the appropriate mode for common functions such as counters, adders, and multipliers. If required, the designer can also create special-purpose functions which use a specific LE operating mode for optimal performance.

The architecture provides a synchronous clock enable to the register in all four modes. The Altera software can set DATA1 to enable the register synchronously, providing easy implementation of fully synchronous designs.

Figure 9 shows the LE operating modes.

| Table 8. EPF10K10, EPF10K20, | Table 8. EPF10K10, EPF10K20, EPF10K30, EPF10K40 & EPF10K50 Peripheral Bus Sources |          |                       |          |                       |  |  |

|------------------------------|-----------------------------------------------------------------------------------|----------|-----------------------|----------|-----------------------|--|--|

| Peripheral<br>Control Signal | EPF10K10<br>EPF10K10A                                                             | EPF10K20 | EPF10K30<br>EPF10K30A | EPF10K40 | EPF10K50<br>EPF10K50V |  |  |

| OE0                          | Row A                                                                             | Row A    | Row A                 | Row A    | Row A                 |  |  |

| OE1                          | Row A                                                                             | Row B    | Row B                 | Row C    | Row B                 |  |  |

| OE2                          | Row B                                                                             | Row C    | Row C                 | Row D    | Row D                 |  |  |

| OE3                          | Row B                                                                             | Row D    | Row D                 | Row E    | Row F                 |  |  |

| OE4                          | Row C                                                                             | Row E    | Row E                 | Row F    | Row H                 |  |  |

| OE5                          | Row C                                                                             | Row F    | Row F                 | Row G    | Row J                 |  |  |

| CLKENA0/CLK0/GLOBAL0         | Row A                                                                             | Row A    | Row A                 | Row B    | Row A                 |  |  |

| CLKENA1/OE6/GLOBAL1          | Row A                                                                             | Row B    | Row B                 | Row C    | Row C                 |  |  |

| CLKENA2/CLR0                 | Row B                                                                             | Row C    | Row C                 | Row D    | Row E                 |  |  |

| CLKENA3/OE7/GLOBAL2          | Row B                                                                             | Row D    | Row D                 | Row E    | Row G                 |  |  |

| CLKENA4/CLR1                 | Row C                                                                             | Row E    | Row E                 | Row F    | Row I                 |  |  |

| CLKENA5/CLK1/GLOBAL3         | Row C                                                                             | Row F    | Row F                 | Row H    | Row J                 |  |  |

| Peripheral<br>Control Signal | EPF10K70 | EPF10K100<br>EPF10K100A | EPF10K130V | EPF10K250A |

|------------------------------|----------|-------------------------|------------|------------|

| OE 0                         | Row A    | Row A                   | Row C      | Row E      |

| OE1                          | Row B    | Row C                   | Row E      | Row G      |

| OE2                          | Row D    | Row E                   | Row G      | Row I      |

| OE3                          | Row I    | Row L                   | Row N      | Row P      |

| OE 4                         | Row G    | Row I                   | Row K      | Row M      |

| OE5                          | Row H    | Row K                   | Row M      | Row O      |

| CLKENA0/CLK0/GLOBAL0         | Row E    | Row F                   | Row H      | Row J      |

| CLKENA1/OE6/GLOBAL1          | Row C    | Row D                   | Row F      | Row H      |

| CLKENA2/CLR0                 | Row B    | Row B                   | Row D      | Row F      |

| CLKENA3/OE7/GLOBAL2          | Row F    | Row H                   | Row J      | Row L      |

| CLKENA4/CLR1                 | Row H    | Row J                   | Row L      | Row N      |

| CLKENA5/CLK1/GLOBAL3         | Row E    | Row G                   | Row I      | Row K      |

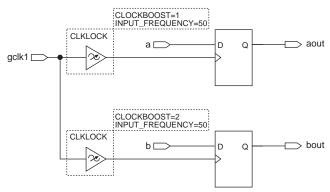

Figure 17. Enabling ClockLock & ClockBoost in the Same Design

To use both the ClockLock and ClockBoost circuits in the same design, designers must use Revision C EPF10K100GC503-3DX devices and MAX+PLUS II software versions 7.2 or higher. The die revision is indicated by the third digit of the nine-digit code on the top side of the device.

## Output Configuration

This section discusses the peripheral component interconnect (PCI) pull-up clamping diode option, slew-rate control, open-drain output option, MultiVolt I/O interface, and power sequencing for FLEX 10K devices. The PCI pull-up clamping diode, slew-rate control, and open-drain output options are controlled pin-by-pin via Altera logic options. The MultiVolt I/O interface is controlled by connecting  $V_{CCIO}$  to a different voltage than  $V_{CCINT}.$  Its effect can be simulated in the Altera software via the **Global Project Device Options** dialog box (Assign menu).

## **PCI Clamping Diodes**

The EPF10K10A and EPF10K30A devices have a pull-up clamping diode on every I/O, dedicated input, and dedicated clock pin. PCI clamping diodes clamp the transient overshoot caused by reflected waves to the  $V_{\rm CCIO}$  value and are required for 3.3-V PCI compliance. Clamping diodes can also be used to limit overshoot in other systems.

Clamping diodes are controlled on a pin-by-pin basis via a logic option in the Altera software. When  $V_{\rm CCIO}$  is 3.3 V, a pin that has the clamping diode turned on can be driven by a 2.5-V or 3.3-V signal, but not a 5.0-V signal. When  $V_{\rm CCIO}$  is 2.5 V, a pin that has the clamping diode turned on can be driven by a 2.5-V signal, but not a 3.3-V or 5.0-V signal. However, a clamping diode can be turned on for a subset of pins, which allows devices to bridge between a 3.3-V PCI bus and a 5.0-V device.

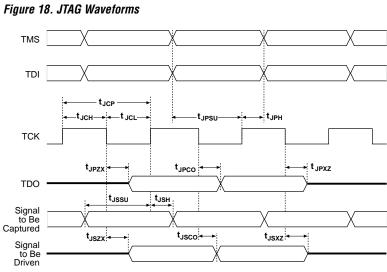

Figure 18 shows the timing requirements for the JTAG signals.

Table 16 shows the timing parameters and values for FLEX 10K devices.

| Table 1           | 6. JTAG Timing Parameters & Values             |     |     |      |

|-------------------|------------------------------------------------|-----|-----|------|

| Symbol            | Parameter                                      | Min | Max | Unit |

| t <sub>JCP</sub>  | TCK clock period                               | 100 |     | ns   |

| t <sub>JCH</sub>  | TCK clock high time                            | 50  |     | ns   |

| t <sub>JCL</sub>  | TCK clock low time                             | 50  |     | ns   |

| t <sub>JPSU</sub> | JTAG port setup time                           | 20  |     | ns   |

| t <sub>JPH</sub>  | JTAG port hold time                            | 45  |     | ns   |

| t <sub>JPCO</sub> | JTAG port clock to output                      |     | 25  | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output       |     | 25  | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance       |     | 25  | ns   |

| t <sub>JSSU</sub> | Capture register setup time                    | 20  |     | ns   |

| t <sub>JSH</sub>  | Capture register hold time                     | 45  |     | ns   |

| t <sub>JSCO</sub> | Update register clock to output                |     | 35  | ns   |

| t <sub>JSZX</sub> | Update register high-impedance to valid output |     | 35  | ns   |

| t <sub>JSXZ</sub> | Update register valid output to high impedance |     | 35  | ns   |

Timing simulation and delay prediction are available with the MAX+PLUS II Simulator and Timing Analyzer, or with industry-standard EDA tools. The Simulator offers both pre-synthesis functional simulation to evaluate logic design accuracy and post-synthesis timing simulation with 0.1-ns resolution. The Timing Analyzer provides point-to-point timing delay information, setup and hold time analysis, and device-wide performance analysis.

Figure 24 shows the overall timing model, which maps the possible paths to and from the various elements of the FLEX 10K device.

Figure 24. FLEX 10K Device Timing Model

| Table 32. LE Timing Microparameters (Part 2 of 2) Note (1) |                                                                                                                                      |            |  |  |  |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------|--|--|--|

| Symbol                                                     | Parameter                                                                                                                            | Conditions |  |  |  |

| t <sub>SU</sub>                                            | LE register setup time for data and enable signals before clock; LE register recovery time after asynchronous clear, preset, or load |            |  |  |  |

| t <sub>H</sub>                                             | LE register hold time for data and enable signals after clock                                                                        |            |  |  |  |

| t <sub>PRE</sub>                                           | LE register preset delay                                                                                                             |            |  |  |  |

| t <sub>CLR</sub>                                           | LE register clear delay                                                                                                              |            |  |  |  |

| t <sub>CH</sub>                                            | Minimum clock high time from clock pin                                                                                               |            |  |  |  |

| $t_{CL}$                                                   | Minimum clock low time from clock pin                                                                                                |            |  |  |  |

| Table 33. IOE       | E Timing Microparameters Note (1)                                                                                     |                |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|----------------|

| Symbol              | Parameter                                                                                                             | Conditions     |

| $t_{IOD}$           | IOE data delay                                                                                                        |                |

| t <sub>IOC</sub>    | IOE register control signal delay                                                                                     |                |

| t <sub>IOCO</sub>   | IOE register clock-to-output delay                                                                                    |                |

| t <sub>IOCOMB</sub> | IOE combinatorial delay                                                                                               |                |

| t <sub>IOSU</sub>   | IOE register setup time for data and enable signals before clock; IOE register recovery time after asynchronous clear |                |

| t <sub>IOH</sub>    | IOE register hold time for data and enable signals after clock                                                        |                |

| t <sub>IOCLR</sub>  | IOE register clear time                                                                                               |                |

| t <sub>OD1</sub>    | Output buffer and pad delay, slow slew rate = off, $V_{CCIO} = V_{CCINT}$                                             | C1 = 35 pF (2) |

| $t_{OD2}$           | Output buffer and pad delay, slow slew rate = off, $V_{CCIO}$ = low voltage                                           | C1 = 35 pF (3) |

| t <sub>OD3</sub>    | Output buffer and pad delay, slow slew rate = on                                                                      | C1 = 35 pF (4) |

| $t_{XZ}$            | IOE output buffer disable delay                                                                                       |                |

| $t_{ZX1}$           | IOE output buffer enable delay, slow slew rate = off, $V_{CCIO} = V_{CCINT}$                                          | C1 = 35 pF (2) |

| $t_{ZX2}$           | IOE output buffer enable delay, slow slew rate = off, V <sub>CCIO</sub> = low voltage                                 | C1 = 35 pF (3) |

| $t_{ZX3}$           | IOE output buffer enable delay, slow slew rate = on                                                                   | C1 = 35 pF (4) |

| t <sub>INREG</sub>  | IOE input pad and buffer to IOE register delay                                                                        |                |

| $t_{IOFD}$          | IOE register feedback delay                                                                                           |                |

| t <sub>INCOMB</sub> | IOE input pad and buffer to FastTrack Interconnect delay                                                              |                |

| Symbol                 | Parameter                                                                              | Conditions |

|------------------------|----------------------------------------------------------------------------------------|------------|

| t <sub>EABAA</sub>     | EAB address access delay                                                               |            |

| t <sub>EABRCCOMB</sub> | EAB asynchronous read cycle time                                                       |            |

| t <sub>EABRCREG</sub>  | EAB synchronous read cycle time                                                        |            |

| t <sub>EABWP</sub>     | EAB write pulse width                                                                  |            |

| t <sub>EABWCCOMB</sub> | EAB asynchronous write cycle time                                                      |            |

| t <sub>EABWCREG</sub>  | EAB synchronous write cycle time                                                       |            |

| t <sub>EABDD</sub>     | EAB data-in to data-out valid delay                                                    |            |

| t <sub>EABDATACO</sub> | EAB clock-to-output delay when using output registers                                  |            |

| t <sub>EABDATASU</sub> | EAB data/address setup time before clock when using input register                     |            |

| t <sub>EABDATAH</sub>  | EAB data/address hold time after clock when using input register                       |            |

| t <sub>EABWESU</sub>   | EAB WE setup time before clock when using input register                               |            |

| t <sub>EABWEH</sub>    | EAB WE hold time after clock when using input register                                 |            |

| t <sub>EABWDSU</sub>   | EAB data setup time before falling edge of write pulse when not using input registers  |            |

| t <sub>EABWDH</sub>    | EAB data hold time after falling edge of write pulse when not using input              |            |

|                        | registers                                                                              |            |

| t <sub>EABWASU</sub>   | EAB address setup time before rising edge of write pulse when not using                |            |

|                        | input registers                                                                        |            |

| <sup>t</sup> EABWAH    | EAB address hold time after falling edge of write pulse when not using input registers |            |

| t <sub>EABWO</sub>     | EAB write enable to data output valid delay                                            |            |

| Symbol                   | Parameter                                                                                                            | Conditions |  |  |

|--------------------------|----------------------------------------------------------------------------------------------------------------------|------------|--|--|

| t <sub>DIN2IOE</sub>     | Delay from dedicated input pin to IOE control input                                                                  | (7)        |  |  |

| t <sub>DCLK2LE</sub>     | Delay from dedicated clock pin to LE or EAB clock                                                                    | (7)        |  |  |

| t <sub>DIN2DATA</sub>    | Delay from dedicated input or clock to LE or EAB data                                                                | (7)        |  |  |

| t <sub>DCLK2IOE</sub>    | Delay from dedicated clock pin to IOE clock                                                                          | (7)        |  |  |

| t <sub>DIN2LE</sub>      | Delay from dedicated input pin to LE or EAB control input                                                            | (7)        |  |  |

| t <sub>SAMELAB</sub>     | Routing delay for an LE driving another LE in the same LAB                                                           |            |  |  |

| t <sub>SAMEROW</sub>     | Routing delay for a row IOE, LE, or EAB driving a row IOE, LE, or EAB in the same row                                | (7)        |  |  |

| t <sub>SAME</sub> COLUMN | Routing delay for an LE driving an IOE in the same column                                                            |            |  |  |

| t <sub>DIFFROW</sub>     | Routing delay for a column IOE, LE, or EAB driving an LE or EAB in a different row                                   | (7)        |  |  |

| t <sub>TWOROWS</sub>     | Routing delay for a row IOE or EAB driving an LE or EAB in a different row                                           | (7)        |  |  |

| t <sub>LEPERIPH</sub>    | Routing delay for an LE driving a control signal of an IOE via the peripheral control bus                            | (7)        |  |  |

| t <sub>LABCARRY</sub>    | Routing delay for the carry-out signal of an LE driving the carry-in signal of a different LE in a different LAB     |            |  |  |

| t <sub>LABCASC</sub>     | Routing delay for the cascade-out signal of an LE driving the cascade-in signal of a different LE in a different LAB |            |  |  |

| Table 37. External Timing Parameters Notes (8), (10) |                                                                                                |            |  |  |  |

|------------------------------------------------------|------------------------------------------------------------------------------------------------|------------|--|--|--|

| Symbol                                               | Parameter                                                                                      | Conditions |  |  |  |

| t <sub>DRR</sub>                                     | Register-to-register delay via four LEs, three row interconnects, and four local interconnects | (9)        |  |  |  |

| t <sub>INSU</sub>                                    | Setup time with global clock at IOE register                                                   |            |  |  |  |

| t <sub>INH</sub>                                     | Hold time with global clock at IOE register                                                    |            |  |  |  |

| t <sub>OUTCO</sub>                                   | Clock-to-output delay with global clock at IOE register                                        |            |  |  |  |

| Table 38. External Bidirectional Timing Parameters       Note (10) |                                                                                |           |  |  |  |

|--------------------------------------------------------------------|--------------------------------------------------------------------------------|-----------|--|--|--|

| Symbol                                                             | Parameter                                                                      | Condition |  |  |  |

| t <sub>INSUBIDIR</sub>                                             | Setup time for bidirectional pins with global clock at adjacent LE register    |           |  |  |  |

| t <sub>INHBIDIR</sub>                                              | Hold time for bidirectional pins with global clock at adjacent LE register     |           |  |  |  |

| t <sub>OUTCOBIDIR</sub>                                            | Clock-to-output delay for bidirectional pins with global clock at IOE register |           |  |  |  |

| t <sub>XZBIDIR</sub>                                               | Synchronous IOE output buffer disable delay                                    |           |  |  |  |

| t <sub>ZXBIDIR</sub>                                               | Synchronous IOE output buffer enable delay, slow slew rate = off               |           |  |  |  |

| Symbol              | -3 Spee | -3 Speed Grade |     | d Grade | Unit |

|---------------------|---------|----------------|-----|---------|------|

|                     | Min     | Max            | Min | Max     |      |

| t <sub>IOD</sub>    |         | 0.4            |     | 0.6     | ns   |

| t <sub>IOC</sub>    |         | 0.5            |     | 0.9     | ns   |

| t <sub>IOCO</sub>   |         | 0.4            |     | 0.5     | ns   |

| t <sub>IOCOMB</sub> |         | 0.0            |     | 0.0     | ns   |

| t <sub>iosu</sub>   | 3.1     |                | 3.5 |         | ns   |

| t <sub>IOH</sub>    | 1.0     |                | 1.9 |         | ns   |

| t <sub>IOCLR</sub>  |         | 1.0            |     | 1.2     | ns   |

| t <sub>OD1</sub>    |         | 3.3            |     | 3.6     | ns   |

| t <sub>OD2</sub>    |         | 5.6            |     | 6.5     | ns   |

| $t_{\text{OD3}}$    |         | 7.0            |     | 8.3     | ns   |

| $t_{XZ}$            |         | 5.2            |     | 5.5     | ns   |

| t <sub>ZX1</sub>    |         | 5.2            |     | 5.5     | ns   |

| t <sub>ZX2</sub>    |         | 7.5            |     | 8.4     | ns   |

| t <sub>ZX3</sub>    |         | 8.9            |     | 10.2    | ns   |

| t <sub>INREG</sub>  |         | 7.7            |     | 10.0    | ns   |

| t <sub>IOFD</sub>   |         | 3.3            |     | 4.0     | ns   |

| t <sub>INCOMB</sub> |         | 3.3            |     | 4.0     | ns   |

| Symbol                  | -3DX Spe | ed Grade | -3 Speed Grade |      | -4 Speed Grade |      | Unit |

|-------------------------|----------|----------|----------------|------|----------------|------|------|

|                         | Min      | Max      | Min            | Max  | Min            | Max  |      |

| t <sub>EABAA</sub>      |          | 13.7     |                | 13.7 |                | 17.0 | ns   |

| t <sub>EABRCCOMB</sub>  | 13.7     |          | 13.7           |      | 17.0           |      | ns   |

| t <sub>EABRCREG</sub>   | 9.7      |          | 9.7            |      | 11.9           |      | ns   |

| t <sub>EABWP</sub>      | 5.8      |          | 5.8            |      | 7.2            |      | ns   |

| t <sub>EABWCCOMB</sub>  | 7.3      |          | 7.3            |      | 9.0            |      | ns   |

| t <sub>EABWCREG</sub>   | 13.0     |          | 13.0           |      | 16.0           |      | ns   |

| t <sub>EABDD</sub>      |          | 10.0     |                | 10.0 |                | 12.5 | ns   |

| t <sub>EABDATA</sub> CO |          | 2.0      |                | 2.0  |                | 3.4  | ns   |

| t <sub>EABDATASU</sub>  | 5.3      |          | 5.3            |      | 5.6            |      | ns   |

| t <sub>EABDATAH</sub>   | 0.0      |          | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWESU</sub>    | 5.5      |          | 5.5            |      | 5.8            |      | ns   |

| t <sub>EABWEH</sub>     | 0.0      |          | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWDSU</sub>    | 5.5      |          | 5.5            |      | 5.8            |      | ns   |

| t <sub>EABWDH</sub>     | 0.0      |          | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWASU</sub>    | 2.1      |          | 2.1            |      | 2.7            |      | ns   |

| t <sub>EABWAH</sub>     | 0.0      |          | 0.0            |      | 0.0            |      | ns   |

| t <sub>EABWO</sub>      |          | 9.5      |                | 9.5  |                | 11.8 | ns   |

| Table 72. EPI       | F10K50V D | evice IOE T | iming Mic | roparamet | ers No         | ote (1) |                |     |      |

|---------------------|-----------|-------------|-----------|-----------|----------------|---------|----------------|-----|------|

| Symbol              | -1 Spec   | ed Grade    | -2 Spee   | d Grade   | -3 Speed Grade |         | -4 Speed Grade |     | Unit |

|                     | Min       | Max         | Min       | Max       | Min            | Max     | Min            | Max |      |

| $t_{IOD}$           |           | 1.2         |           | 1.6       |                | 1.9     |                | 2.1 | ns   |

| $t_{IOC}$           |           | 0.3         |           | 0.4       |                | 0.5     |                | 0.5 | ns   |

| t <sub>IOCO</sub>   |           | 0.3         |           | 0.3       |                | 0.4     |                | 0.4 | ns   |

| t <sub>IOCOMB</sub> |           | 0.0         |           | 0.0       |                | 0.0     |                | 0.0 | ns   |

| $t_{IOSU}$          | 2.8       |             | 2.8       |           | 3.4            |         | 3.9            |     | ns   |

| t <sub>IOH</sub>    | 0.7       |             | 0.8       |           | 1.0            |         | 1.4            |     | ns   |

| t <sub>IOCLR</sub>  |           | 0.5         |           | 0.6       |                | 0.7     |                | 0.7 | ns   |

| t <sub>OD1</sub>    |           | 2.8         |           | 3.2       |                | 3.9     |                | 4.7 | ns   |

| t <sub>OD2</sub>    |           | _           |           | _         |                | _       |                | _   | ns   |

| t <sub>OD3</sub>    |           | 6.5         |           | 6.9       |                | 7.6     |                | 8.4 | ns   |

| $t_{XZ}$            |           | 2.8         |           | 3.1       |                | 3.8     |                | 4.6 | ns   |

| $t_{ZX1}$           |           | 2.8         |           | 3.1       |                | 3.8     |                | 4.6 | ns   |

| $t_{ZX2}$           |           | _           |           | _         |                | _       |                | _   | ns   |

| $t_{ZX3}$           |           | 6.5         |           | 6.8       |                | 7.5     |                | 8.3 | ns   |

| t <sub>INREG</sub>  |           | 5.0         |           | 5.7       |                | 7.0     |                | 9.0 | ns   |

| t <sub>IOFD</sub>   |           | 1.5         |           | 1.9       |                | 2.3     |                | 2.7 | ns   |

| t <sub>INCOMB</sub> |           | 1.5         |           | 1.9       |                | 2.3     |                | 2.7 | ns   |

| Symbol                  | -2 Spee | -2 Speed Grade |      | ed Grade | -4 Spec | Unit |    |

|-------------------------|---------|----------------|------|----------|---------|------|----|

|                         | Min     | Max            | Min  | Max      | Min     | Max  |    |

| t <sub>EABAA</sub>      |         | 11.2           |      | 14.2     |         | 14.2 | ns |

| t <sub>EABRCCOMB</sub>  | 11.1    |                | 14.2 |          | 14.2    |      | ns |

| t <sub>EABRCREG</sub>   | 8.5     |                | 10.8 |          | 10.8    |      | ns |

| t <sub>EABWP</sub>      | 3.7     |                | 4.7  |          | 4.7     |      | ns |

| t <sub>EABWCCOMB</sub>  | 7.6     |                | 9.7  |          | 9.7     |      | ns |

| t <sub>EABWCREG</sub>   | 14.0    |                | 17.8 |          | 17.8    |      | ns |

| t <sub>EABDD</sub>      |         | 11.1           |      | 14.2     |         | 14.2 | ns |

| t <sub>EABDATA</sub> CO |         | 3.6            |      | 4.6      |         | 4.6  | ns |

| t <sub>EABDATASU</sub>  | 4.4     |                | 5.6  |          | 5.6     |      | ns |

| t <sub>EABDATAH</sub>   | 0.0     |                | 0.0  |          | 0.0     |      | ns |

| t <sub>EABWESU</sub>    | 4.4     |                | 5.6  |          | 5.6     |      | ns |

| t <sub>EABWEH</sub>     | 0.0     |                | 0.0  |          | 0.0     |      | ns |

| t <sub>EABWDSU</sub>    | 4.6     |                | 5.9  |          | 5.9     |      | ns |

| t <sub>EABWDH</sub>     | 0.0     |                | 0.0  |          | 0.0     |      | ns |

| t <sub>EABWASU</sub>    | 3.9     |                | 5.0  |          | 5.0     |      | ns |

| t <sub>EABWAH</sub>     | 0.0     |                | 0.0  |          | 0.0     |      | ns |

| t <sub>EABWO</sub>      |         | 11.1           |      | 14.2     |         | 14.2 | ns |

### Notes to tables:

- (1) All timing parameters are described in Tables 32 through 38 in this data sheet.

- (2) Using an LE to register the signal may provide a lower setup time.

- (3) This parameter is specified by characterization.

Tables 92 through 98 show EPF10K30A device internal and external timing parameters.

| Table 92. EPF10     | K30A Device | LE Timing M    | icroparamet | ers Note       | (1) |                |    |  |

|---------------------|-------------|----------------|-------------|----------------|-----|----------------|----|--|

| Symbol              | -1 Spee     | -1 Speed Grade |             | -2 Speed Grade |     | -3 Speed Grade |    |  |

|                     | Min         | Max            | Min         | Max            | Min | Max            |    |  |

| $t_{LUT}$           |             | 0.8            |             | 1.1            |     | 1.5            | ns |  |

| t <sub>CLUT</sub>   |             | 0.6            |             | 0.7            |     | 1.0            | ns |  |

| t <sub>RLUT</sub>   |             | 1.2            |             | 1.5            |     | 2.0            | ns |  |

| t <sub>PACKED</sub> |             | 0.6            |             | 0.6            |     | 1.0            | ns |  |

| t <sub>EN</sub>     |             | 1.3            |             | 1.5            |     | 2.0            | ns |  |

| t <sub>CICO</sub>   |             | 0.2            |             | 0.3            |     | 0.4            | ns |  |

| t <sub>CGEN</sub>   |             | 0.8            |             | 1.0            |     | 1.3            | ns |  |

| t <sub>CGENR</sub>  |             | 0.6            |             | 0.8            |     | 1.0            | ns |  |

| t <sub>CASC</sub>   |             | 0.9            |             | 1.1            |     | 1.4            | ns |  |

| $t_{C}$             |             | 1.1            |             | 1.3            |     | 1.7            | ns |  |

| $t_{CO}$            |             | 0.4            |             | 0.6            |     | 0.7            | ns |  |

| $t_{COMB}$          |             | 0.6            |             | 0.7            |     | 0.9            | ns |  |

| $t_{SU}$            | 0.9         |                | 0.9         |                | 1.4 |                | ns |  |

| $t_H$               | 1.1         |                | 1.3         |                | 1.7 |                | ns |  |

| t <sub>PRE</sub>    |             | 0.5            |             | 0.6            |     | 0.8            | ns |  |

| t <sub>CLR</sub>    |             | 0.5            |             | 0.6            |     | 0.8            | ns |  |

| t <sub>CH</sub>     | 3.0         |                | 3.5         |                | 4.0 |                | ns |  |

| $t_{CL}$            | 3.0         |                | 3.5         |                | 4.0 |                | ns |  |

| Symbol              | -1 Spee | d Grade | rade -2 Speed Grade |     | -3 Spee | d Grade | Unit |

|---------------------|---------|---------|---------------------|-----|---------|---------|------|

|                     | Min     | Max     | Min                 | Max | Min     | Max     |      |

| $t_{IOD}$           |         | 2.2     |                     | 2.6 |         | 3.4     | ns   |

| t <sub>IOC</sub>    |         | 0.3     |                     | 0.3 |         | 0.5     | ns   |

| t <sub>IOCO</sub>   |         | 0.2     |                     | 0.2 |         | 0.3     | ns   |

| t <sub>IOCOMB</sub> |         | 0.5     |                     | 0.6 |         | 0.8     | ns   |

| t <sub>IOSU</sub>   | 1.4     |         | 1.7                 |     | 2.2     |         | ns   |

| Symbol              | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | Unit |    |

|---------------------|----------------|-----|---------|---------|---------|------|----|

|                     | Min            | Max | Min     | Max     | Min     | Max  |    |

| $t_{IOD}$           |                | 2.5 |         | 2.9     |         | 3.4  | ns |

| $t_{IOC}$           |                | 0.3 |         | 0.3     |         | 0.4  | ns |

| $t_{IOCO}$          |                | 0.2 |         | 0.2     |         | 0.3  | ns |

| $t_{IOCOMB}$        |                | 0.5 |         | 0.6     |         | 0.7  | ns |

| $t_{IOSU}$          | 1.3            |     | 1.7     |         | 1.8     |      | ns |

| $t_{IOH}$           | 0.2            |     | 0.2     |         | 0.3     |      | ns |

| $t_{IOCLR}$         |                | 1.0 |         | 1.2     |         | 1.4  | ns |

| $t_{OD1}$           |                | 2.2 |         | 2.6     |         | 3.0  | ns |

| $t_{OD2}$           |                | 4.5 |         | 5.3     |         | 6.1  | ns |

| t <sub>OD3</sub>    |                | 6.8 |         | 7.9     |         | 9.3  | ns |

| $t_{XZ}$            |                | 2.7 |         | 3.1     |         | 3.7  | ns |

| t <sub>ZX1</sub>    |                | 2.7 |         | 3.1     |         | 3.7  | ns |

| $t_{ZX2}$           |                | 5.0 |         | 5.8     |         | 6.8  | ns |

| $t_{ZX3}$           |                | 7.3 |         | 8.4     |         | 10.0 | ns |

| t <sub>INREG</sub>  |                | 5.3 |         | 6.1     |         | 7.2  | ns |

| t <sub>IOFD</sub>   |                | 4.7 |         | 5.5     |         | 6.4  | ns |

| t <sub>INCOMB</sub> |                | 4.7 |         | 5.5     |         | 6.4  | ns |

| Symbol                   | -1 Spee | d Grade | -2 Speed Grade |     | -3 Spee | d Grade | Unit |

|--------------------------|---------|---------|----------------|-----|---------|---------|------|

|                          | Min     | Max     | Min            | Max | Min     | Max     |      |

| t <sub>DIN2IOE</sub>     |         | 4.8     |                | 5.4 |         | 6.0     | ns   |

| t <sub>DIN2LE</sub>      |         | 2.0     |                | 2.4 |         | 2.7     | ns   |

| t <sub>DIN2DATA</sub>    |         | 2.4     |                | 2.7 |         | 2.9     | ns   |

| t <sub>DCLK2IOE</sub>    |         | 2.6     |                | 3.0 |         | 3.5     | ns   |

| t <sub>DCLK2LE</sub>     |         | 2.0     |                | 2.4 |         | 2.7     | ns   |

| t <sub>SAMELAB</sub>     |         | 0.1     |                | 0.1 |         | 0.1     | ns   |

| t <sub>SAMEROW</sub>     |         | 1.5     |                | 1.7 |         | 1.9     | ns   |

| t <sub>SAME</sub> COLUMN |         | 5.5     |                | 6.5 |         | 7.4     | ns   |

| t <sub>DIFFROW</sub>     |         | 7.0     |                | 8.2 |         | 9.3     | ns   |

| t <sub>TWOROWS</sub>     |         | 8.5     |                | 9.9 |         | 11.2    | ns   |

| t <sub>LEPERIPH</sub>    |         | 3.9     |                | 4.2 |         | 4.5     | ns   |

| t <sub>LABCARRY</sub>    |         | 0.2     |                | 0.2 |         | 0.3     | ns   |

| t <sub>LABCASC</sub>     |         | 0.4     |                | 0.5 |         | 0.6     | ns   |

| Table 104. EPF1            | OK100A Devi | ce External T | iming Param    | eters Not | e (1)   |         |      |

|----------------------------|-------------|---------------|----------------|-----------|---------|---------|------|

| Symbol                     | -1 Spee     | ed Grade      | -2 Speed Grade |           | -3 Spee | d Grade | Unit |

|                            | Min         | Max           | Min            | Max       | Min     | Max     |      |

| t <sub>DRR</sub>           |             | 12.5          |                | 14.5      |         | 17.0    | ns   |

| t <sub>INSU</sub> (2), (3) | 3.7         |               | 4.5            |           | 5.1     |         | ns   |

| t <sub>INH</sub> (3)       | 0.0         |               | 0.0            |           | 0.0     |         | ns   |

| t <sub>оитсо</sub> (3)     | 2.0         | 5.3           | 2.0            | 6.1       | 2.0     | 7.2     | ns   |

| Table 105. EPF10K10    | Table 105. EPF10K100A Device External Bidirectional Timing Parameters       Note (1) |          |        |          |         |          |      |  |  |  |  |

|------------------------|--------------------------------------------------------------------------------------|----------|--------|----------|---------|----------|------|--|--|--|--|

| Symbol                 | -1 Spee                                                                              | ed Grade | -2 Spe | ed Grade | -3 Spec | ed Grade | Unit |  |  |  |  |

|                        | Min                                                                                  | Max      | Min    | Max      | Min     | Max      |      |  |  |  |  |

| t <sub>INSUBIDIR</sub> | 4.9                                                                                  |          | 5.8    |          | 6.8     |          | ns   |  |  |  |  |

| t <sub>INHBIDIR</sub>  | 0.0                                                                                  |          | 0.0    |          | 0.0     |          | ns   |  |  |  |  |

| toutcobidir            | 2.0                                                                                  | 5.3      | 2.0    | 6.1      | 2.0     | 7.2      | ns   |  |  |  |  |

| t <sub>XZBIDIR</sub>   |                                                                                      | 7.4      |        | 8.6      |         | 10.1     | ns   |  |  |  |  |

| t <sub>ZXBIDIR</sub>   |                                                                                      | 7.4      |        | 8.6      |         | 10.1     | ns   |  |  |  |  |

| Symbol                 | -1 Speed Grade |     | -2 Spee | d Grade | -3 Spee | Unit |    |

|------------------------|----------------|-----|---------|---------|---------|------|----|

|                        | Min            | Max | Min     | Max     | Min     | Max  |    |

| t <sub>EABDATA1</sub>  |                | 1.3 |         | 1.5     |         | 1.7  | ns |

| t <sub>EABDATA2</sub>  |                | 1.3 |         | 1.5     |         | 1.7  | ns |

| t <sub>EABWE1</sub>    |                | 0.9 |         | 1.1     |         | 1.3  | ns |

| t <sub>EABWE2</sub>    |                | 5.0 |         | 5.7     |         | 6.7  | ns |

| t <sub>EABCLK</sub>    |                | 0.6 |         | 0.7     |         | 0.8  | ns |

| t <sub>EABCO</sub>     |                | 0.0 |         | 0.0     |         | 0.0  | ns |

| t <sub>EABBYPASS</sub> |                | 0.1 |         | 0.1     |         | 0.2  | ns |

| t <sub>EABSU</sub>     | 3.8            |     | 4.3     |         | 5.0     |      | ns |

| t <sub>EABH</sub>      | 0.7            |     | 0.8     |         | 0.9     |      | ns |

| $t_{AA}$               |                | 4.5 |         | 5.0     |         | 5.9  | ns |

| $t_{WP}$               | 5.6            |     | 6.4     |         | 7.5     |      | ns |

| t <sub>WDSU</sub>      | 1.3            |     | 1.4     |         | 1.7     |      | ns |

| t <sub>WDH</sub>       | 0.1            |     | 0.1     |         | 0.2     |      | ns |

| t <sub>WASU</sub>      | 0.1            |     | 0.1     |         | 0.2     |      | ns |

| t <sub>WAH</sub>       | 0.1            |     | 0.1     |         | 0.2     |      | ns |

| $t_{WO}$               |                | 4.1 |         | 4.6     |         | 5.5  | ns |

| t <sub>DD</sub>        |                | 4.1 |         | 4.6     |         | 5.5  | ns |

| t <sub>EABOUT</sub>    |                | 0.1 |         | 0.1     |         | 0.2  | ns |

| t <sub>EABCH</sub>     | 2.5            |     | 3.0     |         | 3.5     |      | ns |

| t <sub>EABCL</sub>     | 5.6            |     | 6.4     |         | 7.5     |      | ns |

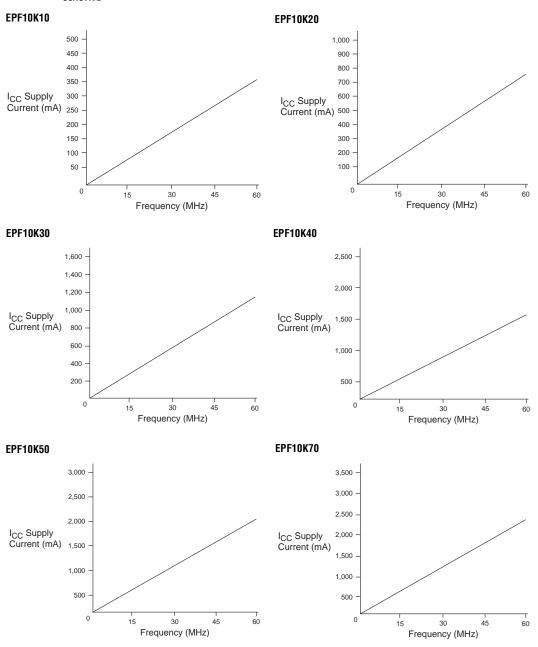

Figure 32. I<sub>CCACTIVE</sub> vs. Operating Frequency (Part 1 of 3)

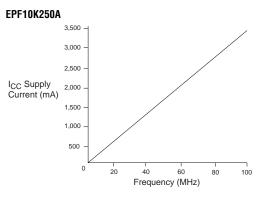

Figure 32. I<sub>CCACTIVE</sub> vs. Operating Frequency (Part 3 of 3)

# Configuration & Operation

The FLEX 10K architecture supports several configuration schemes. This section summarizes the device operating modes and available device configuration schemes.

See *Application Note 116 (Configuring APEX 20K, FLEX 10K & FLEX 6000 Devices)* for detailed descriptions of device configuration options, device configuration pins, and for information on configuring FLEX 10K devices, including sample schematics, timing diagrams, and configuration parameters.

## **Operating Modes**

The FLEX 10K architecture uses SRAM configuration elements that require configuration data to be loaded every time the circuit powers up. The process of physically loading the SRAM data into the device is called *configuration*. Before configuration, as VCC rises, the device initiates a Power-On Reset (POR). This POR event clears the device and prepares it for configuration. The FLEX 10K POR time does not exceed 50  $\mu s$ .

During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power-up, and before and during configuration. Together, the configuration and initialization processes are called *command mode*; normal device operation is called *user mode*.