Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                   |                                                                               |

|--------------------------|-------------------------------------------------------------------------------|

| oduct Status             | Obsolete                                                                      |

| ore Processor            | dsPIC                                                                         |

| ore Size                 | 16-Bit                                                                        |

| peed                     | 20 MIPS                                                                       |

| onnectivity              | CANbus, I <sup>2</sup> C, SPI, UART/USART                                     |

| eripherals               | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                    |

| umber of I/O             | 52                                                                            |

| ogram Memory Size        | 132KB (44K x 24)                                                              |

| ogram Memory Type        | FLASH                                                                         |

| EPROM Size               | 2K x 8                                                                        |

| AM Size                  | 6K x 8                                                                        |

| ltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| ata Converters           | A/D 16x12b                                                                    |

| cillator Type            | Internal                                                                      |

| perating Temperature     | -40°C ~ 125°C (TA)                                                            |

| ounting Type             | Surface Mount                                                                 |

| ickage / Case            | 64-TQFP                                                                       |

| ipplier Device Package   | 64-TQFP (14x14)                                                               |

| rchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f6011-20e-pf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC30F6011/6012/6013/6014 High-Performance Digital Signal Controllers

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "dsPIC30F/33F Programmer's Reference Manual" (DS70157).

### **High-Performance Modified RISC CPU:**

- · Modified Harvard architecture

- · C compiler optimized instruction set architecture

- Flexible addressing modes

- 83 base instructions

- · 24-bit wide instructions, 16-bit wide data path

- Up to 144 Kbytes on-chip Flash program space

- Up to 48K instruction words

- · Up to 8 Kbytes of on-chip data RAM

- Up to 4 Kbytes of nonvolatile data EEPROM

- 16 x 16-bit working register array

- Up to 30 MIPS operation:

- DC to 40 MHz external clock input

- 4 MHz-10 MHz oscillator input with PLL active (4x, 8x, 16x)

- Up to 41 interrupt sources:

- 8 user-selectable priority levels

- 5 external interrupt sources

- 4 processor traps

#### **DSP Features:**

- · Dual data fetch

- Modulo and Bit-Reversed modes

- Two 40-bit wide accumulators with optional saturation logic

- 17-bit x 17-bit single cycle hardware fractional/ integer multiplier

- · All DSP instructions are single cycle:

- Multiply-Accumulate (MAC) operation

- Single-cycle ±16 shift

### **Peripheral Features:**

- High current sink/source I/O pins: 25 mA/25 mA

- Five 16-bit timers/counters; optionally pair up 16-bit timers into 32-bit timer modules

- 16-bit Capture input functions

- 16-bit Compare/PWM output functions

- Data Converter Interface (DCI) supports common audio Codec protocols, including I<sup>2</sup>S and AC'97

- 3-wire SPI modules (supports 4 Frame modes)

- I<sup>2</sup>C<sup>TM</sup> module supports Multi-Master/Slave mode and 7-bit/10-bit addressing

- Two addressable UART modules with FIFO buffers

- Two CAN bus modules compliant with CAN 2.0B standard

### **Analog Features:**

- 12-bit Analog-to-Digital Converter (ADC) with:

- 200 ksps conversion rate

- Up to 16 input channels

- Conversion available during Sleep and Idle

- Programmable Low-Voltage Detection (PLVD)

- · Programmable Brown-out Reset

### **Special Microcontroller Features:**

- · Enhanced Flash program memory:

- 10,000 erase/write cycle (min.) for industrial temperature range, 100K (typical)

- Data EEPROM memory:

- 100,000 erase/write cycle (min.) for industrial temperature range, 1M (typical)

- Self-reprogrammable under software control

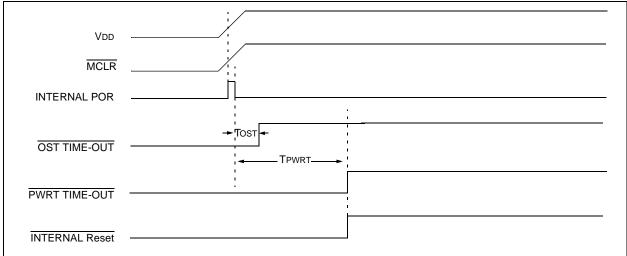

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Flexible Watchdog Timer (WDT) with on-chip low power RC oscillator for reliable operation

### **Special Microcontroller Features (Cont.):**

- Fail-Safe Clock Monitor operation:

- Detects clock failure and switches to on-chip low power RC oscillator

- Programmable code protection

- In-Circuit Serial Programming™ (ICSP™)

- Selectable Power Management modes:

- Sleep, Idle and Alternate Clock modes

### **CMOS Technology:**

- Low-power, high-speed Flash technology

- Wide operating voltage range (2.5V to 5.5V)

- Industrial and Extended temperature ranges

- Low power consumption

#### dsPIC30F6011/6012/6013/6014 Controller Families

| Davidson     | D:   | Progr | am Memory    | SRAM  | EEPROM | Timer  | Input | Output          | Codec                   | A/D12-bit | RT | -  | M                | z  |

|--------------|------|-------|--------------|-------|--------|--------|-------|-----------------|-------------------------|-----------|----|----|------------------|----|

| Device       | Pins | Bytes | Instructions | Bytes | Bytes  | 16-bit | Сар   | Comp/Std<br>PWM | Interface               | 200 ksps  | NA | SP | l <sup>2</sup> C | CA |

| dsPIC30F6011 | 64   | 132K  | 44K          | 6144  | 2048   | 5      | 8     | 8               | _                       | 16 ch     | 2  | 2  | 1                | 2  |

| dsPIC30F6012 | 64   | 144K  | 48K          | 8192  | 4096   | 5      | 8     | 8               | AC'97, I <sup>2</sup> S | 16 ch     | 2  | 2  | 1                | 2  |

| dsPIC30F6013 | 80   | 132K  | 44K          | 6144  | 2048   | 5      | 8     | 8               | _                       | 16 ch     | 2  | 2  | 1                | 2  |

| dsPIC30F6014 | 80   | 144K  | 48K          | 8192  | 4096   | 5      | 8     | 8               | AC'97, I <sup>2</sup> S | 16 ch     | 2  | 2  | 1                | 2  |

NOTES:

| TABLE 3-3: | CORE REGISTER MAP | (CONTINUED) |

|------------|-------------------|-------------|

|------------|-------------------|-------------|

| SFR Name | Address<br>(Home) | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8   | Bit 7   | Bit 6   | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset State         |

|----------|-------------------|--------|--------|--------|--------|--------|--------|--------|---------|---------|---------|--------|--------|-------|-------|-------|-------|---------------------|

| SR       | 0042              | OA     | ОВ     | SA     | SB     | OAB    | SAB    | DA     | DC      | IPL2    | IPL1    | IPL0   | RA     | N     | OV    | Z     | С     | 0000 0000 0000 0000 |

| CORCON   | 0044              | _      | _      | _      | US     | EDT    | DL2    | DL1    | DL0     | SATA    | SATB    | SATDW  | ACCSAT | IPL3  | PSV   | RND   | IF    | 0000 0000 0010 0000 |

| MODCON   | 0046              | XMODEN | YMODEN | _      |        |        | BWM    | l<3:0> |         |         | YWI     | M<3:0> |        |       | XWM<  | 3:0>  |       | 0000 0000 0000 0000 |

| XMODSRT  | 0048              |        |        |        |        |        |        | XS     | S<15:1> |         |         |        |        |       |       |       | 0     | uuuu uuuu uuu0      |

| XMODEND  | 004A              |        |        |        |        |        |        | XE     | <15:1>  |         |         |        |        |       |       |       | 1     | uuuu uuuu uuu1      |

| YMODSRT  | 004C              |        |        |        |        |        |        | YS     | S<15:1> |         |         |        |        |       |       |       | 0     | uuuu uuuu uuu0      |

| YMODEND  | 004E              |        |        |        |        |        |        | YE     | <15:1>  |         |         |        |        |       |       |       | 1     | uuuu uuuu uuu1      |

| XBREV    | 0050              | BREN   |        |        |        |        |        |        | XI      | 3<14:0> |         |        |        |       |       |       |       | uuuu uuuu uuuu uuuu |

| DISICNT  | 0052              | _      | _      |        |        |        |        |        |         | DISICN  | Γ<13:0> |        |        |       |       |       |       | 0000 0000 0000 0000 |

**Legend:** u = uninitialized bit

**Note:** Refer to "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

#### 7.0 DATA EEPROM MEMORY

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "dsPIC30F/33F Programmer's Reference Manual" (DS70157).

The Data EEPROM Memory is readable and writable during normal operation over the entire VDD range. The data EEPROM memory is directly mapped in the program memory address space.

The four SFRs used to read and write the program Flash memory are used to access data EEPROM memory, as well. As described in **Section 6.5 "Control Registers"**, these registers are:

- NVMCON

- NVMADR

- NVMADRU

- NVMKEY

The EEPROM data memory allows read and write of single words and 16-word blocks. When interfacing to data memory, NVMADR in conjunction with the NVMADRU register are used to address the EEPROM location being accessed. TBLRDL and TBLWTL instructions are used to read and write data EEPROM. The dsPIC30F devices have up to 8 Kbytes (4K words) of data EEPROM with an address range from 0x7FF000 to 0x7FFFFE.

A word write operation should be preceded by an erase of the corresponding memory location(s). The write typically requires 2 ms to complete but the write time will vary with voltage and temperature.

A program or erase operation on the data EEPROM does not stop the instruction flow. The user is responsible for waiting for the appropriate duration of time before initiating another data EEPROM write/erase operation. Attempting to read the data EEPROM while a programming or erase operation is in progress results in unspecified data.

Control bit WR initiates write operations similar to program Flash writes. This bit cannot be cleared, only set, in software. They are cleared in hardware at the completion of the write operation. The inability to clear the WR bit in software prevents the accidental or premature termination of a write operation.

The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a MCLR Reset or a WDT Time-out Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and rewrite the location. The address register NVMADR remains unchanged.

Note: Interrupt flag bit NVMIF in the IFS0 register is set when write is complete. It must be cleared in software.

### 7.1 Reading the Data EEPROM

A TBLRD instruction reads a word at the current program word address. This example uses W0 as a pointer to data EEPROM. The result is placed in register W4 as shown in Example 7-1.

#### **EXAMPLE 7-1:** DATA EEPROM READ

MOV #LOW\_ADDR\_WORD,W0 ; Init Pointer

MOV #HIGH\_ADDR\_WORD,W1

MOV W1,TBLPAG

TBLRDL [ W0 ], W4 ; read data EEPROM

### 7.3 Writing to the Data EEPROM

To write an EEPROM data location, the following sequence must be followed:

- 1. Erase data EEPROM word.

- Select word, data EEPROM erase, and set WREN bit in NVMCON register.

- Write address of word to be erased into NVMADR.

- c) Enable NVM interrupt (optional).

- d) Write '55' to NVMKEY.

- e) Write 'AA' to NVMKEY.

- f) Set the WR bit. This will begin erase cycle.

- g) Either poll NVMIF bit or wait for NVMIF interrupt.

- h) The WR bit is cleared when the erase cycle ends.

- Write data word into data EEPROM write latches.

- 3. Program 1 data word into data EEPROM.

- Select word, data EEPROM program, and set WREN bit in NVMCON register.

- b) Enable NVM write done interrupt (optional).

- c) Write '55' to NVMKEY.

- d) Write 'AA' to NVMKEY.

- e) Set the WR bit. This will begin program cycle.

- f) Either poll NVMIF bit or wait for NVM interrupt.

- g) The WR bit is cleared when the write cycle ends.

The write will not initiate if the above sequence is not exactly followed (write  $0 \times 55$  to NVMKEY, write  $0 \times AA$  to NVMCON, then set WR bit) for each word. It is strongly recommended that interrupts be disabled during this code segment.

Additionally, the WREN bit in NVMCON must be set to enable writes. This mechanism prevents accidental writes to data EEPROM due to unexpected code execution. The WREN bit should be kept clear at all times except when updating the EEPROM. The WREN bit is not cleared by hardware.

After a write sequence has been initiated, clearing the WREN bit will not affect the current write cycle. The WR bit will be inhibited from being set unless the WREN bit is set. The WREN bit must be set on a previous instruction. Both WR and WREN cannot be set with the same instruction.

At the completion of the write cycle, the WR bit is cleared in hardware and the Non-Volatile Memory Write Complete Interrupt Flag bit (NVMIF) is set. The user may either enable this interrupt or poll this bit. NVMIF must be cleared by software.

# 7.3.1 WRITING A WORD OF DATA EEPROM

Once the user has erased the word to be programmed, then a table write instruction is used to write one write latch, as shown in Example 7-4.

#### **EXAMPLE 7-4:** DATA EEPROM WORD WRITE

```

; Point to data memory

MOV

#LOW_ADDR_WORD,W0

; Init pointer

#HIGH_ADDR_WORD,W1

MOV

MOV

W1 TBLPAG

MOV

#LOW(WORD), W2

: Get data

TBLWTL

W2 [ W0]

; Write data

; The NVMADR captures last table access address

; Select data EEPROM for 1 word op

#0x4004,W0

MOV

WO NVMCON

MOV

; Operate key to allow write operation

; Block all interrupts with priority <7 for

DISI

#5

; next 5 instructions

MOV

#0x55,W0

MOV

WO NVMKEY

; Write the 0x55 key

MOV

#0xAA,W1

W1 NVMKEY

MOV

; Write the OxAA key

BSET

NVMCON, #WR

; Initiate program sequence

NOP

; Write cycle will complete in 2mS. CPU is not stalled for the Data Write Cycle

; User can poll WR bit, use NVMIF or Timer IRQ to determine write complete

```

### 9.4 Timer Interrupt

The 16-bit timer has the ability to generate an interrupt on period match. When the timer count matches the Period register, the T1IF bit is asserted and an interrupt will be generated if enabled. The T1IF bit must be cleared in software. The timer interrupt flag, T1IF, is located in the IFS0 Control register in the interrupt controller.

When the Gated Time Accumulation mode is enabled, an interrupt will also be generated on the falling edge of the gate signal (at the end of the accumulation cycle).

Enabling an interrupt is accomplished via the respective timer interrupt enable bit, T1IE. The timer interrupt enable bit is located in the IEC0 Control register in the interrupt controller.

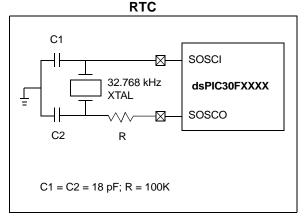

#### 9.5 Real-Time Clock

Timer1, when operating in Real-Time Clock (RTC) mode, provides time of day and event time-stamping capabilities. Key operational features of the RTC are:

- · Operation from 32 kHz LP oscillator

- · 8-bit prescaler

- · Low power

- Real-Time Clock interrupts

These Operating modes are determined by setting the appropriate bit(s) in the T1CON Control register.

FIGURE 9-2: RECOMMENDED COMPONENTS FOR TIMER1 LP OSCILLATOR

#### 9.5.1 RTC OSCILLATOR OPERATION

When the TON = 1, TCS = 1 and TGATE = 0, the timer increments on the rising edge of the 32 kHz LP oscillator output signal, up to the value specified in the Period register and is then Reset to  $^{\circ}$ 0'.

The TSYNC bit must be asserted to a logic '0' (Asynchronous mode) for correct operation.

Enabling LPOSCEN (OSCCON<1>) will disable the normal Timer and Counter modes and enable a timer carry-out wake-up event.

When the CPU enters Sleep mode, the RTC will continue to operate provided the 32 kHz external crystal oscillator is active and the control bits have not been changed. The TSIDL bit should be cleared to '0' in order for RTC to continue operation in Idle mode.

#### 9.5.2 RTC INTERRUPTS

When an interrupt event occurs, the respective interrupt flag, T1IF, is asserted and an interrupt will be generated if enabled. The T1IF bit must be cleared in software. The respective Timer interrupt flag, T1IF, is located in the IFSO Status register in the interrupt controller.

Enabling an interrupt is accomplished via the respective timer interrupt enable bit, T1IE. The timer interrupt enable bit is located in the IEC0 Control register in the interrupt controller.

|          | •     |        |        |        |        |        |        |          |           |                |           |              |        |       |       |       |       |                     |

|----------|-------|--------|--------|--------|--------|--------|--------|----------|-----------|----------------|-----------|--------------|--------|-------|-------|-------|-------|---------------------|

| SFR Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9    | Bit 8     | Bit 7          | Bit 6     | Bit 5        | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset State         |

| TMR2     | 0106  |        |        |        |        |        |        |          | Tir       | mer2 Regist    | er        |              |        |       |       |       |       | uuuu uuuu uuuu uuuu |

| TMR3HLD  | 0108  |        |        |        |        |        | Timer  | 3 Holdin | g Registe | er (for 32-bit | timer ope | rations only | /)     |       |       |       |       | uuuu uuuu uuuu uuuu |

| TMR3     | 010A  |        |        |        |        |        |        |          | Tir       | mer3 Regist    | er        |              |        |       |       |       |       | uuuu uuuu uuuu uuuu |

| PR2      | 010C  |        |        |        |        |        |        |          | Pe        | riod Registe   | r 2       |              |        |       |       |       |       | 1111 1111 1111 1111 |

| PR3      | 010E  |        |        |        |        |        |        |          | Pe        | riod Registe   | r 3       |              |        |       |       |       |       | 1111 1111 1111 1111 |

| T2CON    | 0110  | TON    | _      | TSIDL  | _      | ı      | _      | ı        | _         | _              | TGATE     | TCKPS1       | TCKPS0 | T32   | _     | TCS   | _     | 0000 0000 0000 0000 |

| T3CON    | 0112  | TON    | _      | TSIDL  | _      |        | _      | ı        | _         | _              | TGATE     | TCKPS1       | TCKPS0 | -     | _     | TCS   | _     | 0000 0000 0000 0000 |

|          | •     |        | 11.4   |        | •      |        |        |          | •         |                |           |              |        |       |       |       |       | •                   |

**Legend:** u = uninitialized bit

**Note:** Refer to dsPIC30F Family Reference Manual (DS70046) for descriptions of register bit fields.

NOTES:

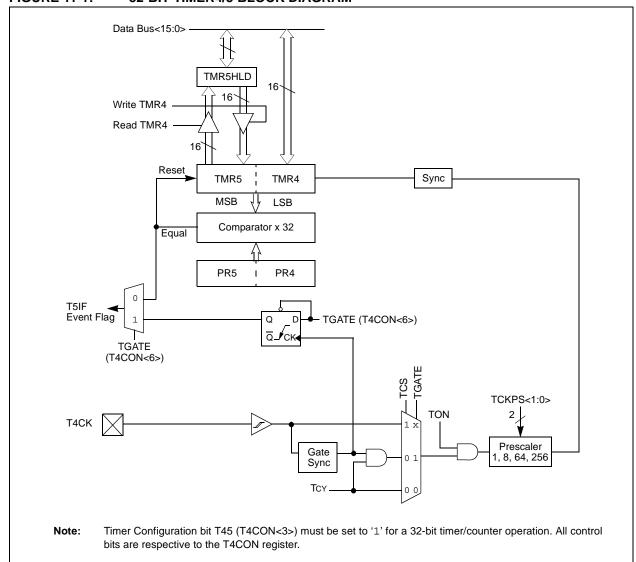

### 11.0 TIMER4/5 MODULE

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the second 32-bit General Purpose Timer module (Timer4/5) and associated operational modes. Figure 11-1 depicts the simplified block diagram of the 32-bit Timer4/5 module. Figure 11-2 and Figure 11-3 show Timer4/5 configured as two independent 16-bit timers, Timer4 and Timer5, respectively.

The Timer4/5 module is similar in operation to the Timer2/3 module. However, there are some differences which are as follows:

- The Timer4/5 module does not support the ADC event trigger feature

- Timer4/5 can not be utilized by other peripheral modules, such as input capture and output compare

The operating modes of the Timer4/5 module are determined by setting the appropriate bit(s) in the 16-bit T4CON and T5CON SFRs.

For 32-bit timer/counter operation, Timer4 is the Isw and Timer5 is the msw of the 32-bit timer.

Note: For 32-bit timer operation, T5CON control bits are ignored. Only T4CON control bits are used for setup and control. Timer4 clock and gate inputs are utilized for the 32-bit timer module but an interrupt is generated with the Timer5 interrupt flag (T5IF) and the interrupt is enabled with the

Timer5 interrupt enable bit (T5IE).

FIGURE 11-1: 32-BIT TIMER4/5 BLOCK DIAGRAM

### TABLE 11-1: TIMER4/5 REGISTER MAP

| SFR Name | Addr. | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8    | Bit 7         | Bit 6       | Bit 5        | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Reset State         |

|----------|-------|--------|--------|--------|--------|--------|--------|-----------|----------|---------------|-------------|--------------|--------|-------|-------|-------|-------|---------------------|

| TMR4     | 0114  |        |        |        |        |        |        |           | Tir      | ner 4 Regis   | ster        |              |        |       |       |       |       | uuuu uuuu uuuu uuuu |

| TMR5HLD  | 0116  |        |        |        |        |        | Time   | er 5 Hold | ding Reg | ister (for 32 | 2-bit opera | ations only) |        |       |       |       |       | uuuu uuuu uuuu uuuu |

| TMR5     | 0118  |        |        |        |        |        |        |           | Tir      | ner 5 Regis   | ster        |              |        |       |       |       |       | uuuu uuuu uuuu uuuu |

| PR4      | 011A  |        |        |        |        |        |        |           | Pe       | riod Registe  | er 4        |              |        |       |       |       |       | 1111 1111 1111 1111 |

| PR5      | 011C  |        |        |        |        |        |        |           | Pe       | riod Registe  | er 5        |              |        |       |       |       |       | 1111 1111 1111 1111 |

| T4CON    | 011E  | TON    | _      | TSIDL  | _      | _      | _      | _         | _        | _             | TGATE       | TCKPS1       | TCKPS0 | T45   | _     | TCS   | _     | 0000 0000 0000 0000 |

| T5CON    | 0120  | TON    | _      | TSIDL  | _      | _      | _      |           | _        | I             | TGATE       | TCKPS1       | TCKPS0 |       | _     | TCS   | _     | 0000 0000 0000 0000 |

**Legend:** u = uninitialized

Refer to "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields. Note:

NOTES:

#### 17.5.6 TRANSMIT INTERRUPTS

Transmit interrupts can be divided into 2 major groups, each including various conditions that generate interrupts:

#### • Transmit Interrupt:

At least one of the three transmit buffers is empty (not scheduled) and can be loaded to schedule a message for transmission. Reading the TXnIF flags will indicate which transmit buffer is available and caused the interrupt.

#### • Transmit Error Interrupts:

A transmission error interrupt will be indicated by the ERRIF flag. This flag shows that an error condition occurred. The source of the error can be determined by checking the error flags in the CAN Interrupt Status register, CilNTF. The flags in this register are related to receive and transmit errors.

- Transmitter Warning Interrupt:

The TXWAR bit indicates that the transmit error counter has reached the CPU warning limit of 96.

- Transmitter Error Passive:

The TXEP bit (CilNTF<12>) indicates that the transmit error counter has exceeded the error passive limit of 127 and the module has gone to error passive state.

- Bus Off:

The TXBO bit (CilNTF<13>) indicates that the transmit error counter has exceeded 255 and the module has gone to the bus off state.

### 17.6 Baud Rate Setting

All nodes on any particular CAN bus must have the same nominal bit rate. In order to set the baud rate, the following parameters have to be initialized:

- · Synchronization Jump Width

- · Baud Rate Prescaler

- · Phase Segments

- Length determination of Phase Segment 2

- Sample Point

- · Propagation Segment bits

#### 17.6.1 BIT TIMING

All controllers on the CAN bus must have the same baud rate and bit length. However, different controllers are not required to have the same master oscillator clock. At different clock frequencies of the individual controllers, the baud rate has to be adjusted by adjusting the number of time quanta in each segment.

The nominal bit time can be thought of as being divided into separate non-overlapping time segments. These segments are shown in Figure 17-2.

- Synchronization Segment (Sync Seg)

- Propagation Time Segment (Prop Seg)

- Phase Segment 1 (Phase1 Seg)

- Phase Segment 2 (Phase2 Seg)

The time segments and also the nominal bit time are made up of integer units of time called time quanta or Tq. By definition, the nominal bit time has a minimum of 8 Tq and a maximum of 25 Tq. Also, by definition, the minimum nominal bit time is 1  $\mu sec$  corresponding to a maximum bit rate of 1 MHz.

FIGURE 20-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

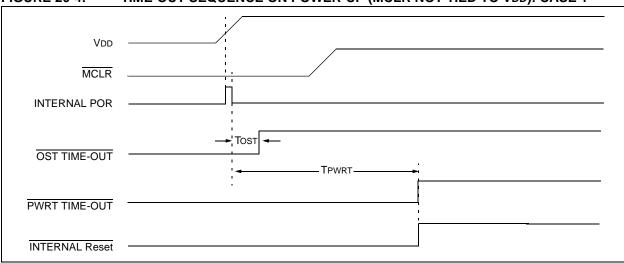

FIGURE 20-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

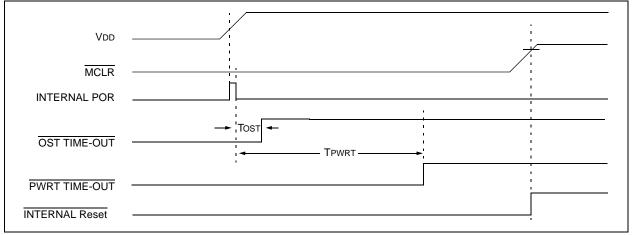

FIGURE 20-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

# 20.3.1.1 POR with Long Crystal Start-up Time (with FSCM Enabled)

The oscillator start-up circuitry is not linked to the POR circuitry. Some crystal circuits (especially low frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after the POR timer and the PWRT have expired:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used).

- The PLL has not achieved a LOCK (if PLL is used).

If the FSCM is enabled and one of the above conditions is true, then a clock failure trap will occur. The device will automatically switch to the FRC oscillator and the user can switch to the desired crystal oscillator in the trap ISR.

### 20.3.1.2 Operating without FSCM and PWRT

If the FSCM is disabled and the Power-up Timer (PWRT) is also disabled, then the device will exit rapidly from Reset on power-up. If the clock source is FRC, LPRC, EXTRC or EC, it will be active immediately.

If the FSCM is disabled and the system clock has not started, the device will be in a frozen state at the Reset vector until the system clock starts. From the user's perspective, the device will appear to be in Reset until a system clock is available.

# 20.3.2 BOR: PROGRAMMABLE BROWN-OUT RESET

The BOR (Brown-out Reset) module is based on an internal voltage reference circuit. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (i.e., missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

The BOR module allows selection of one of the following voltage trip points (see Table 23-11):

- 2.6V-2.71V

- 4.1V-4.4V

Note:

• 4.58V-4.73V

The BOR voltage trip points indicated here are nominal values provided for design guidance only. Refer to the Electrical Specifications in the specific device data sheet for BOR voltage limit specifications.

A BOR will generate a Reset pulse which will reset the device. The BOR will select the clock source based on the device Configuration bit values (FOS<1:0> and FPR<3:0>). Furthermore, if an Oscillator mode is selected, the BOR will activate the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, then the clock will be held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the POR time-out (TPOR) and the PWRT time-out (TPWRT) will be applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100  $\mu$ s is applied. The total delay in this case is (TPOR + TFSCM).

The BOR status bit (RCON<1>) will be set to indicate that a BOR has occurred. The BOR circuit, if enabled, will continue to operate while in Sleep or Idle modes and will reset the device should VDD fall below the BOR threshold voltage.

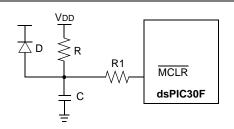

### FIGURE 20-6:

### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2: R should be suitably chosen so as to make sure that the voltage drop across R does not violate the device's electrical specifications.

- 3: R1 should be suitably chosen so as to limit any current flowing into MCLR from external capacitor C, in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD), or Electrical Overstress (EOS).

Note: Dedicated supervisory devices, such as the MCP1XX and MCP8XX, may also be used as an external Power-on Reset circuit.

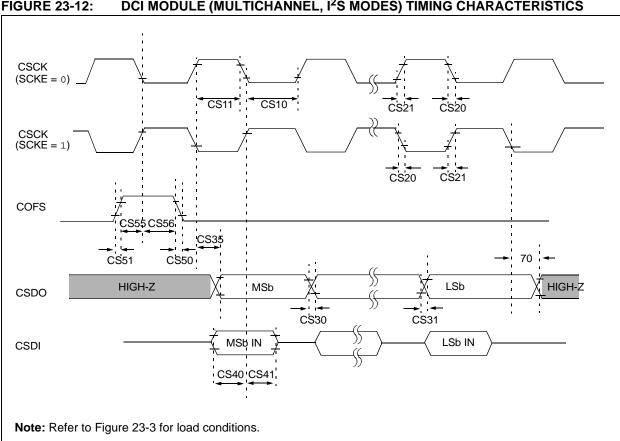

DCI MODULE (MULTICHANNEL, I<sup>2</sup>S MODES) TIMING CHARACTERISTICS FIGURE 23-12:

**AC CHARACTERISTICS**

## TABLE 23-36: I<sup>2</sup>C™ BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

Standard Operating Conditions: 2.5V to 5.5V

(unless otherwise stated)

Operating temperature -40°C ≤ TA ≤ +85°C for Industrial

-40°C ≤ TA ≤ +125°C for Extended

|              | ,       | 1                         |                           | -40 ( | J \( IA \( \) \( \) \( \) | 123 01 | or Extended                 |

|--------------|---------|---------------------------|---------------------------|-------|---------------------------|--------|-----------------------------|

| Param<br>No. | Symbol  | Charac                    | teristic                  | Min   | Max                       | Units  | Conditions                  |

| IS25         | TSU:DAT | Data Input                | 100 kHz mode              | 250   | <u> </u>                  | ns     | _                           |

|              |         | Setup Time                | 400 kHz mode              | 100   | _                         | ns     |                             |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 100   | _                         | ns     |                             |

| IS26         | THD:DAT | Data Input                | 100 kHz mode              | 0     | _                         | ns     | _                           |

|              |         | Hold Time                 | 400 kHz mode              | 0     | 0.9                       | μs     |                             |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0     | 0.3                       | μs     |                             |

| IS30         | Tsu:sta | Start Condition           | 100 kHz mode              | 4.7   | _                         | μs     | Only relevant for repeated  |

|              |         | Setup Time                | 400 kHz mode              | 0.6   | _                         | μs     | Start condition             |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0.25  | _                         | μs     |                             |

| IS31         | THD:STA | Start Condition           | 100 kHz mode              | 4.0   | _                         | μs     | After this period the first |

|              |         | Hold Time                 | 400 kHz mode              | 0.6   | _                         | μs     | clock pulse is generated    |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0.25  | _                         | μs     |                             |

| IS33         | Tsu:sto | Stop Condition            | 100 kHz mode              | 4.7   | _                         | μs     | _                           |

|              |         | Setup Time                | 400 kHz mode              | 0.6   | _                         | μs     |                             |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0.6   | _                         | μs     |                             |

| IS34         | THD:STO | Stop Condition            | 100 kHz mode              | 4000  | _                         | ns     | _                           |

|              |         | Hold Time                 | 400 kHz mode              | 600   | _                         | ns     |                             |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 250   |                           | ns     |                             |

| IS40         | TAA:SCL | Output Valid              | 100 kHz mode              | 0     | 3500                      | ns     | _                           |

|              |         | From Clock                | 400 kHz mode              | 0     | 1000                      | ns     |                             |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0     | 350                       | ns     |                             |

| IS45         | TBF:SDA | Bus Free Time             | 100 kHz mode              | 4.7   | _                         | μs     | Time the bus must be free   |

|              |         |                           | 400 kHz mode              | 1.3   | _                         | μs     | before a new transmission   |

|              |         |                           | 1 MHz mode <sup>(1)</sup> | 0.5   |                           | μs     | can start                   |

| IS50         | Св      | Bus Capacitive<br>Loading | 10. 51. 11.20             | _     | 400                       | pF     | _                           |

**Note 1:** Maximum pin capacitance = 10 pF for all  $I^2\text{C}$  pins (for 1 MHz mode only).

# dsPIC30F6011A/6012A/6013A/6014A

## INDEX A

| A                                                 |     |

|---------------------------------------------------|-----|

| A/D                                               |     |

| Aborting a Conversion                             |     |

| ADCHS Register                                    |     |

| ADCON1 Register                                   |     |

| ADCON2 Register                                   |     |

| ADCON3 Register                                   |     |

| ADCSSL Register                                   |     |

| ADPCFG Register                                   |     |

| Configuring Analog Port Pins64,                   |     |

| Connection Considerations                         |     |

| Conversion Operation                              |     |

| Effects of a Reset Operation During CPU Idle Mode |     |

| Operation During CPU Sleep Mode                   |     |

| Output Formats                                    |     |

| Power-down Modes                                  |     |

| Programming the Sample Trigger                    |     |

| Register Map                                      |     |

| Result Buffer                                     |     |

| Sampling Requirements                             |     |

| Selecting the Conversion Sequence                 |     |

| AC Characteristics                                |     |

| Load Conditions                                   |     |

| AC Temperature and Voltage Specifications         |     |

| AC-Link Mode Operation                            |     |

| 16-bit Mode                                       |     |

| 20-bit Mode                                       | 132 |

| ADC                                               |     |

| Selecting the Conversion Clock                    | 137 |

| ADC Conversion Speeds                             | 138 |

| Address Generator Units                           | 39  |

| Alternate Vector Table                            | 49  |

| Analog-to-Digital Converter. See A/D.             |     |

| Assembler                                         |     |

| MPASM Assembler                                   |     |

| Automatic Clock Stretch                           |     |

| During 10-bit Addressing (STREN = 1)              |     |

| During 7-bit Addressing (STREN = 1)               |     |

| Receive Mode                                      |     |

| Transmit Mode                                     | 98  |

| В                                                 |     |

| Band Gap Start-up Time                            |     |

| Requirements                                      | 188 |

| Timing Characteristics                            | 188 |

| Barrel Shifter                                    |     |

| Bit-Reversed Addressing                           |     |

| Example                                           |     |

| Implementation                                    |     |

| Modifier Values Table                             | 43  |

| Sequence Table (16-Entry)                         |     |

| Block Diagrams                                    |     |

| 12-bit A/D Functional                             | 135 |

| 16-bit Timer1 Module                              |     |

| 16-bit Timer2                                     |     |

| 16-bit Timer3                                     | 75  |

| 16-bit Timer4                                     | 80  |

| 16-bit Timer5                                     |     |

| 32-bit Timer2/3                                   |     |

| 32-bit Timer4/5                                   |     |

| CAN Buffers and Protocol Engine                   |     |

| DCI Module                                        | 126 |

| Dedicated Port Structure DSP Engine                  |     |

|------------------------------------------------------|-----|

| dsPIC30F6011/6012/6013/6014                          | 20  |

|                                                      |     |

| dsPIC30F6013/6014<br>External Power-on Reset Circuit | 450 |

|                                                      |     |

| l <sup>2</sup> C                                     |     |

| Input Capture Mode                                   |     |

| Oscillator System                                    |     |

| Output Compare Mode                                  |     |

| Reset System                                         |     |

| Shared Port Structure                                |     |

| SPI                                                  |     |

| SPI Master/Slave Connection                          |     |

| UART Receiver                                        | 104 |

| UART Transmitter                                     | 103 |

| BOR Characteristics                                  | 181 |

| BOR. See Brown-out Reset.                            |     |

| Brown-out Reset                                      |     |

| Characteristics                                      | 180 |

| Timing Requirements                                  |     |

| _                                                    |     |

| C                                                    |     |

| C Compilers                                          |     |

| MPLAB C18                                            | 170 |

| MPLAB C30                                            |     |

| CAN Module                                           |     |

| Baud Rate Setting                                    |     |

| CAN1 Register Map                                    | 110 |

| Frame Types                                          |     |

|                                                      |     |

| I/O Timing Characteristics                           |     |

| I/O Timing Requirements                              |     |

| Message Reception                                    |     |

| Message Transmission                                 |     |

| Modes of Operation                                   |     |

| Overview                                             | 111 |

| CLKO and I/O Timing                                  |     |

| Characteristics                                      |     |

| Requirements                                         | 186 |

| Code Examples                                        |     |

| Data EEPROM Block Erase                              |     |

| Data EEPROM Block Write                              | 60  |

| Data EEPROM Read                                     | 57  |

| Data EEPROM Word Erase                               | 58  |

| Data EEPROM Word Write                               | 59  |

| Erasing a Row of Program Memory                      |     |

| Initiating a Programming Sequence                    | 54  |

| Loading Write Latches                                | 54  |

| Code Protection                                      |     |

| Core Architecture                                    | 170 |

| Overview                                             | 15  |

| CPU Architecture Overview                            |     |

|                                                      |     |

| Customer Change Notification Service                 |     |

| Customer Notification Service                        |     |

| Customer Support                                     | 223 |

# dsPIC30F6011A/6012A/6013A/6014A

| F                                                      |       |

|--------------------------------------------------------|-------|

| Fast Context Saving                                    | 49    |

| Flash Program Memory                                   |       |

| Control Registers                                      |       |

| NVMADR                                                 |       |

| NVMADRU                                                |       |

| NVMCON                                                 | _     |

| NVMKEY                                                 | 52    |

| 1                                                      |       |

| I/O Pin Specifications                                 |       |

| Input                                                  | . 178 |

| Output                                                 |       |

| I/O Ports                                              |       |

| Parallel (PIO)                                         |       |

| I <sup>2</sup> C 10-bit Slave Mode Operation           | 97    |

| Reception                                              |       |

| Transmission                                           |       |

| I <sup>2</sup> C 7-bit Slave Mode Operation            |       |

| Reception                                              |       |

| Transmission  I <sup>2</sup> C Master Mode Operation   |       |

| Baud Rate Generator                                    | 100   |

| Clock Arbitration                                      | 100   |

| Multi-Master Communication, Bus Collision              | . 100 |

| and Bus Arbitration                                    | . 100 |

| Reception                                              |       |

| Transmission                                           | 99    |

| I <sup>2</sup> C Master Mode Support                   | 99    |

| I <sup>2</sup> C Module                                | 95    |

| Addresses                                              | 97    |

| Bus Data Timing Characteristics                        |       |

| Master Mode                                            |       |

| Slave Mode                                             | 203   |

| Bus Data Timing Requirements                           |       |

| Master Mode                                            |       |

| Slave Mode                                             | 203   |

| Bus Start/Stop Bits Timing Characteristics Master Mode | 201   |

| Slave Mode                                             |       |

| General Call Address Support                           |       |

| Interrupts                                             |       |

| IPMI Support                                           |       |

| Operating Function Description                         |       |

| Operation During CPU Sleep and Idle Modes              | . 100 |

| Pin Configuration                                      |       |

| Programmer's Model                                     |       |

| Register Map                                           |       |

| Registers                                              | 95    |

| Slope Control                                          |       |

| Software Controlled Clock Stretching (STREN = 1).      |       |

| Various Modes                                          |       |

| I <sup>2</sup> S Mode Operation                        |       |

| Data Justification                                     |       |

| Frame and Data Word Length Selection                   |       |

| Idle Current (IDLE)                                    |       |

| In-Circuit Serial Programming (ICSP)                   |       |

| Input Capture (CAPX) Timing Characteristics            |       |

| Input Capture Module Interrupts                        |       |

| Register Map                                           |       |

| Input Capture Operation During Sleep and Idle Modes    |       |

| CPU Idle Mode                                          |       |

| CPU Sleep Mode                                         |       |

| Input Capture Timing Requirements                      |       |

| Input Change Notification Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction Addressing Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| File Register Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Fundamental Modes Supported                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MAC Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| MCU Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Move and Accumulator Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Other Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Instruction Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Summary 161                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Internet Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Interrupt Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Register Map 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Interrupt Priority                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Interrupt Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Interrupt Stack Frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Load Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Low Voltage Detect (LVD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Low-Voltage Detect Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| LVDL Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Memory Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Memory Organization         25           Core Register Map         35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |