Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Detuils                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20 MIPS                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | AC'97, Brown-out Detect/Reset, I <sup>2</sup> S, LVD, POR, PWM, WDT            |

| Number of I/O              | 52                                                                             |

| Program Memory Size        | 144KB (48K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 4K x 8                                                                         |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 16x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f6012t-20i-pf |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC30F6011/6012/6013/6014

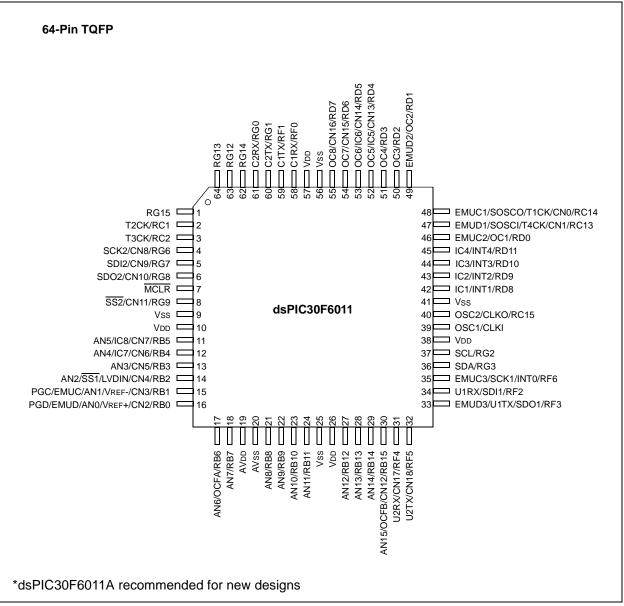

#### **Pin Diagrams**

Note: For descriptions of individual pins, see Section 1.0 "Device Overview".

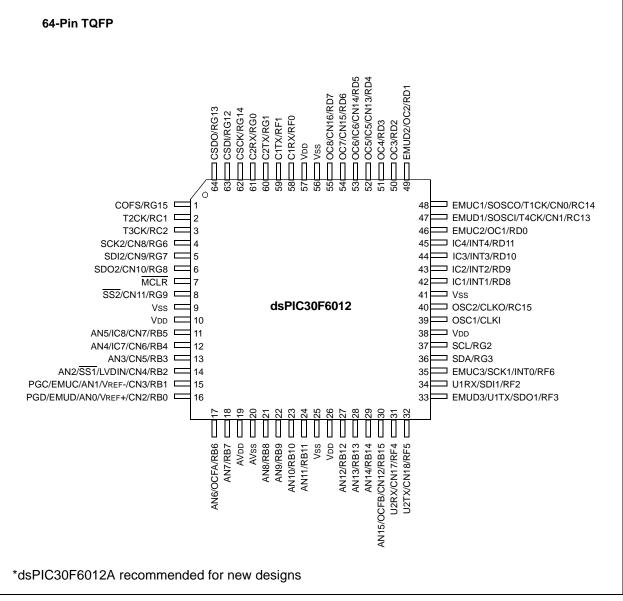

# Pin Diagrams (Continued)

Note: For descriptions of individual pins, see Section 1.0 "Device Overview".

# 2.0 CPU ARCHITECTURE OVERVIEW

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "*dsPIC30F Family Reference Manual*" (DS70046). For more information on the device instruction set and programming, refer to the "*dsPIC30F/ 33F Programmer's Reference Manual*" (DS70157).

# 2.1 Core Overview

This section contains a brief overview of the CPU architecture of the dsPIC30F. For additional hardware and programming information, please refer to the "*dsPIC30F Family Reference Manual*" (DS70046) and the "*dsPIC30F/33F Programmer's Reference Manual*" (DS70157) respectively.

The core has a 24-bit instruction word. The Program Counter (PC) is 23 bits wide with the Least Significant bit (LSb) always clear (refer to **Section 3.1** "**Program Address Space**"), and the Most Significant bit (MSb) is ignored during normal program execution, except for certain specialized instructions. Thus, the PC can address up to 4M instruction words of user program space. An instruction prefetch mechanism is used to help maintain throughput. Program loop constructs, free from loop count management overhead, are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The working register array consists of 16 x 16-bit registers, each of which can act as data, address or offset registers. One working register (W15) operates as a software Stack Pointer for interrupts and calls.

The data space is 64 Kbytes (32K words) and is split into two blocks, referred to as X and Y data memory. Each block has its own independent Address Generation Unit (AGU). Most instructions operate solely through the X memory, AGU, which provides the appearance of a single unified data space. The Multiply-Accumulate (MAC) class of dual source DSP instructions operate through both the X and Y AGUs, splitting the data address space into two parts (see **Section 3.2 "Data Address Space"**). The X and Y data space boundary is device specific and cannot be altered by the user. Each data word consists of 2 bytes, and most instructions can address data either as words or bytes. There are two methods of accessing data stored in program memory:

- The upper 32 Kbytes of data space memory can be mapped into the lower half (user space) of program space at any 16K program word boundary, defined by the 8-bit Program Space Visibility Page (PSVPAG) register. This lets any instruction access program space as if it were data space, with a limitation that the access requires an additional cycle. Moreover, only the lower 16 bits of each instruction word can be accessed using this method.

- Linear indirect access of 32K word pages within program space is also possible using any working register, via table read and write instructions.

Table read and write instructions can be used to access all 24 bits of an instruction word.

Overhead-free circular buffers (Modulo Addressing) are supported in both X and Y address spaces. This is primarily intended to remove the loop overhead for DSP algorithms.

The X AGU also supports Bit-Reversed Addressing on destination effective addresses to greatly simplify input or output data reordering for radix-2 FFT algorithms. Refer to **Section 4.0 "Address Generator Units"** for details on Modulo and Bit-Reversed Addressing.

The core supports Inherent (no operand), Relative, Literal, Memory Direct, Register Direct, Register Indirect, Register Offset and Literal Offset Addressing modes. Instructions are associated with predefined addressing modes, depending upon their functional requirements.

For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, 3-operand instructions are supported, allowing C = A + B operations to be executed in a single cycle.

A DSP engine has been included to significantly enhance the core arithmetic capability and throughput. It features a high-speed 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. Data in the accumulator or any working register can be shifted up to 15 bits right, or 16 bits left in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC class of instructions can concurrently fetch two data operands from memory while multiplying two W registers. To enable this concurrent fetching of data operands, the data space has been split for these instructions and linear for all others. This has been achieved in a transparent and flexible manner, by dedicating certain working registers to each address space for the MAC class of instructions.

# 3.0 MEMORY ORGANIZATION

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "*dsPIC30F Family Reference Manual*" (DS70046). For more information on the device instruction set and programming, refer to the "*dsPIC30F/ 33F Programmer's Reference Manual*" (DS70157).

# 3.1 Program Address Space

The program address space is 4M instruction words. It is addressable by a 24-bit value from either the 23-bit PC, table instruction Effective Address (EA), or data space EA, when program space is mapped into data space as defined by Table 3-1. Note that the program space address is incremented by two between successive program words in order to provide compatibility with data space addressing. User program space access is restricted to the lower 4M instruction word address range (0x000000 to 0x7FFFFE) for all accesses other than TBLRD/TBLWT, which use TBLPAG<7> to determine user or configuration space access. In Table 3-1, Program Space Address Construction, bit 23 allows access to the Device ID, the User ID and the Configuration bits. Otherwise, bit 23 is always clear.

Note: The address map shown in Figure 3-1 and Figure 3-2 is conceptual, and the actual memory configuration may vary across individual devices depending on available memory.

# 3.2 Data Address Space

The core has two data spaces. The data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths.

### 3.2.1 DATA SPACE MEMORY MAP

The data space memory is split into two blocks, X and Y data space. A key element of this architecture is that Y space is a subset of X space, and is fully contained within X space. In order to provide an apparent linear addressing space, X and Y spaces have contiguous addresses.

When executing any instruction other than one of the MAC class of instructions, the X block consists of the 64-Kbyte data address space (including all Y addresses). When executing one of the MAC class of instructions, the X block consists of the 64-Kbyte data address space excluding the Y address block (for data reads only). In other words, all other instructions regard the entire data memory as one composite address space. The MAC class instructions extract the Y address space from data space and address it using EAs sourced from W10 and W11. The remaining X data space is addressed using W8 and W9. Both address spaces are concurrently accessed only with the MAC class instructions.

The data space memory maps are shown in Figure 3-8 and Figure 3-9.

## 3.2.2 DATA SPACES

The X data space is used by all instructions and supports all addressing modes. There are separate read and write data buses. The X read data bus is the return data path for all instructions that view data space as combined X and Y address space. It is also the X address space data path for the dual operand read instructions (MAC class). The X write data bus is the only write path to data space for all instructions.

The X data space also supports Modulo Addressing for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing is only supported for writes to X data space.

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N and MSC) to provide two concurrent data read paths. No writes occur across the Y bus. This class of instructions dedicates two W register pointers, W10 and W11, to always address Y data space, independent of X data space, whereas W8 and W9 always address X data space. Note that during accumulator write back, the data address space is considered a combination of X and Y data spaces, so the write occurs across the X bus. Consequently, the write can be to any address in the entire data space.

The Y data space can only be used for the data prefetch operation associated with the MAC class of instructions. It also supports Modulo Addressing for automated circular buffers. Of course, all other instructions can access the Y data address space through the X data path as part of the composite linear space.

The boundary between the X and Y data spaces is defined as shown in Figure 3-8 and Figure 3-8 and is not user programmable. Should an EA point to data outside its own assigned address space, or to a location outside physical memory, an all zero word/byte will be returned. For example, although Y address space is visible by all non-MAC instructions using any addressing mode, an attempt by a MAC instruction to fetch data from that space using W8 or W9 (X space pointers) will return 0x0000.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. Should a misaligned read or write be attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed, whereas if it occurred on a write, the instruction will be executed but the write will not occur. In either case, a trap will then be executed, allowing the system and/or user to examine the machine state prior to execution of the address fault.

FIGURE 3-10: DATA ALIGNMENT

|      | 15 <b>MSB</b> | 8 | 7 LSB  | 0 |      |

|------|---------------|---|--------|---|------|

| 0001 | Byte1         |   | Byte 0 |   | 0000 |

| 0003 | Byte3         |   | Byte 2 |   | 0002 |

| 0005 | Byte5         |   | Byte 4 |   | 0004 |

|      |               |   |        |   |      |

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A sign-extend (SE) instruction is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions, including the DSP instructions, operate only on words.

## 3.2.5 NEAR DATA SPACE

An 8-Kbyte 'near' data space is reserved in X address memory space between 0x0000 and 0x1FFF, which is directly addressable via a 13-bit absolute address field within all memory direct instructions. The remaining X address space and all of the Y address space is addressable indirectly. Additionally, the whole of X data space is addressable using MOV instructions, which support memory direct addressing with a 16-bit address field.

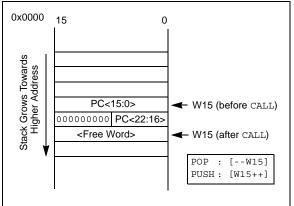

## 3.2.6 SOFTWARE STACK

The dsPIC DSC devices contain a software stack. W15 is used as the Stack Pointer.

The Stack Pointer always points to the first available free word and grows from lower addresses towards higher addresses. It pre-decrements for stack pops and post-increments for stack pushes as shown in Figure 3-11. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | will concatenate the SRL register to the |

|       | MSB of the PC prior to the push.         |

There is a Stack Pointer Limit register (SPLIM) associated with the Stack Pointer. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word aligned. Whenever an Effective Address (EA) is generated using W15 as a source or destination pointer, the address thus generated is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value, 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800, thus preventing the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### FIGURE 3-11: CALL STACK FRAME

### TABLE 6-1: NVM REGISTER MAP

| File Name | Addr. | Bit 15 | Bit 14       | Bit 13                      | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6         | Bit 5               | Bit 4 | Bit 3 | Bit 2 | Bit 1               | Bit 0               | All RESETS |

|-----------|-------|--------|--------------|-----------------------------|--------|--------|--------|-------|-------|-------|---------------|---------------------|-------|-------|-------|---------------------|---------------------|------------|

| NVMCON    | 0760  | WR     | WREN         | WRERR                       | —      | -      | —      | _     | TWRI  | _     | - PROGOP<6:0> |                     |       |       |       |                     | 0000 0000 0000 0000 |            |

| NVMADR    | 0762  |        | NVMADR<15:0> |                             |        |        |        |       |       |       |               | uuuu uuuu uuuu uuuu |       |       |       |                     |                     |            |

| NVMADRU   | 0764  | _      | _            | ─ ─ ─ ─ ─ ─ ─ NVMADR<23:16> |        |        |        |       |       |       |               | 0000 0000 uuuu uuuu |       |       |       |                     |                     |            |

| NVMKEY    | 0766  | _      | _            |                             | _      | -      |        | _     |       |       | KEY<7:0>      |                     |       |       |       | 0000 0000 0000 0000 |                     |            |

**Legend:** u = uninitialized bit

**Note:** Refer to "*dsPIC30F Family Reference Manual*" (DS70046) for descriptions of register bit fields.

# 16.9 Auto Baud Support

To allow the system to determine baud rates of received characters, the input can be optionally linked to a capture input (IC1 for UART1, IC2 for UART2). To enable this mode, the user must program the input capture module to detect the falling and rising edges of the Start bit.

## 16.10 UART Operation During CPU Sleep and Idle Modes

#### 16.10.1 UART OPERATION DURING CPU SLEEP MODE

When the device enters Sleep mode, all clock sources to the module are shutdown and stay at logic '0'. If entry into Sleep mode occurs while a transmission is in progress, then the transmission is aborted. The UxTX pin is driven to logic '1'. Similarly, if entry into Sleep mode occurs while a reception is in progress, then the reception is aborted. The UxSTA, UxMODE, transmit and receive registers and buffers, and the UxBRG register are not affected by Sleep mode.

If the WAKE bit (UxMODE<7>) is set before the device enters Sleep mode, then a falling edge on the UxRX pin will generate a receive interrupt. The Receive Interrupt Select mode bit (URXISEL) has no effect for this function. If the receive interrupt is enabled, then this will wake-up the device from Sleep. The UARTEN bit must be set in order to generate a wake-up interrupt.

# 16.10.2 UART OPERATION DURING CPU IDLE MODE

For the UART, the USIDL bit selects if the module will stop operation when the device enters Idle mode or whether the module will continue on Idle. If USIDL = 0, the module will continue operation during Idle mode. If USIDL = 1, the module will stop on Idle.

# 17.0 CAN MODULE

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "*dsPIC30F Family Reference Manual*" (DS70046).

# 17.1 Overview

The Controller Area Network (CAN) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/ protocol was designed to allow communications within noisy environments.

The CAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH specification. The module will support CAN 1.2, CAN 2.0A, CAN 2.0B Passive, and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader may refer to the BOSCH CAN specification for further details.

The module features are as follows:

- Implementation of the CAN protocol CAN 1.2, CAN 2.0A and CAN 2.0B

- Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Support for remote frames

- Double-buffered receiver with two prioritized received message storage buffers (each buffer may contain up to 8 bytes of data)

- 6 full (standard/extended identifier) acceptance filters, 2 associated with the high priority receive buffer and 4 associated with the low priority receive buffer

- 2 full acceptance filter masks, one each associated with the high and low priority receive buffers

- Three transmit buffers with application specified prioritization and abort capability (each buffer may contain up to 8 bytes of data)

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- Programmable clock source

- Programmable link to Input Capture module (IC2, for both CAN1 and CAN2) for time-stamping and network synchronization

- Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

# 17.2 Frame Types

The CAN module transmits various types of frames which include data messages or remote transmission requests initiated by the user, as other frames that are automatically generated for control purposes. The following frame types are supported:

• Standard Data Frame:

A standard data frame is generated by a node when the node wishes to transmit data. It includes an 11-bit standard identifier (SID) but not an 18-bit extended identifier (EID).

• Extended Data Frame:

An extended data frame is similar to a standard data frame but includes an extended identifier as well.

• Remote Frame:

It is possible for a destination node to request the data from the source. For this purpose, the destination node sends a remote frame with an identifier that matches the identifier of the required data frame. The appropriate data source node will then send a data frame as a response to this remote request.

• Error Frame:

An error frame is generated by any node that detects a bus error. An error frame consists of 2 fields: an error flag field and an error delimiter field.

Overload Frame:

An overload frame can be generated by a node as a result of 2 conditions. First, the node detects a dominant bit during interframe space which is an illegal condition. Second, due to internal conditions, the node is not yet able to start reception of the next message. A node may generate a maximum of 2 sequential overload frames to delay the start of the next message.

• Interframe Space:

Interframe space separates a proceeding frame (of whatever type) from a following data or remote frame.

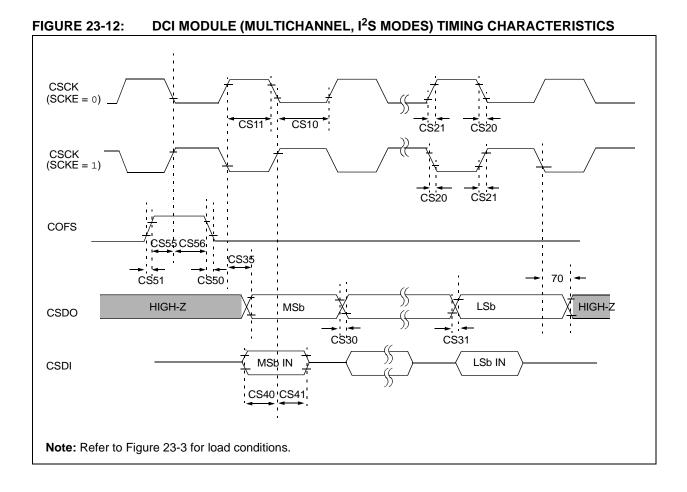

# 18.0 DATA CONVERTER INTERFACE (DCI) MODULE

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "*dsPIC30F Family Reference Manual*" (DS70046).

# **18.1 Module Introduction**

The dsPIC30F Data Converter Interface (DCI) module allows simple interfacing of devices, such as audio coder/decoders (Codecs), A/D converters and D/A converters. The following interfaces are supported:

- Framed Synchronous Serial Transfer (Single or Multi-Channel)

- Inter-IC Sound (I<sup>2</sup>S) Interface

- AC-Link Compliant mode

The DCI module provides the following general features:

- Programmable word size up to 16 bits

- Support for up to 16 time slots, for a maximum frame size of 256 bits

- Data buffering for up to 4 samples without CPU overhead

# 18.2 Module I/O Pins

There are four I/O pins associated with the module. When enabled, the module controls the data direction of each of the four pins.

#### 18.2.1 CSCK PIN

The CSCK pin provides the serial clock for the DCI module. The CSCK pin may be configured as an input or output using the CSCKD control bit in the DCICON1 SFR. When configured as an output, the serial clock is provided by the dsPIC30F. When configured as an input, the serial clock must be provided by an external device.

#### 18.2.2 CSDO PIN

The serial data output (CSDO) pin is configured as an output only pin when the module is enabled. The CSDO pin drives the serial bus whenever data is to be transmitted. The CSDO pin is tri-stated or driven to '0' during CSCK periods when data is not transmitted, depending on the state of the CSDOM control bit. This allows other devices to place data on the serial bus during transmission periods not used by the DCI module.

## 18.2.3 CSDI PIN

The serial data input (CSDI) pin is configured as an input only pin when the module is enabled.

## 18.2.3.1 COFS PIN

The Codec frame synchronization (COFS) pin is used to synchronize data transfers that occur on the CSDO and CSDI pins. The COFS pin may be configured as an input or an output. The data direction for the COFS pin is determined by the COFSD control bit in the DCICON1 register.

The DCI module accesses the shadow registers while the CPU is in the process of accessing the memory mapped buffer registers.

#### 18.2.4 BUFFER DATA ALIGNMENT

Data values are always stored left justified in the buffers since most Codec data is represented as a signed 2's complement fractional number. If the received word length is less than 16 bits, the unused LSbs in the receive buffer registers are set to '0' by the module. If the transmitted word length is less than 16 bits, the unused LSbs in the transmit buffer register are ignored by the module. The word length setup is described in subsequent sections of this document.

#### 18.2.5 TRANSMIT/RECEIVE SHIFT REGISTER

The DCI module has a 16-bit shift register for shifting serial data in and out of the module. Data is shifted in/ out of the shift register MSb first, since audio PCM data is transmitted in signed 2's complement format.

## 18.2.6 DCI BUFFER CONTROL

The DCI module contains a buffer control unit for transferring data between the shadow buffer memory and the serial shift register. The buffer control unit is a simple 2-bit address counter that points to word locations in the shadow buffer memory. For the receive memory space (high address portion of DCI buffer memory), the address counter is concatenated with a '0' in the MSb location to form a 3-bit address. For the transmit memory space (high portion of DCI buffer memory), the address counter is concatenated with a '1' in the MSb location.

Note: The DCI buffer control unit always accesses the same relative location in the transmit and receive buffers, so only one address counter is provided.

# 20.0 SYSTEM INTEGRATION

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "*dsPIC30F Family Reference Manual*" (DS70046). For more information on the device instruction set and programming, refer to the "*dsPIC30F/ 33F Programmer's Reference Manual*" (DS70157).

There are several features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection:

- Oscillator Selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Programmable Brown-out Reset (BOR)

- Watchdog Timer (WDT)

- Low-Voltage Detect

- Power-Saving Modes (Sleep and Idle)

- Code Protection

- Unit ID Locations

- In-Circuit Serial Programming (ICSP)

dsPIC30F devices have a Watchdog Timer which is permanently enabled via the Configuration bits or can be software controlled. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT) which provides a delay on power-up only, designed to keep the part in Reset while the power supply stabilizes. With these two timers on-chip, most applications need no external Reset circuitry.

Sleep mode is designed to offer a very low-current Power-down mode. The user can wake-up from Sleep through external Reset, Watchdog Timer wake-up, or through an interrupt. Several oscillator options are also made available to allow the part to fit a wide variety of applications. In the Idle mode, the clock sources are still active but the CPU is shut off. The RC oscillator option saves system cost while the LP crystal option saves power.

### 20.1 Oscillator System Overview

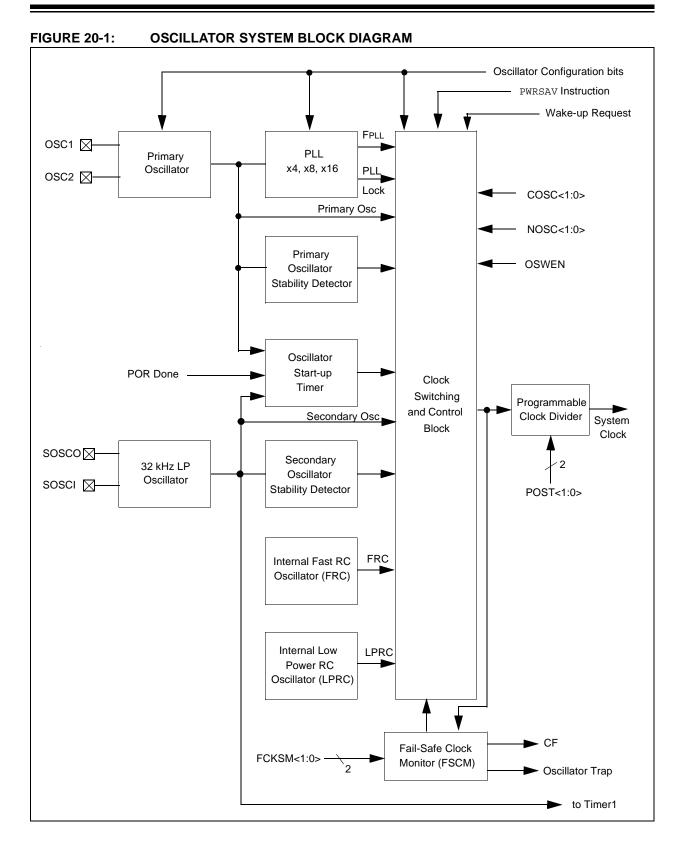

The dsPIC30F oscillator system has the following modules and features:

- Various external and internal oscillator options as clock sources

- An on-chip PLL to boost internal operating frequency

- A clock switching mechanism between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- Clock Control register (OSCCON)

- · Configuration bits for main oscillator selection

Table 20-1 provides a summary of the dsPIC30F Oscillator Operating modes. A simplified diagram of the oscillator system is shown in Figure 20-1.

Configuration bits determine the clock source upon Power-on Reset (POR) and Brown-out Reset (BOR). Thereafter, the clock source can be changed between permissible clock sources. The OSCCON register controls the clock switching and reflects system clock related status bits.

## TABLE 20-1: OSCILLATOR OPERATING MODES

| Oscillator Mode | Description                                                                         |

|-----------------|-------------------------------------------------------------------------------------|

| XTL             | 200 kHz-4 MHz crystal on OSC1:OSC2.                                                 |

| ХТ              | 4 MHz-10 MHz crystal on OSC1:OSC2.                                                  |

| XT w/PLL 4x     | 4 MHz-10 MHz crystal on OSC1:OSC2, 4x PLL enabled.                                  |

| XT w/PLL 8x     | 4 MHz-10 MHz crystal on OSC1:OSC2, 8x PLL enabled.                                  |

| XT w/PLL 16x    | 4 MHz-10 MHz crystal on OSC1:OSC2, 16x PLL enabled <sup>(1)</sup> .                 |

| LP              | 32 kHz crystal on SOSCO:SOSCI <sup>(2)</sup> .                                      |

| HS              | 10 MHz-25 MHz crystal.                                                              |

| EC              | External clock input (0-40 MHz).                                                    |

| ECIO            | External clock input (0-40 MHz), OSC2 pin is I/O.                                   |

| EC w/PLL 4x     | External clock input (4-10 MHz), OSC2 pin is I/O, 4x PLL enabled <sup>(1)</sup> .   |

| EC w/PLL 8x     | External clock input (4-10 MHz), OSC2 pin is I/O, 8x PLL enabled <sup>(1)</sup> .   |

| EC w/PLL 16x    | External clock input (4-7.5 MHz), OSC2 pin is I/O, 16x PLL enabled <sup>(1)</sup> . |

| ERC             | External RC oscillator, OSC2 pin is Fosc/4 output <sup>(3)</sup> .                  |

| ERCIO           | External RC oscillator, OSC2 pin is I/O <sup>(3)</sup> .                            |

| FRC             | 7.37 MHz internal RC oscillator.                                                    |

| LPRC            | 512 kHz internal RC oscillator.                                                     |

Note 1: dsPIC30F maximum operating frequency of 120 MHz must be met.

2: LP oscillator can be conveniently shared as system clock, as well as real-time clock for Timer1.

3: Requires external R and C. Frequency operation up to 4 MHz.

# dsPIC30F6011/6012/6013/6014

| DC CHARACTERISTICS |        |                                               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |     |      |       |            |  |  |

|--------------------|--------|-----------------------------------------------|-------------------------------------------------------|------|-----|------|-------|------------|--|--|

| Param<br>No.       | Symbol | Characteristic <sup>(</sup>                   | 1)                                                    | Min  | Тур | Max  | Units | Conditions |  |  |

| LV10               | Vplvd  | LVDL Voltage on VDD transition<br>high to low | LVDL = 0000 <sup>(2)</sup>                            |      |     | _    | V     |            |  |  |

|                    |        |                                               | LVDL = 0001 <sup>(2)</sup>                            | —    |     | —    | V     |            |  |  |

|                    |        |                                               | LVDL = 0010 <sup>(2)</sup>                            | —    |     | —    | V     |            |  |  |

|                    |        |                                               | LVDL = 0011(2)                                        | _    |     | _    | V     |            |  |  |

|                    |        |                                               | LVDL = 0100                                           | 2.50 |     | 2.65 | V     |            |  |  |

|                    |        |                                               | LVDL = 0101                                           | 2.70 |     | 2.86 | V     |            |  |  |

|                    |        |                                               | LVDL = 0110                                           | 2.80 |     | 2.97 | V     |            |  |  |

|                    |        |                                               | LVDL = 0111                                           | 3.00 |     | 3.18 | V     |            |  |  |

|                    |        |                                               | LVDL = 1000                                           | 3.30 |     | 3.50 | V     |            |  |  |

|                    |        |                                               | LVDL = 1001                                           | 3.50 | _   | 3.71 | V     |            |  |  |

|                    |        |                                               | LVDL = 1010                                           | 3.60 |     | 3.82 | V     |            |  |  |

|                    |        |                                               | LVDL = 1011                                           | 3.80 |     | 4.03 | V     |            |  |  |

|                    |        |                                               | LVDL = 1100                                           | 4.00 | _   | 4.24 | V     |            |  |  |

|                    |        |                                               | LVDL = 1101                                           | 4.20 | _   | 4.45 | V     |            |  |  |

|                    |        |                                               | LVDL = 1110                                           | 4.50 |     | 4.77 | V     |            |  |  |

| LV15               | Vlvdin | External LVD input pin threshold voltage      | LVDL = 1111                                           | _    | _   | _    | V     |            |  |  |

#### TABLE 23-10: ELECTRICAL CHARACTERISTICS: LVDL

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** These values not in usable operating range.

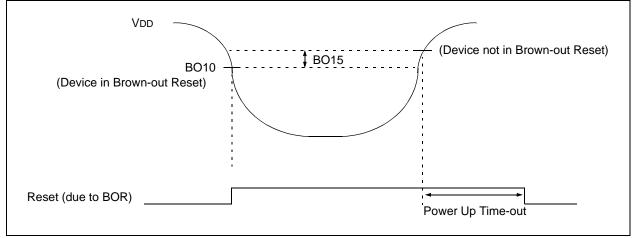

### FIGURE 23-2: BROWN-OUT RESET CHARACTERISTICS

#### TABLE 23-11: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |                                                             |           | (unless otherw           | Standard Operating Conditions: 2.5V to 5.5Vunless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                    |      |       |                        |  |  |

|--------------------|-------------------------------------------------------------|-----------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|-------|------------------------|--|--|

| Param<br>No.       | Symbol                                                      | Character | istic                    | Min                                                                                                                                                                                                 | Typ <sup>(1)</sup> | Max  | Units | Conditions             |  |  |

| BO10               | BO10 VBOR BOR Voltage <sup>(2)</sup> on VDD transition high |           | BORV = 11 <sup>(3)</sup> | _                                                                                                                                                                                                   | _                  | _    | V     | Not in operating range |  |  |

|                    |                                                             | low       | BORV = 10                | 2.6                                                                                                                                                                                                 |                    | 2.71 | V     |                        |  |  |

|                    |                                                             |           | BORV = 01                | 4.1                                                                                                                                                                                                 | _                  | 4.4  | V     |                        |  |  |

|                    | BORV = 0                                                    |           | BORV = 00                | 4.58                                                                                                                                                                                                | —                  | 4.73 | V     |                        |  |  |

| BO15               | VBHYS                                                       |           |                          | _                                                                                                                                                                                                   | 5                  |      | mV    |                        |  |  |

**Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized but not tested in manufacturing.

**3:** '11' values not in usable operating range.

#### TABLE 23-12: DC CHARACTERISTICS: PROGRAM AND EEPROM

| DC CHARACTERISTICS |        |                                     |      |                    | ise state | nditions: 2.5V to 5.5V<br>ed)<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                                                  |  |  |

|--------------------|--------|-------------------------------------|------|--------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic                      | Min  | Typ <sup>(1)</sup> | Max       | Units                                                                                                                                          | Conditions                                                       |  |  |

|                    |        | Data EEPROM Memory <sup>(2)</sup>   |      |                    |           |                                                                                                                                                |                                                                  |  |  |

| D120               | ED     | Byte Endurance                      | 100K | 1M                 |           | E/W                                                                                                                                            | $-40^{\circ}C \le TA \le +85^{\circ}C$                           |  |  |

| D121               | Vdrw   | VDD for Read/Write                  | Vmin | _                  | 5.5       | V                                                                                                                                              | Using EECON to read/write<br>VMIN = Minimum operating<br>voltage |  |  |

| D122               | TDEW   | Erase/Write Cycle Time              | —    | 2                  | —         | ms                                                                                                                                             |                                                                  |  |  |

| D123               | Tretd  | Characteristic Retention            | 40   | 100                | —         | Year                                                                                                                                           | Provided no other specifications are violated                    |  |  |

| D124               | IDEW   | IDD During Programming              | _    | 10                 | 30        | mA                                                                                                                                             | Row Erase                                                        |  |  |

|                    |        | Program FLASH Memory <sup>(2)</sup> |      |                    |           |                                                                                                                                                |                                                                  |  |  |

| D130               | Eр     | Cell Endurance                      | 10K  | 100K               | _         | E/W                                                                                                                                            | $-40^{\circ}C \le TA \le +85^{\circ}C$                           |  |  |

| D131               | Vpr    | VDD for Read                        | VMIN | —                  | 5.5       | V                                                                                                                                              | VMIN = Minimum operating<br>voltage                              |  |  |

| D132               | VEB    | VDD for Bulk Erase                  | 4.5  |                    | 5.5       | V                                                                                                                                              |                                                                  |  |  |

| D133               | VPEW   | VDD for Erase/Write                 | 3.0  |                    | 5.5       | V                                                                                                                                              |                                                                  |  |  |

| D134               | TPEW   | Erase/Write Cycle Time              | _    | 2                  | _         | ms                                                                                                                                             |                                                                  |  |  |

| D135               | Tretd  | Characteristic Retention            | 40   | 100                | —         | Year                                                                                                                                           | Provided no other specifications are violated                    |  |  |

| D136               | Тев    | ICSP Block Erase Time               | —    | 4                  | _         | ms                                                                                                                                             |                                                                  |  |  |

| D137               | IPEW   | IDD During Programming              | —    | 10                 | 30        | mA                                                                                                                                             | Row Erase                                                        |  |  |

| D138               | lев    | IDD During Programming              | _    | 10                 | 30        | mA                                                                                                                                             | Bulk Erase                                                       |  |  |

**Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated.

**2:** These parameters are characterized but not tested in manufacturing.

# 23.2 AC Characteristics and Timing Parameters

The information contained in this section defines dsPIC30F AC characteristics and timing parameters.

### TABLE 23-13: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 2.5V to 5.5V<br>(unless otherwise stated)                                                                                                                                       |  |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended<br>Operating voltage VDD range as described in DC Spec <b>Section 23.0</b> |  |  |  |  |

|                    | "Electrical Characteristics".                                                                                                                                                                                  |  |  |  |  |

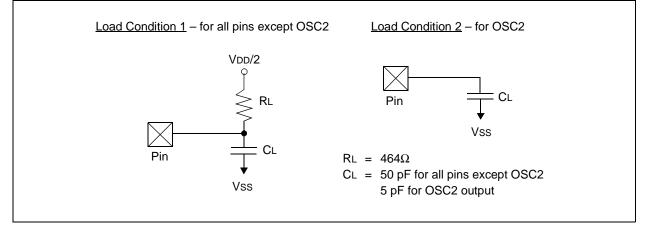

## FIGURE 23-3: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

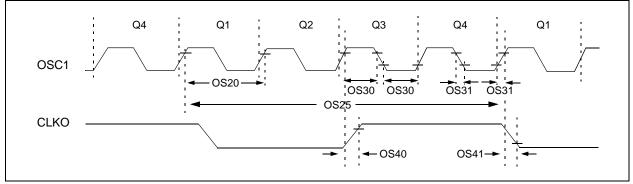

# FIGURE 23-4: EXTERNAL CLOCK TIMING

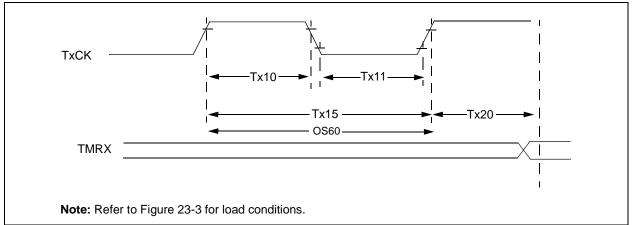

#### FIGURE 23-8: TYPE A, B AND C TIMER EXTERNAL CLOCK TIMING CHARACTERISTICS

# TABLE 23-23: TYPE A TIMER (TIMER1) EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

| AC CHARACTERISTICS |           |                                                                 |                                                |       | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}\mbox{C} \leq \mbox{Ta} \leq +85^{\circ}\mbox{C for Industrial} \\ & -40^{\circ}\mbox{C} \leq \mbox{Ta} \leq +125^{\circ}\mbox{C for Extended} \end{array}$ |     |            |       |                                          |  |  |  |

|--------------------|-----------|-----------------------------------------------------------------|------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-------|------------------------------------------|--|--|--|

| Param<br>No.       | Symbol    | Characte                                                        | eristic                                        |       | Min                                                                                                                                                                                                                                                                                                               | Тур | Max        | Units | Conditions                               |  |  |  |

| TA10               | ТтхН      | TxCK High Time                                                  | Synchro<br>no presc                            |       | 0.5 Tcy + 20                                                                                                                                                                                                                                                                                                      | —   | _          | ns    | Must also meet parameter TA15            |  |  |  |

|                    |           |                                                                 | Synchronous,<br>with prescaler<br>Asynchronous |       | 10                                                                                                                                                                                                                                                                                                                | _   | —          | ns    |                                          |  |  |  |

|                    |           |                                                                 |                                                |       | 10                                                                                                                                                                                                                                                                                                                | —   | —          | ns    |                                          |  |  |  |

| TA11               | TTXL      | TxCK Low Time Synchronous<br>no prescaler                       |                                                |       | 0.5 Tcy + 20                                                                                                                                                                                                                                                                                                      | _   | —          | ns    | Must also meet parameter TA15            |  |  |  |

|                    |           |                                                                 | Synchro<br>with pres                           |       | 10                                                                                                                                                                                                                                                                                                                | _   | —          | ns    |                                          |  |  |  |

|                    |           |                                                                 | Asynchr                                        | onous | 10                                                                                                                                                                                                                                                                                                                | _   | —          | ns    |                                          |  |  |  |

| TA15               | ΤτχΡ      | TxCK Input Period                                               | Synchronous,<br>no prescaler                   |       | Tcy + 10                                                                                                                                                                                                                                                                                                          | _   | —          | ns    |                                          |  |  |  |

|                    |           |                                                                 | Synchro<br>with pres                           |       | Greater of:<br>20 ns or<br>(TCY + 40)/N                                                                                                                                                                                                                                                                           | _   | —          | _     | N = prescale<br>value<br>(1, 8, 64, 256) |  |  |  |

|                    |           |                                                                 | Asynchr                                        | onous | 20                                                                                                                                                                                                                                                                                                                | _   | —          | ns    |                                          |  |  |  |

| OS60               | Ft1       | SOSC1/T1CK oscil<br>frequency range (or<br>by setting bit TCS ( | scillator enabled                              |       | DC                                                                                                                                                                                                                                                                                                                | —   | 50         | kHz   |                                          |  |  |  |

| TA20               | TCKEXTMRL | Delay from Externa<br>Edge to Timer Incre                       |                                                | lock  | 0.5 TCY                                                                                                                                                                                                                                                                                                           |     | 1.5<br>Тсү |       |                                          |  |  |  |

Note 1: Timer1 is a Type A.

| AC CHAI      | RACTERIST             | Standard Operating Conditions: 2.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                 |                    |     |       |                       |  |

|--------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------------|-----|-------|-----------------------|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                                                                                                                                                        | Min             | Тур <sup>(2)</sup> | Мах | Units | Conditions            |  |

| SP70         | TscL                  | SCKx Input Low Time                                                                                                                                                                                  | 30              | —                  |     | ns    | _                     |  |

| SP71         | TscH                  | SCKx Input High Time                                                                                                                                                                                 | 30              | —                  |     | ns    | —                     |  |

| SP72         | TscF                  | SCKx Input Fall Time <sup>(3)</sup>                                                                                                                                                                  | —               | 10                 | 25  | ns    | —                     |  |

| SP73         | TscR                  | SCKx Input Rise Time <sup>(3)</sup>                                                                                                                                                                  | —               | 10                 | 25  | ns    | —                     |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time <sup>(3)</sup>                                                                                                                                                            | —               | —                  | —   | ns    | See parameter<br>D032 |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time <sup>(3)</sup>                                                                                                                                                            | _               | —                  | —   | ns    | See parameter<br>D031 |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                                                                                                                                                            | —               | —                  | 30  | ns    | —                     |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                                                                                                                                                           | 20              | —                  | _   | ns    | —                     |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge                                                                                                                                                         | 20              | —                  | —   | ns    | _                     |  |

| SP50         | TssL2scH,<br>TssL2scL | SSx↓ to SCKx↑ or SCKx↓ Input                                                                                                                                                                         | 120             | _                  | _   | ns    |                       |  |

| SP51         | TssH2doZ              | SSx↑ to SDOx Output<br>Hi-Impedance <sup>(3)</sup>                                                                                                                                                   | 10              | —                  | 50  | ns    | —                     |  |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCK Edge                                                                                                                                                                                   | 1.5 TCY +<br>40 | —                  | —   | ns    | —                     |  |

## TABLE 23-33: SPI MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: Assumes 50 pF load on all SPI pins.

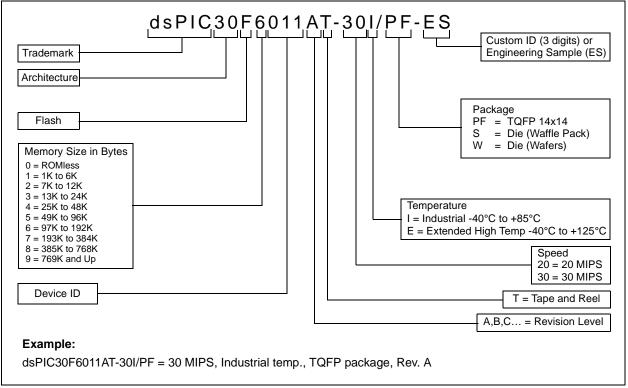

# PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.