Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20 MIPS                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                     |

| Number of I/O              | 68                                                                             |

| Program Memory Size        | 132KB (44K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 2K x 8                                                                         |

| RAM Size                   | 6K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 16x12b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 80-TQFP                                                                        |

| Supplier Device Package    | 80-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f6013t-20i-pf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "dsPIC30F/33F Programmer's Reference Manual" (DS70157).

This document contains specific information for the dsPIC30F6011/6012/6013/6014 Digital Signal Controller (DSC) devices. The dsPIC30F devices contain extensive Digital Signal Processor (DSP) functionality within a high-performance 16-bit microcontroller (MCU) architecture. Figure 1-1 and Figure 1-2 show device block diagrams for dsPIC30F6011/6012 and dsPIC30F6013/6014 respectively.

### 6.0 FLASH PROGRAM MEMORY

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "dsPIC30F/33F Programmer's Reference Manual" (DS70157).

The dsPIC30F family of devices contains internal program Flash memory for executing user code. There are two methods by which the user can program this memory:

- 1. Run-Time Self-Programming (RTSP)

- 2. In-Circuit Serial Programming (ICSP)

# 6.1 In-Circuit Serial Programming (ICSP)

dsPIC30F devices can be serially programmed while in the end application circuit. This is simply done with two lines for Programming Clock and Programming Data (which are named PGC and PGD respectively), and three other lines for Power (VDD), Ground (Vss) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

# 6.2 Run-Time Self-Programming (RTSP)

RTSP is accomplished using  ${\tt TBLRD}$  (table read) and  ${\tt TBLWT}$  (table write) instructions.

With RTSP, the user may erase program memory, 32 instructions (96 bytes) at a time and can write program memory data, 32 instructions (96 bytes) at a time.

# 6.3 Table Instruction Operation Summary

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in Word or Byte mode.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can access program memory in Word or Byte mode.

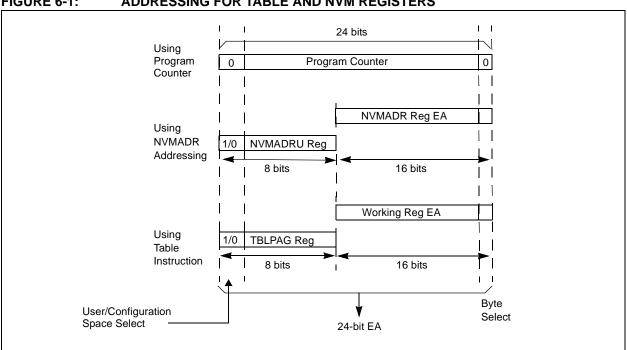

A 24-bit program memory address is formed using bits<7:0> of the TBLPAG register and the effective address (EA) from a W register specified in the table instruction, as shown in Figure 6-1.

FIGURE 6-1: ADDRESSING FOR TABLE AND NVM REGISTERS

### 7.4 Write Verify

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

### 7.5 Protection Against Spurious Write

There are conditions when the device may not want to write to the data EEPROM memory. To protect against spurious EEPROM writes, various mechanisms have been built-in. On power-up, the WREN bit is cleared; also, the Power-up Timer prevents EEPROM write.

The write initiate sequence and the WREN bit together help prevent an accidental write during brown-out, power glitch, or software malfunction.

### 8.0 I/O PORTS

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKI) are shared between the peripherals and the parallel I/O ports.

All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

### 8.1 Parallel I/O (PIO) Ports

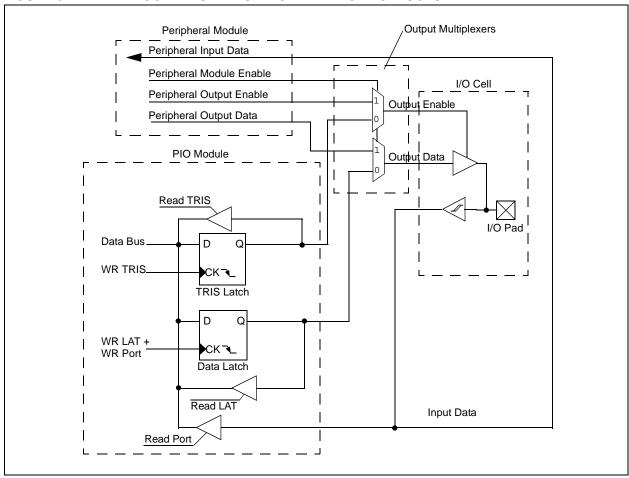

When a peripheral is enabled and the peripheral is actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read but the output driver for the parallel port bit will be disabled. If a peripheral is enabled but the peripheral is not actively driving a pin, that pin may be driven by a port.

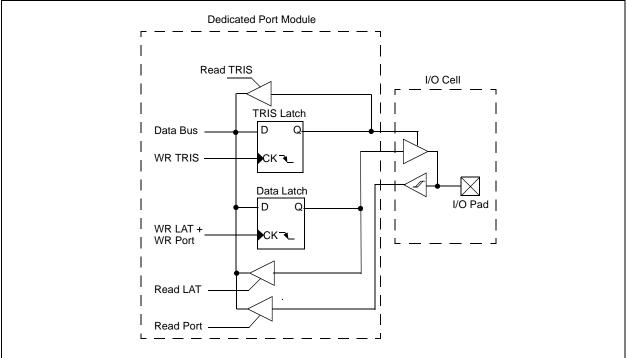

All port pins have three registers directly associated with the operation of the port pin. The Data Direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch (LATx). Reads from the port (PORTx), read the port pins and writes to the port pins, write the latch (LATx).

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pin will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs. An example is the INT4 pin.

The format of the registers for PORTA are shown in Table 8-1.

The TRISA (Data Direction Control) register controls the direction of the RA<7:0> pins, as well as the INTx pins and the VREF pins. The LATA register supplies data to the outputs and is readable/writable. Reading the PORTA register yields the state of the input pins, while writing the PORTA register modifies the contents of the LATA register.

A parallel I/O (PIO) port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pad cell. Figure 8-2 shows how ports are shared with other peripherals and the associated I/O cell (pad) to which they are connected. Table 8-2 through Table 8-9 show the formats of the registers for the shared ports, PORTB through PORTG.

**Note:** The actual bits in use vary between devices.

FIGURE 8-1: BLOCK DIAGRAM OF A DEDICATED PORT STRUCTURE

### 8.2 Configuring Analog Port Pins

The use of the ADPCFG and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

When reading the Port register, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) may cause the input buffer to consume current that exceeds the device specifications.

FIGURE 8-2: BLOCK DIAGRAM OF A SHARED PORT STRUCTURE

### 8.3 Input Change Notification Module

The input change notification module provides the dsPIC30F devices the ability to generate interrupt requests to the processor, in response to a change of state on selected input pins. This module is capable of detecting input change of states even in Sleep mode, when the clocks are disabled. There are up to 24 external signals (CN0 through CN23) that may be selected (enabled) for generating an interrupt request on a change of state.

TABLE 8-10: INPUT CHANGE NOTIFICATION REGISTER MAP FOR dsPIC30F6011/6012 (BITS 15-8)

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Reset State         |

|-------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|---------------------|

| CNEN1       | 00C0  | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | 0000 0000 0000 0000 |

| CNEN2       | 00C2  | _       | _       | _       | _       | _       | _       | _      | _      | 0000 0000 0000 0000 |

| CNPU1       | 00C4  | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | 0000 0000 0000 0000 |

| CNPU2       | 00C6  | _       | _       | _       | _       | _       | _       | _      | _      | 0000 0000 0000 0000 |

**Note:** Refer to "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

TABLE 8-11: INPUT CHANGE NOTIFICATION REGISTER MAP FOR dsPIC30F6011/6012 (BITS 7-0)

| SFR<br>Name | Addr. | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2   | Bit 1   | Bit 0   | Reset State         |

|-------------|-------|--------|--------|--------|--------|--------|---------|---------|---------|---------------------|

| CNEN1       | 00C0  | CN7IE  | CN6IE  | CN5IE  | CN4IE  | CN3IE  | CN2IE   | CN1IE   | CN0IE   | 0000 0000 0000 0000 |

| CNEN2       | 00C2  | _      | _      | _      | _      | _      | CN18IE  | CN17IE  | CN16IE  | 0000 0000 0000 0000 |

| CNPU1       | 00C4  | CN7PUE | CN6PUE | CN5PUE | CN4PUE | CN3PUE | CN2PUE  | CN1PUE  | CN0PUE  | 0000 0000 0000 0000 |

| CNPU2       | 00C6  | _      | _      | _      | _      | _      | CN18PUE | CN17PUE | CN16PUE | 0000 0000 0000 0000 |

**Note:** Refer to "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

TABLE 8-12: INPUT CHANGE NOTIFICATION REGISTER MAP FOR dsPIC30F6013/6014 (BITS 15-8)

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Reset State         |

|-------------|-------|---------|---------|---------|---------|---------|---------|--------|--------|---------------------|

| CNEN1       | 00C0  | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | 0000 0000 0000 0000 |

| CNEN2       | 00C2  | _       | _       | _       | _       | _       | _       | _      | _      | 0000 0000 0000 0000 |

| CNPU1       | 00C4  | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | 0000 0000 0000 0000 |

| CNPU2       | 00C6  | -       | _       | -       | -       | -       | _       | ı      | -      | 0000 0000 0000 0000 |

**Note:** Refer to "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

TABLE 8-13: INPUT CHANGE NOTIFICATION REGISTER MAP FOR dsPIC30F6013/6014 (BITS 7-0)

| SFR<br>Name | Addr. | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Reset State         |

|-------------|-------|---------|---------|---------|---------|---------|---------|---------|---------|---------------------|

| CNEN1       | 00C0  | CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE   | 0000 0000 0000 0000 |

| CNEN2       | 00C2  | CN23IE  | CN22IE  | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE  | 0000 0000 0000 0000 |

| CNPU1       | 00C4  | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | CN0PUE  | 0000 0000 0000 0000 |

| CNPU2       | 00C6  | CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE | 0000 0000 0000 0000 |

**Note:** Refer to "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

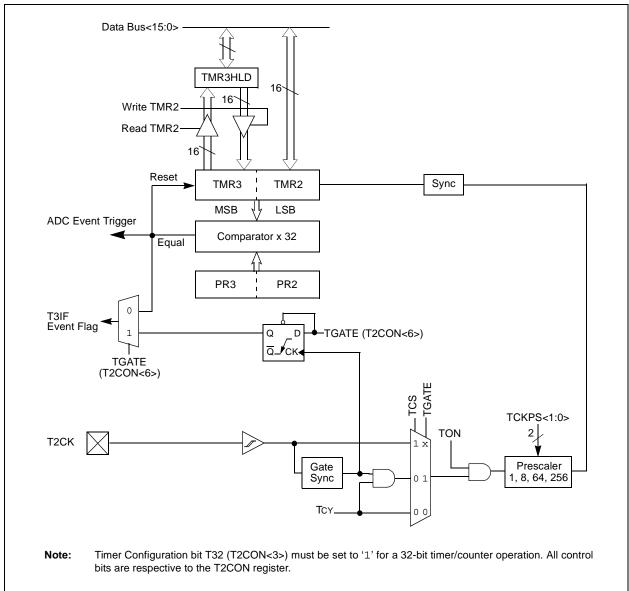

FIGURE 10-1: 32-BIT TIMER2/3 BLOCK DIAGRAM

NOTES:

#### 15.4.2 10-BIT MODE SLAVE RECEPTION

Once addressed, the master can generate a Repeated Start, reset the high byte of the address and set the R\_W bit without generating a Stop bit, thus initiating a slave transmit operation.

### 15.5 Automatic Clock Stretch

In the Slave modes, the module can synchronize buffer reads and write to the master device by clock stretching.

### 15.5.1 TRANSMIT CLOCK STRETCHING

Both 10-bit and 7-bit Transmit modes implement clock stretching by asserting the SCLREL bit after the falling edge of the ninth clock, if the TBF bit is cleared, indicating the buffer is empty.

In Slave Transmit modes, clock stretching is always performed irrespective of the STREN bit.

Clock synchronization takes place following the ninth clock of the transmit sequence. If the device samples an  $\overline{ACK}$  on the falling edge of the ninth clock and if the TBF bit is still clear, then the SCLREL bit is automatically cleared. The SCLREL being cleared to '0' will assert the SCL line low. The user's ISR must set the SCLREL bit before transmission is allowed to continue. By holding the SCL line low, the user has time to service the ISR and load the contents of the I2CTRN before the master device can initiate another transmit sequence.

- Note 1: If the user loads the contents of I2CTRN, setting the TBF bit before the falling edge of the ninth clock, the SCLREL bit will not be cleared and clock stretching will not occur.

- **2:** The SCLREL bit can be set in software, regardless of the state of the TBF bit.

### 15.5.2 RECEIVE CLOCK STRETCHING

The STREN bit in the I2CCON register can be used to enable clock stretching in Slave Receive mode. When the STREN bit is set, the SCL pin will be held low at the end of each data receive sequence.

### 15.5.3 CLOCK STRETCHING DURING 7-BIT ADDRESSING (STREN = 1)

When the STREN bit is set in Slave Receive mode, the SCL line is held low when the buffer register is full. The method for stretching the SCL output is the same for both 7 and 10-bit addressing modes.

Clock stretching takes place following the ninth clock of the receive sequence. On the falling edge of the ninth clock at the end of the ACK sequence, if the RBF bit is set, the SCLREL bit is automatically cleared, forcing the SCL output to be held low. The user's ISR must set the SCLREL bit before reception is allowed to continue. By holding the SCL line low, the user has time to service the ISR and read the contents of the I<sup>2</sup>CRCV before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring.

- Note 1: If the user reads the contents of the I2CRCV, clearing the RBF bit before the falling edge of the ninth clock, the SCLREL bit will not be cleared and clock stretching will not occur.

- 2: The SCLREL bit can be set in software regardless of the state of the RBF bit. The user should be careful to clear the RBF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

### 15.5.4 CLOCK STRETCHING DURING 10-BIT ADDRESSING (STREN = 1)

Clock stretching takes place automatically during the addressing sequence. Because this module has a register for the entire address, it is not necessary for the protocol to wait for the address to be updated.

After the address phase is complete, clock stretching will occur on each data receive or transmit sequence as was described earlier.

### 15.6 Software Controlled Clock Stretching (STREN = 1)

When the STREN bit is '1', the SCLREL bit may be cleared by software to allow software to control the clock stretching. The logic will synchronize writes to the SCLREL bit with the SCL clock. Clearing the SCLREL bit will not assert the SCL output until the module detects a falling edge on the SCL output and SCL is sampled low. If the SCLREL bit is cleared by the user while the SCL line has been sampled low, the SCL output will be asserted (held low). The SCL output will remain low until the SCLREL bit is set, and all other devices on the I<sup>2</sup>C bus have de-asserted SCL. This ensures that a write to the SCLREL bit will not violate the minimum high time requirement for SCL.

If the STREN bit is '0', a software write to the SCLREL bit will be disregarded and have no effect on the SCLREL bit.

### 15.7 Interrupts

The I<sup>2</sup>C module generates two interrupt flags, MI2CIF (I<sup>2</sup>C Master Interrupt Flag) and SI2CIF (I<sup>2</sup>C Slave Interrupt Flag). The MI2CIF interrupt flag is activated on completion of a master message event. The SI2CIF interrupt flag is activated on detection of a message directed to the slave.

#### 15.12.3 BAUD RATE GENERATOR

In I<sup>2</sup>C Master mode, the reload value for the BRG is located in the I2CBRG register. When the BRG is loaded with this value, the BRG counts down to '0' and stops until another reload has taken place. If clock arbitration is taking place, for instance, the BRG is reloaded when the SCL pin is sampled high.

As per the I<sup>2</sup>C standard, FSCK may be 100 kHz or 400 kHz. However, the user can specify any baud rate up to 1 MHz. I2CBRG values of '0' or '1' are illegal.

### **EQUATION 15-1: SERIAL CLOCK RATE**

$$I2CBRG = \left(\frac{FCY}{FSCK} - \frac{FCY}{1,111,111}\right) - 1$$

### 15.12.4 CLOCK ARBITRATION

Clock arbitration occurs when the master de-asserts the SCL pin (SCL allowed to float high) during any receive, transmit, or Restart/Stop condition. When the SCL pin is allowed to float high, the Baud Rate Generator is suspended from counting until the SCL pin is actually sampled high. When the SCL pin is sampled high, the Baud Rate Generator is reloaded with the contents of I2CBRG and begins counting. This ensures that the SCL high time will always be at least one BRG rollover count in the event that the clock is held low by an external device.

### 15.12.5 MULTI-MASTER COMMUNICATION, BUS COLLISION, AND BUS ARBITRATION

Multi-master operation support is achieved by bus arbitration. When the master outputs address/data bits onto the SDA pin, arbitration takes place when the master outputs a '1' on SDA by letting SDA float high while another master asserts a '0'. When the SCL pin floats high, data should be stable. If the expected data on SDA is a '1' and the data sampled on the SDA pin = 0, then a bus collision has taken place. The master will set the MI2CIF pulse and reset the master portion of the  $I^2C$  port to its Idle state.

If a transmit was in progress when the bus collision occurred, the transmission is halted, the TBF flag is cleared, the SDA and SCL lines are de-asserted and a value can now be written to I2CTRN. When the user services the  $\rm I^2C$  master event Interrupt Service Routine, if the  $\rm I^2C$  bus is free (i.e., the P bit is set), the user can resume communication by asserting a Start condition.

If a Start, Restart, Stop or Acknowledge condition was in progress when the bus collision occurred, the condition is aborted, the SDA and SCL lines are de-asserted, and the respective control bits in the I2CCON register are cleared to '0'. When the user services the bus collision Interrupt Service Routine, and if the I<sup>2</sup>C bus is free, the user can resume communication by asserting a Start condition.

The master will continue to monitor the SDA and SCL pins, and if a Stop condition occurs, the MI2CIF bit will be set.

A write to the I2CTRN will start the transmission of data at the first data bit regardless of where the transmitter left off when bus collision occurred.

In a multi-master environment, the interrupt generation on the detection of Start and Stop conditions allows the determination of when the bus is free. Control of the  $I^2C$  bus can be taken when the P bit is set in the I2CSTAT register, or the bus is Idle and the S and P bits are cleared.

# 15.13 I<sup>2</sup>C Module Operation During CPU Sleep and Idle Modes

### 15.13.1 I<sup>2</sup>C OPERATION DURING CPU SLEEP MODE

When the device enters Sleep mode, all clock sources to the module are shutdown and stay at logic '0'. If Sleep occurs in the middle of a transmission and the state machine is partially into a transmission as the clocks stop, then the transmission is aborted. Similarly, if Sleep occurs in the middle of a reception, then the reception is aborted.

# 15.13.2 I<sup>2</sup>C OPERATION DURING CPU IDLE MODE

For the I $^2$ C, the I2CSIDL bit selects if the module will stop on Idle or continue on Idle. If I2CSIDL = 0, the module will continue operation on assertion of the Idle mode. If I2CSIDL = 1, the module will stop on Idle.

#### 16.3.4 TRANSMIT INTERRUPT

The transmit interrupt flag (U1TXIF or U2TXIF) is located in the corresponding interrupt flag register.

The transmitter generates an edge to set the UxTXIF bit. The condition for generating the interrupt depends on the UTXISEL control bit:

- a) If UTXISEL = 0, an interrupt is generated when a word is transferred from the transmit buffer to the Transmit Shift register (UxTSR). This implies that the transmit buffer has at least one empty word.

- b) If UTXISEL = 1, an interrupt is generated when a word is transferred from the transmit buffer to the Transmit Shift register (UxTSR) and the transmit buffer is empty.

Switching between the two Interrupt modes during operation is possible and sometimes offers more flexibility.

### 16.3.5 TRANSMIT BREAK

Setting the UTXBRK bit (UxSTA<11>) will cause the UxTX line to be driven to logic '0'. The UTXBRK bit overrides all transmission activity. Therefore, the user should generally wait for the transmitter to be Idle before setting UTXBRK.

To send a break character, the UTXBRK bit must be set by software and must remain set for a minimum of 13 baud clock cycles. The UTXBRK bit is then cleared by software to generate Stop bits. The user must wait for a duration of at least one or two baud clock cycles in order to ensure a valid Stop bit(s) before reloading the UxTXB, or starting other transmitter activity. Transmission of a break character does not generate a transmit interrupt.

### 16.4 Receiving Data

## 16.4.1 RECEIVING IN 8-BIT OR 9-BIT DATA MODE

The following steps must be performed while receiving 8-bit or 9-bit data:

- 1. Set up the UART (see Section 16.3.1 "Transmitting in 8-bit data mode").

- 2. Enable the UART (see Section 16.3.1 "Transmitting in 8-bit data mode").

- A receive interrupt will be generated when one or more data words have been received, depending on the receive interrupt settings specified by the URXISEL bits (UxSTA<7:6>).

- 4. Read the OERR bit to determine if an overrun error has occurred. The OERR bit must be reset in software.

- Read the received data from UxRXREG. The act of reading UxRXREG will move the next word to the top of the receive FIFO, and the PERR and

FERR values will be updated.

### 16.4.2 RECEIVE BUFFER (UxRXB)

The receive buffer is 4 words deep. Including the Receive Shift register (UxRSR), the user effectively has a 5-word deep FIFO buffer.

URXDA (UxSTA<0>) = 1 indicates that the receive buffer has data available. URXDA = 0 implies that the buffer is empty. If a user attempts to read an empty buffer, the old values in the buffer will be read and no data shift will occur within the FIFO.

The FIFO is reset during any device Reset. It is not affected when the device enters or wakes up from a power-saving mode.

### 16.4.3 RECEIVE INTERRUPT

The receive interrupt flag (U1RXIF or U2RXIF) can be read from the corresponding interrupt flag register. The interrupt flag is set by an edge generated by the receiver. The condition for setting the receive interrupt flag depends on the settings specified by the URXISEL<1:0> (UxSTA<7:6>) control bits.

- a) If URXISEL<1:0> = 00 or 01, an interrupt is generated every time a data word is transferred from the Receive Shift register (UxRSR) to the receive buffer. There may be one or more characters in the receive buffer.

- b) If URXISEL<1:0> = 10, an interrupt is generated when a word is transferred from the Receive Shift register (UxRSR) to the receive buffer, which as a result of the transfer, contains 3 characters.

- c) If URXISEL<1:0> = 11, an interrupt is set when a word is transferred from the Receive Shift register (UxRSR) to the receive buffer, which as a result of the transfer, contains 4 characters (i.e., becomes full).

Switching between the Interrupt modes during operation is possible, though generally not advisable during normal operation.

### 16.5 Reception Error Handling

## 16.5.1 RECEIVE BUFFER OVERRUN ERROR (OERR BIT)

The OERR bit (UxSTA<1>) is set if all of the following conditions occur:

- a) The receive buffer is full.

- b) The Receive Shift register is full, but unable to transfer the character to the receive buffer.

- The Stop bit of the character in the UxRSR is detected, indicating that the UxRSR needs to transfer the character to the buffer.

© 2006 Microchip Technology Inc.

TABLE 17-2: CAN2 REGISTER MAP (CONTINUED)

| SFR Name | Addr. | Bit 15                   | Bit 14                                          | Bit 13                   | Bit 12      | Bit 11      | Bit 10 | Bit 9    | Bit 8                   | Bit 7                                        | Bit 6              | Bit 5        | Bit 4      | Bit 3          | Bit 2              | Bit 1              | Bit 0              | Reset State        |

|----------|-------|--------------------------|-------------------------------------------------|--------------------------|-------------|-------------|--------|----------|-------------------------|----------------------------------------------|--------------------|--------------|------------|----------------|--------------------|--------------------|--------------------|--------------------|

| C2TX1EID | 0412  | Transn                   | nit Buffer 1 I<br><17:                          | Extended Ide<br>:14>     | ntifier     | _           | _      | _        | _                       |                                              | Tr                 | ansmit Buf   | fer 1 Exte | nded Identifie | r <13:6>           |                    |                    | uuuu 0000 uuuu uuu |

| C2TX1DLC | 0414  |                          | Transmit B                                      | Suffer 1 Exter           | nded Ident  | ifier <5:0> |        | TXRTR    | TXRB1                   | TXRB0                                        |                    | DLC          | <3:0>      |                | _                  |                    | _                  | uuuu uuuu uuuu u00 |

| C2TX1B1  | 0416  |                          |                                                 | Tra                      | nsmit Buff  | er 1 Byte 1 |        |          |                         | Transmit Buffer 1 Byte 0                     |                    |              |            |                |                    |                    | uuuu uuuu uuuu uuu |                    |

| C2TX1B2  | 0418  |                          |                                                 | Tra                      | nsmit Buff  | er 1 Byte 3 |        |          |                         |                                              |                    | Tra          | ansmit Bu  | fer 1 Byte 2   |                    |                    |                    | uuuu uuuu uuuu uuu |

| C2TX1B3  | 041A  |                          |                                                 | Tra                      | nsmit Buff  | er 1 Byte 5 |        |          |                         | Transmit Buffer 1 Byte 4                     |                    |              |            |                |                    |                    | uuuu uuuu uuuu uuu |                    |

| C2TX1B4  | 041C  |                          |                                                 | Tra                      | nsmit Buff  | er 1 Byte 7 |        |          |                         |                                              |                    | Tra          | ansmit Bu  | fer 1 Byte 6   |                    |                    |                    | uuuu uuuu uuuu uuu |

| C2TX1CON | 041E  | _                        | _                                               | 1                        | _           | _           | _      | _        | _                       | - TXABT TXLARB TXERR TXREQ - TXPRI<1:0>      |                    |              |            |                | 0000 0000 0000 000 |                    |                    |                    |

| C2TX0SID | 0420  | Tran                     | smit Buffer                                     | 0 Standard Id            | dentifier < | 10:6>       | _      | _        | _                       | Tr                                           | ansmit Bu          | ffer 0 Stand | dard Ident | ifier <5:0>    |                    | SRR                | TXIDE              | uuuu u000 uuuu uuu |

| C2TX0EID | 0422  | Transn                   | nit Buffer 0 I<br><17:                          | Extended Ide<br>:14>     | entifier    | _           | _      | _        | _                       | Transmit Buffer 0 Extended Identifier <13:6> |                    |              |            |                | uuuu 0000 uuuu uuu |                    |                    |                    |

| C2TX0DLC | 0424  |                          | Transmit B                                      | Suffer 0 Exter           | nded Ident  | ifier <5:0> |        | TXRTR    | TXRB1                   | TXRB0 DLC<3:0> — — —                         |                    |              |            |                | uuuu uuuu uuuu u00 |                    |                    |                    |

| C2TX0B1  | 0426  |                          |                                                 | Tra                      | nsmit Buff  | er 0 Byte 1 |        |          |                         |                                              |                    | Tra          | ansmit Bu  | fer 0 Byte 0   |                    |                    |                    | uuuu uuuu uuuu uuu |

| C2TX0B2  | 0428  | Transmit Buffer 0 Byte 3 |                                                 |                          |             |             |        |          |                         |                                              |                    | Tra          | ansmit Bu  | ffer 0 Byte 2  |                    |                    |                    | uuuu uuuu uuuu uuu |

| C2TX0B3  | 042A  | Transmit Buffer 0 Byte 5 |                                                 |                          |             |             |        |          |                         |                                              |                    | Tra          | ansmit Bu  | fer 0 Byte 4   |                    |                    |                    | uuuu uuuu uuuu uuu |

| C2TX0B4  | 042C  |                          |                                                 | Transmit Buffer 0 Byte 7 |             |             |        |          |                         | Transmit Buffer 0 Byte 6                     |                    |              |            |                |                    | uuuu uuuu uuuu uuu |                    |                    |

| C2TX0CON | 042E  | _                        | _                                               | _                        | _           | _           | _      | _        | _                       | _                                            | TXABT              | TXLARB       | TXERR      | TXREQ          | _                  | TXPR               | I<1:0>             | 0000 0000 0000 000 |

| C2RX1SID | 0430  | _                        | _                                               | _                        |             | _           |        | Red      | ceive Buffe             | r 1 Standard Id                              | entifier <1        | 0:0>         |            |                |                    | SRR                | RXIDE              | 000u uuuu uuuu uuu |

| C2RX1EID | 0432  | _                        | _                                               | 1                        | _           |             |        |          |                         | Receive Buffe                                | er 1 Exten         | ded Identifi | er <17:6>  |                |                    |                    |                    | 0000 uuuu uuuu uuu |

| C2RX1DLC | 0434  |                          | Receive B                                       | uffer 1 Exten            | ided Identi | fier <5:0>  |        | RXRTR    | RXRB1                   | _                                            | _                  | _            | RXRB0      |                | DLC                | <3:0>              |                    | uuuu uuuu 000u uuu |

| C2RX1B1  | 0436  |                          | Receive Buffer 1 Byte 1 Receive Buffer 1 Byte 0 |                          |             |             |        |          |                         |                                              | uuuu uuuu uuuu uuu |              |            |                |                    |                    |                    |                    |

| C2RX1B2  | 0438  |                          | Receive Buffer 1 Byte 3                         |                          |             |             |        |          | Receive Buffer 1 Byte 2 |                                              |                    |              |            |                | uuuu uuuu uuu uuu  |                    |                    |                    |

| C2RX1B3  | 043A  |                          |                                                 | Re                       | ceive Buff  | er 1 Byte 5 |        |          |                         |                                              |                    | Re           | ceive Buf  | fer 1 Byte 4   |                    |                    |                    | uuuu uuuu uuu uuu  |

| C2RX1B4  | 043C  |                          |                                                 | Re                       | ceive Buff  | er 1 Byte 7 |        |          |                         |                                              |                    | Re           | ceive Buf  | fer 1 Byte 6   |                    |                    |                    | uuuu uuuu uuu uuu  |

| C2RX1CON | 043E  | _                        | _                                               | 1                        | _           | _           | _      | _        | _                       | RXFUL                                        | _                  | -            | _          | RXRTRRO        |                    | FILHIT<2:0         | 0>                 | 0000 0000 0000 000 |

| C2RX0SID | 0440  | _                        | _                                               | ı                        |             | •           | •      | Red      | eive Buffe              | r 0 Standard Id                              | entifier <1        | 0:0>         | -          | •              |                    | SRR                | RXIDE              | 000u uuuu uuuu uuu |

| C2RX0EID | 0442  | _                        | _                                               | ı                        | _           |             |        |          |                         | Receive Buffe                                | er 0 Exten         | ded Identifi | er <17:6>  |                |                    |                    |                    | 0000 uuuu uuuu uuu |

| C2RX0DLC | 0444  |                          | Receive B                                       | uffer 0 Exten            | ded Identi  | fier <5:0>  |        | RXRTR    | RXRB1                   | _                                            | _                  | _            | RXRB0      |                | DLC                | <3:0>              |                    | uuuu uuuu 000u uuu |

| C2RX0B1  | 0446  |                          |                                                 | Re                       | ceive Buff  | er 0 Byte 1 |        |          |                         |                                              |                    | Re           | ceive Buf  | fer 0 Byte 0   |                    |                    |                    | uuuu uuuu uuuu uuu |

| C2RX0B2  | 0448  |                          |                                                 | Re                       | ceive Buff  | er 0 Byte 3 |        |          |                         |                                              |                    | Re           | ceive Buf  | fer 0 Byte 2   |                    |                    |                    | uuuu uuuu uuuu uuu |

| C2RX0B3  | 044A  |                          |                                                 | Re                       | ceive Buff  | er 0 Byte 5 |        |          |                         |                                              |                    | Re           | ceive Buf  | fer 0 Byte 4   |                    |                    |                    | uuuu uuuu uuu uuu  |

| C2RX0B4  | 044C  |                          |                                                 | Re                       | ceive Buff  | er 0 Byte 7 |        |          |                         |                                              |                    | Re           | ceive But  | fer 0 Byte 6   |                    |                    |                    | uuuu uuuu uuu uuu  |

| C2RX0CON | 044E  |                          |                                                 | _                        | _           | _           | _      | _        |                         | RXFUL                                        | _                  |              | _          | RXRTRRO        | DBEN               | JTOFF              | FILHIT0            | 0000 0000 0000 000 |

| C2CTRL   | 0450  | CANCAP                   | _                                               | CSIDLE                   | ABAT        | CANCKS      | R      | REQOP<2: | 0>                      | OPM                                          | 1ODE<2:0           | >            | _          | ICO            | ODE<2:0            | >                  | _                  | 0000 0100 1000 000 |

| C2CFG1   | 0452  | _                        | _                                               | 1                        | _           | _           | _      | _        | _                       | SJW<1                                        | :0>                |              |            | BRP<5          | :0>                |                    |                    | 0000 0000 0000 000 |

| C2CFG2   | 0454  | _                        | WAKFIL                                          | _                        | _           | _           | S      | EG2PH<2  | :0>                     | SEG2PHTS                                     | SAM                | S            | EG1PH<     | 2:0>           |                    | PRSEG<2:           | 0>                 | 0u00 0uuu uuuu uuu |

**Legend:** u = uninitialized bit

Refer to "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields. Note:

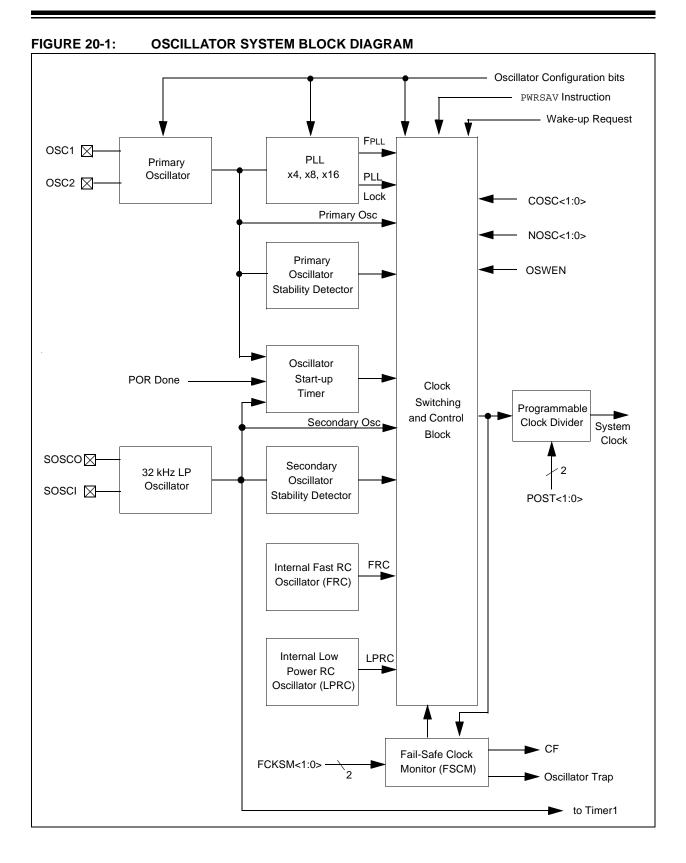

TABLE 20-1: OSCILLATOR OPERATING MODES

| Oscillator Mode | Description                                                                         |

|-----------------|-------------------------------------------------------------------------------------|

| XTL             | 200 kHz-4 MHz crystal on OSC1:OSC2.                                                 |

| XT              | 4 MHz-10 MHz crystal on OSC1:OSC2.                                                  |

| XT w/PLL 4x     | 4 MHz-10 MHz crystal on OSC1:OSC2, 4x PLL enabled.                                  |

| XT w/PLL 8x     | 4 MHz-10 MHz crystal on OSC1:OSC2, 8x PLL enabled.                                  |

| XT w/PLL 16x    | 4 MHz-10 MHz crystal on OSC1:OSC2, 16x PLL enabled <sup>(1)</sup> .                 |

| LP              | 32 kHz crystal on SOSCO:SOSCI <sup>(2)</sup> .                                      |

| HS              | 10 MHz-25 MHz crystal.                                                              |

| EC              | External clock input (0-40 MHz).                                                    |

| ECIO            | External clock input (0-40 MHz), OSC2 pin is I/O.                                   |

| EC w/PLL 4x     | External clock input (4-10 MHz), OSC2 pin is I/O, 4x PLL enabled <sup>(1)</sup> .   |

| EC w/PLL 8x     | External clock input (4-10 MHz), OSC2 pin is I/O, 8x PLL enabled <sup>(1)</sup> .   |

| EC w/PLL 16x    | External clock input (4-7.5 MHz), OSC2 pin is I/O, 16x PLL enabled <sup>(1)</sup> . |

| ERC             | External RC oscillator, OSC2 pin is Fosc/4 output <sup>(3)</sup> .                  |

| ERCIO           | External RC oscillator, OSC2 pin is I/O <sup>(3)</sup> .                            |

| FRC             | 7.37 MHz internal RC oscillator.                                                    |

| LPRC            | 512 kHz internal RC oscillator.                                                     |

**Note 1:** dsPIC30F maximum operating frequency of 120 MHz must be met.

2: LP oscillator can be conveniently shared as system clock, as well as real-time clock for Timer1.

3: Requires external R and C. Frequency operation up to 4 MHz.

NOTES:

All instructions are a single word, except for certain double-word instructions, which were made double-word instructions so that all the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes, and RETURN/RETFIE instructions,

which are single-word instructions but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single word or two-word instruction. Moreover, double-word moves require two cycles. The double-word instructions execute in two instruction cycles.

**Note:** For more details on the instruction set, refer to the "dsPIC30F/33F Programmer's Reference Manual" (DS70157)

TABLE 21-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Field           | Description                                                                 |

|-----------------|-----------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                             |

| (text)          | Means "content of text"                                                     |

| [text]          | Means "the location addressed by text"                                      |

| { }             | Optional field or operation                                                 |

| <n:m></n:m>     | Register bit field                                                          |

| .b              | Byte mode selection                                                         |

| .d              | Double-Word mode selection                                                  |

| .S              | Shadow register select                                                      |

| .w              | Word mode selection (default)                                               |

| Acc             | One of two accumulators {A, B}                                              |

| AWB             | Accumulator write back destination address register ∈ {W13, [W13]+=2}       |

| bit4            | 4-bit bit selection field (used in word addressed instructions) ∈ {015}     |

| C, DC, N, OV, Z | MCU status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero        |

| Expr            | Absolute address, label or expression (resolved by the linker)              |

| f               | File register address ∈ {0x00000x1FFF}                                      |

| lit1            | 1-bit unsigned literal ∈ {0,1}                                              |

| lit4            | 4-bit unsigned literal ∈ {015}                                              |

| lit5            | 5-bit unsigned literal ∈ {031}                                              |

| lit8            | 8-bit unsigned literal ∈ {0255}                                             |

| lit10           | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode      |

| lit14           | 14-bit unsigned literal ∈ {016384}                                          |

| lit16           | 16-bit unsigned literal ∈ {065535}                                          |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSB must be 0                         |

| None            | Field does not require an entry, may be blank                               |

| OA, OB, SA, SB  | DSP status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate |

| PC              | Program Counter                                                             |

| Slit10          | 10-bit signed literal ∈ {-512511}                                           |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                       |

| Slit6           | 6-bit signed literal ∈ {-1616}                                              |

### 23.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC30F electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

For detailed information about the dsPIC30F architecture and core, refer to "dsPIC30F Family Reference Manual" (DS70046).

Absolute maximum ratings for the dsPIC30F family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

### Absolute Maximum Ratings(†)

| Ambient temperature under bigs                                                  | 40°C to 1125°C       |

|---------------------------------------------------------------------------------|----------------------|

| Ambient temperature under bias                                                  |                      |

| Storage temperature                                                             | 65°C to +150°C       |

| Voltage on any pin with respect to Vss (except VDD and MCLR) (Note 1)           | 0.3V to (VDD + 0.3V) |

| Voltage on VDD with respect to Vss                                              | 0.3V to +5.5V        |

| Voltage on MCLR with respect to Vss                                             | 0V to +13.25V        |

| Maximum current out of Vss pin                                                  | 300 mA               |

| Maximum current into VDD pin (Note 2)                                           | 250 mA               |

| Input clamp current, IiK (VI < 0 or VI > VDD)                                   | ±20 mA               |

| Output clamp current, IOK (VO < 0 or VO > VDD)                                  | ±20 mA               |

| Maximum output current sunk by any I/O pin                                      | 25 mA                |

| Maximum output current sourced by any I/O pin                                   | 25 mA                |

| Maximum current sunk by all ports                                               | 200 mA               |

| Maximum current sourced by all ports (Note 2)                                   | 200 mA               |

| Note 1: Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater |                      |

**Note 1:** Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater than 80 mA, may cause latchup. Thus, a series resistor of 50-100Ω should be used when applying a "low" level to the MCLR/VPP pin, rather than pulling this pin directly to Vss.

2: Maximum allowable current is a function of device maximum power dissipation. See Table 23-2 for PDMAX.

<sup>†</sup>NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

**Note:** All peripheral electrical characteristics are specified. For exact peripherals available on specific devices, please refer the Family Cross Reference Table.

### 23.1 DC Characteristics

TABLE 23-1: OPERATING MIPS VS. VOLTAGE

| Vpp Bongo | Temp Range     | Max MIPS         |                  |                  |  |  |  |  |  |

|-----------|----------------|------------------|------------------|------------------|--|--|--|--|--|

| VDD Range | Temp Kange     | dsPIC30F601X-30I | dsPIC30F601X-20I | dsPIC30F601X-20E |  |  |  |  |  |

| 4.75-5.5V | -40°C to 85°C  | 30               | 20               | _                |  |  |  |  |  |

| 4.75-5.5V | -40°C to 125°C | _                | _                | 20               |  |  |  |  |  |

| 3.0-3.6V  | -40°C to 85°C  | 15               | 10               | _                |  |  |  |  |  |

| 3.0-3.6V  | -40°C to 125°C | _                | _                | 10               |  |  |  |  |  |

| 2.5-3.0V  | -40°C to 85°C  | 7.5              | 7.5              | _                |  |  |  |  |  |

TABLE 23-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                                             | Symbol         | Min                                 | Тур                        | Max  | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------------------------|----------------------------|------|------|

| dsPIC30F601x-30I                                                                                                                                                                                                   |                |                                     |                            |      |      |

| Operating Junction Temperature Range                                                                                                                                                                               | $T_J$          | -40                                 |                            | +125 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                                                | $T_A$          | -40                                 |                            | +85  | °C   |

| dsPIC30F601x-20I                                                                                                                                                                                                   |                |                                     |                            |      |      |

| Operating Junction Temperature Range                                                                                                                                                                               | $T_J$          | -40                                 |                            | +150 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                                                | T <sub>A</sub> | -40                                 |                            | +85  | °C   |

| dsPIC30F601x-20E                                                                                                                                                                                                   |                |                                     |                            |      |      |

| Operating Junction Temperature Range                                                                                                                                                                               | $T_J$          | -40                                 |                            | +150 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                                                | $T_A$          | -40                                 |                            | +125 | °C   |

| Power Dissipation: Internal chip power dissipation: $P_{INT} = V_{DD} \times (I_{DD} - \sum I_{OH})$ I/O Pin power dissipation: $P_{I/O} = \sum (\{V_{DD} - V_{OH}\} \times I_{OH}) + \sum (V_{OL} \times I_{OL})$ | P <sub>D</sub> | P <sub>INT</sub> + P <sub>I/O</sub> |                            |      | W    |

| Maximum Allowed Power Dissipation                                                                                                                                                                                  | Ромах          | (7                                  | $\Gamma_J - T_A) / \Theta$ | JA   | W    |

### **TABLE 23-3: THERMAL PACKAGING CHARACTERISTICS**

| Characteristic                                      | Symbol            | Тур | Max | Unit | Notes |

|-----------------------------------------------------|-------------------|-----|-----|------|-------|

| Package Thermal Resistance, 80-pin TQFP (14x14x1mm) | $\theta_{\sf JA}$ |     | 50  | °C/W | 1     |

| Package Thermal Resistance, 64-pin TQFP (14x14x1mm) | $\theta_{\sf JA}$ |     | 50  | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-ja  $(\theta_{JA})$  numbers are achieved by package simulations.

### TABLE 23-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS              |                                  |                                                                  | Standard Operating Co.<br>(unless otherwise state<br>Operating temperature |                    |     |       |                                  |  |  |

|---------------------------------|----------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------|-----|-------|----------------------------------|--|--|

| Param No. Symbol Characteristic |                                  |                                                                  | Min                                                                        | Typ <sup>(1)</sup> | Max | Units | Conditions                       |  |  |

| Operatir                        | Operating Voltage <sup>(2)</sup> |                                                                  |                                                                            |                    |     |       |                                  |  |  |

| DC10                            | VDD                              | Supply Voltage                                                   | 2.5                                                                        | _                  | 5.5 | V     | Industrial temperature           |  |  |

| DC11                            | VDD                              | Supply Voltage                                                   | 3.0                                                                        | _                  | 5.5 | V     | Extended temperature             |  |  |

| DC12                            | VDR                              | RAM Data Retention Voltage <sup>(3)</sup>                        | _                                                                          | 1.5                | _   | V     |                                  |  |  |

| DC16                            | VPOR                             | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal | _                                                                          | Vss                | _   | V     |                                  |  |  |

| DC17                            | SVDD                             | VDD Rise Rate<br>to ensure internal<br>Power-on Reset signal     | 0.05                                                                       |                    |     | V/ms  | 0-5V in 0.1 sec<br>0-3V in 60 ms |  |  |

Note 1: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: These parameters are characterized but not tested in manufacturing.

- 3: This is the limit to which VDD can be lowered without losing RAM data.

TABLE 23-15: PLL CLOCK TIMING SPECIFICATIONS (VDD = 2.5 TO 5.5 V)

| AC CHARACTERISTICS |                      |                                   | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                                         |    |                    |     |                       |

|--------------------|----------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----|--------------------|-----|-----------------------|

| Param<br>No.       | Sympol Characteristi |                                   |                                                                                                                                                                                                                                                     | Min Typ <sup>(2)</sup> Max Units Condit |    |                    |     |                       |

| OS50               | FPLLI                | PLL Input Frequency               | Range <sup>(2)</sup>                                                                                                                                                                                                                                | 4                                       | _  | 10                 | MHz | EC with 4x PLL        |

|                    |                      |                                   |                                                                                                                                                                                                                                                     | 4                                       | _  | 10                 | MHz | EC with 8x PLL        |

|                    |                      |                                   |                                                                                                                                                                                                                                                     | 4                                       | _  | 7.5 <sup>(3)</sup> | MHz | EC with 16x PLL       |

|                    |                      |                                   |                                                                                                                                                                                                                                                     | 4                                       | _  | 10                 | MHz | XT with 4x PLL        |

|                    |                      |                                   |                                                                                                                                                                                                                                                     | 4                                       | _  | 10                 | MHz | XT with 8x PLL        |

|                    |                      |                                   |                                                                                                                                                                                                                                                     | 4                                       | _  | 7.5 <sup>(3)</sup> | MHz | XT with 16x PLL       |

| OS51               | Fsys                 | On-Chip PLL Output <sup>(2)</sup> |                                                                                                                                                                                                                                                     | 16                                      | _  | 120                | MHz | EC, XT modes with PLL |

| OS52               | TLOC                 | PLL Start-up Time (L              | ock Time)                                                                                                                                                                                                                                           | _                                       | 20 | 50                 | μs  |                       |

- Note 1: These parameters are characterized but not tested in manufacturing.

- 2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: Limited by device operating frequency range.

### **TABLE 23-16: PLL JITTER**

| AC CHARACTERISTICS |                | Standard Operating Conditions: 2.5V to 5.5V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |                    |       |       |                     |                     |  |  |

|--------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------|-------|---------------------|---------------------|--|--|

| Param<br>No.       | Characteristic | Min                                                                                                                                                                                                                                              | Typ <sup>(1)</sup> | Max   | Units | Conditions          |                     |  |  |

| OS61               | x4 PLL         | _                                                                                                                                                                                                                                                | 0.251              | 0.413 | %     | -40°C ≤ TA ≤ +85°C  | VDD = 3.0  to  3.6V |  |  |

|                    |                | _                                                                                                                                                                                                                                                | 0.251              | 0.413 | %     | -40°C ≤ TA ≤ +125°C | VDD = 3.0  to  3.6V |  |  |

|                    |                | _                                                                                                                                                                                                                                                | 0.256              | 0.47  | %     | -40°C ≤ TA ≤ +85°C  | VDD = 4.5  to  5.5V |  |  |

|                    |                | _                                                                                                                                                                                                                                                | 0.256              | 0.47  | %     | -40°C ≤ TA ≤ +125°C | VDD = 4.5  to  5.5V |  |  |

|                    | x8 PLL         | _                                                                                                                                                                                                                                                | 0.355              | 0.584 | %     | -40°C ≤ TA ≤ +85°C  | VDD = 3.0  to  3.6V |  |  |

|                    |                | _                                                                                                                                                                                                                                                | 0.355              | 0.584 | %     | -40°C ≤ TA ≤ +125°C | VDD = 3.0  to  3.6V |  |  |

|                    |                | _                                                                                                                                                                                                                                                | 0.362              | 0.664 | %     | -40°C ≤ TA ≤ +85°C  | VDD = 4.5  to  5.5V |  |  |

|                    |                |                                                                                                                                                                                                                                                  | 0.362              | 0.664 | %     | -40°C ≤ TA ≤ +125°C | VDD = 4.5  to  5.5V |  |  |

|                    | x16 PLL        | _                                                                                                                                                                                                                                                | 0.67               | 0.92  | %     | -40°C ≤ TA ≤ +85°C  | VDD = 3.0  to  3.6V |  |  |

|                    |                | _                                                                                                                                                                                                                                                | 0.632              | 0.956 | %     | -40°C ≤ TA ≤ +85°C  | VDD = 4.5  to  5.5V |  |  |

|                    |                | _                                                                                                                                                                                                                                                | 0.632              | 0.956 | %     | -40°C ≤ TA ≤ +125°C | VDD = 4.5  to  5.5V |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

### **TABLE 23-17: INTERNAL CLOCK TIMING EXAMPLES**

| Clock<br>Oscillator<br>Mode | Fosc<br>(MHz) <sup>(1)</sup> | Tcγ (μsec) <sup>(2)</sup> | MIPS <sup>(3)</sup><br>w/o PLL | MIPS <sup>(3)</sup><br>w/PLL x4 | MIPS <sup>(3)</sup><br>w/PLL x8 | MIPS <sup>(3)</sup><br>w/PLL x16 |

|-----------------------------|------------------------------|---------------------------|--------------------------------|---------------------------------|---------------------------------|----------------------------------|

| EC                          | 0.200                        | 20.0                      | 0.05                           | _                               | _                               | _                                |

|                             | 4                            | 1.0                       | 1.0                            | 4.0                             | 8.0                             | 16.0                             |

|                             | 10                           | 0.4                       | 2.5                            | 10.0                            | 20.0                            | _                                |

|                             | 25                           | 0.16                      | 6.25                           | _                               | _                               | _                                |

| XT                          | 4                            | 1.0                       | 1.0                            | 4.0                             | 8.0                             | 16.0                             |

|                             | 10                           | 0.4                       | 2.5                            | 10.0                            | 20.0                            | _                                |

TABLE 23-39: 12-BIT A/D CONVERSION TIMING REQUIREMENTS

| AC CHARACTERISTICS |                   |                                                       | Standard Operating Conditions: 2.7V to 5.5V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$ for Extended |         |            |      |                                                    |  |  |

|--------------------|-------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|------|----------------------------------------------------|--|--|

| Param<br>No.       | Symbol            | Characteristic                                        | Min.                                                                                                                                                                                                                                              | Тур     | Conditions |      |                                                    |  |  |

|                    |                   | Clock                                                 | k Parame                                                                                                                                                                                                                                          | ters    |            |      |                                                    |  |  |

| AD50               | TAD               | A/D Clock Period                                      | _                                                                                                                                                                                                                                                 | 334     | _          | ns   | VDD = 3-5.5V (Note 1)                              |  |  |

| AD51               | trc               | A/D Internal RC Oscillator Period                     | od 1.2 1.5 1.8 μs                                                                                                                                                                                                                                 |         |            |      | _                                                  |  |  |

|                    |                   | Con                                                   | version R                                                                                                                                                                                                                                         | ate     |            |      |                                                    |  |  |

| AD55               | tCONV             | Conversion Time                                       | _                                                                                                                                                                                                                                                 | 14 TAD  |            | ns   | _                                                  |  |  |

| AD56               | FCNV              | Throughput Rate                                       | _                                                                                                                                                                                                                                                 | 200     | _          | ksps | VDD = VREF = 3-5.5V                                |  |  |

| AD57               | Тѕамр             | Sample Time                                           | _                                                                                                                                                                                                                                                 | 1 TAD   |            | ns   | VDD = 3-5.5V<br>Source resistance<br>Rs = 0-2.5 kΩ |  |  |

|                    | Timing Parameters |                                                       |                                                                                                                                                                                                                                                   |         |            |      |                                                    |  |  |