Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART                                     |

| Peripherals                | AC'97, Brown-out Detect/Reset, I <sup>2</sup> S, LVD, POR, PWM, WDT           |

| Number of I/O              | 68                                                                            |

| Program Memory Size        | 144KB (48K x 24)                                                              |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 4K x 8                                                                        |

| RAM Size                   | 8K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 16x12b                                                                    |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 80-TQFP                                                                       |

| Supplier Device Package    | 80-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f6014-20e-pf |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active Thermistor, Mindi, MiWi, MPASM, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2006, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona, Gresham, Oregon and Mountain View, California. The Company's quality system processes and procedures are for its PIC<sup>®</sup> 8-bit MCUs, KEELO0<sup>®</sup> code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## dsPIC30F6011/6012/6013/6014 High-Performance Digital Signal Controllers

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "*dsPIC30F Family Reference Manual*" (DS70046). For more information on the device instruction set and programming, refer to the "*dsPIC30F/33F Programmer's Reference Manual*" (DS70157).

### High-Performance Modified RISC CPU:

- Modified Harvard architecture

- C compiler optimized instruction set architecture

- Flexible addressing modes

- 83 base instructions

- 24-bit wide instructions, 16-bit wide data path

- Up to 144 Kbytes on-chip Flash program space

- Up to 48K instruction words

- Up to 8 Kbytes of on-chip data RAM

- Up to 4 Kbytes of nonvolatile data EEPROM

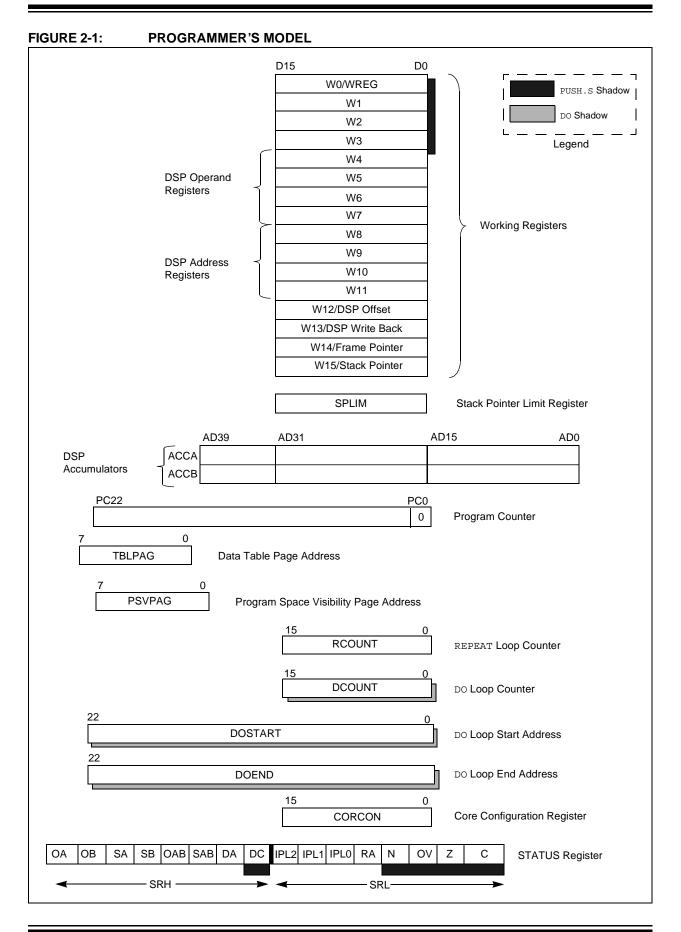

- 16 x 16-bit working register array

- Up to 30 MIPS operation:

- DC to 40 MHz external clock input

- 4 MHz-10 MHz oscillator input with PLL active (4x, 8x, 16x)

- Up to 41 interrupt sources:

- 8 user-selectable priority levels

- 5 external interrupt sources

- 4 processor traps

#### **DSP Features:**

- · Dual data fetch

- · Modulo and Bit-Reversed modes

- Two 40-bit wide accumulators with optional saturation logic

- 17-bit x 17-bit single cycle hardware fractional/ integer multiplier

- All DSP instructions are single cycle:

- Multiply-Accumulate (MAC) operation

- Single-cycle ±16 shift

### **Peripheral Features:**

- High current sink/source I/O pins: 25 mA/25 mA

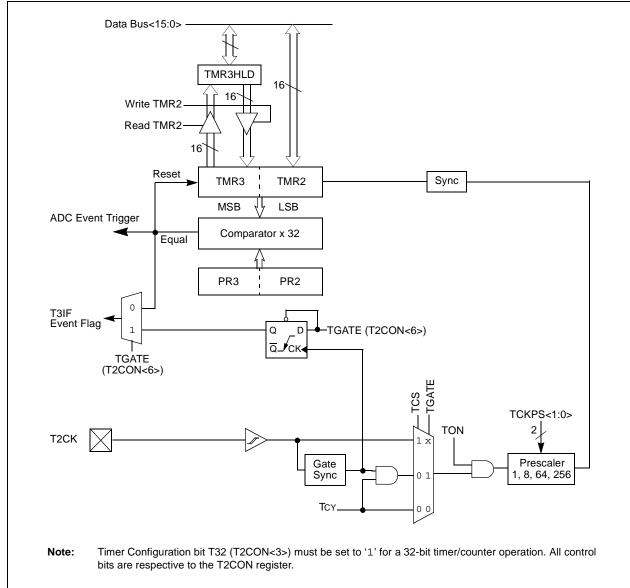

- Five 16-bit timers/counters; optionally pair up 16-bit timers into 32-bit timer modules

- 16-bit Capture input functions

- 16-bit Compare/PWM output functions

- Data Converter Interface (DCI) supports common audio Codec protocols, including I<sup>2</sup>S and AC'97

- 3-wire SPI modules (supports 4 Frame modes)

- I<sup>2</sup>C<sup>™</sup> module supports Multi-Master/Slave mode and 7-bit/10-bit addressing

- Two addressable UART modules with FIFO buffers

- Two CAN bus modules compliant with CAN 2.0B standard

### **Analog Features:**

- 12-bit Analog-to-Digital Converter (ADC) with:

- 200 ksps conversion rate

- Up to 16 input channels

- Conversion available during Sleep and Idle

- Programmable Low-Voltage Detection (PLVD)

- Programmable Brown-out Reset

#### **Special Microcontroller Features:**

- Enhanced Flash program memory:

- 10,000 erase/write cycle (min.) for industrial temperature range, 100K (typical)

- Data EEPROM memory:

- 100,000 erase/write cycle (min.) for industrial temperature range, 1M (typical)

- Self-reprogrammable under software control

- Power-on Reset (POR), Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Flexible Watchdog Timer (WDT) with on-chip low power RC oscillator for reliable operation

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. Should a misaligned read or write be attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed, whereas if it occurred on a write, the instruction will be executed but the write will not occur. In either case, a trap will then be executed, allowing the system and/or user to examine the machine state prior to execution of the address fault.

FIGURE 3-10: DATA ALIGNMENT

|      | 15 <b>MSB</b> | 8 | 7 LSB  | 0 |      |

|------|---------------|---|--------|---|------|

| 0001 | Byte1         |   | Byte 0 |   | 0000 |

| 0003 | Byte3         |   | Byte 2 |   | 0002 |

| 0005 | Byte5         |   | Byte 4 |   | 0004 |

|      |               |   |        |   |      |

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A sign-extend (SE) instruction is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions, including the DSP instructions, operate only on words.

### 3.2.5 NEAR DATA SPACE

An 8-Kbyte 'near' data space is reserved in X address memory space between 0x0000 and 0x1FFF, which is directly addressable via a 13-bit absolute address field within all memory direct instructions. The remaining X address space and all of the Y address space is addressable indirectly. Additionally, the whole of X data space is addressable using MOV instructions, which support memory direct addressing with a 16-bit address field.

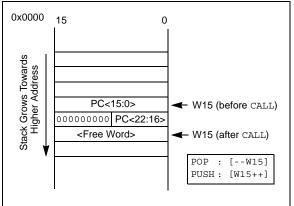

### 3.2.6 SOFTWARE STACK

The dsPIC DSC devices contain a software stack. W15 is used as the Stack Pointer.

The Stack Pointer always points to the first available free word and grows from lower addresses towards higher addresses. It pre-decrements for stack pops and post-increments for stack pushes as shown in Figure 3-11. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

| Note: | A PC push during exception processing    |

|-------|------------------------------------------|

|       | will concatenate the SRL register to the |

|       | MSB of the PC prior to the push.         |

There is a Stack Pointer Limit register (SPLIM) associated with the Stack Pointer. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word aligned. Whenever an Effective Address (EA) is generated using W15 as a source or destination pointer, the address thus generated is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value, 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800, thus preventing the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### FIGURE 3-11: CALL STACK FRAME

### TABLE 3-3: CORE REGISTER MAP (CONTINUED)

| © 2006     |  |

|------------|--|

| Microchip  |  |

| Technology |  |

| / Inc.     |  |

| SFR Name | Address<br>(Home) | Bit 15 | Bit 14        | Bit 13 | Bit 12 | Bit 11 | Bit 10                     | Bit 9 | Bit 8   | Bit 7  | Bit 6   | Bit 5 | Bit 4          | Bit 3 | Bit 2 | Bit 1               | Bit 0 | Reset State         |

|----------|-------------------|--------|---------------|--------|--------|--------|----------------------------|-------|---------|--------|---------|-------|----------------|-------|-------|---------------------|-------|---------------------|

| SR       | 0042              | OA     | OB            | SA     | SB     | OAB    | SAB                        | DA    | DC      | IPL2   | IPL1    | IPL0  | RA             | N     | OV    | Z                   | С     | 0000 0000 0000 0000 |

| CORCON   | 0044              | —      | _             | _      | US     | EDT    | DL2                        | DL1   | DL0     | SATA   | SATB    | SATDW | ACCSAT         | IPL3  | PSV   | RND                 | IF    | 0000 0000 0010 0000 |

| MODCON   | 0046              | XMODEN | YMODEN        | _      | _      |        | BWM<3:0> YWM<3:0> XWM<3:0> |       |         |        |         |       |                |       |       | 0000 0000 0000 0000 |       |                     |

| XMODSRT  | 0048              |        | XS<15:1> 0    |        |        |        |                            |       |         |        |         | 0     | uuuu uuuu uuu0 |       |       |                     |       |                     |

| XMODEND  | 004A              |        | XE<15:1> 1    |        |        |        |                            |       |         |        |         | 1     | uuuu uuuu uuul |       |       |                     |       |                     |

| YMODSRT  | 004C              |        |               |        |        |        |                            | YS    | 6<15:1> |        |         |       |                |       |       |                     | 0     | uuuu uuuu uuu0      |

| YMODEND  | 004E              |        | YE<15:1> 1    |        |        |        |                            |       |         |        |         | 1     | uuuu uuuu uuu1 |       |       |                     |       |                     |

| XBREV    | 0050              | BREN   | BREN XB<14:0> |        |        |        |                            |       |         |        |         |       | uuuu uuuu uuuu |       |       |                     |       |                     |

| DISICNT  | 0052              | _      | _             |        |        |        |                            |       |         | DISICN | Г<13:0> |       |                |       |       |                     |       | 0000 0000 0000 0000 |

**Legend:** u = uninitialized bit

Note: Refer to "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

NOTES:

## 9.4 Timer Interrupt

The 16-bit timer has the ability to generate an interrupt on period match. When the timer count matches the Period register, the T1IF bit is asserted and an interrupt will be generated if enabled. The T1IF bit must be cleared in software. The timer interrupt flag, T1IF, is located in the IFS0 Control register in the interrupt controller.

When the Gated Time Accumulation mode is enabled, an interrupt will also be generated on the falling edge of the gate signal (at the end of the accumulation cycle).

Enabling an interrupt is accomplished via the respective timer interrupt enable bit, T1IE. The timer interrupt enable bit is located in the IEC0 Control register in the interrupt controller.

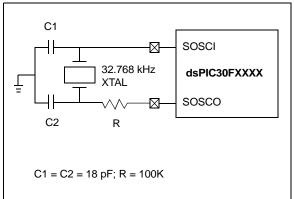

## 9.5 Real-Time Clock

Timer1, when operating in Real-Time Clock (RTC) mode, provides time of day and event time-stamping capabilities. Key operational features of the RTC are:

- Operation from 32 kHz LP oscillator

- 8-bit prescaler

- Low power

- Real-Time Clock interrupts

These Operating modes are determined by setting the appropriate bit(s) in the T1CON Control register.

#### FIGURE 9-2: RECOMMENDED COMPONENTS FOR TIMER1 LP OSCILLATOR RTC

## 9.5.1 RTC OSCILLATOR OPERATION

When the TON = 1, TCS = 1 and TGATE = 0, the timer increments on the rising edge of the 32 kHz LP oscillator output signal, up to the value specified in the Period register and is then Reset to '0'.

The TSYNC bit must be asserted to a logic '0' (Asynchronous mode) for correct operation.

Enabling LPOSCEN (OSCCON<1>) will disable the normal Timer and Counter modes and enable a timer carry-out wake-up event.

When the CPU enters Sleep mode, the RTC will continue to operate provided the 32 kHz external crystal oscillator is active and the control bits have not been changed. The TSIDL bit should be cleared to '0' in order for RTC to continue operation in Idle mode.

## 9.5.2 RTC INTERRUPTS

When an interrupt event occurs, the respective interrupt flag, T1IF, is asserted and an interrupt will be generated if enabled. The T1IF bit must be cleared in software. The respective Timer interrupt flag, T1IF, is located in the IFS0 Status register in the interrupt controller.

Enabling an interrupt is accomplished via the respective timer interrupt enable bit, T1IE. The timer interrupt enable bit is located in the IEC0 Control register in the interrupt controller.

#### FIGURE 10-1: 32-BIT TIMER2/3 BLOCK DIAGRAM

NOTES:

## 15.2 I<sup>2</sup>C Module Addresses

The I2CADD register contains the Slave mode addresses. The register is a 10-bit register.

If the A10M bit (I2CCON<10>) is '0', the address is interpreted by the module as a 7-bit address. When an address is received, it is compared to the 7 LSbs of the I2CADD register.

If the A10M bit is '1', the address is assumed to be a 10-bit address. When an address is received, it will be compared with the binary value '11110 A9 A8' (where A9 and A8 are two Most Significant bits of I2CADD). If that value matches, the next address will be compared with the Least Significant 8 bits of I2CADD, as specified in the 10-bit addressing protocol.

#### TABLE 15-1: 7-BIT I<sup>2</sup>C<sup>™</sup> SLAVE ADDRESSES SUPPORTED BY DSPIC30F

| 0x00      | General call address or Start byte    |

|-----------|---------------------------------------|

| 0x01-0x03 | Reserved                              |

| 0x04-0x07 | Hs mode Master codes                  |

| 0x08-0x77 | Valid 7-bit addresses                 |

| 0x78-0x7b | Valid 10-bit addresses (lower 7 bits) |

| 0x7c-0x7f | Reserved                              |

## 15.3 I<sup>2</sup>C 7-bit Slave Mode Operation

Once enabled (I2CEN = 1), the slave module will wait for a Start bit to occur (i.e., the I<sup>2</sup>C module is 'Idle'). Following the detection of a Start bit, 8 bits are shifted into I2CRSR and the address is compared against I2CADD. In 7-bit mode (A10M = 0), bits I2CADD<6:0> are compared against I2CRSR<7:1> and I2CRSR<0> is the R\_W bit. All incoming bits are sampled on the rising edge of SCL.

If an address match occurs, an Acknowledgement will be sent, and the slave event interrupt flag (SI2CIF) is set on the falling edge of the ninth ( $\overline{ACK}$ ) bit. The address match does not affect the contents of the I2CRCV buffer or the RBF bit.

## 15.3.1 SLAVE TRANSMISSION

If the R\_W bit received is a '1', then the serial port will go into Transmit mode. It will send ACK on the ninth bit and then hold SCL to '0' until the CPU responds by writing to I2CTRN. SCL is released by setting the SCLREL bit, and 8 bits of data are shifted out. Data bits are shifted out on the falling edge of SCL, such that SDA is valid during SCL high. The interrupt pulse is sent on the falling edge of the ninth clock pulse, regardless of the status of the ACK received from the master.

## 15.3.2 SLAVE RECEPTION

If the R\_W bit received is a '0' during an address match, then Receive mode is initiated. Incoming bits are sampled on the rising edge of SCL. After 8 bits are received, if I2CRCV is not full or I2COV is not set, I2CRSR is transferred to I2CRCV. ACK is sent on the ninth clock.

If the RBF flag is set, indicating that I2CRCV is still holding data from a previous operation (RBF = 1), then ACK is not sent; however, the interrupt pulse is generated. In the case of an overflow, the contents of the I2CRSR are not loaded into the I2CRCV.

| Note: | The ICCRCV/ will be leaded if the ICCOV/         |

|-------|--------------------------------------------------|

| Note: | The I2CRCV will be loaded if the I2COV           |

|       | bit = $1$ and the RBF flag = $0$ . In this case, |

|       | a read of the I2CRCV was performed but           |

|       | the user did not clear the state of the          |

|       | I2COV bit before the next receive                |

|       | occurred. The Acknowledgement is not             |

|       | sent ( $\overline{ACK} = 1$ ) and the I2CRCV is  |

|       | updated.                                         |

## 15.4 I<sup>2</sup>C 10-bit Slave Mode Operation

In 10-bit mode, the basic receive and transmit operations are the same as in the 7-bit mode. However, the criteria for address match is more complex.

The  $I^2C$  specification dictates that a slave must be addressed for a write operation with two address bytes following a Start bit.

The A10M bit is a control bit that signifies that the address in I2CADD is a 10-bit address rather than a 7-bit address. The address detection protocol for the first byte of a message address is identical for 7-bit and 10-bit messages, but the bits being compared are different.

I2CADD holds the entire 10-bit address. Upon receiving an address following a Start bit, I2CRSR <7:3> is compared against a literal '11110' (the default 10-bit address) and I2CRSR<2:1> are compared against I2CADD<9:8>. If a match occurs and if  $R_W = 0$ , the interrupt pulse is sent. The ADD10 bit will be cleared to indicate a partial address match. If a match fails or  $R_W = 1$ , the ADD10 bit is cleared and the module returns to the Idle state.

The low byte of the address is then received and compared with I2CADD<7:0>. If an address match occurs, the interrupt pulse is generated and the ADD10 bit is set, indicating a complete 10-bit address match. If an address match did not occur, the ADD10 bit is cleared and the module returns to the Idle state.

#### 15.4.1 10-BIT MODE SLAVE TRANSMISSION

Once a slave is addressed in this fashion with the full 10-bit address (we will refer to this state as "PRIOR\_ADDR\_MATCH"), the master can begin sending data bytes for a slave reception operation. NOTES:

### TABLE 18-2: DCI REGISTER MAP

| SFR Name | Addr. | Bit 15                               | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7     | Bit 6  | Bit 5               | Bit 4               | Bit 3 | Bit 2 | Bit 1   | Bit 0  | Reset State         |

|----------|-------|--------------------------------------|--------|---------|--------|--------|--------|------------|-------------|-----------|--------|---------------------|---------------------|-------|-------|---------|--------|---------------------|

| DCICON1  | 0240  | DCIEN                                | —      | DCISIDL | _      | DLOOP  | CSCKD  | CSCKE      | COFSD       | UNFM      | CSDOM  | DJST                | _                   | _     | _     | COFSM1  | COFSM0 | 0000 0000 0000 0000 |

| DCICON2  | 0242  |                                      | _      |         | _      | BLEN1  | BLEN0  | _          |             | COFS      | G<3:0> |                     |                     |       | V     | VS<3:0> |        | 0000 0000 0000 0000 |

| DCICON3  | 0244  | _                                    | —      | _       | _      |        |        |            |             |           | BCG<1  | 1:0>                |                     |       |       |         |        | 0000 0000 0000 0000 |

| DCISTAT  | 0246  | _                                    | —      | _       | _      | SLOT3  | SLOT2  | SLOT1      | SLOT0       | _         |        |                     |                     | ROV   | RFUL  | TUNF    | TMPTY  | 0000 0000 0000 0000 |

| TSCON    | 0248  | TSE15                                | TSE14  | TSE13   | TSE12  | TSE11  | TSE10  | TSE9       | TSE8        | TSE7      | TSE6   | TSE5                | TSE4                | TSE3  | TSE2  | TSE1    | TSE0   | 0000 0000 0000 0000 |

| RSCON    | 024C  | RSE15                                | RSE14  | RSE13   | RSE12  | RSE11  | RSE10  | RSE9       | RSE8        | RSE7      | RSE6   | RSE5                | RSE4                | RSE3  | RSE2  | RSE1    | RSE0   | 0000 0000 0000 0000 |

| RXBUF0   | 0250  | 0250 Receive Buffer #0 Data Register |        |         |        |        |        |            |             |           |        |                     | 0000 0000 0000 0000 |       |       |         |        |                     |

| RXBUF1   | 0252  |                                      |        |         |        |        |        | Receive B  | uffer #1 D  | ata Regis | ster   |                     |                     |       |       |         |        | 0000 0000 0000 0000 |

| RXBUF2   | 0254  |                                      |        |         |        |        |        | Receive B  | uffer #2 D  | ata Regis | ster   |                     |                     |       |       |         |        | 0000 0000 0000 0000 |

| RXBUF3   | 0256  |                                      |        |         |        |        |        | Receive B  | uffer #3 D  | ata Regis | ster   |                     |                     |       |       |         |        | 0000 0000 0000 0000 |

| TXBUF0   | 0258  |                                      |        |         |        |        |        | Transmit B | Suffer #0 D | ata Regi  | ster   |                     |                     |       |       |         |        | 0000 0000 0000 0000 |

| TXBUF1   | 025A  |                                      |        |         |        |        |        | Transmit B | Suffer #1 D | ata Regi  | ster   |                     |                     |       |       |         |        | 0000 0000 0000 0000 |

| TXBUF2   | 025C  |                                      |        |         |        |        |        | Transmit B | Suffer #2 D | ata Regi  | ster   |                     |                     |       |       |         |        | 0000 0000 0000 0000 |

| TXBUF3   | 025E  | Transmit Buffer #3 Data Register     |        |         |        |        |        |            |             |           |        | 0000 0000 0000 0000 |                     |       |       |         |        |                     |

Note: Refer to "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

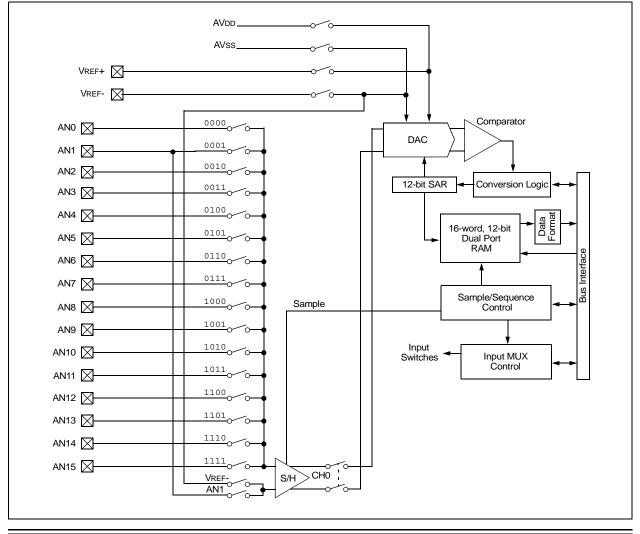

## 19.0 12-BIT ANALOG-TO-DIGITAL CONVERTER (A/D) MODULE

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "*dsPIC30F Family Reference Manual*" (DS70046).

The 12-bit Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 12-bit digital number. This module is based on a Successive Approximation Register (SAR) architecture and provides a maximum sampling rate of 200 ksps. The ADC module has up to 16 analog inputs which are multiplexed into a sample and hold amplifier. The output of the sample and hold is the input into the converter which generates the result. The analog reference voltage is software selectable to either the device supply voltage (AVDD/AVSS) or the voltage level on the (VREF+/VREF-) pin. The ADC has a unique feature of being able to operate while the device is in Sleep mode with RC oscillator selection.

The ADC module has six 16-bit registers:

- ADC Control Register 1 (ADCON1)

- ADC Control Register 2 (ADCON2)

- ADC Control Register 3 (ADCON3)

- ADC Input Select Register (ADCHS)

- ADC Port Configuration Register (ADPCFG)

- ADC Input Scan Selection Register (ADCSSL)

The ADCON1, ADCON2 and ADCON3 registers control the operation of the A/D module. The ADCHS register selects the input channels to be converted. The ADPCFG register configures the port pins as analog inputs or as digital I/O. The ADCSSL register selects inputs for scanning.

The block diagram of the 12-bit ADC module is shown in Figure 19-1.

#### FIGURE 19-1: 12-BIT ADC FUNCTIONAL BLOCK DIAGRAM

Note: The SSRC<2:0>, ASAM, SMPI<3:0>, BUFM and ALTS bits, as well as the ADCON3 and ADCSSL registers, must not be written to while ADON = 1. This would lead to indeterminate results.

Table 20-5 shows the Reset conditions for the RCON register. Since the control bits within the RCON register are R/W, the information in the table implies that all the bits are negated prior to the action specified in the condition column.

| Condition                              | Program<br>Counter | TRAPR | IOPUWR | EXTR | SWR | WDTO | IDLE | SLEEP | POR | BOR |

|----------------------------------------|--------------------|-------|--------|------|-----|------|------|-------|-----|-----|

| Power-on Reset                         | 0x000000           | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 1   | 1   |

| Brown-out Reset                        | 0x000000           | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 1   |

| MCLR Reset during normal operation     | 0x000000           | 0     | 0      | 1    | 0   | 0    | 0    | 0     | 0   | 0   |

| Software Reset during normal operation | 0x000000           | 0     | 0      | 0    | 1   | 0    | 0    | 0     | 0   | 0   |

| MCLR Reset during Sleep                | 0x000000           | 0     | 0      | 1    | 0   | 0    | 0    | 1     | 0   | 0   |

| MCLR Reset during Idle                 | 0x000000           | 0     | 0      | 1    | 0   | 0    | 1    | 0     | 0   | 0   |

| WDT Time-out Reset                     | 0x000000           | 0     | 0      | 0    | 0   | 1    | 0    | 0     | 0   | 0   |

| WDT Wake-up                            | PC + 2             | 0     | 0      | 0    | 0   | 1    | 0    | 1     | 0   | 0   |

| Interrupt Wake-up from Sleep           | PC + 2(1)          | 0     | 0      | 0    | 0   | 0    | 0    | 1     | 0   | 0   |

| Clock Failure Trap                     | 0x000004           | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

| Trap Reset                             | 0x000000           | 1     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

| Illegal Operation Trap                 | 0x000000           | 0     | 1      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

## TABLE 20-5: INITIALIZATION CONDITION FOR RCON REGISTER: CASE 1

**Legend:** u = unchanged, x = unknown

**Note 1:** When the wake-up is due to an enabled interrupt, the PC is loaded with the corresponding interrupt vector.

Any interrupt that is individually enabled (using the corresponding IE bit) and meets the prevailing priority level will be able to wake-up the processor. The processor will process the interrupt and branch to the ISR. The Sleep status bit in the RCON register is set upon wake-up.

Note: In spite of various delays applied (ΤΡΟR, TLOCK and TPWRT), the crystal oscillator (and PLL) may not be active at the end of the time-out (e.g., for low-frequency crystals). In such cases, if FSCM is enabled, then the device will detect this as a clock failure and process the clock failure trap, the FRC oscillator will be enabled and the user will have to re-enable the crystal oscillator. If FSCM is not enabled, then the device will simply suspend execution of code until the clock is stable and will remain in Sleep until the oscillator clock has started.

All Resets will wake-up the processor from Sleep mode. Any Reset, other than POR, will set the Sleep status bit. In a POR, the Sleep bit is cleared.

If the Watchdog Timer is enabled, then the processor will wake-up from Sleep mode upon WDT time-out. The Sleep and WDTO status bits are both set.

## 20.6.2 IDLE MODE

In Idle mode, the clock to the CPU is shutdown while peripherals keep running. Unlike Sleep mode, the clock source remains active.

Several peripherals have a control bit in each module that allows them to operate during Idle.

LPRC Fail-Safe Clock remains active if clock failure detect is enabled.

The processor wakes up from Idle if at least one of the following conditions has occurred:

- any interrupt that is individually enabled (IE bit is '1') and meets the required priority level

- any Reset (POR, BOR, MCLR)

- WDT time-out

Upon wake-up from Idle mode, the clock is re-applied to the CPU and instruction execution begins immediately, starting with the instruction following the PWRSAV instruction.

Any interrupt that is individually enabled (using IE bit) and meets the prevailing priority level will be able to wake-up the processor. The processor will process the interrupt and branch to the ISR. The Idle status bit in the RCON register is set upon wake-up.

Any Reset other than POR will set the Idle status bit. On a POR, the Idle bit is cleared.

If Watchdog Timer is enabled, then the processor will wake-up from Idle mode upon WDT time-out. The Idle and WDTO status bits are both set.

Unlike wake-up from Sleep, there are no time delays involved in wake-up from Idle.

## 20.7 Device Configuration Registers

The Configuration bits in each device configuration register specify some of the device modes and are programmed by a device programmer, or by using the In-Circuit Serial Programming (ICSP) feature of the device. Each device configuration register is a 24-bit register, but only the lower 16 bits of each register are used to hold configuration data. There are four device configuration registers available to the user:

- 1. FOSC (0xF80000): Oscillator Configuration Register

- 2. FWDT (0xF80002): Watchdog Timer Configuration Register

- 3. FBORPOR (0xF80004): BOR and POR Configuration Register

- 4. FGS (0xF8000A): General Code Segment Configuration Register

The placement of the Configuration bits is automatically handled when you select the device in your device programmer. The desired state of the Configuration bits may be specified in the source code (dependent on the language tool used), or through the programming interface. After the device has been programmed, the application software may read the Configuration bit values through the table read instructions. For additional information, please refer to the programming specifications of the device.

Note: If the code protection configuration fuse bits (FGS<GCP> and FGS<GWRP>) have been programmed, an erase of the entire code-protected device is only possible at voltages VDD ≥ 4.5V.

### 22.7 MPLAB ICE 2000 High-Performance In-Circuit Emulator

The MPLAB ICE 2000 In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers. Software control of the MPLAB ICE 2000 In-Circuit Emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The architecture of the MPLAB ICE 2000 In-Circuit Emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE 2000 In-Circuit Emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows<sup>®</sup> 32-bit operating system were chosen to best make these features available in a simple, unified application.

## 22.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC<sup>®</sup> and MCU devices. It debugs and programs PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The MPLAB REAL ICE probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with the popular MPLAB ICD 2 system (RJ11) or with the new high speed, noise tolerant, lowvoltage differential signal (LVDS) interconnection (CAT5).

MPLAB REAL ICE is field upgradeable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added, such as software breakpoints and assembly code trace. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, real-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 22.9 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low-cost, run-time development tool, connecting to the host PC via an RS-232 or high-speed USB interface. This tool is based on the Flash PIC MCUs and can be used to develop for these and other PIC MCUs and dsPIC DSCs. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the Flash devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers costeffective, in-circuit Flash debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single stepping and watching variables, and CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real time. MPLAB ICD 2 also serves as a development programmer for selected PIC devices.

## 22.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an SD/MMC card for file storage and secure data applications.

## TABLE 23-21: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET TIMING REQUIREMENTS

| АС СНА       | RACTER | ISTICS                                     | Standard Operating Conditions: 2.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                    |     |    |                        |  |  |  |

|--------------|--------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----|----|------------------------|--|--|--|

| Param<br>No. | Symbol | Characteristic <sup>(1)</sup>              | Min                                                                                                                                                                                                  | <i>l</i> in Typ <sup>(2)</sup> Max |     |    | Conditions             |  |  |  |

| SY25         | TBOR   | Brown-out Reset Pulse Width <sup>(3)</sup> | 100                                                                                                                                                                                                  | —                                  | —   | μs | $VDD \leq VBOR (D034)$ |  |  |  |

| SY30         | Tost   | Oscillation Start-up Timer Period          | _                                                                                                                                                                                                    | 1024 Tosc                          | _   | _  | Tosc = OSC1 period     |  |  |  |

| SY35         | TFSCM  | Fail-Safe Clock Monitor Delay              | —                                                                                                                                                                                                    | 500                                | 900 | μs | -40°C to +85°C         |  |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ" column is at 5V, 25°C unless otherwise stated.

3: Refer to Figure 23-2 and Table 23-11 for BOR.

#### FIGURE 23-7: BAND GAP START-UP TIME CHARACTERISTICS

| 0V -                           |                                                 | VBGAP              |

|--------------------------------|-------------------------------------------------|--------------------|

| Enable Band Ga<br>(see Note) - | p                                               | Band Gap<br>Stable |

| Note: Set LVDEN                | N bit (RCON<12>) or the BOREN bit (FBORPOR<7>). |                    |

#### TABLE 23-22: BAND GAP START-UP TIME REQUIREMENTS

| AC CHARACTERISTICS |        |                               |     | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |       |                                                                                                                                                                   |  |  |  |  |

|--------------------|--------|-------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup> | Min | Тур <sup>(2)</sup>                                                                                                                                                                                                                                                                      | Max | Units | Conditions                                                                                                                                                        |  |  |  |  |

| SY40               | TBGAP  | Band Gap Start-up Time        |     | 40                                                                                                                                                                                                                                                                                      | 65  | μs    | Defined as the time between the<br>instant that the band gap is enabled<br>and the moment that the band gap<br>reference voltage is stable.<br>RCON<13>Status bit |  |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ" column is at 5V, 25°C unless otherwise stated.

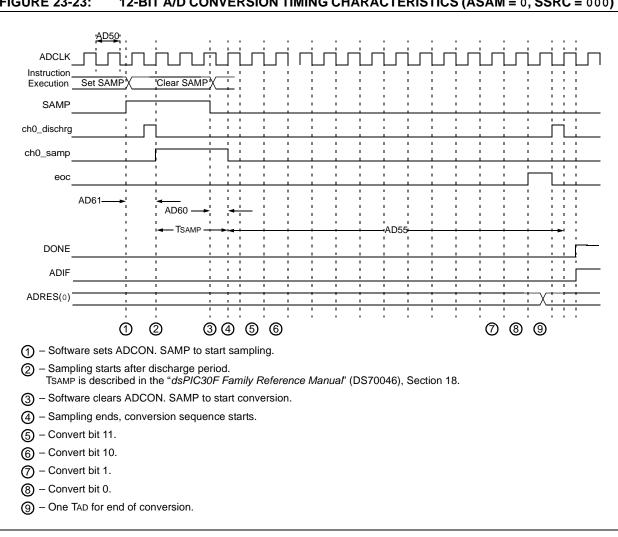

## FIGURE 23-23: 12-BIT A/D CONVERSION TIMING CHARACTERISTICS (ASAM = 0, SSRC = 000)

## **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:                                                             | Technical Publications Manager                                                           | Total Pages Sent |  |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------|--|

| RE:                                                             | Reader Response                                                                          |                  |  |

| From:                                                           | rom: Name                                                                                |                  |  |

|                                                                 |                                                                                          |                  |  |

|                                                                 |                                                                                          |                  |  |

|                                                                 |                                                                                          |                  |  |

|                                                                 | Telephone: ()                                                                            | FAX: ()          |  |

| Application (optional):                                         |                                                                                          |                  |  |

| Would you like a reply?YN                                       |                                                                                          |                  |  |

| Device: dsPIC30F6011/6012/6013/6014 Literature Number: DS70117F |                                                                                          |                  |  |

| Questions:                                                      |                                                                                          |                  |  |

| 1. W                                                            | 1. What are the best features of this document?                                          |                  |  |

|                                                                 |                                                                                          |                  |  |

|                                                                 |                                                                                          |                  |  |

| 2. H                                                            | 2. How does this document meet your hardware and software development needs?             |                  |  |

| _                                                               |                                                                                          |                  |  |

| 2 <u>–</u>                                                      | Do you find the organization of this document easy to follow? If not, why?               |                  |  |

| 3. D                                                            |                                                                                          |                  |  |

|                                                                 |                                                                                          |                  |  |

| 4. W                                                            | What additions to the document do you think would enhance the structure and subject?     |                  |  |

|                                                                 |                                                                                          |                  |  |

|                                                                 |                                                                                          |                  |  |

| 5. W                                                            | What deletions from the document could be made without affecting the overall usefulness? |                  |  |

|                                                                 |                                                                                          |                  |  |

| _                                                               |                                                                                          |                  |  |

| 6. Is                                                           | . Is there any incorrect or misleading information (what and where)?                     |                  |  |

|                                                                 |                                                                                          |                  |  |

| 7. H                                                            | . How would you improve this document?                                                   |                  |  |

|                                                                 |                                                                                          |                  |  |

|                                                                 |                                                                                          |                  |  |

|                                                                 |                                                                                          |                  |  |

## WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Alpharetta, GA Tel: 770-640-0034 Fax: 770-640-0307

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Habour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Fuzhou** Tel: 86-591-8750-3506 Fax: 86-591-8750-3521

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Shunde Tel: 86-757-2839-5507 Fax: 86-757-2839-5571

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7250 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-4182-8400 Fax: 91-80-4182-8422

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Gumi** Tel: 82-54-473-4301 Fax: 82-54-473-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

**Malaysia - Penang** Tel: 60-4-646-8870 Fax: 60-4-646-5086

Philippines - Manila Tel: 63-2-634-9065

Fax: 63-2-634-9069 Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-572-9526 Fax: 886-3-572-6459

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820