#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 10x10b/12b                                                             |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

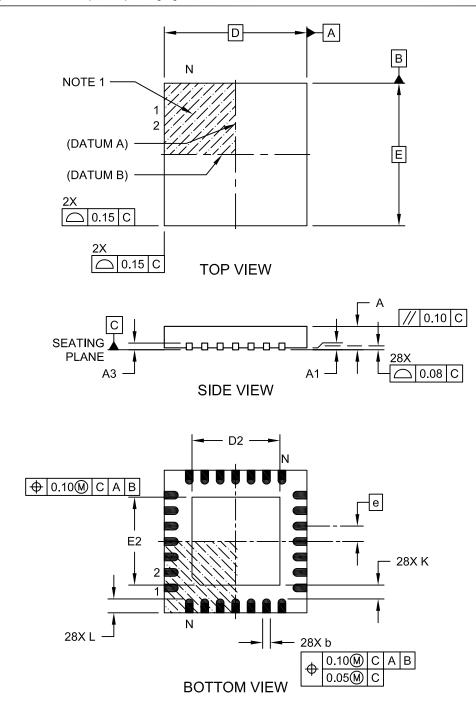

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26j13-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                                                  | Pin Nu                     | ımber     |             |                                        |                                                                         |

|--------------------------------------------------------------------------------------------------|----------------------------|-----------|-------------|----------------------------------------|-------------------------------------------------------------------------|

| Pin Name                                                                                         | 28-SPDIP/<br>SSOP/<br>SOIC | 28-QFN    | Pin<br>Type | Buffer<br>Type                         | Description                                                             |

| Vss1                                                                                             | 8                          | 5         | Р           |                                        | Ground reference for logic and I/O pins.                                |

| Vss2                                                                                             | 19                         | 16        | —           | —                                      |                                                                         |

| Vdd                                                                                              | 20                         | 17        | Ρ           | —                                      | Positive supply for peripheral digital logic and I/O pins.              |

| Vddcore/Vcap                                                                                     | 6                          | 3         | —           | —                                      | Core logic power or external filter capacitor connection.               |

| VDDCORE                                                                                          |                            |           | Ρ           | —                                      | Positive supply for microcontroller core logic<br>(regulator disabled). |

| VCAP                                                                                             |                            |           | Ρ           | —                                      | External filter capacitor connection (regulator enabled).               |

| Legend: TTL = TTL compati<br>ST = Schmitt Trigg<br>I = Input<br>P = Power<br>DIG = Digital outpu | ger input wi               | th CMOS   | levels      | CMOS = CMOS compatible input or output |                                                                         |

| Note 1: RA7 and RA6 will be                                                                      | e disabled                 | if OSC1 a | nd OSC      | 2 are us                               | ed for the clock function.                                              |

#### **TABLE 1-3**: PIC18F2XJ13 PINOUT I/O DESCRIPTIONS (CONTINUED)

bled if USC1 and US C2 are use for the clock functio

2: 5.5V tolerant.

| TABLE 5-2:           | INITIALIZAT | ITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED) |                                                                |                                                                            |                                 |  |  |  |  |  |

|----------------------|-------------|-------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|

| Register             | Applicabl   | e Devices                                             | Power-on Reset,<br>Brown-out Reset,<br>Wake From Deep<br>Sleep | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |  |  |  |  |

| IPR1                 | PIC18F2XJ13 | PIC18F4XJ13                                           | 1111 1111                                                      | 1111 1111                                                                  | uuuu uuuu                       |  |  |  |  |  |

| PIR1                 | PIC18F2XJ13 | PIC18F4XJ13                                           | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu <sup>(3)</sup>        |  |  |  |  |  |

| PIE1                 | PIC18F2XJ13 | PIC18F4XJ13                                           | 0000 0000                                                      | 0000 0000                                                                  | սսսս սսսս                       |  |  |  |  |  |

| RCSTA2               | PIC18F2XJ13 | PIC18F4XJ13                                           | 0000 0000                                                      | 0000 0000                                                                  | սսսս սսսս                       |  |  |  |  |  |

| OSCTUNE              | PIC18F2XJ13 | PIC18F4XJ13                                           | 0000 0000                                                      | 0000 0000                                                                  | սսսս սսսս                       |  |  |  |  |  |

| T1GCON               | PIC18F2XJ13 | PIC18F4XJ13                                           | 0000 0x00                                                      | 0000 0x00                                                                  | uuuu uxuu                       |  |  |  |  |  |

| T3GCON               | PIC18F2XJ13 | PIC18F4XJ13                                           | 0000 0x00                                                      | uuuu uxuu                                                                  | uuuu uxuu                       |  |  |  |  |  |

| TRISE <sup>(5)</sup> | —           | PIC18F4XJ13                                           | 00111                                                          | 00111                                                                      | uuuuu                           |  |  |  |  |  |

| TRISD <sup>(5)</sup> | —           | PIC18F4XJ13                                           | 1111 1111                                                      | 1111 1111                                                                  | սսսս սսսս                       |  |  |  |  |  |

| TRISC                | PIC18F2XJ13 | PIC18F4XJ13                                           | 1111 1111                                                      | 1111 1111                                                                  | սսսս սսսս                       |  |  |  |  |  |

| TRISB                | PIC18F2XJ13 | PIC18F4XJ13                                           | 1111 1111                                                      | 1111 1111                                                                  | սսսս սսսս                       |  |  |  |  |  |

| TRISA                | PIC18F2XJ13 | PIC18F4XJ13                                           | 111- 1111                                                      | 111- 1111                                                                  | นนน- นนนน                       |  |  |  |  |  |

| PIE5                 | PIC18F2XJ13 | PIC18F4XJ13                                           | 00 0000                                                        | 00 0000                                                                    | uu uuuu                         |  |  |  |  |  |

| IPR4                 | PIC18F2XJ13 | PIC18F4XJ13                                           | 1111 1111                                                      | 1111 1111                                                                  | սսսս սսսս                       |  |  |  |  |  |

| PIR4                 | PIC18F2XJ13 | PIC18F4XJ13                                           | 0000 0000                                                      | 0000 0000                                                                  | սսսս սսսս                       |  |  |  |  |  |

| PIE4                 | PIC18F2XJ13 | PIC18F4XJ13                                           | 0000 0000                                                      | 0000 0000                                                                  | սսսս սսսս                       |  |  |  |  |  |

| LATE <sup>(5)</sup>  | —           | PIC18F4XJ13                                           | xxx                                                            | uuu                                                                        | uuu                             |  |  |  |  |  |

| LATD <sup>(5)</sup>  | —           | PIC18F4XJ13                                           | XXXX XXXX                                                      | սսսս սսսս                                                                  | սսսս սսսս                       |  |  |  |  |  |

| LATC                 | PIC18F2XJ13 | PIC18F4XJ13                                           | XXXX XXXX                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |  |

| LATB                 | PIC18F2XJ13 | PIC18F4XJ13                                           | XXXX XXXX                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |  |

| LATA                 | PIC18F2XJ13 | PIC18F4XJ13                                           | XXX- XXXX                                                      | uuu- uuuu                                                                  | uuu- uuuu                       |  |  |  |  |  |

| DMACON1              | PIC18F2XJ13 | PIC18F4XJ13                                           | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |

| OSCCON2              | PIC18F2XJ13 | PIC18F4XJ13                                           | -0-1 01                                                        | -0-1 ul                                                                    | -u-u uu                         |  |  |  |  |  |

| DMACON2              | PIC18F2XJ13 | PIC18F4XJ13                                           | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |

| HLVDCON              | PIC18F2XJ13 | PIC18F4XJ13                                           | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |

| PORTE <sup>(5)</sup> | —           | PIC18F4XJ13                                           | xxx                                                            | uuu                                                                        | uuu                             |  |  |  |  |  |

| PORTD <sup>(5)</sup> | _           | PIC18F4XJ13                                           | XXXX XXXX                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |  |

| PORTC                | PIC18F2XJ13 | PIC18F4XJ13                                           | XXXX XXXX                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |  |

| PORTB                | PIC18F2XJ13 | PIC18F4XJ13                                           | XXXX XXXX                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |  |  |  |  |

| PORTA                | PIC18F2XJ13 | PIC18F4XJ13                                           | XXX- XXXX                                                      | uuu- uuuu                                                                  | uuu- uuuu                       |  |  |  |  |  |

| SPBRGH1              | PIC18F2XJ13 | PIC18F4XJ13                                           | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |  |  |  |  |

| BAUDCON1             | PIC18F2XJ13 | PIC18F4XJ13                                           | 0100 0-00                                                      | 0100 0-00                                                                  | uuuu u-uu                       |  |  |  |  |  |

# TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, – = unimplemented bit, read as '0', q = value depends on condition.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 4: See Table 5-1 for the Reset value for a specific condition.

- 5: Not implemented on PIC18F2XJ13 devices.

- 6: Not implemented on "LF" devices.

### 6.3 Data Memory Organization

| Note: | The operation of some aspects of data    |

|-------|------------------------------------------|

|       | memory are changed when the PIC18        |

|       | extended instruction set is enabled. See |

|       | Section 6.6 "Data Memory and the         |

|       | Extended Instruction Set" for more       |

|       | information.                             |

The data memory in PIC18 devices is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. The memory space is divided into as many as 16 banks that contain 256 bytes each. The PIC18F47J13 Family implements all available banks and provides 3.8 Kbytes of data memory available to the user. Figure 6-6 provides the data memory organization for the devices.

The data memory contains Special Function Registers (SFRs) and General Purpose Registers (GPRs). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratchpad operations in the user's application. Any read of an unimplemented location will read as '0's.

The instruction set and architecture allow operations across all banks. The entire data memory may be accessed by Direct, Indirect or Indexed Addressing modes. Addressing modes are discussed later in this section.

To ensure that commonly used registers (select SFRs and select GPRs) can be accessed in a single cycle, PIC18 devices implement an Access Bank. This is a 256-byte memory space that provides fast access to select SFRs and the lower portion of GPR Bank 0 without using the BSR. **Section 6.3.2 "Access Bank**" provides a detailed description of the Access RAM.

#### 6.3.1 BANK SELECT REGISTER

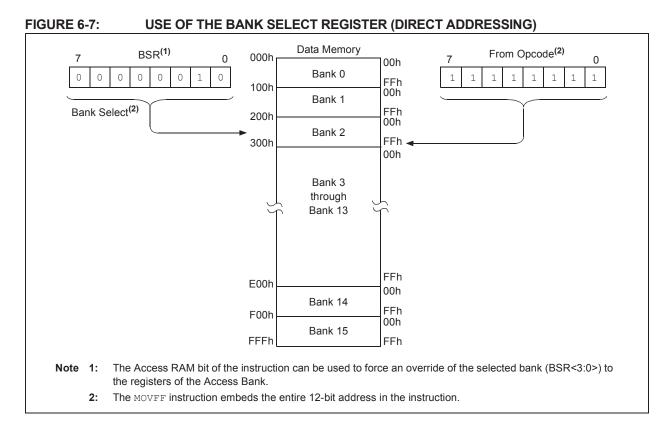

Large areas of data memory require an efficient addressing scheme to make rapid access to any address possible. Ideally, this means that an entire address does not need to be provided for each read or write operation. For PIC18 devices, this is accomplished with a RAM banking scheme. This divides the memory space into 16 contiguous banks of 256 bytes. Depending on the instruction, each location can be addressed directly by its full 12-bit address, or an 8-bit low-order address and a 4-bit Bank Pointer.

Most instructions in the PIC18 instruction set make use of the Bank Pointer, known as the Bank Select Register (BSR). This SFR holds the 4 MSbs of a location's address; the instruction itself includes the 8 LSbs. Only the four lower bits of the BSR are implemented (BSR<3:0>). The upper four bits are unused; they will always read '0' and cannot be written to. The BSR can be loaded directly by using the MOVLB instruction.

The value of the BSR indicates the bank in data memory. The 8 bits in the instruction show the location in the bank and can be thought of as an offset from the bank's lower boundary. The relationship between the BSR's value and the bank division in data memory is illustrated in Figure 6-7.

Because up to 16 registers can share the same low-order address, the user must always be careful to ensure that the proper bank is selected before performing a data read or write. For example, writing what should be program data to an 8-bit address of F9h, while the BSR is 0Fh, will end up resetting the PC.

While any bank can be selected, only those banks that are actually implemented can be read or written to. Writes to unimplemented banks are ignored, while reads from unimplemented banks will return '0's. Even so, the STATUS register will still be affected as if the operation was successful. The data memory map in Figure 6-6 indicates which banks are implemented.

In the core PIC18 instruction set, only the MOVFF instruction fully specifies the 12-bit address of the source and target registers. This instruction ignores the BSR completely when it executes. All other instructions include only the low-order address as an operand and must use either the BSR or the Access Bank to locate their target registers.

#### 6.3.2 ACCESS BANK

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected. Otherwise, data may be read from, or written to, the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 96 bytes of memory (00h-5Fh) in Bank 0 and the last 160 bytes of memory (60h-FFh) in Bank 15. The lower half is known as the Access RAM and is composed of GPRs. The upper half is where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 6-6).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0', however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle without updating the BSR first. For 8-bit addresses of 60h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 60h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 6.6.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

#### 6.3.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM, which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upward toward the bottom of the SFR area. GPRs are not initialized by a POR and are unchanged on all other Resets.

# REGISTER 9-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2 (ACCESS FA1h)

| R/W-0  | R/W-0 | R/W-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-------|-------|-----|--------|--------|--------|--------|

| OSCFIF | CM2IF | CM1IF | —   | BCL1IF | HLVDIF | TMR3IF | CCP2IF |

| bit 7  |       |       |     |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7 | OSCFIF: Oscillator Fail Interrupt Flag bit                                                                                                                    |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = The device oscillator failed, clock input has changed to INTOSC (must be cleared in software)</li> <li>0 = The device clock operating</li> </ul> |

| bit 6 | CM2IF: Comparator 2 Interrupt Flag bit                                                                                                                        |

|       | <ul> <li>1 = The comparator input has changed (must be cleared in software)</li> <li>0 = The comparator input has not changed</li> </ul>                      |

| bit 5 | CM1IF: Comparator 1 Interrupt Flag bit                                                                                                                        |

|       | <ul> <li>1 = The comparator input has changed (must be cleared in software)</li> <li>0 = The comparator input has not changed</li> </ul>                      |

| bit 4 | Unimplemented: Read as '0'                                                                                                                                    |

| bit 3 | BCL1IF: Bus Collision Interrupt Flag bit (MSSP1 module)                                                                                                       |

|       | <ul><li>1 = A bus collision occurred (must be cleared in software)</li><li>0 = No bus collision occurred</li></ul>                                            |

| bit 2 | HLVDIF: High/Low-Voltage Detect (HLVD) Interrupt Flag bit                                                                                                     |

|       | <ul> <li>1 = A High/Low-Voltage condition occurred (must be cleared in software)</li> <li>0 = An HLVD event has not occurred</li> </ul>                       |

| bit 1 | TMR3IF: TMR3 Overflow Interrupt Flag bit                                                                                                                      |

|       | <ul><li>1 = The TMR3 register overflowed (must be cleared in software)</li><li>0 = The TMR3 register did not overflow</li></ul>                               |

| bit 0 | CCP2IF: ECCP2 Interrupt Flag bit                                                                                                                              |

|       | <u>Capture mode:</u><br>1 = A TMR1/TMR3 register capture occurred (must be cleared in software)<br>0 = No TMR1/TMR3 register capture occurred                 |

|       | <u>Compare mode:</u><br>1 = A TMR1/TMR3 register compare match occurred (must be cleared in software)<br>0 = No TMR1/TMR3 register compare match occurred     |

|       | <u>PWM mode:</u><br>Unused in this mode.                                                                                                                      |

# PIC18F47J13 FAMILY

| Pin                      | Function            | TRIS<br>Setting | I/O | l/O<br>Type | Description                                                                                                                                  |

|--------------------------|---------------------|-----------------|-----|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/AN12/<br>C3IND/INT0/ | RB0                 | 1               | Ι   | TTL         | PORTB<0> data input; weak pull-up when the RBPU bit is cleared. Disabled when analog input is enabled. <sup>(1)</sup>                        |

| RP3                      |                     | 0               | 0   | DIG         | LATB<0> data output; not affected by an analog input.                                                                                        |

|                          | AN12                | 1               | Ι   | ANA         | A/D Input Channel 12. <sup>(1)</sup>                                                                                                         |

|                          | C3IND               | 1               | Ι   | ANA         | Comparator 3 Input D.                                                                                                                        |

|                          | INT0                | 1               | Ι   | ST          | External Interrupt 0 input.                                                                                                                  |

|                          | RP3                 | 1               | Ι   | ST          | Remappable Peripheral Pin 3 input.                                                                                                           |

|                          |                     | 0               | 0   | DIG         | Remappable Peripheral Pin 3 output.                                                                                                          |

| RB1/AN10/<br>C3INC/PMBE/ | RB1                 | 1               | Ι   | TTL         | PORTB<1> data input; weak pull-up when the $\overline{\text{RBPU}}$ bit is cleared. Disabled when an analog input is enabled. <sup>(1)</sup> |

| RTCC/RP4                 |                     | 0               | 0   | DIG         | LATB<1> data output; not affected by an analog input.                                                                                        |

|                          | AN10                | 1               | Ι   | ANA         | A/D Input Channel 10. <sup>(1)</sup>                                                                                                         |

|                          | C3INC               | 1               | Ι   | ANA         | Comparator 3 Input C.                                                                                                                        |

|                          | PMBE <sup>(3)</sup> | х               | 0   | DIG         | Parallel Master Port byte enable.                                                                                                            |

|                          | RTCC                | 0               | 0   | DIG         | Asynchronous serial transmit data output (USART module).                                                                                     |

|                          | RP4                 | 1               | Ι   | ST          | Remappable Peripheral Pin 4 input.                                                                                                           |

|                          |                     | 0               | 0   | DIG         | Remappable Peripheral Pin 4 output.                                                                                                          |

| RB2/AN8/<br>C2INC/CTED1/ | RB2                 | 1               | Ι   | TTL         | PORTB<2> data input; weak pull-up when the $\overline{\text{RBPU}}$ bit is cleared. Disabled when an analog input is enabled. <sup>(1)</sup> |

| PMA3/REFO/               |                     | 0               | 0   | DIG         | LATB<2> data output; not affected by an analog input.                                                                                        |

| RP5                      | AN8                 | 1               | Ι   | ANA         | A/D Input Channel 8. <sup>(1)</sup>                                                                                                          |

|                          | C2INC               | 1               | Ι   | ANA         | Comparator 2 Input C.                                                                                                                        |

|                          | CTED1               | 1               | Ι   | ST          | CTMU Edge 1 input.                                                                                                                           |

|                          | PMA3 <sup>(3)</sup> | Х               | 0   | DIG         | Parallel Master Port address.                                                                                                                |

|                          | REFO                | 0               | 0   | DIG         | Reference output clock.                                                                                                                      |

|                          | RP5                 | 1               | Ι   | ST          | Remappable Peripheral Pin 5 input.                                                                                                           |

|                          |                     | 0               | 0   | DIG         | Remappable Peripheral Pin 5 output.                                                                                                          |

| RB3/AN9/                 | RB3                 | 0               | 0   | DIG         | LATB<3> data output; not affected by analog input.                                                                                           |

| C3INA/CTED2/<br>PMA2/RP6 |                     | 1               | Ι   | TTL         | PORTB<3> data input; weak pull-up when the $\overline{\text{RBPU}}$ bit is cleared. Disabled when analog input is enabled. <sup>(1)</sup>    |

|                          | AN9                 | 1               | Ι   | ANA         | A/D Input Channel 9. <sup>(1)</sup>                                                                                                          |

| i F                      | C3INA               | 1               | Ι   | ANA         | Comparator 3 Input A.                                                                                                                        |

| i F                      | CTED2               | 1               | Ι   | ST          | CTMU Edge 2 input.                                                                                                                           |

| i F                      | PMA2 <sup>(3)</sup> | х               | 0   | DIG         | Parallel Master Port address.                                                                                                                |

| i F                      | RP6                 | 1               | Ι   | ST          | Remappable Peripheral Pin 6 input.                                                                                                           |

|                          |                     | 0               | 0   | DIG         | Remappable Peripheral Pin 6 output.                                                                                                          |

TABLE 10-5: PORTB I/O SUMMARY

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRISx bit does not affect port direction or is overridden for this option)

**Note 1:** Pins are configured as analog inputs by default on POR. Using these pins for digital inputs requires setting the appropriate bits in the ANCON1 register.

2: All other pin functions are disabled when ICSP<sup>™</sup> or ICD is enabled.

**3:** Only on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

4: Only on 28-pin devices (PIC18F26J13, PIC18F27J13, PIC18LF26J13 and PIC18LF27J13).

### REGISTER 10-33: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9 (BANKED EC9h)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | RP9R4 | RP9R3 | RP9R2 | RP9R1 | RP9R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                             |                    |  |  |

|-------------------|-------------------------------------------------------------|-----------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                            | U = Unimplemented bit, read | l as '0'           |  |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared        | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP9R<4:0>:** Peripheral Output Function is Assigned to RP9 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-34: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10 (BANKED ECAh)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | R/W = Readable bit, | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                    |  |  |  |

|-------------------|---------------------|-------------------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit                                       | , read as '0'      |  |  |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared                                        | x = Bit is unknown |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP10R<4:0>:** Peripheral Output Function is Assigned to RP10 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-35: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11 (BANKED ECBh)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

|       |     |     | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable bit, Writa | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                    |  |  |  |  |

|-------------------|----------------------------------------|-------------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                       | U = Unimplemented bit, read as '0'                          |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                       | '0' = Bit is cleared                                        | x = Bit is unknown |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP11R<4:0>:** Peripheral Output Function is Assigned to RP11 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### 13.5.1 USING TIMER1 AS A CLOCK SOURCE

The Timer1 oscillator is also available as a clock source in power-managed modes. By setting the clock select bits, SCS<1:0> (OSCCON<1:0>), to '01', the device switches to SEC\_RUN mode. Both the CPU and peripherals are clocked from the Timer1 oscillator. If the IDLEN bit (OSCCON<7>) is cleared and a SLEEP instruction is executed, the device enters SEC\_IDLE mode. Additional details are available in Section 4.0 "Low-Power Modes".

Whenever the Timer1 oscillator is providing the clock source, the Timer1 system clock status flag, SOSCRUN (OSCCON2<6>), is set. This can be used to determine the controller's current clocking mode. It can also indicate the clock source currently being used by the Fail-Safe Clock Monitor. If the Clock Monitor is enabled and the Timer1 oscillator fails while providing the clock, polling the SOSCRUN bit will indicate whether the clock is being provided by the Timer1 oscillator or another source.

#### 13.5.2 TIMER1 OSCILLATOR LAYOUT CONSIDERATIONS

The Timer1 oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity. This is especially true when the oscillator is configured for extremely Low-Power mode (SOSCSEL = 0b01).

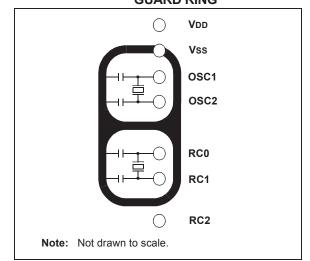

The oscillator circuit, displayed in Figure 13-2, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than VSS or VDD.

If a high-speed circuit must be located near the oscillator (such as the ECCP1 pin in Output Compare or PWM mode, or the primary oscillator using the OSC2 pin), a grounded guard ring around the oscillator circuit, as displayed in Figure 13-3, may be helpful when used on a single-sided PCB or in addition to a ground plane.

#### FIGURE 13-3:

OSCILLATOR CIRCUIT WITH GROUNDED GUARD RING

In the Low Drive Level mode, SOSCSEL = 0b01, it is critical that the RC2 I/O pin signals be kept away from the oscillator circuit. Configuring RC2 as a digital output, and toggling it, can potentially disturb the oscillator circuit, even with relatively good PCB layout. If possible, it is recommended to either leave RC2 unused, or use it as an input pin with a slew rate limited signal source. If RC2 must be used as a digital output, it may be necessary to use the Higher Drive Level Oscillator mode (SOSCSEL = 0b11) with many PCB layouts. Even in the High Drive Level mode, careful layout procedures should still be followed when designing the oscillator circuit.

In addition to dV/dt induced noise considerations, it is also important to ensure that the circuit board is clean. Even a very small amount of conductive soldering flux residue can cause PCB leakage currents which can overwhelm the oscillator circuit.

# 13.6 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled or disabled by setting or clearing the Timer1 Interrupt Enable bit, TMR1IE (PIE1<0>).

# PIC18F47J13 FAMILY

#### REGISTER 17-5: ALRMRPT: ALARM REPEAT COUNTER (ACCESS F46h)

| ARPT7         ARPT6         ARPT5         ARPT4         ARPT3         ARPT2         ARPT1         ARPT0           bit 7         bit 0 | R/W-0 |

|---------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| bit 7 bit 0                                                                                                                           | ARPT7 | ARPT6 | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 |

|                                                                                                                                       | bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits 11111111 = Alarm will repeat 255 more times

00000000 = Alarm will not repeat

The counter decrements on any alarm event. The counter is prevented from rolling over from 00h to FFh unless CHIME = 1.

### 17.1.4 RTCEN BIT WRITE

An attempt to write to the RTCEN bit while RTCWREN = 0 will be ignored. RTCWREN must be set before a write to RTCEN can take place.

Like the RTCEN bit, the RTCVALH and RTCVALL registers can only be written to when RTCWREN = 1. A write to these registers, while RTCWREN = 0, will be ignored.

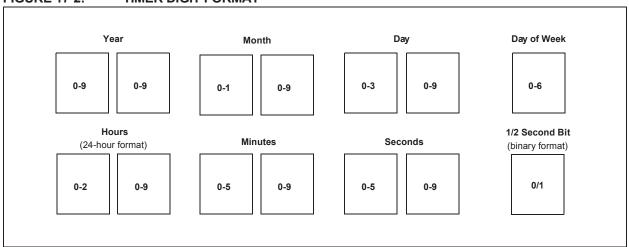

FIGURE 17-2: TIMER DIGIT FORMAT

## 17.2 Operation

#### 17.2.1 REGISTER INTERFACE

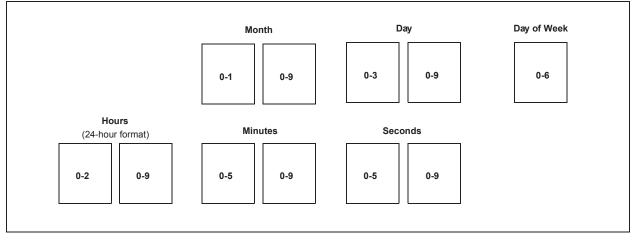

The register interface for the RTCC and alarm values is implemented using the Binary Coded Decimal (BCD) format. This simplifies the firmware when using the module, as each of the digits is contained within its own 4-bit value (see Figure 17-2 and Figure 17-3).

#### FIGURE 17-3: ALARM DIGIT FORMAT

# 19.4 PWM (Enhanced Mode)

The Enhanced PWM mode can generate a PWM signal on up to four different output pins with up to 10 bits of resolution. It can do this through four different PWM Output modes:

- Single PWM mode

- Half-Bridge PWM mode

- Full-Bridge PWM, Forward mode

- Full-Bridge PWM, Reverse mode

To select an Enhanced PWM mode, the PxM bits of the CCPxCON register must be set appropriately.

The PWM outputs are multiplexed with I/O pins and are designated: PxA, PxB, PxC and PxD. The polarity of the PWM pins is configurable and is selected by setting the CCPxM bits in the CCPxCON register appropriately.

Table 19-1 provides the pin assignments for each Enhanced PWM mode.

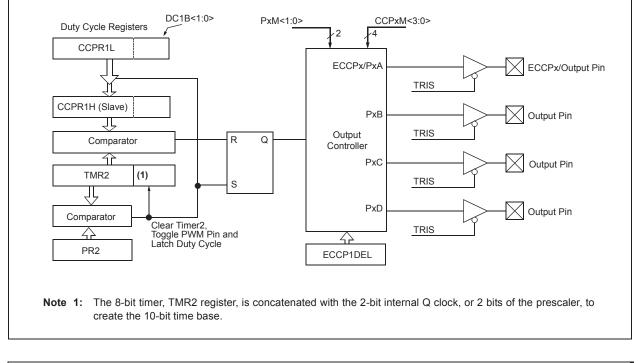

Figure 19-3 provides an example of a simplified block diagram of the Enhanced PWM module.

**Note:** To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

#### FIGURE 19-3: SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE EXAMPLE

Note 1: The TRIS register value for each PWM output must be configured appropriately.2: Any pin not used by an Enhanced PWM mode is available for alternate pin functions.

When a shutdown event occurs, two things happen:

- The ECCPxASE bit is set to '1'. The ECCPxASE will remain set until cleared in firmware or an auto-restart occurs. (See Section 19.4.5 "Auto-Restart Mode".)

- The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs (PxA/PxC and

PxB/PxD). The state of each pin pair is determined by the PSSxAC and PSSxBD bits (ECCPxAS<3:0>).

Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

#### REGISTER 19-4: ECCPxAS: ECCP1/2/3 AUTO-SHUTDOWN CONTROL REGISTER (1, ACCESS FBEh; 2, FB8h; 3, BANKED F19h)

| R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|----------|----------|----------|----------|---------|---------|---------|---------|

| ECCPxASE | ECCPxAS2 | ECCPxAS1 | ECCPxAS0 | PSSxAC1 | PSSxAC0 | PSSxBD1 | PSSxBD0 |

| bit 7    |          |          |          |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | ECCPxASE: ECCP Auto-Shutdown Event Status bit                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = A shutdown event has occurred; ECCP outputs are in a shutdown state</li> <li>0 = ECCP outputs are operating</li> </ul>                                                                                                                                                                                                                                                                                                                                       |

| bit 6-4 | ECCPxAS<2:0>: ECCP Auto-Shutdown Source Select bits                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>000 = Auto-shutdown is disabled</li> <li>001 = Comparator, C1OUT, output is high</li> <li>010 = Comparator, C2OUT, output is high</li> <li>011 = Either comparator, C1OUT or C2OUT, is high</li> <li>100 = VIL on FLT0 pin</li> <li>101 = VIL on FLT0 pin or comparator, C1OUT, output is high</li> <li>110 = VIL on FLT0 pin or comparator, C2OUT, output is high</li> <li>111 = VIL on FLT0 pin or comparator, C1OUT, or comparator, C2OUT, is high</li> </ul> |

| bit 3-2 | PSSxAC<1:0>: PxA and PxC Pins Shutdown State Control bits                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | 00 = Drive pins, PxA and PxC, to '0'<br>01 = Drive pins, PxA and PxC, to '1'<br>1x = PxA and PxC pins tri-state                                                                                                                                                                                                                                                                                                                                                           |

| bit 1-0 | PSSxBD<1:0>: PxB and PxD Pins Shutdown State Control bits<br>00 = Drive pins, PxB and PxD, to '0'<br>01 = Drive pins, PxB and PxD, to '1'<br>1x = PxB and PxD pins tri-state                                                                                                                                                                                                                                                                                              |

| Note 1: | The auto-shutdown condition is a level-based signal, not an edge-based signal. As long as the level is                                                                                                                                                                                                                                                                                                                                                                    |

|         | present, the auto-shutdown will persist.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2:      | Writing to the ECCPxASE bit is disabled while an auto-shutdown condition persists.                                                                                                                                                                                                                                                                                                                                                                                        |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

3: Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart), the PWM signal will always restart at the beginning of the next PWM period.

### REGISTER 20-2: SSPxCON1: MSSPx CONTROL REGISTER 1 (SPI MODE) (1, ACCESS FC6h; 2, F72h)

|            |                                                                                              |                                        | -                                                                                                |                                                                                  |                       |                      |                      |

|------------|----------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------|----------------------|----------------------|

| R/W-0      | R/C-0                                                                                        | R/W-0                                  | R/W-0                                                                                            | R/W-0                                                                            | R/W-0                 | R/W-0                | R/W-0                |

| WCOL       | SSPOV <sup>(1)</sup>                                                                         | SSPEN <sup>(2)</sup>                   | CKP                                                                                              | SSPM3 <sup>(3)</sup>                                                             | SSPM2 <sup>(3)</sup>  | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7      |                                                                                              |                                        |                                                                                                  |                                                                                  |                       |                      | bit 0                |

|            |                                                                                              | 0 01 11                                | 1.14                                                                                             |                                                                                  |                       |                      |                      |

| Legend:    |                                                                                              | C = Clearable                          |                                                                                                  |                                                                                  |                       |                      |                      |

| R = Reada  |                                                                                              | W = Writable                           |                                                                                                  | -                                                                                | nented bit, read      |                      |                      |

| -n = Value | at POR                                                                                       | '1' = Bit is set                       |                                                                                                  | '0' = Bit is clea                                                                | ared                  | x = Bit is unkr      | nown                 |

| bit 7      | 1 = The SSP                                                                                  | •                                      |                                                                                                  | e it is still transm                                                             | nitting the previ     | ous word (mus        | t be cleared in      |

|            | software)<br>0 = No collisi                                                                  | /                                      |                                                                                                  |                                                                                  |                       |                      |                      |

| bit 6      |                                                                                              | eive Overflow I                        | ndicator hit(1)                                                                                  |                                                                                  |                       |                      |                      |

| bit 0      | SPI Slave mo                                                                                 |                                        |                                                                                                  |                                                                                  |                       |                      |                      |

|            | flow, the                                                                                    | data in SSPxS<br>F, even if only tr    | R is lost. Over                                                                                  | BUF register is s<br>flow can only or<br>a, to avoid settir                      | ccur in Slave n       | node. The user       | must read the        |

| bit 5      |                                                                                              | ter Synchronou                         | s Serial Port F                                                                                  | nable bit <sup>(2)</sup>                                                         |                       |                      |                      |

|            | 1 = Enables s                                                                                | serial port and o                      | onfigures SCI                                                                                    | <pre><x, as="" i="" o="" p<="" pins="" pre="" sdix="" sdox,="" se=""></x,></pre> |                       | erial port pins      |                      |

| bit 4      |                                                                                              | Polarity Select b                      |                                                                                                  |                                                                                  | -                     |                      |                      |

|            | 1 = Idle state                                                                               | for clock is a hi<br>for clock is a lo | igh level                                                                                        |                                                                                  |                       |                      |                      |

| bit 3-0    | SSPM<3:0>:                                                                                   | Master Synchr                          | onous Serial F                                                                                   | Port Mode Selec                                                                  | t bits <sup>(3)</sup> |                      |                      |

|            | 0101 = SPI S<br>0100 = SPI S<br>0011 = SPI N<br>0010 = SPI N<br>0001 = SPI N<br>1010 = SPI N | Slave mode, clo                        | ck = SCKx pin<br>ck = SCKx pin<br>ock = TMR2 o<br>ock = Fosc/64<br>ock = Fosc/16<br>ock = Fosc/8 | ; <u>SSx</u> pin contro<br>; SSx pin contro<br>utput/2                           | ol disabled, SS       | x can be used        | as I/O pin           |

|            | In Master mode, t<br>writing to the SSF                                                      |                                        |                                                                                                  | e each new rec                                                                   | eption (and tra       | insmission) is ir    | nitiated by          |

- 2: When enabled, this pin must be properly configured as input or output.

- 3: Bit combinations not specifically listed here are either reserved or implemented in I<sup>2</sup>C mode only.

# REGISTER 20-5: SSPxSTAT: MSSPx STATUS REGISTER (I<sup>2</sup>C MODE) (1, ACCESS FC7h; 2, F73h)

| R/W-1      | R/W-1                      | R-1                                   | R-1                     | R-1              | R-1                  | R-1               | R-1      |

|------------|----------------------------|---------------------------------------|-------------------------|------------------|----------------------|-------------------|----------|

| SMP        | CKE                        | D/A                                   | P <sup>(1)</sup>        | S <sup>(1)</sup> | R/W <sup>(2,3)</sup> | UA                | BF       |

| bit 7      |                            |                                       |                         |                  |                      |                   | bit 0    |

|            |                            |                                       |                         |                  |                      |                   |          |

| Legend:    |                            |                                       | 1.11                    |                  |                      | 1                 |          |

| R = Read   |                            | W = Writable                          |                         | -                | emented bit, rea     |                   |          |

| -n = Value | at POR                     | '1' = Bit is se                       | ľ                       | '0' = Bit is cl  | eared                | x = Bit is unkr   | IOWN     |

| bit 7      | SMP: Slew                  | Rate Control bit                      | t                       |                  |                      |                   |          |

|            | In Master or               | Slave mode:                           |                         |                  |                      |                   |          |

|            |                            |                                       |                         | •                | de (100 kHz an       | d 1 MHz)          |          |

| bit 6      | 0 = Slew ra                | ite control is en:                    | abled for High-s        | speed mode (4    | 400 KHZ)             |                   |          |

| DILO       |                            | Slave mode:                           |                         |                  |                      |                   |          |

|            |                            | SMBus specific                        | inputs                  |                  |                      |                   |          |

|            |                            | SMBus specific                        |                         |                  |                      |                   |          |

| bit 5      | D/A: Data/A                | ddress bit                            |                         |                  |                      |                   |          |

|            | In Master m<br>Reserved.   | ode:                                  |                         |                  |                      |                   |          |

|            | In Slave mo                | de:                                   |                         |                  |                      |                   |          |

|            |                            | s that the last b                     | yte received or         | transmitted wa   | as data              |                   |          |

|            |                            | s that the last b                     | yte received or         | transmitted wa   | as address           |                   |          |

| bit 4      | P: Stop bit <sup>(1</sup>  |                                       |                         |                  |                      |                   |          |

|            |                            | s that a Stop bit<br>was not detected |                         | cted last        |                      |                   |          |

| bit 3      | S: Start bit <sup>(1</sup> |                                       |                         |                  |                      |                   |          |

|            | 1 = Indicate               | s that a Start bi                     | has been dete           | cted last        |                      |                   |          |

|            |                            | was not detected                      |                         |                  |                      |                   |          |

| bit 2      |                            | Write Informatio                      | on bit <sup>(2,3)</sup> |                  |                      |                   |          |

|            | In Slave mo                | <u>de:</u>                            |                         |                  |                      |                   |          |

|            | 1 = Read<br>0 = Write      |                                       |                         |                  |                      |                   |          |

|            | In Master m                | ode:                                  |                         |                  |                      |                   |          |

|            |                            | t is in progress                      |                         |                  |                      |                   |          |

|            |                            | t is not in progr                     |                         |                  |                      |                   |          |

| bit 1      | •                          | Address bit (10                       |                         |                  |                      | D an ainte a      |          |

|            |                            | s that the user i<br>does not need    | -                       | e the address    | in the SSPxADI       | Dregister         |          |

| bit 0      |                            | ull Status bit                        |                         |                  |                      |                   |          |

|            | In Transmit                | mode:                                 |                         |                  |                      |                   |          |

|            | 1 = SSPxBL                 |                                       |                         |                  |                      |                   |          |

|            | 0 = SSPxBl                 |                                       |                         |                  |                      |                   |          |

|            | In Receive r               | <u>node:</u><br>JF is full (does ı    | not include the         | ACK and Stop     | bits)                |                   |          |

|            |                            | JF is empty (do                       |                         |                  | ,                    |                   |          |

| Note 1:    | This bit is cleare         | ed on Reset and                       | when SSPEN              | is cleared.      |                      |                   |          |

| 2:         | This bit holds th          |                                       |                         |                  | ess match. This      | bit is only valid | from the |

|            | address match f            | to the next Start                     | bit, Stop bit or        | not ACK bit.     |                      |                   |          |

3: ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSPx is in Active mode.

### 29.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

### 30.2 DC Characteristics: Power-Down and Supply Current PIC18F47J13 Family (Industrial) (Continued)

| PIC18LF47J   | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |     |       |    |       |                                        |                                |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-------|----|-------|----------------------------------------|--------------------------------|--|--|

| PIC18F47J1   | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |     |       |    |       |                                        |                                |  |  |

| Param<br>No. | Тур                                                                                                                                | Max | Units |    | Conc  | litions                                |                                |  |  |

|              | PIC18LFXXJ13                                                                                                                       | 9   | 45    | μA | -40°C |                                        |                                |  |  |

|              |                                                                                                                                    | 9   | 45    | μA | +25°C | VDD = 2.5V,<br>VDDCORE = 2.5V          |                                |  |  |

|              |                                                                                                                                    | 12  | 61    | μA | +85°C |                                        |                                |  |  |

|              | PIC18FXXJ13                                                                                                                        | 24  | 95    | μA | -40°C |                                        | Fosc = 32 kHz <sup>(3)</sup> , |  |  |

|              |                                                                                                                                    | 28  | 95    | μA | +25°C | VDD = 2.15V,<br>VDDCORE = 10 μF        | SEC_RUN mode,                  |  |  |

|              |                                                                                                                                    | 35  | 105   | μA | +85°C | το μι                                  | SOSCSEL = 0b01                 |  |  |

|              | PIC18FXXJ13                                                                                                                        | 27  | 110   | μA | -40°C |                                        |                                |  |  |

|              |                                                                                                                                    | 31  | 110   | μA | +25°C | VDD = $3.3V$ ,<br>VDDCORE = $10 \mu$ F |                                |  |  |

|              |                                                                                                                                    | 35  | 150   | μA | +85°C | το μι                                  |                                |  |  |

|              | PIC18LFXXJ13                                                                                                                       | 2.5 | 31    | μA | -40°C |                                        |                                |  |  |

|              |                                                                                                                                    | 3.0 | 31    | μA | +25°C | VDD = 2.5V,<br>VDDCORE = 2.5V          |                                |  |  |

|              |                                                                                                                                    | 6.1 | 50    | μA | +85°C | 12300AL 2.0V                           |                                |  |  |

|              | PIC18FXXJ13                                                                                                                        | 19  | 87    | μA | -40°C |                                        | Fosc = 32 kHz <sup>(3)</sup> , |  |  |

|              |                                                                                                                                    | 24  | 89    | μA | +25°C | VDD = 2.15V,<br>VDDCORE = 10 μF        | SEC_IDLE mode,                 |  |  |

|              |                                                                                                                                    | 31  | 97    | μA | +85°C | το μι                                  | SOSCSEL = 0b01                 |  |  |

|              | PIC18FXXJ13                                                                                                                        | 21  | 100   | μA | -40°C |                                        |                                |  |  |

|              |                                                                                                                                    | 25  | 100   | μΑ | +25°C | VDD = $3.3V$ ,<br>VDDCORE = $10 \mu$ F |                                |  |  |

|              |                                                                                                                                    | 31  | 140   | μA | +85°C | νουσικέ – το μι                        |                                |  |  |