Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 10x10b/12b                                                             |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

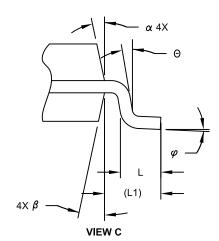

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f26j13-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

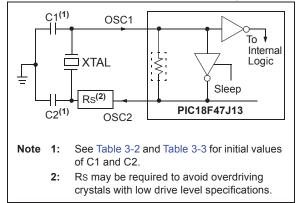

# 3.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

In HS and HSPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 3-2 displays the pin connections.

The oscillator design requires the use of a parallel resonant crystal.

| Note: | Use of a series resonant crystal may give |           |     |    |     |         |  |  |  |

|-------|-------------------------------------------|-----------|-----|----|-----|---------|--|--|--|

|       | а                                         | frequency | out | of | the | crystal |  |  |  |

|       | manufacturer's specifications.            |           |     |    |     |         |  |  |  |

#### FIGURE 3-2: CRYSTAL/CERAMIC RESONATOR OPERATION (HS OR HSPLL CONFIGURATION)

# TABLE 3-2:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Typical Capacitor Values Used: |                     |                |                |  |  |  |

|--------------------------------|---------------------|----------------|----------------|--|--|--|

| Mode                           | Freq                | OSC1           | OSC2           |  |  |  |

| HS                             | 8.0 MHz<br>16.0 MHz | 27 pF<br>22 pF | 27 pF<br>22 pF |  |  |  |

Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. **These values are not optimized**.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following Table 3-3 for additional information.

| Resonators Used: |

|------------------|

| 4.0 MHz          |

| 8.0 MHz          |

| 16.0 MHz         |

# TABLE 3-3:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq | Typical Capacitor Values<br>Tested: |       |  |

|----------|-----------------|-------------------------------------|-------|--|

|          | Freq            | C1                                  | C2    |  |

| HS       | 4 MHz           | 27 pF                               | 27 pF |  |

|          | 8 MHz           | 22 pF                               | 22 pF |  |

| 16 MHz   |                 | 18 pF                               | 18 pF |  |

Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. **These values are not optimized.**

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

| Crystals Used: |

|----------------|

| 4 MHz          |

| 8 MHz          |

| 16 MHz         |

- Note 1: Higher capacitance not only increases the stability of oscillator, but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **3:** Rs may be required to avoid overdriving crystals with low drive level specification.

- **4:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

An internal postscaler allows users to select a clock frequency other than that of the crystal or resonator. Frequency division is determined by the CPDIV Configuration bits. Users may select a clock frequency of the oscillator frequency, or 1/2, 1/3 or 1/6 of the frequency.

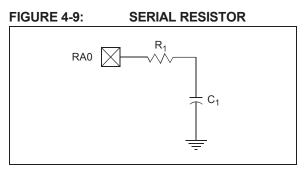

A series resistor between RA0 and the external capacitor provides overcurrent protection for the RA0/AN0/C1INA/ULPWU/RP0 pin and can allow for software calibration of the time-out (see Figure 4-9).

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired interrupt delay. This technique will compensate for the affects of temperature, voltage and component accuracy. The ULPWU peripheral can also be configured as a simple Programmable Low-Voltage Detect (LVD) or temperature sensor.

| Note: | For more information, refer to AN879, |

|-------|---------------------------------------|

|       | Using the Microchip Ultra Low-Power   |

|       | Wake-up Module application note       |

|       | (DS00879).                            |

# 4.8 Peripheral Module Disable

All peripheral modules (except for I/O ports) also have a second control bit that can disable their functionality. These bits, known as the Peripheral Module Disable (PMD) bits, are generically named "xxxMD" (using "xxx" as the mnemonic version of the module's name).

These bits are located in the PMDISx special function registers. In contrast to the module enable bits (generically named "xxxEN" and located in bit position seven of the control registers), the PMD bits must be set (= 1) to disable the modules.

While the PMD and module enable bits both disable a peripheral's functionality, the PMD bit completely shuts down the peripheral, effectively powering down all circuits and removing all clock sources. This has the additional effect of making any of the module's control and buffer registers, mapped in the SFR space, unavailable for operations. Essentially, the peripheral ceases to exist until the PMD bit is cleared.

This differs from using the module enable bit, which allows the peripheral to be reconfigured and buffer registers preloaded, even when the peripheral's operations are disabled.

The PMD bits are most useful in highly power-sensitive applications. In these cases, the bits can be set before the main body of the application to remove peripherals that will not be needed at all.

| Register | Bit 7                | Bit 6   | Bit 5                 | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on POR, BOR |

|----------|----------------------|---------|-----------------------|---------|---------|--------|--------|--------|-------------------|

| PMDIS3   | CCP10MD              | CCP9MD  | CCP8MD                | CCP7MD  | CCP6MD  | CCP5MD | CCP4MD | _      | 0000 000-         |

| PMDIS2   | —                    | TMR8MD  | —                     | TMR6MD  | TMR5MD  | CMP3MD | CMP2MD | CMP1MD | -0-0 0000         |

| PMDIS1   | PSPMD <sup>(1)</sup> | CTMUMD  | RTCCMD <sup>(2)</sup> | TMR4MD  | TMR3MD  | TMR2MD | TMR1MD | _      | 0000 000-         |

| PMDIS0   | ECCP3MD              | ECCP2MD | ECCP1MD               | UART2MD | UART1MD | SPI2MD | SP11MD | ADCMD  | 0000 0000         |

### TABLE 4-2:LOW-POWER MODE REGISTERS

Note 1: Not implemented on 28-pin devices (PIC18F26J13, PIC18F27J13, PIC18LF26J13 and PIC18LF27J13).

2: To prevent accidental RTCC changes, the RTCCMD bit is normally locked. Use the following unlock sequence (with interrupts disabled) to successfully modify the RTCCMD bit:

1. Write 55h to EECON2.

2. Write 0AAh to EECON2.

3. Immediately write the modified RTCCMD setting to PMDIS1.

# REGISTER 9-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2 (ACCESS FA1h)

| R/W-0  | R/W-0 | R/W-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-------|-------|-----|--------|--------|--------|--------|

| OSCFIF | CM2IF | CM1IF | —   | BCL1IF | HLVDIF | TMR3IF | CCP2IF |

| bit 7  |       |       |     |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7 | OSCFIF: Oscillator Fail Interrupt Flag bit                                                                                                                    |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = The device oscillator failed, clock input has changed to INTOSC (must be cleared in software)</li> <li>0 = The device clock operating</li> </ul> |

| bit 6 | CM2IF: Comparator 2 Interrupt Flag bit                                                                                                                        |

|       | <ul> <li>1 = The comparator input has changed (must be cleared in software)</li> <li>0 = The comparator input has not changed</li> </ul>                      |

| bit 5 | CM1IF: Comparator 1 Interrupt Flag bit                                                                                                                        |

|       | <ul> <li>1 = The comparator input has changed (must be cleared in software)</li> <li>0 = The comparator input has not changed</li> </ul>                      |

| bit 4 | Unimplemented: Read as '0'                                                                                                                                    |

| bit 3 | BCL1IF: Bus Collision Interrupt Flag bit (MSSP1 module)                                                                                                       |

|       | <ul><li>1 = A bus collision occurred (must be cleared in software)</li><li>0 = No bus collision occurred</li></ul>                                            |

| bit 2 | HLVDIF: High/Low-Voltage Detect (HLVD) Interrupt Flag bit                                                                                                     |

|       | <ul> <li>1 = A High/Low-Voltage condition occurred (must be cleared in software)</li> <li>0 = An HLVD event has not occurred</li> </ul>                       |

| bit 1 | TMR3IF: TMR3 Overflow Interrupt Flag bit                                                                                                                      |

|       | <ul><li>1 = The TMR3 register overflowed (must be cleared in software)</li><li>0 = The TMR3 register did not overflow</li></ul>                               |

| bit 0 | CCP2IF: ECCP2 Interrupt Flag bit                                                                                                                              |

|       | <u>Capture mode:</u><br>1 = A TMR1/TMR3 register capture occurred (must be cleared in software)<br>0 = No TMR1/TMR3 register capture occurred                 |

|       | <u>Compare mode:</u><br>1 = A TMR1/TMR3 register compare match occurred (must be cleared in software)<br>0 = No TMR1/TMR3 register compare match occurred     |

|       | <u>PWM mode:</u><br>Unused in this mode.                                                                                                                      |

# REGISTER 10-27: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTER 3 (BANKED EC3h)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | RP3R4 | RP3R3 | RP3R2 | RP3R1 | RP3R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                         |  |  |  |

|-------------------|-------------------------------------------------------------|-----------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit                                            | U = Unimplemented bit, read as '0'      |  |  |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared x = Bit is unknown |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP3R<4:0>:** Peripheral Output Function is Assigned to RP3 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-28: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTER 4 (BANKED EC4h)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | RP4R4 | RP4R3 | RP4R2 | RP4R1 | RP4R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | R/W = Readable bit, \ | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |  |  |  |

|-------------------|-----------------------|-------------------------------------------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit                                       | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared                                        | x = Bit is unknown                 |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP4R<4:0>:** Peripheral Output Function is Assigned to RP4 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-29: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTER 5 (BANKED EC5h)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

|       | —   | —   | RP5R4 | RP5R3 | RP5R2 | RP5R1 | RP5R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                         |  |  |  |

|-------------------|-------------------------------------------------------------|-----------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit                                            | U = Unimplemented bit, read as '0'      |  |  |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared x = Bit is unknown |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP5R<4:0>:** Peripheral Output Function is Assigned to RP5 Output Pin bits (see Table 10-14 for peripheral function numbers)

## REGISTER 10-36: RPOR12: PERIPHERAL PIN SELECT OUTPUT REGISTER 12 (BANKED ECCh)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP12R4 | RP12R3 | RP12R2 | RP12R1 | RP12R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | R/W = Readable bit, V | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |  |  |  |

|-------------------|-----------------------|-------------------------------------------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit                                       | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared                                        | x = Bit is unknown                 |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP12R<4:0>:** Peripheral Output Function is Assigned to RP12 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-37: RPOR13: PERIPHERAL PIN SELECT OUTPUT REGISTER 13 (BANKED ECDh)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP13R4 | RP13R3 | RP13R2 | RP13R1 | RP13R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | R/W = Readable bit, | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |  |  |  |

|-------------------|---------------------|-------------------------------------------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit                                       | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared                                        | x = Bit is unknown                 |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP13R<4:0>:** Peripheral Output Function is Assigned to RP13 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-38: RPOR14: PERIPHERAL PIN SELECT OUTPUT REGISTER 14 (BANKED ECEh)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

|       | —   | —   | RP14R4 | RP14R3 | RP14R2 | RP14R1 | RP14R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable bit, W | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |  |  |  |

|-------------------|------------------------------------|-------------------------------------------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit                   | U = Unimplemented bit,                                      | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared                                        | x = Bit is unknown                 |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP14R<4:0>:** Peripheral Output Function is Assigned to RP14 Output Pin bits (see Table 10-14 for peripheral function numbers)

# REGISTER 11-5: PMEH: PARALLEL PORT ENABLE REGISTER HIGH BYTE (BANKED F57h)<sup>(1)</sup>

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|--------|--------|--------|--------|--------|--------|-------|-------|

| PTEN15 | PTEN14 | PTEN13 | PTEN12 | PTEN11 | PTEN10 | PTEN9 | PTEN8 |

| bit 7  |        |        |        |        |        |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7-6 | PTEN<15:14>: PMCS Port Enable bits                                                                                      |

|---------|-------------------------------------------------------------------------------------------------------------------------|

|         | 1 = PMA<15:14> function as either PMA<15:14> or PMCS<br>0 = PMA<15:14> function as port I/O                             |

| bit 5-0 | PTEN<13:8>: PMP Address Port Enable bits                                                                                |

|         | <ul> <li>1 = PMA&lt;13:8&gt; function as PMP address lines</li> <li>0 = PMA&lt;13:8&gt; function as port I/O</li> </ul> |

**Note 1:** This register is only available on 44-pin devices.

# REGISTER 11-6: PMEL: PARALLEL PORT ENABLE REGISTER LOW BYTE (BANKED F56h)<sup>(1)</sup>

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PTEN7 | PTEN6 | PTEN5 | PTEN4 | PTEN3 | PTEN2 | PTEN1 | PTEN0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7-2 | PTEN<7:2>: PMP Address Port Enable bits                     |

|---------|-------------------------------------------------------------|

|         | 1 = PMA<7:2> function as PMP address lines                  |

|         | 0 = PMA<7:2> function as port I/O                           |

| bit 1-0 | PTEN<1:0>: PMALH/PMALL Strobe Enable bits                   |

|         | 1 = PMA<1:0> function as either PMA<1:0> or PMALH and PMALL |

|         | 0 = PMA<1:0> pads functions as port I/O                     |

Note 1: This register is only available on 44-pin devices.

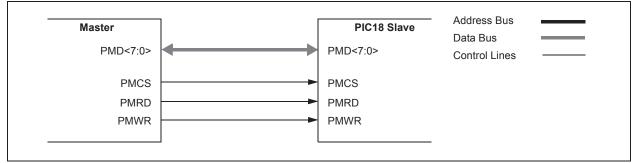

# 11.2 Slave Port Modes

The primary mode of operation for the module is configured using the MODE<1:0> bits in the PMMODEH register. The setting affects whether the module acts as a slave or a master and it determines the usage of the control pins.

#### 11.2.1 LEGACY MODE (PSP)

In Legacy mode (PMMODEH<1:0> = 00 and PMPEN = 1), the module is configured as a Parallel Slave Port (PSP) with the associated enabled module

pins dedicated to the module. In this mode, an external device, such as another microcontroller or microprocessor, can asynchronously read and write data using the 8-bit data bus (PMD<7:0>), the read (PMRD), write (PMWR) and chip select (PMCS) inputs. It acts as a slave on the bus and responds to the read/write control signals.

Figure 11-2 displays the connection of the PSP. When chip select is active and a write strobe occurs (PMCS = 1 and PMWR = 1), the data from PMD<7:0> is captured into the PMDIN1L register.

### FIGURE 11-2: LEGACY PARALLEL SLAVE PORT EXAMPLE

| TADLE IT-2.                |                                            |                                                                 |              |         |         |           |           |        |  |  |

|----------------------------|--------------------------------------------|-----------------------------------------------------------------|--------------|---------|---------|-----------|-----------|--------|--|--|

| Name                       | Bit 7                                      | Bit 6                                                           | Bit 5        | Bit 4   | Bit 3   | Bit 2     | Bit 1     | Bit 0  |  |  |

| INTCON                     | GIE/GIEH                                   | PEIE/GIEL                                                       | TMR0IE       | INT0IE  | RBIE    | TMR0IF    | INT0IF    | RBIF   |  |  |

| PIR1                       | PMPIF <sup>(2)</sup>                       | ADIF                                                            | RC1IF        | TX1IF   | SSP1IF  | CCP1IF    | TMR2IF    | TMR1IF |  |  |

| PIE1                       | PMPIE <sup>(2)</sup>                       | PMPIE <sup>(2)</sup> ADIE RC1IE TX1IE SSP1IE CCP1IE TMR2IE TMR1 |              |         |         |           |           |        |  |  |

| IPR1                       | PMPIP <sup>(2)</sup>                       | MPIP <sup>(2)</sup> ADIP RC1IP TX1IP SSP1IP CCP1IP TMR2IP TMF   |              |         |         |           |           |        |  |  |

| PMCONH <sup>(2)</sup>      | PMPEN                                      | —                                                               | —            | ADRMUX1 | ADRMUX0 | PTBEEN    | PTWREN    | PTRDEN |  |  |

| PMCONL <sup>(2)</sup>      | CSF1                                       | CSF0                                                            | ALP          | _       | CS1P    | BEP       | WRSP      | RDSP   |  |  |

| PMADDRH <sup>(1,2)</sup> / | —                                          | CS1 Parallel Master Port Address High Byte                      |              |         |         |           |           |        |  |  |

| PMDOUT1H <sup>(1,2)</sup>  | Parallel Port                              | Parallel Port Out Data High Byte (Buffer 1)                     |              |         |         |           |           |        |  |  |

| PMADDRL <sup>(1,2)</sup> / | Parallel Mas                               | Parallel Master Port Address Low Byte                           |              |         |         |           |           |        |  |  |

| PMDOUT1L <sup>(1,2)</sup>  | Parallel Port Out Data Low Byte (Buffer 0) |                                                                 |              |         |         |           |           |        |  |  |

| PMDOUT2H <sup>(2)</sup>    | Parallel Port                              | Parallel Port Out Data High Byte (Buffer 3)                     |              |         |         |           |           |        |  |  |

| PMDOUT2L <sup>(2)</sup>    | Parallel Port                              | t Out Data Lo                                                   | w Byte (Bu   | ffer 2) |         |           |           |        |  |  |

| PMDIN1H <sup>(2)</sup>     | Parallel Port                              | t In Data High                                                  | n Byte (Buff | er 1)   |         |           |           |        |  |  |

| PMDIN1L <sup>(2)</sup>     | Parallel Port                              | t In Data Low                                                   | Byte (Buffe  | er 0)   |         |           |           |        |  |  |

| PMDIN2H <sup>(2)</sup>     | Parallel Port                              | t In Data High                                                  | n Byte (Buff | er 3)   |         |           |           |        |  |  |

| PMDIN2L <sup>(2)</sup>     | Parallel Port                              | t In Data Low                                                   | Byte (Buffe  | er 2)   |         |           |           |        |  |  |

| PMMODEH <sup>(2)</sup>     | BUSY                                       | IRQM1                                                           | IRQM0        | INCM1   | INCM0   | MODE16    | MODE1     | MODE0  |  |  |

| PMMODEL <sup>(2)</sup>     | WAITB1                                     | WAITB0                                                          | WAITM3       | WAITM2  | WAITM1  | WAITM0    | WAITE1    | WAITE0 |  |  |

| PMEH <sup>(2)</sup>        | PTEN15                                     | PTEN14                                                          | PTEN13       | PTEN12  | PTEN11  | PTEN10    | PTEN9     | PTEN8  |  |  |

| PMEL <sup>(2)</sup>        | PTEN7                                      | PTEN6                                                           | PTEN5        | PTEN4   | PTEN3   | PTEN2     | PTEN1     | PTEN0  |  |  |

| PMSTATH <sup>(2)</sup>     | IBF                                        | IBOV                                                            | —            | —       | IB3F    | IB2F      | IB1F      | IB0F   |  |  |

| PMSTATL <sup>(2)</sup>     | OBE                                        | OBUF                                                            |              |         | OB3E    | OB2E      | OB1E      | OB0E   |  |  |

| PADCFG1                    | —                                          | —                                                               | —            | _       | —       | RTSECSEL1 | RTSECSEL0 | PMPTTL |  |  |

|                            |                                            |                                                                 |              |         |         |           |           |        |  |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during PMP operation.

**Note 1:** The PMADDRH/PMDOUT1H and PMADDRL/PMDOUT1L register pairs share the physical registers and addresses, but have different functions determined by the module's operating mode.

2: These bits and/or registers are only available in 44-pin devices.

#### REGISTER 19-2: CCPTMRS0: ECCP1/2/3 TIMER SELECT 0 REGISTER (BANKED F52h)

| R/W-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| C3TSEL1 | C3TSEL0 | C2TSEL2 | C2TSEL1 | C2TSEL0 | C1TSEL2 | C1TSEL1 | C1TSEL0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-6 | C3TSEL<1:0>: ECCP3 Timer Selection bits |

|---------|-----------------------------------------|

|         | 00 = ECCP3 is based off of TMR1/TMR2    |

|         | 01 = ECCP3 is based off of TMR3/TMR4    |

|         | 10 = ECCP3 is based off of TMR3/TMR6    |

|         | 11 = ECCP3 is based off of TMR3/TMR8    |

| bit 5-3 | C2TSEL<2:0>: ECCP2 Timer Selection bits |

|         | 000 = ECCP2 is based off of TMR1/TMR2   |

|         | 001 = ECCP2 is based off of TMR3/TMR4   |

|         | 010 = ECCP2 is based off of TMR3/TMR6   |

|         | 011 = ECCP2 is based off of TMR3/TMR8   |

|         | 1xx = Reserved; do not use              |

| bit 2-0 | C1TSEL<2:0>: ECCP1 Timer Selection bits |

|         | 000 = ECCP1 is based off of TMR1/TMR2   |

|         | 001 = ECCP1 is based off of TMR3/TMR4   |

|         | 010 = ECCP1 is based off of TMR3/TMR6   |

|         | 011 = ECCP1 is based off of TMR3/TMR8   |

|         | 1xx = Reserved; do not use              |

In addition to the expanded range of modes available through the CCPxCON and ECCPxAS registers, the ECCP modules have two additional registers associated with Enhanced PWM operation and auto-shutdown features. They are:

- ECCPxDEL Enhanced PWM Control

- PSTRxCON Pulse Steering Control

#### 20.4.4.1 DMACON1

The DMACON1 register is used to select the main operating mode of the SPI DMA module. The SSCON1 and SSCON0 bits are used to control the slave select pin.

When MSSP2 is used in SPI Master mode with the SPI DMA module, SSDMA can be controlled by the DMA module as an output pin. If MSSP2 will be used to communicate with an SPI slave device that needs the SSX pin to be toggled periodically, the SPI DMA hardware can automatically be used to deassert SSx between each byte, every two bytes or every four bytes.

Alternatively, user firmware can manually generate slave select signals with normal general purpose I/O pins, if required by the slave device(s).

When the TXINC bit is set, the TXADDR register will automatically increment after each transmitted byte. Automatic transmit address increment can be disabled by clearing the TXINC bit. If the automatic transmit address increment is disabled, each byte which is output on SDO2, will be the same (the contents of the SRAM pointed to by the TXADDR register) for the entire DMA transaction.

When the RXINC bit is set, the RXADDR register will automatically increment after each received byte. Automatic receive address increment can be disabled by clearing the RXINC bit. If RXINC is disabled in Full-Duplex or Half-Duplex Receive modes, all incoming data bytes on SDI2 will overwrite the same memory location pointed to by the RXADDR register. After the SPI DMA transaction has completed, the last received byte will reside in the memory location pointed to by the RXADDR register.

The SPI DMA module can be used for either half-duplex receive only communication, half-duplex transmit only communication or full-duplex simultaneous transmit and receive operations. All modes are available for both SPI master and SPI slave configurations. The DUPLEX0 and DUPLEX1 bits can be used to select the desired operating mode.

The behavior of the DLYINTEN bit varies greatly depending on the SPI operating mode. For example behavior for each of the modes, see Figure 20-3 through Figure 20-6.

**SPI Slave mode, DLYINTEN = 1:** In this mode, an SSP2IF interrupt will be generated during a transfer if the time between successful byte transmission events is longer than the value set by the DLYCYC<3:0> bits in the DMACON2 register. This interrupt allows slave firmware to know that the master device is taking an unusually large amount of time between byte transmissions. For example, this information may be useful for implementing application defined communication

protocols involving time-outs if the bus remains Idle for too long. When DLYINTEN = 1, the DLYCYC<3:0> interrupts occur normally according to the selected setting.

**SPI Slave mode, DLYINTEN =** 0: In this mode, the time-out based interrupt is disabled. No additional SSP2IF interrupt events will be generated by the SPI DMA module, other than those indicated by the INTLVL<3:0> bits in the DMACON2 register. In this mode, always set DLYCYC<3:0> = 0000.

**SPI Master mode, DLYINTEN = 0:** The DLYCYC<3:0> bits in the DMACON2 register determine the amount of additional inter-byte delay, which is added by the <u>SPI</u> DMA module during a transfer. The Master mode <u>SS2</u> output feature may be used.

**SPI Master mode, DLYINTEN = 1:** The amount of hardware overhead is slightly reduced in this mode, and the minimum inter-byte delay is 8 TcY for Fosc/4, 9 TcY for Fosc/16 and 15 TcY for Fosc/64. This mode can potentially be used to obtain slightly higher effective SPI bandwidth. In this mode, the SS2 control feature cannot be used, and should always be disabled (DMACON1<7:6> = 00). Additionally, the interrupt generating hardware (used in Slave mode) remains active. To avoid extraneous SSP2IF interrupt events, set the DMACON2 delay bits, DLYCYC<3:0> = 1111, and ensure that the SPI serial clock rate is no slower than Fosc/64.

In SPI Master modes, the DMAEN bit is used to enable the SPI DMA module and to initiate an SPI DMA transaction. After user firmware sets the DMAEN bit, the DMA hardware will begin transmitting and/or receiving data bytes according to the configuration used. In SPI Slave modes, setting the DMAEN bit will finish the initialization steps needed to prepare the SPI DMA module for communication (which still must be initiated by the master device).

To avoid possible data corruption, once the DMAEN bit is set, user firmware should not attempt to modify any of the MSSP2 or SPI DMA related registers, with the exception of the INTLVL bits in the DMACON2 register.

If user firmware wants to Halt an ongoing DMA transaction, the DMAEN bit can be manually cleared by the firmware. Clearing the DMAEN bit while a byte is currently being transmitted will not immediately Halt the byte in progress. Instead, any byte currently in progress will be completed before the MSSP2 and SPI DMA modules go back to their Idle conditions. If user firmware clears the DMAEN bit, the TXADDR, RXADDR and DMABC registers will no longer update, and the DMA module will no longer make any additional read or writes to SRAM; therefore, state information can be lost.

# REGISTER 20-5: SSPxSTAT: MSSPx STATUS REGISTER (I<sup>2</sup>C MODE) (1, ACCESS FC7h; 2, F73h)

| R/W-1      | R/W-1                                                                                                                                                | R-1                                | R-1                     | R-1              | R-1                  | R-1               | R-1      |  |  |  |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------------------|------------------|----------------------|-------------------|----------|--|--|--|--|

| SMP        | CKE                                                                                                                                                  | D/A                                | P <sup>(1)</sup>        | S <sup>(1)</sup> | R/W <sup>(2,3)</sup> | UA                | BF       |  |  |  |  |

| bit 7      |                                                                                                                                                      |                                    |                         |                  |                      |                   | bit 0    |  |  |  |  |

|            |                                                                                                                                                      |                                    |                         |                  |                      |                   |          |  |  |  |  |

| Legend:    |                                                                                                                                                      |                                    | 1.11                    |                  |                      | 1                 |          |  |  |  |  |

| R = Read   |                                                                                                                                                      | W = Writable                       |                         | -                | emented bit, rea     |                   |          |  |  |  |  |

| -n = Value | at POR                                                                                                                                               | '1' = Bit is se                    | ľ                       | '0' = Bit is cl  | eared                | x = Bit is unkr   | IOWN     |  |  |  |  |

| bit 7      | SMP: Slew                                                                                                                                            | Rate Control bit                   | t                       |                  |                      |                   |          |  |  |  |  |

|            | In Master or                                                                                                                                         | Slave mode:                        |                         |                  |                      |                   |          |  |  |  |  |

|            |                                                                                                                                                      |                                    |                         | •                | de (100 kHz an       | d 1 MHz)          |          |  |  |  |  |

| bit 6      | 0 = Slew ra                                                                                                                                          | ite control is en:                 | abled for High-s        | speed mode (4    | 400 KHZ)             |                   |          |  |  |  |  |

| DILO       |                                                                                                                                                      | Slave mode:                        |                         |                  |                      |                   |          |  |  |  |  |

|            |                                                                                                                                                      | SMBus specific                     | inputs                  |                  |                      |                   |          |  |  |  |  |

|            |                                                                                                                                                      | SMBus specific                     |                         |                  |                      |                   |          |  |  |  |  |

| bit 5      | D/A: Data/A                                                                                                                                          | ddress bit                         |                         |                  |                      |                   |          |  |  |  |  |

|            | In Master mode:                                                                                                                                      |                                    |                         |                  |                      |                   |          |  |  |  |  |

|            |                                                                                                                                                      | Reserved.<br>In Slave mode:        |                         |                  |                      |                   |          |  |  |  |  |

|            |                                                                                                                                                      | s that the last b                  | yte received or         | transmitted wa   | as data              |                   |          |  |  |  |  |

|            |                                                                                                                                                      | s that the last b                  | yte received or         | transmitted wa   | as address           |                   |          |  |  |  |  |

| bit 4      | P: Stop bit <sup>(1</sup>                                                                                                                            |                                    |                         |                  |                      |                   |          |  |  |  |  |

|            | <ul> <li>1 = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last</li> </ul>                                 |                                    |                         |                  |                      |                   |          |  |  |  |  |

| bit 3      | Start bit <sup>(1)</sup>                                                                                                                             |                                    |                         |                  |                      |                   |          |  |  |  |  |

|            | 1 = Indicates that a Start bit has been detected last                                                                                                |                                    |                         |                  |                      |                   |          |  |  |  |  |

|            |                                                                                                                                                      | was not detecte                    |                         |                  |                      |                   |          |  |  |  |  |

| bit 2      |                                                                                                                                                      | Write Informatio                   | on bit <sup>(2,3)</sup> |                  |                      |                   |          |  |  |  |  |

|            | In Slave mo                                                                                                                                          | <u>de:</u>                         |                         |                  |                      |                   |          |  |  |  |  |

|            | 1 = Read<br>0 = Write                                                                                                                                |                                    |                         |                  |                      |                   |          |  |  |  |  |

|            | In Master m                                                                                                                                          | ode:                               |                         |                  |                      |                   |          |  |  |  |  |

|            |                                                                                                                                                      | t is in progress                   |                         |                  |                      |                   |          |  |  |  |  |

|            |                                                                                                                                                      | t is not in progr                  |                         |                  |                      |                   |          |  |  |  |  |

| bit 1      | •                                                                                                                                                    | Address bit (10                    |                         |                  |                      | D an ainte a      |          |  |  |  |  |

|            | <ul> <li>1 = Indicates that the user needs to update the address in the SSPxADD register</li> <li>0 = Address does not need to be updated</li> </ul> |                                    |                         |                  |                      |                   |          |  |  |  |  |

| bit 0      |                                                                                                                                                      | ull Status bit                     |                         |                  |                      |                   |          |  |  |  |  |

|            | In Transmit mode:                                                                                                                                    |                                    |                         |                  |                      |                   |          |  |  |  |  |

|            | 1 = SSPxBL                                                                                                                                           |                                    |                         |                  |                      |                   |          |  |  |  |  |

|            | 0 = SSPxBl                                                                                                                                           |                                    |                         |                  |                      |                   |          |  |  |  |  |

|            | <u>In Receive r</u><br>1 = SSPxBL                                                                                                                    | <u>node:</u><br>JF is full (does ı | not include the         | ACK and Stop     | bits)                |                   |          |  |  |  |  |

|            |                                                                                                                                                      | JF is empty (do                    |                         |                  | ,                    |                   |          |  |  |  |  |

| Note 1:    | This bit is cleare                                                                                                                                   | ed on Reset and                    | when SSPEN              | is cleared.      |                      |                   |          |  |  |  |  |

| 2:         | This bit holds th                                                                                                                                    |                                    |                         |                  | ess match. This      | bit is only valid | from the |  |  |  |  |

|            | address match t                                                                                                                                      | to the next Start                  | bit, Stop bit or        | not ACK bit.     |                      |                   |          |  |  |  |  |

3: ORing this bit with SEN, RSEN, PEN, RCEN or ACKEN will indicate if the MSSPx is in Active mode.

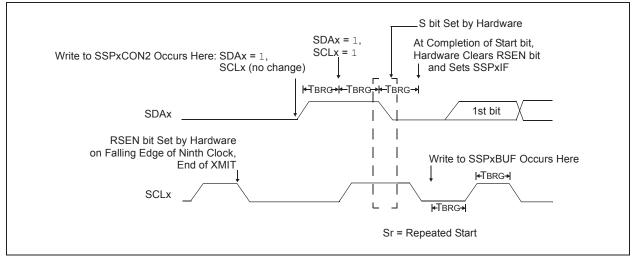

# 20.5.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPxCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the BRG is loaded with the contents of SSPxADD<5:0> and begins counting. The SDAx pin is released (brought high) for one BRG count (TBRG). When the BRG times out, and if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the BRG is reloaded with the contents of SSPxADD<6:0> and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. Following this, the RSEN bit (SSPxCON2<1>) will be automatically cleared and the BRG will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the Start bit (SSPxSTAT<3>) will be set. The SSPxIF bit will not be set until the BRG has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPxIF bit getting set, the user may write the SSPxBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional 8 bits of address (10-bit mode) or 8 bits of data (7-bit mode).

# 20.5.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur).

Note: Because queueing of events is not allowed, writing of the lower five bits of SSPxCON2 is disabled until the Repeated Start condition is complete.

# FIGURE 20-22: REPEATED START CONDITION WAVEFORM

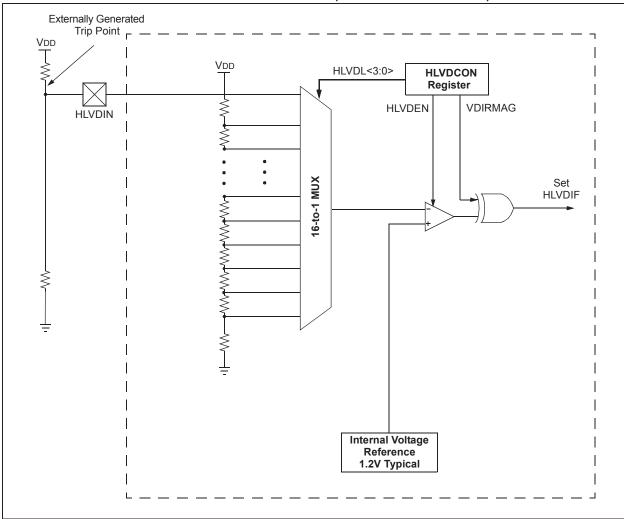

The module is enabled by setting the HLVDEN bit. Each time the module is enabled, the circuitry requires some time to stabilize. The IRVST bit is a read-only bit that indicates when the circuit is stable. The module can generate an interrupt only after the circuit is stable and IRVST is set.

The VDIRMAG bit determines the overall operation of the module. When VDIRMAG is cleared, the module monitors for drops in VDD below a predetermined set point. When the bit is set, the module monitors for rises in VDD above the set point.

# 25.1 Operation

When the HLVD module is enabled, a comparator uses an internally generated reference voltage as the set point. The set point is compared with the trip point, where each node in the resistor divider represents a trip point voltage. The "trip point" voltage is the voltage level at which the device detects a high or low-voltage event, depending on the configuration of the module.

When the supply voltage is equal to the trip point, the voltage tapped off of the resistor array is equal to the internal reference voltage generated by the voltage reference module. The comparator then generates an interrupt signal by setting the HLVDIF bit.

The trip point voltage is software programmable to any one of 16 values. The trip point is selected by programming the HLVDL<3:0> bits (HLVDCON<3:0>).

Additionally, the HLVD module allows the user to supply the trip voltage to the module from an external source. This mode is enabled when bits, HLVDL<3:0>, are set to '1111'. In this state, the comparator input is multiplexed from the external input pin, HLVDIN. This gives users flexibility because it allows them to configure the HLVD interrupt to occur at any voltage in the valid operating range.

FIGURE 25-1: HLVD MODULE BLOCK DIAGRAM (WITH EXTERNAL INPUT)

#### EXAMPLE 26-1: SETUP FOR CTMU CALIBRATION ROUTINES

```

#include <pl8cxxx.h>

void setup(void)

{ //CTMUCON - CTMU Control register

CTMUCONH = 0 \times 00;

//make sure CTMU is disabled

CTMUCONL = 0 \times 90;

//CTMU continues to run when emulator is stopped,CTMU continues

//to run in idle mode, Time Generation mode disabled, Edges are blocked

//No edge sequence order, Analog current source not grounded, trigger

//output disabled, Edge2 polarity = positive level, Edge2 source =

//source 0, Edge1 polarity = positive level, Edge1 source = source 0,

//CTMUICON - CTMU Current Control Register

CTMUICON = 0 \times 01;

//0.55uA, Nominal - No Adjustment

//Setup AD converter;

TRISA=0x04;

//set channel 2 as an input

// Configured AN2 as an analog channel

// ANCONO

ANCONO = 0xFB;

// ANCON1

ANCON1 = 0 \times 1F;

// ADCON1

// Result format 1= Right justified

ADCON1bits.ADFM=1;

// Normal A/D conversion operation

ADCON1bits.ADCAL=0;

// Acquisition time 7 = 20TAD 2 = 4TAD 1=2TAD

ADCON1bits.ACQT=1;

ADCON1bits.ADCS=2;

// Clock conversion bits 6= FOSC/64 2=FOSC/32

// ADCONO

// Vref+ = AVdd

ADCONObits.VCFG0 =0;

ADCONObits.VCFG1 =0;

// Vref- = AVss

ADCON0bits.CHS=2;

// Select ADC channel

ADCON0bits.ADON=1;

// Turn on ADC

}

```

# REGISTER 27-1: CONFIG1L: CONFIGURATION REGISTER 1 LOW (BYTE ADDRESS 300000h)

| R/WO-1 | R/WO-1 | R/WO-1 | R/WO-1   | R/WO-1  | R/WO-1  | R/WO-1  | R/WO-1 |

|--------|--------|--------|----------|---------|---------|---------|--------|

| DEBUG  | XINST  | STVREN | CFGPLLEN | PLLDIV2 | PLLDIV1 | PLLDIV0 | WDTEN  |

| bit 7  |        |        |          |         |         |         | bit 0  |

| Legend:      |                                                                                                   |                                                                                                                                                                                                                                                                                                                                      |                                                                                    |                                                         |  |  |

|--------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|

| R = Readal   | ole bit                                                                                           | WO = Write-Once bit                                                                                                                                                                                                                                                                                                                  | U = Unimplemented bit,                                                             | read as '0'                                             |  |  |

| -n = Value a | at POR                                                                                            | '1' = Bit is set                                                                                                                                                                                                                                                                                                                     | '0' = Bit is cleared                                                               | x = Bit is unknown                                      |  |  |

|              |                                                                                                   |                                                                                                                                                                                                                                                                                                                                      |                                                                                    |                                                         |  |  |

| bit 7        | DEBUG: B                                                                                          | ackground Debugger Enable                                                                                                                                                                                                                                                                                                            | e bit                                                                              |                                                         |  |  |

|              |                                                                                                   | round debugger is disabled;<br>round debugger is enabled; F                                                                                                                                                                                                                                                                          |                                                                                    | ed as general purpose I/O pins<br>I to In-Circuit Debug |  |  |

| bit 6        | XINST: Ext                                                                                        | ended Instruction Set Enable                                                                                                                                                                                                                                                                                                         | e bit                                                                              |                                                         |  |  |

|              |                                                                                                   | ction set extension and Index ction set extension and Index                                                                                                                                                                                                                                                                          |                                                                                    |                                                         |  |  |

| bit 5        | STVREN: S                                                                                         | Stack Overflow/Underflow Re                                                                                                                                                                                                                                                                                                          | eset Enable bit                                                                    |                                                         |  |  |

|              |                                                                                                   | on stack overflow/underflow on stack overflow/underflow                                                                                                                                                                                                                                                                              |                                                                                    |                                                         |  |  |

| bit 4        | 1 = PLL is                                                                                        | <ul> <li>PLL Enable bit</li> <li>disabled until firmware sets t</li> <li>enabled at start-up</li> </ul>                                                                                                                                                                                                                              | the PLLEN bit at run time (C                                                       | DSCTUNE<6>)                                             |  |  |

| bit 3-1      | PLLDIV<2                                                                                          | :0>: Oscillator Selection bits                                                                                                                                                                                                                                                                                                       |                                                                                    |                                                         |  |  |

|              | on 4x<br>111 = No o<br>110 = Osc<br>101 = Osc<br>011 = Osc<br>010 = Osc<br>010 = Osc<br>001 = Osc | st be configured to provide a<br>PLL operation.<br>divide – oscillator is used dire<br>illator divided by 2 (8 MHz ing<br>illator divided by 3 (12 MHz ir<br>illator divided by 4 (16 MHz ir<br>illator divided by 5 (20 MHz ir<br>illator divided by 6 (24 MHz ir<br>illator divided by 10 (40 MHz<br>illator divided by 12 (48 MHz | ctly (4 MHz input)<br>put)<br>nput)<br>nput)<br>nput)<br>nput)<br>input)<br>input) | Hz PLL. These bits have no effect                       |  |  |

| bit 0        | 1 = WDT is                                                                                        | Vatchdog Timer Enable bit<br>s enabled<br>s disabled (control is placed c                                                                                                                                                                                                                                                            | on the SWDTEN bit)                                                                 |                                                         |  |  |

# PIC18F47J13 FAMILY

| MOVFF                                                                        | Move f to f                               |                                                                  |                                          | MOVLB             | Move Liter                           | al to Low Nil                                                                                                       | bble in BSR                 |  |

|------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------|------------------------------------------|-------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------|--|

| Syntax:                                                                      | MOVFF f <sub>s</sub>                      | ,f <sub>d</sub>                                                  |                                          | Syntax:           | MOVLW k                              | ,                                                                                                                   |                             |  |

| Operands:                                                                    |                                           | $0 \le f_s \le 4095$                                             |                                          | Operands:         | $Operands: \qquad 0 \leq k \leq 255$ |                                                                                                                     |                             |  |

|                                                                              | $0 \le f_d \le 409$                       | 95                                                               |                                          | Operation:        | Operation: $k \rightarrow BSR$       |                                                                                                                     |                             |  |

| Operation:                                                                   | $(f_s) \to f_d$                           |                                                                  |                                          | Status Affected:  | None                                 |                                                                                                                     |                             |  |

| Status Affected:                                                             | None                                      |                                                                  |                                          | Encoding:         | 0000                                 | 0001 kk                                                                                                             | kk kkkk                     |  |

| Encoding:<br>1st word (source)<br>2nd word (destin.)                         | 1100<br>1111                              | ffff ff:<br>ffff ff:                                             | 5                                        | Description:      | Bank Selec                           | The 8-bit literal 'k' is loaded into the<br>Bank Select Register (BSR). The value<br>of BSR<7:4> always remains '0' |                             |  |

| Description:                                                                 |                                           | ts of source re                                                  |                                          |                   |                                      | of the value o                                                                                                      |                             |  |

|                                                                              |                                           | estination regi                                                  | ster 'f <sub>d</sub> '.<br>i be anywhere | Words:            | 1                                    |                                                                                                                     |                             |  |

|                                                                              |                                           | -byte data spa                                                   |                                          | Cycles:           | 1                                    |                                                                                                                     |                             |  |

|                                                                              |                                           | location of des                                                  |                                          | Q Cycle Activity: |                                      |                                                                                                                     |                             |  |

|                                                                              | can also be<br>FFFh.                      | anywhere fro                                                     | m uuun to                                | Q1                | Q2                                   | Q3                                                                                                                  | Q4                          |  |

|                                                                              | Either sour                               | ce or destinati                                                  | on can be W                              | Decode            | Read<br>literal 'k'                  | Process<br>Data                                                                                                     | Write literal<br>'k' to BSR |  |

|                                                                              |                                           | ecial situation                                                  |                                          |                   |                                      | Data                                                                                                                | K to Bolt                   |  |

|                                                                              | peripheral r<br>buffer or an<br>The MOVFF | egister (such a<br>I/O port).<br>instruction ca<br>J, TOSH or TC |                                          | After Instruc     | egister = 02                         |                                                                                                                     |                             |  |

| Words:                                                                       | 2                                         |                                                                  |                                          |                   |                                      |                                                                                                                     |                             |  |

| Cycles:                                                                      | 2                                         |                                                                  |                                          |                   |                                      |                                                                                                                     |                             |  |

| Q Cycle Activity:                                                            |                                           |                                                                  |                                          |                   |                                      |                                                                                                                     |                             |  |

| Q1                                                                           | Q2                                        | Q3                                                               | Q4                                       |                   |                                      |                                                                                                                     |                             |  |

| Decode                                                                       | Read<br>register 'f'<br>(src)             | Process<br>Data                                                  | No<br>operation                          |                   |                                      |                                                                                                                     |                             |  |

| Decode                                                                       | No<br>operation<br>No dummy<br>read       | No<br>operation                                                  | Write<br>register 'f'<br>(dest)          |                   |                                      |                                                                                                                     |                             |  |

| Example:<br>Before Instru<br>REG1<br>REG2<br>After Instructi<br>REG1<br>REG2 | ction<br>= 33<br>= 11                     | h                                                                |                                          |                   |                                      |                                                                                                                     |                             |  |

#### TABLE 30-5: ULPWU SPECIFICATIONS

| DC CH/       | ARACT | ERISTICS                           | Standard Operating Conditions (unless otherwise stated Operating temperature -40°C $\leq$ TA $\leq$ +85°C for industrial |      |     |       |                                                                                                                                                                             |

|--------------|-------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym   | Characteristic                     | Min                                                                                                                      | Тур† | Max | Units | Conditions                                                                                                                                                                  |