Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 10x10b/12b                                                             |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f27j13-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.0 LOW-POWER MODES

The PIC18F47J13 Family devices can manage power consumption through clocking to the CPU and the peripherals. In general, reducing the clock frequency and number of circuits being clocked reduces power consumption.

For managing power in an application, the primary modes of operation are:

- Run Mode

- Idle Mode

- Sleep Mode

- Deep Sleep Mode

Additionally, there is an Ultra Low-Power Wake-up (ULPWU) mode for generating an interrupt-on-change on RA0.

These modes define which portions of the device are clocked and at what speed.

- The Run and Idle modes can use any of the three available clock sources (primary, secondary or internal oscillator blocks).

- The Sleep mode does not use a clock source.

The ULPWU mode on RA0 allows a slow falling voltage to generate an interrupt-on-change on RA0 without excess current consumption. See **Section 4.7 "Ultra Low-Power Wake-up**".

The power-managed modes include several power-saving features offered on previous PIC<sup>®</sup> devices, such as clock switching, ULPWU and Sleep mode. In addition, the PIC18F47J13 Family devices have added a new power-managed Deep Sleep mode.

# 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires these decisions:

- Will the CPU be clocked?

- · If so, which clock source will be used?

The IDLEN bit (OSCCON<7>) controls CPU clocking and the SCS<1:0> bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

# 4.1.1 CLOCK SOURCES

The SCS<1:0> bits allow the selection of one of three clock sources for power-managed modes. They are:

- Primary clock source Defined by the FOSC<2:0> Configuration bits

- Timer1 clock Provided by the secondary oscillator

- Postscaled internal clock Derived from the internal oscillator block

#### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one clock source to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source.

Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch also may be subject to clock transition delays. These delays are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, the IDLEN bit or the DSEN bit prior to issuing a SLEEP instruction.

If the IDLEN and DSEN bits are already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

# 6.1.4.2 Return Stack Pointer (STKPTR)

The STKPTR register (Register 6-1) contains the Stack Pointer value, the STKFUL (Stack Full) and the STKUNF (Stack Underflow) status bits. The value of the Stack Pointer can be 0 through 31. The Stack Pointer increments before values are pushed onto the stack and decrements after values are popped off of the stack. On Reset, the Stack Pointer value will be zero. The user may read and write the Stack Pointer value. This feature can be used by a Real-Time Operating System (RTOS) for return stack maintenance.

After the PC is pushed onto the stack 31 times (without popping any values off the stack), the STKFUL bit is set. The STKFUL bit is cleared by software or by a Power-on Reset (POR).

The action that takes place when the stack becomes full depends on the state of the Stack Overflow Reset Enable (STVREN) Configuration bit.

Refer to **Section 27.1 "Configuration Bits**" for the device Configuration bits' description.

If STVREN is set (default), the  $31^{st}$  push will push the (PC + 2) value onto the stack, set the STKFUL bit and reset the device. The STKFUL bit will remain set and the Stack Pointer will be set to zero.

If STVREN is cleared, the STKFUL bit will be set on the 31<sup>st</sup> push and the Stack Pointer will increment to 31. Any additional pushes will not overwrite the 31<sup>st</sup> push and the STKPTR will remain at 31.

When the stack has been popped enough times to unload the stack, the next pop will return zero to the PC and set the STKUNF bit, while the Stack Pointer remains at zero. The STKUNF bit will remain set until cleared by software or until a POR occurs.

| Note: | Returning a value of zero to the PC on an |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|

|       | underflow has the effect of vectoring the |  |  |  |  |  |

|       | program to the Reset vector, where the    |  |  |  |  |  |

|       | stack conditions can be verified and      |  |  |  |  |  |

|       | appropriate actions can be taken. This is |  |  |  |  |  |

|       | not the same as a Reset, as the contents  |  |  |  |  |  |

|       | of the SFRs are not affected.             |  |  |  |  |  |

#### 6.1.4.3 PUSH and POP Instructions

Since the Top-of-Stack (TOS) is readable and writable, the ability to push values onto the stack and pull values off of the stack, without disturbing normal program execution, is necessary. The PIC18 instruction set includes two instructions, PUSH and POP, that permit the TOS to be manipulated under software control. TOSU, TOSH and TOSL can be modified to place data or a return address on the stack.

The PUSH instruction places the current PC value onto the stack. This increments the Stack Pointer and loads the current PC value onto the stack.

The POP instruction discards the current TOS by decrementing the Stack Pointer. The previous value pushed onto the stack then becomes the TOS value.

x = Bit is unknown

# REGISTER 6-1: STKPTR: STACK POINTER REGISTER (ACCESS FFCh)

| R/C-0                             | R/C-0                 | U-0 | R/W-0 | R/W-0        | R/W-0            | R/W-0         | R/W-0 |

|-----------------------------------|-----------------------|-----|-------|--------------|------------------|---------------|-------|

| STKFUL <sup>(1)</sup>             | STKUNF <sup>(1)</sup> | —   | SP4   | SP3          | SP2              | SP1           | SP0   |

| bit 7                             |                       |     |       |              |                  |               | bit 0 |

| -                                 |                       |     |       |              |                  |               |       |

| Legend: C = Clearable bit         |                       |     | bit   |              |                  |               |       |

| R = Readable bit W = Writable bit |                       |     | bit   | U = Unimplem | nented bit, read | <b>as</b> '0' |       |

'0' = Bit is cleared

| bit 7   | STKFUL: Stack Full Flag bit <sup>(1)</sup>      |

|---------|-------------------------------------------------|

|         | 1 = Stack became full or overflowed             |

|         | 0 = Stack has not become full or overflowed     |

| bit 6   | STKUNF: Stack Underflow Flag bit <sup>(1)</sup> |

|         | 1 = Stack underflow occurred                    |

|         | 0 = Stack underflow did not occur               |

| bit 5   | Unimplemented: Read as '0'                      |

| bit 4-0 | SP<4:0>: Stack Pointer Location bits            |

'1' = Bit is set

**Note 1:** Bits 7 and 6 are cleared by user software or by a POR.

-n = Value at POR

| Addr. | File Name             | Bit 7       | Bit 6                                   | Bit 5                                               | Bit 4                                                                                                             | Bit 3               | Bit 2              | Bit 1        | Bit 0     | Value on<br>POR, BOR |

|-------|-----------------------|-------------|-----------------------------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------|--------------------|--------------|-----------|----------------------|

| F07h  | CCPR8L                | Capture/Com | Capture/Compare/PWM Register 8 Low Byte |                                                     |                                                                                                                   |                     |                    |              | XXXX XXXX |                      |

| F06h  | CCP8CON               | _           | _                                       | DC8B1                                               | DC8B0                                                                                                             | CCP8M3              | CCP8M2             | CCP8M1       | CCP8M0    | 00 0000              |

| F05h  | CCPR9H                | Capture/Com | pare/PWM Re                             | gister 9 High I                                     | Byte                                                                                                              |                     |                    |              |           | XXXX XXXX            |

| F04h  | CCPR9L                | Capture/Com | pare/PWM Re                             | gister 9 Low E                                      | Byte                                                                                                              |                     | _                  |              |           | XXXX XXXX            |

| F03h  | CCP9CON               | —           | —                                       | DC9B1                                               | DC9B0                                                                                                             | CCP9M3              | CCP9M2             | CCP9M1       | CCP9M0    | 00 0000              |

| F02h  | CCPR10H               | Capture/Com | pare/PWM Re                             | gister 10 High                                      | Byte                                                                                                              |                     | <u>.</u>           |              |           | XXXX XXXX            |

| F01h  | CCPR10L               | Capture/Com | pare/PWM Re                             | gister 10 Low                                       | Byte                                                                                                              |                     |                    |              |           | XXXX XXXX            |

| F00h  | CCP10CON              | —           | _                                       | DC10B1                                              | DC10B0                                                                                                            | CCP10M3             | CCP10M2            | CCP10M1      | CCP10M0   | 00 0000              |

| EFFh  | RPINR24               | —           | _                                       | _                                                   | PWM Fault Ir                                                                                                      | nput (FLT0) to      | Input Pin Mapp     | bing bits    |           | 1 1111               |

| EFEh  | RPINR23               | _           | _                                       | _                                                   | SPI2 Slave S                                                                                                      | elect Input (S      | S2) to Input Pin   | Mapping bits |           | 1 1111               |

| EFDh  | RPINR22               | —           | _                                       | _                                                   | SPI2 Clock Ir                                                                                                     | nput (SCK2) to      | o Input Pin Map    | ping bits    |           | 1 1111               |

| EFCh  | RPINR21               | —           | _                                       | _                                                   | SPI2 Data In                                                                                                      | put (SDI2) to I     | nput Pin Mappi     | ng bits      |           | 1 1111               |

| EFBh  | _                     | _           | _                                       | _                                                   | _                                                                                                                 | _                   | <u> </u>           | _            | _         | (3)                  |

| EFAh  | _                     | _           | _                                       | _                                                   | _                                                                                                                 | _                   | _                  | _            | _         | (3)                  |

| EF9h  | _                     | _           | _                                       | _                                                   | _                                                                                                                 | _                   | _                  | _            | _         | (3)                  |

| EF8h  | RPINR17               | _           | _                                       | _                                                   | EUSART2 C                                                                                                         | lock Input (CK      | 2) to Input Pin I  | Mapping bits |           | 1 1111               |

| EF7h  | RPINR16               | _           | _                                       | _                                                   | EUSART2 R                                                                                                         | X2/DT2 to Inp       | ut Pin Mapping     | bits         |           | 1 1111               |

| EF6h  | _                     | _           | _                                       | _                                                   |                                                                                                                   | _                   | _                  | _            | _         | (3)                  |

| EF5h  | _                     | _           | _                                       | _                                                   | _                                                                                                                 | _                   | _                  | _            | _         | (3)                  |

| EF4h  | RPINR14               | _           | _                                       | _                                                   | Timer5 Gate                                                                                                       | I<br>Input (T5G) to | I<br>Input Pin Map | ning bits    |           | 1 1111               |

| EF3h  | RPINR13               | _           | _                                       | — Timer3 Gate Input (T3G) to Input Pin Mapping bits |                                                                                                                   |                     |                    |              | 1 1111    |                      |

| EF2h  | RPINR12               |             | _                                       | _                                                   | Timer1 Gate Input (T1G) to Input Pin Mapping bits                                                                 |                     |                    |              |           | 1 1111               |

| EF1h  |                       |             |                                         |                                                     |                                                                                                                   |                     |                    |              | _         | (3)                  |

| EF0h  |                       |             |                                         |                                                     |                                                                                                                   |                     |                    |              |           | (3)                  |

| EEFh  |                       |             |                                         |                                                     |                                                                                                                   |                     |                    |              |           | (3)                  |

| EEEh  |                       |             |                                         |                                                     |                                                                                                                   |                     |                    |              |           | (3)                  |

| EEDh  |                       | <u> </u>    |                                         |                                                     |                                                                                                                   |                     |                    |              |           | (3)                  |

| EECh  |                       |             |                                         |                                                     |                                                                                                                   |                     |                    |              |           | (3)                  |

| EEBh  |                       |             |                                         |                                                     |                                                                                                                   |                     |                    |              |           |                      |

| EEAh  | RPINR9                |             |                                         |                                                     | ECCP3 Input                                                                                                       |                     | ) to Input Pin M   | apping bits  | _         | (3)                  |

| EE9h  | RPINR9                |             |                                         |                                                     | ECCP3 Input Capture (IC3) to Input Pin Mapping bits                                                               |                     |                    |              |           |                      |

|       | RPINR0                |             |                                         |                                                     | ECCP2 Input Capture (IC2) to Input Pin Mapping bits                                                               |                     |                    |              | 1 1111    |                      |

| EE8h  |                       |             |                                         |                                                     | ECCP1 Input Capture (IC1) to Input Pin Mapping bits                                                               |                     |                    |              | 1 1111    |                      |

| EE7h  | RPINR15               |             |                                         |                                                     | Timer5 External Clock Input (T5CKI) to Input Pin Mapping bits                                                     |                     |                    |              | 1 1111    |                      |

| EE6h  | RPINR6                |             |                                         |                                                     | Timer3 External Clock Input (T3CKI) to Input Pin Mapping bits                                                     |                     |                    |              | 1 1111    |                      |

| EE5h  |                       | _           | _                                       | _                                                   |                                                                                                                   |                     |                    |              | a hita    | (3)                  |

| EE4h  | RPINR4                | _           | _                                       | _                                                   | Timer0 External Clock Input (T0CKI) to Input Pin Mapping bits External Interrupt (INT3) to Input Pin Mapping bits |                     |                    |              |           | 1 1111               |

| EE3h  | RPINR3                | _           | _                                       | _                                                   |                                                                                                                   | 1 ( )               |                    | 0            |           | 1 1111               |

| EE2h  | RPINR2                | _           | —                                       | _                                                   | External Interrupt (INT2) to Input Pin Mapping bits External Interrupt (INT1) to Input Pin Mapping bits           |                     |                    |              | 1 1111    |                      |

| EE1h  | RPINR1                | _           | —                                       | _                                                   |                                                                                                                   | παρτ (IN I 1) to    | input Pin Mapp     |              |           | 1 1111               |

| EE0h  | _                     | _           | —                                       | _                                                   | _                                                                                                                 | —                   | _                  | _            | _         | (3)                  |

| EDFh  | -                     | _           | _                                       |                                                     |                                                                                                                   | —                   | -                  |              | -         | (3)                  |

| EDEh  | _                     | _           | _                                       |                                                     |                                                                                                                   | _                   |                    |              |           | (3)                  |

| EDDh  | _                     | _           | _                                       | _                                                   |                                                                                                                   | _                   |                    |              | -         | (3)                  |

| EDCh  | _                     | _           | —                                       |                                                     | -                                                                                                                 | —                   | _                  |              |           | (3)                  |

| EDBh  |                       | —           | —                                       |                                                     | —                                                                                                                 | —                   |                    |              |           | (3)                  |

| EDAh  |                       | _           | —                                       | —                                                   | _                                                                                                                 | —                   | -                  | —            | -         | (3)                  |

| ED9h  |                       | _           | —                                       | —                                                   | —                                                                                                                 | —                   | -                  | —            | -         | (3)                  |

| ED8h  | RPOR24 <sup>(2)</sup> | —           | —                                       | -                                                   | Remappable                                                                                                        | Pin RP24 Ou         | tput Signal Sele   | ect bits     |           | 0 0000               |

| ED7h  | RPOR23 <sup>(2)</sup> | —           | —                                       | —                                                   | Remappable                                                                                                        | Pin RP23 Ou         | tput Signal Sele   | ect bits     |           | 0 0000               |

Note 1: Applicable for 28-pin devices (PIC18F26J13, PIC18F27J13, PIC18LF26J13 and PIC18LF27J13).

2: Applicable for 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

3: Value on POR, BOR.

Example 8-3 provides the instruction sequence for a 16 x 16 unsigned multiplication. Equation 8-1 provides the algorithm that is used. The 32-bit result is stored in four registers (RES3:RES0).

#### EQUATION 8-1: 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

| H:ARG2L |

|---------|

| +       |

| -       |

| -       |

|         |

|         |

#### EXAMPLE 8-3: 16 x 16 UNSIGNED MULTIPLY ROUTINE

| MOVF   | ARG1L, W    |                   |

|--------|-------------|-------------------|

| MULWF  | ARG2L       | ; ARG1L * ARG2L-> |

|        |             | ; PRODH:PRODL     |

| MOVFF  | PRODH, RES1 | ;                 |

| MOVFF  | PRODL, RESO | ;                 |

|        |             |                   |

| MOVF   | ARG1H, W    |                   |

| MULWF  | ARG2H       | ; ARG1H * ARG2H-> |

|        |             | ; PRODH:PRODL     |

| MOVFF  | PRODH, RES3 | ;                 |

| MOVFF  | PRODL, RES2 | ;                 |

|        |             |                   |

| MOVF   | ARG1L, W    |                   |

| MULWF  | ARG2H       | ; ARG1L * ARG2H-> |

|        |             | ; PRODH:PRODL     |

| MOVF   | PRODL, W    | ;                 |

| ADDWF  | RES1, F     | ; Add cross       |

|        | PRODH, W    | ; products        |

| ADDWFC | RES2, F     | ;                 |

| CLRF   |             | ;                 |

| ADDWFC | RES3, F     | ;                 |

|        |             |                   |

|        | ARG1H, W    | ;                 |

| MULWF  | ARG2L       | ; ARG1H * ARG2L-> |

|        |             | ; PRODH:PRODL     |

| MOVF   | PRODL, W    | ;                 |

| ADDWF  | RES1, F     | ; Add cross       |

|        | PRODH, W    | ; products        |

|        | RES2, F     | ;                 |

| CLRF   |             | ;                 |

| ADDWFC | RES3, F     | ;                 |

|        |             |                   |

Example 8-4 provides the sequence to do a 16 x 16 signed multiply. Equation 8-2 provides the algorithm used. The 32-bit result is stored in four registers (RES3:RES0). To account for the sign bits of the arguments, the MSb for each argument pair is tested and the appropriate subtractions are done.

#### EQUATION 8-2: 16 x 16 SIGNED MULTIPLICATION ALGORITHM

| $RES3:RES0 = ARG1H:ARG1L \cdot ARG2H:ARG2L$ $= (ARG1H \cdot ARG2H \cdot 2^{16}) + (ARG1H \cdot ARG2L \cdot 2^{8}) + (ARG1L \cdot ARG2L \cdot 2^{8}) + (ARG1L \cdot ARG2L \cdot 2^{8}) + (ARG1L \cdot ARG2L) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L \cdot 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L \cdot 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L \cdot 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H:ARG1L - 2^{16}) + (-1 \cdot ARG2H < 7 > ARG1H + ARG1$ |           |                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------|

| (-1 · ARG1H> · ARG2H:ARG2L · 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RES3:RES0 | $(ARG1H \cdot ARG2H \cdot 2^{16}) + (ARG1H \cdot ARG2L \cdot 2^{8}) + (ARG1L \cdot ARG2H \cdot 2^{8}) + $ |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |                                                                                                           |

# EXAMPLE 8-4:

16 x 16 SIGNED MULTIPLY ROUTINE

| MOVF      | ARG1L, W    |                    |

|-----------|-------------|--------------------|

| MULWF     | ARG2L       | ; ARG1L * ARG2L -> |

|           |             | ; PRODH:PRODL      |

| MOVFF     | PRODH, RES1 | ;                  |

| MOVFF     | PRODL, RESO | ;                  |

|           |             |                    |

| MOVF      | ARG1H, W    |                    |

|           | ARG2H       | ; ARG1H * ARG2H -> |

|           |             | ; PRODH:PRODL      |

| MOVFF     | PRODH, RES3 | ;                  |

| MOVFF     | PRODL, RES2 | ;                  |

|           |             |                    |

| MOVF      | ARG1L, W    |                    |

| MULWF     | ARG2H       | ; ARG1L * ARG2H -> |

|           |             | ; PRODH:PRODL      |

| MOVF      | PRODL, W    | ;                  |

|           | RES1, F     | ; Add cross        |

| MOVF      | PRODH, W    | ; products         |

|           | RES2, F     | ;                  |

|           | WREG        | ;                  |

|           | RES3, F     | ;                  |

|           |             | ,                  |

| MOVF      | ARG1H, W    | ;                  |

|           | ARG2L       | ; ARG1H * ARG2L -> |

|           |             | ; PRODH:PRODL      |

| MOVF      | PRODL, W    | ;                  |

|           | RES1, F     | ; Add cross        |

| MOVF      | PRODH, W    | ; products         |

|           | RES2, F     | ;                  |

|           | WREG        | ;                  |

|           | RES3, F     | ;                  |

|           |             |                    |

| BTFSS     | ARG2H, 7    | ; ARG2H:ARG2L neg? |

| BRA       | SIGN ARG1   | ; no, check ARG1   |

| MOVF      | ARG1L, W    | ;                  |

|           | RES2        | ;                  |

|           | ARG1H, W    | ;                  |

| SUBWFB    |             | ,                  |

|           |             |                    |

| SIGN ARG1 |             |                    |

| _         | ARG1H, 7    | ; ARG1H:ARG1L neg? |

| BRA       | CONT CODE   | ; no, done         |

| MOVF      | ARG2L, W    | ;                  |

|           | RES2        | ;                  |

|           | ARG2H, W    | ;                  |

| SUBWFB    |             | ·                  |

|           |             |                    |

| CONT CODE |             |                    |

| :         |             |                    |

| -         |             |                    |

# REGISTER 9-5: PIR2: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 2 (ACCESS FA1h)

| R/W-0  | R/W-0 | R/W-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-------|-------|-----|--------|--------|--------|--------|

| OSCFIF | CM2IF | CM1IF | —   | BCL1IF | HLVDIF | TMR3IF | CCP2IF |

| bit 7  |       |       |     |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7 | OSCFIF: Oscillator Fail Interrupt Flag bit                                                                                                                    |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = The device oscillator failed, clock input has changed to INTOSC (must be cleared in software)</li> <li>0 = The device clock operating</li> </ul> |

| bit 6 | CM2IF: Comparator 2 Interrupt Flag bit                                                                                                                        |

|       | <ul> <li>1 = The comparator input has changed (must be cleared in software)</li> <li>0 = The comparator input has not changed</li> </ul>                      |

| bit 5 | CM1IF: Comparator 1 Interrupt Flag bit                                                                                                                        |

|       | <ul> <li>1 = The comparator input has changed (must be cleared in software)</li> <li>0 = The comparator input has not changed</li> </ul>                      |

| bit 4 | Unimplemented: Read as '0'                                                                                                                                    |

| bit 3 | BCL1IF: Bus Collision Interrupt Flag bit (MSSP1 module)                                                                                                       |

|       | <ul><li>1 = A bus collision occurred (must be cleared in software)</li><li>0 = No bus collision occurred</li></ul>                                            |

| bit 2 | HLVDIF: High/Low-Voltage Detect (HLVD) Interrupt Flag bit                                                                                                     |

|       | <ul> <li>1 = A High/Low-Voltage condition occurred (must be cleared in software)</li> <li>0 = An HLVD event has not occurred</li> </ul>                       |

| bit 1 | TMR3IF: TMR3 Overflow Interrupt Flag bit                                                                                                                      |

|       | <ul><li>1 = The TMR3 register overflowed (must be cleared in software)</li><li>0 = The TMR3 register did not overflow</li></ul>                               |

| bit 0 | CCP2IF: ECCP2 Interrupt Flag bit                                                                                                                              |

|       | <u>Capture mode:</u><br>1 = A TMR1/TMR3 register capture occurred (must be cleared in software)<br>0 = No TMR1/TMR3 register capture occurred                 |

|       | <u>Compare mode:</u><br>1 = A TMR1/TMR3 register compare match occurred (must be cleared in software)<br>0 = No TMR1/TMR3 register compare match occurred     |

|       | <u>PWM mode:</u><br>Unused in this mode.                                                                                                                      |

| REGISTER      | 9-8: PIR5:  | PERIPHERA        | L INTERRUP      | T REQUEST         | (FLAG) REGI      | STER 5 (ACC     | CESS <mark>F98</mark> h) |

|---------------|-------------|------------------|-----------------|-------------------|------------------|-----------------|--------------------------|

| U-0           | U-0         | R-0              | R/W-0           | R/W-0             | R/W-0            | R/W-0           | R/W-0                    |

|               | —           | CM3IF            | TMR8IF          | TMR6IF            | TMR5IF           | TMR5GIF         | TMR1GIF                  |

| bit 7         |             |                  |                 |                   |                  |                 | bit 0                    |

| ·             |             |                  |                 |                   |                  |                 |                          |

| Legend:       |             |                  |                 |                   |                  |                 |                          |

| R = Readable  | e bit       | W = Writable     | bit             | U = Unimplem      | nented bit, read | l as '0'        |                          |

| -n = Value at | POR         | '1' = Bit is set |                 | '0' = Bit is clea | ared             | x = Bit is unkr | iown                     |

|               |             |                  |                 |                   |                  |                 |                          |

| bit 7-6       | Unimplemen  | ted: Read as '   | )'              |                   |                  |                 |                          |

| bit 5         | CM3IF: Comp | parator Interrup | t Flag bit      |                   |                  |                 |                          |

|               |             | •                | •               | t be cleared in   | software)        |                 |                          |

|               | 0 = Compara | tor 3 input has  | not changed     |                   |                  |                 |                          |

| bit 4         | TMR8IF: TMF | R8 to PR8 Mate   | h Interrupt Fla | g bit             |                  |                 |                          |

|               |             |                  | •               | e cleared in sof  | tware)           |                 |                          |

|               | 0 = No IMR8 | 3 to PR8 match   | occurred        |                   |                  |                 |                          |

| bit 3         | TMR6IF: TMF | R6 to PR6 Mate   | h Interrupt Fla | g bit             |                  |                 |                          |

|               |             |                  |                 | e cleared in sof  | tware)           |                 |                          |

|               | 0 = No TMR6 | 6 to PR6 match   | occurred        |                   |                  |                 |                          |

| bit 2         | TMR5IF: TMF | R3 Overflow Int  | errupt Flag bit |                   |                  |                 |                          |

1 = TMR3 register overflowed (must be cleared in software)

1 = TMR gate interrupt occurred (must be cleared in software)

1 = TMR gate interrupt occurred (must be cleared in software)

0 = TMR3 register did not overflow

0 = No TMR gate interrupt occurred

0 = No TMR gate interrupt occurred

TMR5GIF: TMR5 Gate Interrupt Flag bits

TMR1GIF: TMR5 Gate Interrupt Flag bits

bit 1

bit 0

# 10.7 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices similar to the PIC18F47J13 Family. In an application that needs to use more than one peripheral, multiplexed on a single pin, inconvenient work arounds in application code or a complete redesign may be the only option.

The Peripheral Pin Select (PPS) feature provides an alternative to these choices by enabling the user's peripheral set selection and its placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The PPS feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/ or output of any one of the many digital peripherals to any one of these I/O pins. PPS is performed in software, and generally, does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 10.7.1 AVAILABLE PINS

The PPS feature is used with a range of up to 22 pins. The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number. See Table 1-3 and Table 1-4 for pinout options in each package offering.

### 10.7.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and external interrupt inputs. Also included are the outputs of the comparator module, since these are discrete digital signals.

The PPS module is not applied to I<sup>2</sup>C, change notification inputs, RTCC alarm outputs or peripherals with analog inputs. Additionally, the MSSP1 and EUSART1 modules are not routed through the PPS module.

A key difference between pin select and non-pin select peripherals is that pin select peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-pin select peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

#### 10.7.2.1 Peripheral Pin Select Function Priority

When a pin selectable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Pin select peripherals never take priority over any analog functions associated with the pin.

#### 10.7.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of Special Function Registers (SFRs): one to map peripheral inputs and the other to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or an output is being mapped.

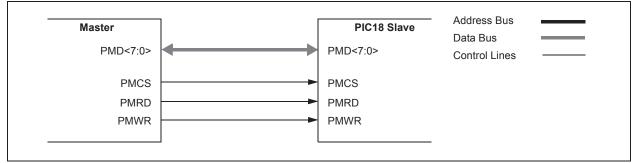

# 11.2 Slave Port Modes

The primary mode of operation for the module is configured using the MODE<1:0> bits in the PMMODEH register. The setting affects whether the module acts as a slave or a master and it determines the usage of the control pins.

#### 11.2.1 LEGACY MODE (PSP)

In Legacy mode (PMMODEH<1:0> = 00 and PMPEN = 1), the module is configured as a Parallel Slave Port (PSP) with the associated enabled module

pins dedicated to the module. In this mode, an external device, such as another microcontroller or microprocessor, can asynchronously read and write data using the 8-bit data bus (PMD<7:0>), the read (PMRD), write (PMWR) and chip select (PMCS) inputs. It acts as a slave on the bus and responds to the read/write control signals.

Figure 11-2 displays the connection of the PSP. When chip select is active and a write strobe occurs (PMCS = 1 and PMWR = 1), the data from PMD<7:0> is captured into the PMDIN1L register.

#### FIGURE 11-2: LEGACY PARALLEL SLAVE PORT EXAMPLE

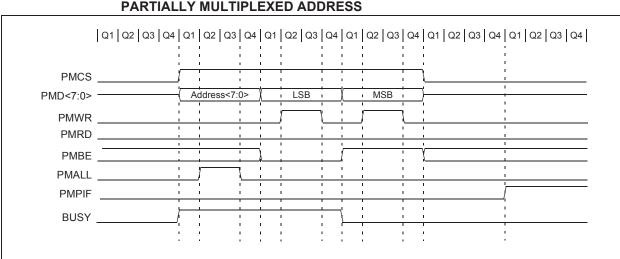

# FIGURE 11-24: WRITE TIMING, 16-BIT MULTIPLEXED DATA, PARTIALLY MULTIPLEXED ADDRESS

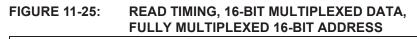

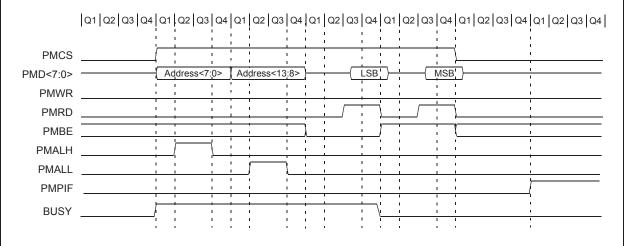

#### FIGURE 11-26: WRITE TIMING, 16-BIT MULTIPLEXED DATA, FULLY MULTIPLEXED 16-BIT ADDRESS

|          | Q1 Q2 Q3 Q4 | Q1 | Q2 Q3    | Q4          | Q1       | Q2 Q3       | Q4        | Q1          | Q2 Q3       | Q4       | Q1 | Q2 Q3 | Q4          | Q1 Q2 Q3    | Q4 Q1 Q2 Q3 C |

|----------|-------------|----|----------|-------------|----------|-------------|-----------|-------------|-------------|----------|----|-------|-------------|-------------|---------------|

| PMCS     |             |    | ı<br>ı   | 1<br>1<br>1 | <u>.</u> | <br>        | 1<br>1    | <br>        |             |          |    | <br>  | 1<br>1<br>1 | Ϋ́          | 1<br>1<br>1   |

| PMD<7:0> |             | Ad | ldress<7 | :0>         | Ad       | dress<1     | 3:8>      |             | LSB         |          |    | MSB   | I<br>I      | )           |               |

| PMWR     | i           | 1  | 1        |             | 1<br>1   | i<br>I      | 1<br>1    | I           | <u></u>     | <u> </u> |    |       | Ĺ           | 1<br>1      | -<br>-        |

| PMRD     |             | 1  |          | 1<br>1      |          | 1<br>1      | -<br>-    | 1<br>1      |             |          | 1  |       | 1<br>1      | 1<br>1      | 1             |

| PMBE     | I           |    |          | 1<br>1      | 1        | 1           | 1         |             | i<br>i      |          |    |       | !<br>!      | Ý.          | 1             |

| PMALH    |             |    |          |             |          | 1<br>1<br>1 |           | 1<br>1      | 1<br>1<br>1 | · ·      |    |       | 1<br>1      | i<br>I      | 1             |

| PMALL    |             |    |          |             |          | <u> </u>    | Ĺ         | ,<br>,<br>, | 1<br>1      | · ;      |    |       | ,<br>,<br>, | ,<br>,      |               |

| PMPIF    |             | 1  | 1        | 1<br>1      | 1<br>1   | 1<br>1      | 1<br>1    | 1<br>1      | 1<br>1      | · ·      |    | 1     | 1<br>1      | 1<br>1      |               |

| BUSY     |             |    |          |             | ;        | <br>        | <br> <br> | <br> <br>   | ,<br>,<br>, |          |    |       | <br> <br>   | 1<br>1<br>1 | 1<br>1<br>1   |

|          | 1           | 1  | 1        | •           |          | 1           |           | 1<br>1      | 1           |          |    | 1     |             |             |               |

NOTES:

| R/W-0        | R/W-0         | R/W-0                               | R/W-0          | R/W-0                              | R/W-0            | R/W-0            | R/W-0       |

|--------------|---------------|-------------------------------------|----------------|------------------------------------|------------------|------------------|-------------|

| SSCON1       | SSCON0        | TXINC                               | RXINC          | DUPLEX1                            | DUPLEX0          | DLYINTEN         | DMAEN       |

| bit 7        |               |                                     |                |                                    |                  |                  | bit C       |

|              |               |                                     |                |                                    |                  |                  |             |

| Legend:      |               |                                     | L.14           |                                    |                  | 1 10'            |             |

| R = Readab   |               | W = Writable                        |                | •                                  | nented bit, read |                  |             |

| -n = Value a | at POR        | '1' = Bit is se                     | t              | '0' = Bit is cle                   | ared             | x = Bit is unkn  | own         |

| bit 7-6      | SSCON-1.0     |                                     | nut Control bi | ts (Master mode                    | es only)         |                  |             |

|              |               |                                     | -              | of 4 bytes; DLY                    | • ·              | vs reset low     |             |

|              |               |                                     |                | of 2 bytes; DLY                    |                  |                  |             |

|              | 10 = SSDMA    | is asserted fo                      | r the duration | of 1 byte; DLYII                   | NTEN is always   | s reset low      |             |

|              |               |                                     | -              |                                    | LYINTEN bit is   | software progra  | ammable     |

| bit 5        | TXINC: Trans  | smit Address Ir                     | ncrement Ena   | ble bit                            |                  |                  |             |

|              |               |                                     |                | as the transfer                    |                  |                  |             |

|              |               |                                     |                | ented from the i                   |                  |                  |             |

|              |               |                                     | 2              | the initial value                  | e of TXADDR<1    | 1:0>             |             |

| bit 4        |               | eive Address Ir                     |                |                                    |                  |                  |             |

|              |               |                                     |                | as the transfer p                  | •                |                  |             |

|              |               |                                     |                | o the initial value                |                  | RXADDR<11:0>     |             |

| bit 3-2      |               |                                     |                | ting Mode Selec                    |                  | 11.0             |             |

|              |               |                                     | -              | -                                  |                  | nsmitted and re  | ceived      |

|              | 01 = DMA op   | erates in Half-                     | Duplex mode    | data is transmi                    | itted only       |                  |             |

|              | •             |                                     | •              | data is receive                    | d only           |                  |             |

| bit 1        |               | Delay Interrupt                     |                |                                    |                  |                  |             |

|              |               | interrupt to be the latest com      |                |                                    | TCY cycles sp    | ecified in DLYC  | YC<2:0> has |

|              |               | rupt is enabled<br>rupt is disabled |                | > must be set t                    | <b>o</b> '00'    |                  |             |

| bit 0        | DMAEN: DM     | A Operation S                       | tart/Stop bit  |                                    |                  |                  |             |

|              |               |                                     |                | tart the DMA op<br>eted or aborted |                  | set back to zero | by the DMA  |

|              | 1 = DMA is in | n session                           |                |                                    |                  |                  |             |

|              | 0 = DMA is n  | ot in accesion                      |                |                                    |                  |                  |             |

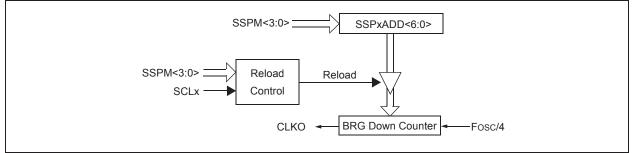

#### 20.5.7.1 Baud Rate and Module Interdependence

Because MSSP1 and MSSP2 are independent, they can operate simultaneously in I<sup>2</sup>C Master mode at different baud rates. This is done by using different BRG reload values for each module.

Because this mode derives its basic clock source from the system clock, any changes to the clock will affect both modules in the same proportion. It may be possible to change one or both baud rates back to a previous value by changing the BRG reload value.

# FIGURE 20-19: BAUD RATE GENERATOR BLOCK DIAGRAM

## TABLE 20-3: I<sup>2</sup>C CLOCK RATE w/BRG

| Fosc   | Fcy    | Fcy * 2 | BRG Value | FscL<br>(2 Rollovers of BRG) |

|--------|--------|---------|-----------|------------------------------|

| 40 MHz | 10 MHz | 20 MHz  | 18h       | 400 kHz                      |

| 40 MHz | 10 MHz | 20 MHz  | 1Fh       | 312.5 kHz                    |

| 40 MHz | 10 MHz | 20 MHz  | 63h       | 100 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 09h       | 400 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 0Ch       | 308 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 27h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 02h       | 333 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 09h       | 100 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 03h       | 1 MHz <sup>(1)</sup>         |

**Note 1:** The I<sup>2</sup>C interface does not conform to the 400 kHz I<sup>2</sup>C specification (which applies to rates greater than 100 kHz) in all details, but may be used with care where higher rates are required by the application.

#### 21.3.2 EUSART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit, SREN (RCSTAx<5>), or the Continuous Receive Enable bit, CREN (RCSTAx<4>). Data is sampled on the RXx pin on the falling edge of the clock.

If enable bit, SREN, is set, only a single word is received. If enable bit, CREN, is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- 2. Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. Ensure bits, CREN and SREN, are clear.

- 4. If interrupts are desired, set enable bit, RCxIE.

- 5. If 9-bit reception is desired, set bit, RX9.

- 6. If a single reception is required, set bit, SREN. For continuous reception, set bit, CREN.

- 7. Interrupt flag bit, RCxIF, will be set when reception is complete and an interrupt will be generated if the enable bit, RCxIE, was set.

- 8. Read the RCSTAx register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 9. Read the 8-bit received data by reading the RCREGx register.

- 10. If any error occurred, clear the error by clearing bit, CREN.

- 11. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

|             |       |             |                    | Q1 Q2 Q3 | •••      |             | • • • | · .         |             | . ,    |             |   | 1 1         |   |                  |                                      |   |

|-------------|-------|-------------|--------------------|----------|----------|-------------|-------|-------------|-------------|--------|-------------|---|-------------|---|------------------|--------------------------------------|---|

|             | bit 7 | X           | bit 6              | oit 5    |          | bit 4       | oit 3 | X           | bit 2       | $\geq$ | bit 1       | ) | bit (       |   |                  | RC7/CCP10/PMA4/                      | F |

| 1<br>1<br>1 |       |             |                    |          | ;        | ;           | 1     | ;           | <u></u>     |        | ;           |   | <u>.</u>    | ſ | ,<br>1<br>       | %/CCP9/PMA5/TX1/<br>RP17 (TXCKP = 0) |   |

| 1<br>7<br>1 |       |             |                    |          |          | ļ           |       | ;           |             |        |             |   | ;<br>       |   | 1<br>1<br>1<br>1 | %/CCP9/PMA5/TX1/<br>RP17 (TXCKP = 1) |   |

| 1<br>1<br>1 |       | 1<br>1<br>1 | 1<br>1<br>1        |          |          | 1<br>1<br>1 |       | 1<br>1<br>1 | 1<br>1<br>1 |        | 1<br>1<br>1 |   | 1<br>1<br>1 |   | '                | Write to<br>SREN bit                 |   |

| '<br>1<br>7 |       |             |                    |          |          | ;           |       |             |             |        |             |   | -           |   | ÷                | SREN bit                             |   |

| . "(        | 1 I   | ،<br>ا      |                    |          | ,<br>,   | 1           |       |             | ı<br>1      |        | <u> </u>    |   | 1           |   | ʻ0'              | CREN bit                             |   |

|             |       |             | 1<br>1<br><u>1</u> |          | <u> </u> |             |       | ,<br>,<br>, | 1<br>1<br>1 |        | ,<br>,<br>, |   | ,<br>,<br>, |   |                  | RC1IF bit<br>(Interrupt) —           |   |

|             |       | 1<br>1<br>1 | 1                  |          |          |             |       | ,<br>1<br>1 | ,<br>,<br>, |        | ,<br>,      |   |             |   |                  | Read<br>RCREG1 —                     |   |

#### FIGURE 21-13: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

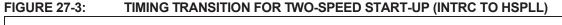

# 27.4 Two-Speed Start-up

The Two-Speed Start-up feature helps to minimize the latency period, from oscillator start-up to code execution, by allowing the microcontroller to use the INTRC oscillator as a clock source until the primary clock source is available. It is enabled by setting the IESO Configuration bit.

Two-Speed Start-up should be enabled only if the primary oscillator mode is HS or HSPLL (Crystal-Based) modes. Since the EC and ECPLL modes do not require an Oscillator Start-up Timer (OST) delay, Two-Speed Start-up should be disabled. When enabled, Resets and wake-ups from Sleep mode cause the device to configure itself to run from the internal oscillator block as the clock source, following the time-out of the Power-up Timer after a Power-on Reset is enabled. This allows almost immediate code execution while the primary oscillator starts and the OST is running. Once the OST times out, the device automatically switches to PRI\_RUN mode.

In all other power-managed modes, Two-Speed Start-up is not used. The device will be clocked by the currently selected clock source until the primary clock source becomes available. The setting of the IESO bit is ignored.

#### 27.4.1 SPECIAL CONSIDERATIONS FOR USING TWO-SPEED START-UP

While using the INTRC oscillator in Two-Speed Start-up, the device still obeys the normal command sequences for entering power-managed modes, including serial SLEEP instructions (refer to Section 4.1.4 "Multiple Sleep Commands"). In practice, this means that user code can change the SCS<1:0> bit settings or issue SLEEP instructions before the OST times out. This would allow an application to briefly wake-up, perform routine "housekeeping" tasks and return to Sleep before the device starts to operate from the primary oscillator.

User code can also check if the primary clock source is currently providing the device clocking by checking the status of the OSTS bit (OSCCON<3>). If the bit is set, the primary oscillator is providing the clock. Otherwise, the internal oscillator block is providing the clock during wake-up from Reset or Sleep mode.

# 27.5 Fail-Safe Clock Monitor

The Fail-Safe Clock Monitor (FSCM) allows the microcontroller to continue operation in the event of an external oscillator failure by automatically switching the device clock to the internal oscillator block. The FSCM function is enabled by setting the FCMEN Configuration bit.

When FSCM is enabled, the INTRC oscillator runs at all times to monitor clocks to peripherals and provide a backup clock in the event of a clock failure. Clock monitoring (shown in Figure 27-4) is accomplished by creating a sample clock signal, which is the INTRC output divided by 64. This allows ample time between FSCM sample clocks for a peripheral clock edge to occur. The peripheral device clock and the sample clock are presented as inputs to the clock monitor latch. The clock monitor is set on the falling edge of the device clock source but cleared on the rising edge of the sample clock.

#### TABLE 28-1: OPCODE FIELD DESCRIPTIONS

| Field           | Description                                                                                                                                                     |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| a               | RAM Access bit:                                                                                                                                                 |

|                 | a = 0: RAM location in Access RAM (BSR register is ignored)                                                                                                     |

|                 | a = 1: RAM bank is specified by BSR register                                                                                                                    |

| bbb             | Bit address within an 8-bit file register (0 to 7).                                                                                                             |

| BSR             | Bank Select Register. Used to select the current RAM bank.                                                                                                      |

| C, DC, Z, OV, N | ALU Status bits: Carry, Digit Carry, Zero, Overflow, Negative.                                                                                                  |

| d               | Destination Select bit:<br>d = 0: store result in WREG                                                                                                          |

|                 | d = 1: store result in file register f                                                                                                                          |

| dest            | Destination: either the WREG register or the specified register file location.                                                                                  |

| f               | 8-bit Register file address (00h to FFh), or 2-bit FSR designator (0h to 3h).                                                                                   |

| fs              | 12-bit Register file address (000h to FFFh). This is the source address.                                                                                        |

| f <sub>d</sub>  | 12-bit Register file address (000h to FFFh). This is the destination address.                                                                                   |

| GIE             | Global Interrupt Enable bit.                                                                                                                                    |

| k               | Literal field, constant data or label (may be either an 8-bit, 12-bit or a 20-bit value).                                                                       |

| label           | Label name.                                                                                                                                                     |

| mm              | The mode of the TBLPTR register for the table read and table write instructions.                                                                                |

|                 | Only used with table read and table write instructions:                                                                                                         |

| *               | No change to register (such as TBLPTR with table reads and writes)                                                                                              |

| *+              | Post-Increment register (such as TBLPTR with table reads and writes)                                                                                            |

| *_              | Post-Decrement register (such as TBLPTR with table reads and writes)                                                                                            |

| +*              | Pre-Increment register (such as TBLPTR with table reads and writes)                                                                                             |

| n               | The relative address (2's complement number) for relative branch instructions or the direct address for                                                         |

|                 | Call/Branch and Return instructions.                                                                                                                            |

| PC              | Program Counter.                                                                                                                                                |

| PCL             | Program Counter Low Byte.                                                                                                                                       |

| PCH             | Program Counter High Byte.                                                                                                                                      |

| PCLATH          | Program Counter High Byte Latch.                                                                                                                                |

| PCLATU          | Program Counter Upper Byte Latch.                                                                                                                               |

| PD              | Power-Down bit.                                                                                                                                                 |

| PRODH           | Product of Multiply High Byte.                                                                                                                                  |

| PRODL           | Product of Multiply Low Byte.                                                                                                                                   |

| S               | Fast Call/Return Mode Select bit:                                                                                                                               |