#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

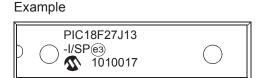

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 10x10b/12b                                                             |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 28-SPDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f27j13-i-sp |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                   |                                                                                  | Pin                                                                                                                                    | Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

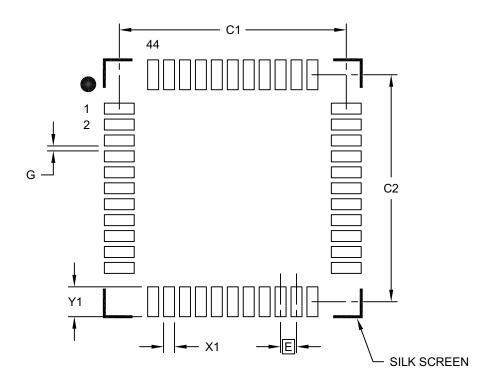

| 44-<br>QFN        | 44-<br>TQFP                                                                      | Туре                                                                                                                                   | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                   |                                                                                  |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PORTB (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 14 <sup>(3)</sup> | 14(3)                                                                            | I/O<br>I/O<br>I/O                                                                                                                      | TTL/DIG<br>ST/DIG<br>ST/TTL/<br>DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Capture/Compare/PWM input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                   |                                                                                  | I<br>I/O                                                                                                                               | TTL<br>ST/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Interrupt-on-change pin.<br>Remappable Peripheral Pin 7 input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 15 <sup>(3)</sup> | 15 <sup>(3)</sup>                                                                | I/O<br>I/O<br>I/O                                                                                                                      | TTL/DIG<br>ST/DIG<br>ST/TTL/<br>DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Digital I/O.<br>Capture/Compare/PWM input/output.<br>Parallel Master Port address.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                   |                                                                                  | I<br>I/O                                                                                                                               | TTL<br>ST/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Interrupt-on-change pin.<br>Remappable Peripheral Pin 8 input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16 <sup>(3)</sup> | 16 <sup>(3)</sup>                                                                | I/O<br>I/O<br>I<br>I/O                                                                                                                 | TTL/DIG<br>ST/DIG<br>TTL<br>ST<br>ST/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Digital I/O.<br>Capture/Compare/PWM input/output.<br>Interrupt-on-change pin.<br>ICSP™ clock input.<br>Remappable Peripheral Pin 9 input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 17 <sup>(3)</sup> | 17 <sup>(3)</sup>                                                                | I/O<br>I/O<br>I<br>I/O                                                                                                                 | TTL/DIG<br>ST/DIG<br>TTL<br>ST/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Digital I/O.<br>Capture/Compare/PWM input/output.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming<br>data pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                   |                                                                                  | I/O                                                                                                                                    | ST/DIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Remappable Peripheral Pin 10 input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   | h CMO                                                                            | S level                                                                                                                                | S .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CMOS= CMOS compatible input or outputAnalog= Analog inputO= OutputOD= Open-Drain (no P diode to VDD) $l^2C$ = Open-Drain, $l^2C$ specific                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                   | 15 <sup>(3)</sup><br>16 <sup>(3)</sup><br>17 <sup>(3)</sup><br>input<br>nput wit | 15 <sup>(3)</sup> 15 <sup>(3)</sup><br>16 <sup>(3)</sup> 16 <sup>(3)</sup><br>17 <sup>(3)</sup> 17 <sup>(3)</sup><br>17 <sup>(3)</sup> | 15(3)       15(3)       I/O         15(3)       15(3)       I/O         16(3)       16(3)       I/O         16(3)       16(3)       I/O         17(3)       17(3)       I/O         17(3)       17(3)       I/O         I/O       I/O       I/O         I/O | $10^{(3)}$ $15^{(3)}$ $15^{(3)}$ $15^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ $10^{(3)}$ |

#### TABLE 1-4 PIC18F4X.I13 PINOUT I/O DESCRIPTIONS (CONTINUED)

2: Available only on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

3: 5.5V tolerant.

#### 3.3 Clock Sources and Oscillator Switching

Like previous PIC18 enhanced devices, the PIC18F47J13 Family includes a feature that allows the device clock source to be switched from the main oscillator to an alternate, low-frequency clock source. PIC18F47J13 Family devices offer two alternate clock sources. When an alternate clock source is enabled, the various power-managed operating modes are available.

Essentially, there are three clock sources for these devices:

- Primary Oscillators

- Secondary Oscillators

- Internal Oscillator Block

The **Primary Oscillators** include the External Crystal and Resonator modes, the External Clock modes and the internal oscillator block. The particular mode is defined by the FOSC<2:0> Configuration bits. The details of these modes are covered earlier in this chapter.

The **Secondary Oscillators** are external sources that are not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power-managed mode.

PIC18F47J13 Family devices offer the Timer1 oscillator as a secondary oscillator. This oscillator, in all power-managed modes, is often the time base for functions such as a Real-Time Clock (RTC). Most often, a 32.768 kHz watch crystal is connected between the RC0/T1OSO/T1CKI/RP11 and RC1/CCP8/T1OSI/RP12 pins. Like the HS Oscillator mode circuits, loading capacitors are also connected from each pin to ground. The Timer1 oscillator is discussed in larger detail in Section 13.5 "Timer1 Oscillator".

In addition to being a primary clock source, the **postscaled internal clock** is available as a power-managed mode clock source. The INTRC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor (FSCM).

#### 3.3.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 3-2) controls several aspects of the device clock's operation, both in full-power operation and in power-managed modes.

The System Clock Select bits, SCS<1:0>, select the clock source. The available clock sources are the primary clock (defined by the FOSC<2:0> Configuration bits), the secondary clock (Timer1 oscillator) and the postscaled internal clock. The clock source changes immediately, after one or more of the bits is written to, following a brief clock transition interval. The SCS bits are cleared on all forms of Reset.

The Internal Oscillator Frequency Select bits, IRCF<2:0>, select the frequency output provided on the postscaled internal clock line. The choices are the INTRC source, the INTOSC source (8 MHz) or one of the frequencies derived from the INTOSC postscaler (31 kHz to 4 MHz). If the postscaled internal clock is supplying the device clock, changing the states of these bits will have an immediate change on the internal oscillator's output. On device Resets, the default output frequency of the INTOSC postscaler is set at 4 MHz.

When an output frequency of 31 kHz is selected (IRCF<2:0> = 000), users may choose the internal oscillator, which acts as the source. This is done with the INTSRC bit in the OSCTUNE register (OSCTUNE<7>). Setting this bit selects INTOSC as a 31.25 kHz clock source by enabling the divide-by-256 output of the INTOSC postscaler. Clearing INTSRC selects INTRC (nominally 31 kHz) as the clock source.

This option allows users to select the tunable and more precise INTOSC as a clock source, while maintaining power savings with a very low clock speed. Regardless of the setting of INTSRC, INTRC always remains the clock source for features such as the WDT and the FSCM.

The OSTS and SOSCRUN bits indicate which clock source is currently providing the device clock. The OSTS bit indicates that the Oscillator Start-up Timer (OST) has timed out and the primary clock is providing the device clock in primary clock modes. The SOSCRUN bit (OSC-CON2<6>) indicates when the Timer1 oscillator is providing the device clock in secondary clock modes. In power-managed modes, only one of these bits will be set at any time. If none of these bits are set, the INTRC is providing the clock or the internal oscillator block has just started and is not yet stable.

The IDLEN bit determines if the device goes into Sleep mode, or one of the Idle modes, when the SLEEP instruction is executed.

#### 3.4 Reference Clock Output

In addition to the peripheral clock/4 output in certain oscillator modes, the device clock in the PIC18F47J13 Family can also be configured to provide a reference clock output signal to a port pin. This feature is available in all oscillator configurations and allows the user to select a greater range of clock submultiples to drive external devices in the application.

This reference clock output is controlled by the REFOCON register (Register 3-4). Setting the ROON bit (REFOCON<7>) makes the clock signal available on the REFO (RB2) pin. The RODIV<3:0> bits enable the selection of 16 different clock divider options.

The ROSSLP and ROSEL bits (REFOCON<5:4>) control the availability of the reference output during Sleep mode. The ROSEL bit determines if the oscillator is on OSC1 and OSC2, or the current system clock source is used for the reference clock output. The ROSSLP bit determines if the reference source is available on RB2 when the device is in Sleep mode.

To use the reference clock output in Sleep mode, both the ROSSLP and ROSEL bits must be set. The device clock must also be configured for an EC or HS mode; otherwise, the oscillator on OSC1 and OSC2 will be powered down when the device enters Sleep mode. Clearing the ROSEL bit allows the reference output frequency to change as the system clock changes during any clock switches.

#### REGISTER 3-4: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER (BANKED F3Dh)

| R/W-0      | U-0                                                             | R/W-0                                 | R/W-0          | R/W-0            | R/W-0              | R/W-0            | R/W-0            |  |  |

|------------|-----------------------------------------------------------------|---------------------------------------|----------------|------------------|--------------------|------------------|------------------|--|--|

| ROON       | —                                                               | ROSSLP                                | ROSEL          | RODIV3           | RODIV2             | RODIV1           | RODIV0           |  |  |

| bit 7      | L                                                               |                                       |                | ł                |                    | 1                | bit 0            |  |  |

| <b></b>    |                                                                 |                                       |                |                  |                    |                  |                  |  |  |

| Legend:    |                                                                 |                                       |                |                  |                    |                  |                  |  |  |

| R = Reada  |                                                                 | W = Writable t                        | bit            | -                | mented bit, read   |                  |                  |  |  |

| -n = Value | at POR                                                          | '1' = Bit is set                      |                | '0' = Bit is cle | ared               | x = Bit is unkr  | nown             |  |  |

| bit 7      | ROON: Refe                                                      | rence Oscillator                      | Output Enab    | le hit           |                    |                  |                  |  |  |

| bit i      |                                                                 | e oscillator is en                    |                |                  |                    |                  |                  |  |  |

|            |                                                                 | e oscillator is dis                   |                |                  |                    |                  |                  |  |  |

| bit 6      | Unimplemen                                                      | nted: Read as '0                      | ,              |                  |                    |                  |                  |  |  |

| bit 5      | ROSSLP: Re                                                      | eference Oscillat                     | or Output Sto  | op in Sleep bit  |                    |                  |                  |  |  |

|            | 1 = Referenc                                                    | e oscillator conti                    | nues to run i  | n Sleep          |                    |                  |                  |  |  |

|            | 0 = Referenc                                                    | e oscillator is dis                   | sabled in Slee | ер               |                    |                  |                  |  |  |

| bit 4      |                                                                 | erence Oscillato                      |                |                  |                    |                  |                  |  |  |

|            |                                                                 | oscillator crystal                    |                |                  |                    |                  | <i>.</i>         |  |  |

|            | •                                                               | clock (Fosc) is us                    |                |                  | e clock reflects a | NY CIOCK SWITCHI | ng of the device |  |  |

| bit 3-0    |                                                                 | : Reference Osc                       |                |                  |                    |                  |                  |  |  |

|            |                                                                 | clock value divi                      |                |                  |                    |                  |                  |  |  |

|            |                                                                 | clock value divi                      |                |                  |                    |                  |                  |  |  |

|            |                                                                 | clock value divi                      |                |                  |                    |                  |                  |  |  |

|            |                                                                 | clock value divi                      |                |                  |                    |                  |                  |  |  |

|            |                                                                 | clock value divi                      |                | Ļ                |                    |                  |                  |  |  |

|            |                                                                 | clock value divi                      |                |                  |                    |                  |                  |  |  |

|            |                                                                 | clock value divi                      |                |                  |                    |                  |                  |  |  |

|            | 0110 = Base clock value divided by 64                           |                                       |                |                  |                    |                  |                  |  |  |

|            |                                                                 | 0101 = Base clock value divided by 32 |                |                  |                    |                  |                  |  |  |

|            |                                                                 | 0100 = Base clock value divided by 16 |                |                  |                    |                  |                  |  |  |

|            |                                                                 | clock value divi                      |                |                  |                    |                  |                  |  |  |

|            |                                                                 |                                       |                |                  |                    |                  |                  |  |  |

|            | 0001 = Base clock value divided by 2<br>0000 = Base clock value |                                       |                |                  |                    |                  |                  |  |  |

| Note 1     | The crystal oscill                                              | ator must be en:                      | ahled usina ti | he FOSC<2.0>     | hits: the crystal  | maintains the    | operation in     |  |  |

**Note 1:** The crystal oscillator must be enabled using the FOSC<2:0> bits; the crystal maintains the operation in Sleep mode.

#### 10.3 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISB. Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATB) is also memory mapped. Read-modify-write operations on the LATB register read and write the latched output value for PORTB.

| CLRF           | PORTB          | ; Initialize PORTB by ; clearing output                                |

|----------------|----------------|------------------------------------------------------------------------|

| CLRF           | LATB           | ; data latches<br>; Alternate method<br>; to clear output              |

| MOVLB          | OxOF           | ; data latches<br>; ANCON1 not in Access<br>; Bank                     |

| MOVLW<br>MOVWF | 0x17<br>ANCON1 | ; Configure as digital I/O<br>; pins in this example                   |

| MOVLW          | 0xCF           | ; Value used to<br>; initialize data<br>; direction                    |

| MOVWF          | TRISB          | ; Set RB<3:0> as inputs<br>; RB<5:4> as outputs<br>; RB<7:6> as inputs |

|                |                |                                                                        |

EXAMPLE 10-3: INITIALIZING PORTB

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn <u>on all</u> the pull-ups. This is performed by clearing bit, RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a POR. The integrated weak pull-ups consist of a semiconductor structure similar to, but somewhat different from, a discrete resistor. On an unloaded I/O pin, the weak pull-ups are intended to provide logic high indication, but will not necessarily pull the pin all the way to VDD levels.

| Note: | On a     | POR,      | the   | RB<3:0>      | bits    | are  |

|-------|----------|-----------|-------|--------------|---------|------|

|       | configu  | red as a  | nalog | inputs by d  | lefault | and  |

|       | read as  | 6'0'; RE  | 3<7:4 | > bits are o | config  | ured |

|       | as digit | al inputs | S.    |              |         |      |

Four of the PORTB pins (RB<7:4>) have an interrupton-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupton-change comparison). The input pins (of RB<7:4>) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from Sleep mode or any of the Idle modes. Application software can clear the interrupt flag by following these steps:

- 1. Any read or write of PORTB (except with the MOVFF (ANY), PORTB instruction).

- 2. Wait one instruction cycle (such as executing a NOP instruction).

- 3. Clear flag bit, RBIF.

A mismatch condition continues to set flag bit, RBIF. Reading PORTB will end the mismatch condition and allow flag bit, RBIF, to be cleared after one instruction cycle of delay.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

The RB5 pin is multiplexed with the Timer0 module clock input and one of the comparator outputs to become the RB5/CCP5/PMA0/KBI1/RP8 pin.

## PIC18F47J13 FAMILY

| <b>TABLE 10-9</b> : | PORTD I/O SUMMARY |

|---------------------|-------------------|

|---------------------|-------------------|

| TABLE 10-9: |                     |                 |     |                          |                                                                                        |  |

|-------------|---------------------|-----------------|-----|--------------------------|----------------------------------------------------------------------------------------|--|

| Pin         | Function            | TRIS<br>Setting | I/O | I/O<br>Type              | Description                                                                            |  |

| RD0/PMD0/   | RD0                 | 1               | Ι   | ST                       | PORTD<0> data input.                                                                   |  |

| SCL2        |                     | 0               | 0   | DIG                      | LATD<0> data output.                                                                   |  |

|             | PMD0 <sup>(1)</sup> | 1               | I   | ST/TTL                   | Parallel Master Port data in.                                                          |  |

|             |                     | 0               | 0   | DIG                      | Parallel Master Port data out.                                                         |  |

|             | SCL2 <sup>(1)</sup> | 1               | I   | I <sup>2</sup> C/<br>SMB | I <sup>2</sup> C clock input (MSSP2 module); input type depends on the module setting. |  |

|             |                     | 0               | 0   | DIG                      | I <sup>2</sup> C clock output (MSSP2 module); takes priority over port data.           |  |

| RD1/PMD1/   | RD1                 | 1               | Ι   | ST                       | PORTD<1> data input.                                                                   |  |

| SDA2        |                     | 0               | 0   | DIG                      | LATD<1> data output.                                                                   |  |

|             | PMD1 <sup>(1)</sup> | 1               | Ι   | ST/TTL                   | Parallel Master Port data in.                                                          |  |

|             |                     | 0               | 0   | DIG                      | Parallel Master Port data out.                                                         |  |

|             | SDA2 <sup>(1)</sup> | 1               | I   | I <sup>2</sup> C/<br>SMB | I <sup>2</sup> C data input (MSSP2 module); input type depends on the module setting.  |  |

|             |                     | 0               | 0   | DIG                      | I <sup>2</sup> C data output (MSSP2 module); takes priority over port data.            |  |

| RD2/PMD2/   | RD2                 | 1               | I   | ST                       | PORTD<2> data input.                                                                   |  |

| RP19        |                     | 0               | 0   | DIG                      | LATD<2> data output.                                                                   |  |

|             | PMD2 <sup>(1)</sup> | 1               | I   | ST/TTL                   | Parallel Master Port data in.                                                          |  |

|             |                     | 0               | 0   | DIG                      | Parallel Master Port data out.                                                         |  |

|             | RP19                | 1               | Ι   | ST                       | Remappable Peripheral Pin 19 input.                                                    |  |

|             |                     | 0               | 0   | DIG                      | Remappable Peripheral Pin 19 output.                                                   |  |

| RD3/PMD3/   | RD3                 | 1               | Ι   | ST                       | PORTD<3> data input.                                                                   |  |

| RP20        |                     | 0               | 0   | DIG                      | LATD<3> data output.                                                                   |  |

|             | PMD3 <sup>(1)</sup> | 1               | Ι   | ST/TTL                   | Parallel Master Port data in.                                                          |  |

|             |                     | 0               | 0   | DIG                      | Parallel Master Port data out.                                                         |  |

|             | RP20                | 1               | I   | ST                       | Remappable Peripheral Pin 20 input.                                                    |  |

|             |                     | 0               | 0   | DIG                      | Remappable Peripheral Pin 20 output.                                                   |  |

| RD4/PMD4/   | RD4                 | 1               | Ι   | ST                       | PORTD<4> data input.                                                                   |  |

| RP21        |                     | 0               | 0   | DIG                      | LATD<4> data output.                                                                   |  |

|             | PMD4 <sup>(1)</sup> | 1               | Ι   | ST/TTL                   | Parallel Master Port data in.                                                          |  |

|             |                     | 0               | 0   | DIG                      | Parallel Master Port data out.                                                         |  |

|             | RP21                | 1               | Ι   | ST                       | Remappable Peripheral Pin 21 input.                                                    |  |

|             |                     | 0               | 0   | DIG                      | Remappable Peripheral Pin 21 output.                                                   |  |

| RD5/PMD5/   | RD5                 | 1               | Ι   | ST                       | PORTD<5> data input.                                                                   |  |

| RP22        |                     | 0               | 0   | DIG                      | LATD<5> data output.                                                                   |  |

|             | PMD5 <sup>(1)</sup> | 1               | Ι   | ST/TTL                   | Parallel Master Port data in.                                                          |  |

|             |                     | 0               | 0   | DIG                      | Parallel Master Port data out.                                                         |  |

|             | RP22                | 1               | Ι   | ST                       | Remappable Peripheral Pin 22 input.                                                    |  |

|             |                     | 0               | 0   | DIG                      | Remappable Peripheral Pin 22 output.                                                   |  |

|             |                     |                 |     |                          | Iffer: ST = Sebmitt Triager input buffer: $I^2C/SMP = I^2C/SMP$                        |  |

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer;  $I^2C/SMB = I^2C/SMB$ us input buffer; x = Don't care (TRISx bit does not affect port direction or is overridden for this option).

Note 1: Only on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

#### 11.1 Module Registers

The PMP module has a total of 14 Special Function Registers (SFRs) for its operation, plus one additional register to set configuration options. Of these, eight registers are used for control and six are used for PMP data transfer.

#### 11.1.1 CONTROL REGISTERS

The eight PMP Control registers are:

- PMCONH and PMCONL

- PMMODEH and PMMODEL

- PMSTATL and PMSTATH

- PMEH and PMEL

The PMCON registers (Register 11-1 and Register 11-2) control basic module operations, including turning the module on or off. They also configure address multiplexing and control strobe configuration.

The PMMODE registers (Register 11-3 and Register 11-4) configure the various Master and Slave modes, the data width and interrupt generation.

The PMEH and PMEL registers (Register 11-5 and Register 11-6) configure the module's operation at the hardware (I/O pin) level.

The PMSTAT registers (Register 11-5 and Register 11-6) provide status flags for the module's input and output buffers, depending on the operating mode.

#### REGISTER 11-1: PMCONH: PARALLEL PORT CONTROL REGISTER HIGH BYTE (BANKED F5Fh)<sup>(1)</sup>

| R/W-0 | U-0 | U-0 | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|---------|---------|--------|--------|--------|

| PMPEN | —   | —   | ADRMUX1 | ADRMUX0 | PTBEEN | PTWREN | PTRDEN |

| bit 7 |     |     |         |         |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | PMPEN: Parallel Master Port Enable bit                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------|

|         | 1 = PMP enabled                                                                                                       |

|         | 0 = PMP disabled, no off-chip access performed                                                                        |

| bit 6-5 | Unimplemented: Read as '0'                                                                                            |

| bit 4-3 | ADRMUX<1:0>: Address/Data Multiplexing Selection bits                                                                 |

|         | 11 = Reserved                                                                                                         |

|         | 10 = All 16 bits of address are multiplexed on PMD<7:0> pins                                                          |

|         | 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins (only eight bits of address are available in this mode) |

|         | 00 = Address and data appear on separate pins (only eight bits of address are available in this mode)                 |

| bit 2   | PTBEEN: Byte Enable Port Enable bit (16-Bit Master mode)                                                              |

|         | 1 = PMBE port enabled                                                                                                 |

|         | 0 = PMBE port disabled                                                                                                |

| bit 1   | PTWREN: Write Enable Strobe Port Enable bit                                                                           |

|         | 1 = PMWR/PMENB port enabled                                                                                           |

|         | 0 = PMWR/PMENB port disabled                                                                                          |

| bit 0   | PTRDEN: Read/Write Strobe Port Enable bit                                                                             |

|         | 1 = PMRD/PMWR port enabled                                                                                            |

|         | 0 = PMRD/PMWR port disabled                                                                                           |

|         |                                                                                                                       |

**Note 1:** This register is only available on 44-pin devices.

#### 15.6 Timer3/5 Interrupt

The TMRx register pair (TMRxH:TMRxL) increments from 0000h to FFFFh and overflows to 0000h. The Timerx interrupt, if enabled, is generated on overflow and is latched in the interrupt flag bit, TMRxIF. Table 15-3 gives each module's flag bit.

TABLE 15-3: TIMER3/5 INTERRUPT FLAG BITS

| Timer Module | Flag Bit |

|--------------|----------|

| 3            | PIR2<1>  |

| 5            | PIR5<1>  |

This interrupt can be enabled or disabled by setting or clearing the TMRxIE bit, respectively. Table 15-4 gives each module's enable bit.

#### TABLE 15-4: TIMER3/5 INTERRUPT ENABLE BITS

| Timer Module | Flag Bit |

|--------------|----------|

| 3            | PIE2<1>  |

| 5            | PIE5<2>  |

#### 15.7 Resetting Timer3/5 Using the ECCP Special Event Trigger

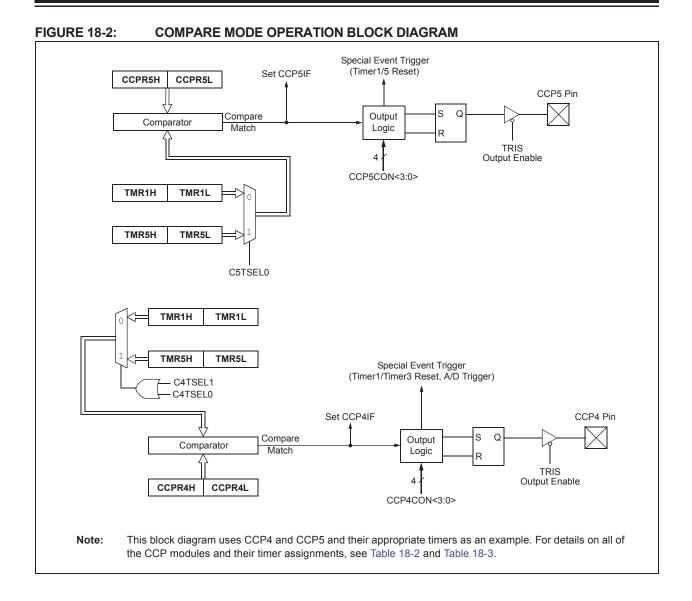

If the ECCP modules are configured to use Timerx and to generate a Special Event Trigger in Compare mode (CCPxM<3:0> = 1011), this signal will reset Timerx. The trigger from ECCP2 will also start an A/D conversion if the A/D module is enabled. (For more information, see Section 19.3.4 "Special Event Trigger".)

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPRxH:CCPRxL register pair effectively becomes a Period register for TimerX.

If Timerx is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timerx coincides with a Special Event Trigger from an ECCP module, the write will take precedence.

| Note: | The Special Event Triggers from the        |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | ECCPx module will only clear the TMR3      |  |  |  |  |  |  |  |  |

|       | register's content, but not set the TMR3IF |  |  |  |  |  |  |  |  |

|       | interrupt flag bit (PIR1<0>).              |  |  |  |  |  |  |  |  |

Note: The CCP and ECCP modules use Timers, 1 through 8, for some modes. The assignment of a particular timer to a CCP/ECCP module is determined by the Timer to CCP enable bits in the CCPTMRSx registers. For more details, see Register 18-3 and Register 19-2.

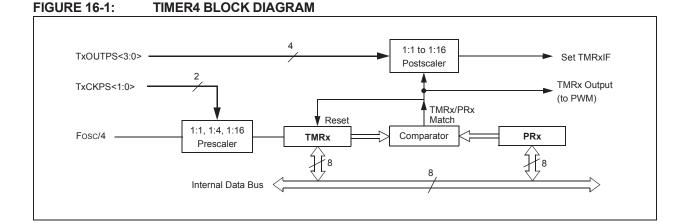

## REGISTER 16-1: TxCON: TIMER4/6/8 CONTROL REGISTER (ACCESS F76h, BANKED F1Eh, BANKED F1Bh)

| U-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0   |

|-------|----------|----------|----------|----------|--------|---------|---------|

| —     | TxOUTPS3 | TxOUTPS2 | TxOUTPS1 | TxOUTPS0 | TMRxON | TxCKPS1 | TxCKPS0 |

| bit 7 |          |          |          |          |        |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                        |

|---------|---------------------------------------------------|

| bit 6-3 | TxOUTPS<3:0>: Timerx Output Postscale Select bits |

|         | 0000 = 1:1 Postscale                              |

|         | 0001 = 1:2 Postscale                              |

|         | •                                                 |

|         | •                                                 |

|         |                                                   |

|         | 1111 = 1:16 Postscale                             |

| bit 2   | TMRxON: Timerx On bit                             |

|         | 1 = Timerx is on                                  |

|         | 0 = Timerx is off                                 |

| bit 1-0 | TxCKPS<1:0>: Timerx Clock Prescale Select bits    |

|         | 00 = Prescaler is 1                               |

|         | 01 = Prescaler is 4                               |

|         | 1x = Prescaler is 16                              |

|         |                                                   |

#### 16.2 Timer4/6/8 Interrupt

The Timer4/6/8 modules have 8-bit Period registers, PRx, that are both readable and writable. Timer4/6/8 increment from 00h until they match PR4/6/8 and then reset to 00h on the next increment cycle. The PRx registers are initialized to FFh upon Reset.

#### 16.3 Output of TMRx

The outputs of TMRx (before the postscaler) are used only as a PWM time base for the ECCP modules. They are not used as baud rate clocks for the MSSP modules as is the Timer2 output.

# PIC18F47J13 FAMILY

#### REGISTER 17-5: ALRMRPT: ALARM REPEAT COUNTER (ACCESS F46h)

| ARPT7         ARPT6         ARPT5         ARPT4         ARPT3         ARPT2         ARPT1         ARPT0           bit 7         bit 0 | R/W-0 |

|---------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| bit 7 bit 0                                                                                                                           | ARPT7 | ARPT6 | ARPT5 | ARPT4 | ARPT3 | ARPT2 | ARPT1 | ARPT0 |

|                                                                                                                                       | bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |