#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| 2000                       |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 22                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 10x10b/12b                                                             |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 28-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f27j13-i-ss |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                                           | 9     |

|-------|---------------------------------------------------------------------------|-------|

| 2.0   | Guidelines for Getting Started with PIC18FJ Microcontrollers              | 28    |

| 3.0   | Oscillator Configurations                                                 | 32    |

| 4.0   | Low-Power Modes                                                           | 43    |

| 5.0   | Reset                                                                     | 60    |

| 6.0   | Memory Organization                                                       | 75    |

| 7.0   | Flash Program Memory                                                      | . 101 |

| 8.0   | 8 x 8 Hardware Multiplier                                                 | . 111 |

| 9.0   | Interrupts                                                                | . 113 |

| 10.0  | I/O Ports                                                                 | . 133 |

| 11.0  | Parallel Master Port (PMP)                                                | . 173 |

| 12.0  | Timer0 Module                                                             | . 198 |

| 13.0  | Timer1 Module                                                             | . 202 |

| 14.0  | Timer2 Module                                                             | . 212 |

| 15.0  | Timer3/5 Module                                                           | . 214 |

| 16.0  | Timer4/6/8 Module                                                         | . 226 |

| 17.0  | Real-Time Clock and Calendar (RTCC)                                       | . 229 |

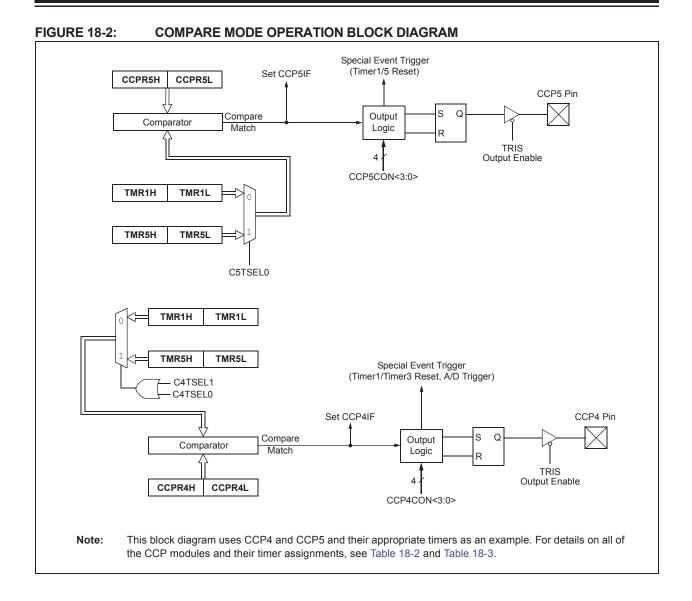

| 18.0  | Capture/Compare/PWM (CCP) Modules                                         | . 248 |

| 19.0  | Enhanced Capture/Compare/PWM (ECCP) Module                                | . 260 |

| 20.0  | Master Synchronous Serial Port (MSSP) Module                              |       |

| 21.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | . 336 |

| 22.0  | 10/12-Bit Analog-to-Digital Converter (A/D) Module                        | . 358 |

| 23.0  | Comparator Module                                                         |       |

| 24.0  | Comparator Voltage Reference Module                                       |       |

| 25.0  | High/Low Voltage Detect (HLVD)                                            | . 380 |

| 26.0  | Charge Time Measurement Unit (CTMU)                                       |       |

| 27.0  | Special Features of the CPU                                               | . 403 |

| 28.0  | Instruction Set Summary                                                   | . 420 |

| 29.0  | Development Support                                                       | . 470 |

| 30.0  | Electrical Characteristics                                                |       |

| 31.0  | Packaging Information                                                     | . 516 |

|       | ndix A: Revision History                                                  |       |

| Appe  | ndix B: Migration From PIC18F46J11 to PIC18F47J13                         | . 534 |

|       | /icrochip Website                                                         |       |

|       | mer Change Notification Service                                           |       |

|       | mer Support                                                               |       |

| Produ | uct Identification System                                                 | . 536 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

Microchip's Worldwide Website; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

The use of the flag and control bits in the OSCCON register is discussed in more detail in **Section 4.0** "Low-Power Modes".

- Note 1: The Timer1 crystal driver is enabled by setting the T1OSCEN bit in the Timer1 Control register (T1CON<3>). If the Timer1 oscillator is not enabled, then any attempt to select the Timer1 clock source will be ignored, unless the CONFIG2L register's SOSCSEL<1:0> bits are set to Digital mode.

- 2: If Timer1 is driving a crystal, it is recommended that the Timer1 oscillator be operating and stable prior to switching to it as the clock source; otherwise, a very long delay may occur while the Timer1 oscillator starts.

### 3.3.2 OSCILLATOR TRANSITIONS

PIC18F47J13 Family devices contain circuitry to prevent clock "glitches" when switching between clock sources. A short pause in the device clock occurs during the clock switch. The length of this pause is the sum of two cycles of the old clock source and three to four cycles of the new clock source. This formula assumes that the new clock source is stable.

Clock transitions are discussed in more detail in **Section 4.1.2 "Entering Power-Managed Modes**".

### REGISTER 3-2: OSCCON: OSCILLATOR CONTROL REGISTER (ACCESS FD3h)

| R/W-0 | R/W-1 | R/W-1 | R/W-0 | R-1 <sup>(1)</sup> | U-1 | R/W-0 | R/W-0 |

|-------|-------|-------|-------|--------------------|-----|-------|-------|

| IDLEN | IRCF2 | IRCF1 | IRCF0 | OSTS               | —   | SCS1  | SCS0  |

| bit 7 |       |       |       |                    |     |       | bit 0 |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

| bit 7   | IDLEN: Idle Enable bit<br>1 = Device enters Idle mode on SLEEP instruction<br>0 = Device enters Sleep mode on SLEEP instruction                                                                                                                                                                                                                                                                              |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | <pre>IRCF&lt;2:0&gt;: Internal Oscillator Frequency Select bits When using INTOSC to drive the 4x PLL, select 8 MHz or 4 MHz only to avoid operating the 4x PLL outside of specification. 111 = 8 MHz (INTOSC drives clock directly) 110 = 4 MHz<sup>(2)</sup> 101 = 2 MHz 100 = 1 MHz 011 = 500 kHz 010 = 250 kHz 001 = 125 kHz 000 = 31 kHz (from either INTOSC/256 or INTRC directly)<sup>(3)</sup></pre> |

| bit 3   | <b>OSTS:</b> Oscillator Start-up Time-out Status bit <sup>(1)</sup><br>1 = Oscillator Start-up Timer time-out has expired; primary oscillator is running<br>0 = Oscillator Start-up Timer time-out is running; primary oscillator is not ready                                                                                                                                                               |

| bit 2   | Unimplemented: Read as '1'                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 1-0 | SCS<1:0>: System Clock Select bits<br>11 = Postscaled internal clock (INTRC/INTOSC derived)<br>10 = Reserved<br>01 = Timer1 oscillator<br>00 = Primary clock source (INTOSC postscaler output when FOSC<2:0> = 001 or 000)<br>00 = Primary clock source (CPU divider output for other values of FOSC<2:0>)                                                                                                   |

| Note 1: | Reset value is '0' when Two-Speed Start-up is enabled and '1' if disabled.                                                                                                                                                                                                                                                                                                                                   |

- **2:** Default output frequency of INTOSC on Reset (4 MHz).

- **3:** Source selected by the INTSRC bit (OSCTUNE<7>).

| Addr. | File Name             | Bit 7       | Bit 6       | Bit 5           | Bit 4         | Bit 3               | Bit 2              | Bit 1        | Bit 0   | Value on<br>POR, BOR |

|-------|-----------------------|-------------|-------------|-----------------|---------------|---------------------|--------------------|--------------|---------|----------------------|

| F07h  | CCPR8L                | Capture/Com | pare/PWM Re | gister 8 Low E  | Byte          |                     |                    |              |         | XXXX XXXX            |

| F06h  | CCP8CON               | _           | _           | DC8B1           | DC8B0         | CCP8M3              | CCP8M2             | CCP8M1       | CCP8M0  | 00 0000              |

| F05h  | CCPR9H                | Capture/Com | pare/PWM Re | gister 9 High I | Byte          |                     |                    |              |         | XXXX XXXX            |

| F04h  | CCPR9L                | Capture/Com | pare/PWM Re | gister 9 Low E  | Byte          |                     | _                  |              |         | XXXX XXXX            |

| F03h  | CCP9CON               | —           | —           | DC9B1           | DC9B0         | CCP9M3              | CCP9M2             | CCP9M1       | CCP9M0  | 00 0000              |

| F02h  | CCPR10H               | Capture/Com | pare/PWM Re | gister 10 High  | Byte          |                     | <u>.</u>           |              |         | XXXX XXXX            |

| F01h  | CCPR10L               | Capture/Com | pare/PWM Re | gister 10 Low   | Byte          |                     |                    |              |         | XXXX XXXX            |

| F00h  | CCP10CON              | —           | _           | DC10B1          | DC10B0        | CCP10M3             | CCP10M2            | CCP10M1      | CCP10M0 | 00 0000              |

| EFFh  | RPINR24               | —           | _           | _               | PWM Fault Ir  | nput (FLT0) to      | Input Pin Mapp     | bing bits    |         | 1 1111               |

| EFEh  | RPINR23               | _           | _           | _               | SPI2 Slave S  | elect Input (S      | S2) to Input Pin   | Mapping bits |         | 1 1111               |

| EFDh  | RPINR22               | —           | _           | _               | SPI2 Clock Ir | nput (SCK2) to      | o Input Pin Map    | ping bits    |         | 1 1111               |

| EFCh  | RPINR21               | —           | _           | _               | SPI2 Data In  | put (SDI2) to I     | nput Pin Mappi     | ng bits      |         | 1 1111               |

| EFBh  | _                     | _           | _           | _               | _             | _                   | <u> </u>           | _            | _       | (3)                  |

| EFAh  | _                     | _           | _           | _               | _             | _                   | _                  | _            | _       | (3)                  |

| EF9h  | _                     | _           | _           | _               | _             | _                   | _                  | _            | _       | (3)                  |

| EF8h  | RPINR17               | _           | _           | _               | EUSART2 C     | lock Input (CK      | 2) to Input Pin I  | Mapping bits |         | 1 1111               |

| EF7h  | RPINR16               | _           | _           | _               | EUSART2 R     | X2/DT2 to Inp       | ut Pin Mapping     | bits         |         | 1 1111               |

| EF6h  | _                     | _           | _           | _               |               | _                   | _                  | _            | _       | (3)                  |

| EF5h  | _                     | _           | _           | _               | _             | _                   | _                  | _            | _       | (3)                  |

| EF4h  | RPINR14               | _           | _           | _               | Timer5 Gate   | I<br>Input (T5G) to | I<br>Input Pin Map | ning bits    |         | 1 1111               |

| EF3h  | RPINR13               | _           | _           |                 |               | 1 ( )               | o Input Pin Map    |              |         | 1 1111               |

| EF2h  | RPINR12               |             | _           | _               | -             |                     | o Input Pin Map    |              |         | 1 1111               |

| EF1h  |                       |             |             |                 |               |                     |                    |              | _       | (3)                  |

| EF0h  |                       |             |             |                 |               |                     |                    |              |         | (3)                  |

| EEFh  |                       |             |             |                 |               |                     |                    |              |         | (3)                  |

| EEEh  |                       |             |             |                 |               |                     |                    |              |         | (3)                  |

| EEDh  |                       | <u> </u>    |             |                 |               |                     |                    |              |         | (3)                  |

| EECh  |                       |             |             |                 |               |                     |                    |              |         | (3)                  |

| EEBh  |                       |             |             |                 |               |                     |                    |              |         |                      |

| EEAh  | RPINR9                |             |             |                 | ECCP3 Input   |                     | ) to Input Pin M   | apping bits  | _       | (3)                  |

| EE9h  | RPINR9                |             |             |                 | · · ·         | 1 \                 | / 1                | 11 0         |         |                      |

|       | RPINR0                |             |             |                 |               | · · ·               | ) to Input Pin M   |              |         | 1 1111               |

| EE8h  |                       |             |             |                 |               |                     | ) to Input Pin M   |              | a hita  | 1 1111               |

| EE7h  | RPINR15               |             |             |                 |               |                     | ut (T5CKI) to Inp  |              | 0       | 1 1111               |

| EE6h  | RPINR6                |             |             |                 |               |                     | ut (T3CKI) to Inp  |              |         | 1 1111               |

| EE5h  |                       | _           | _           | _               |               |                     |                    |              | a hita  | (3)                  |

| EE4h  | RPINR4                | _           | _           | _               | -             |                     | ut (TOCKI) to Inp  |              | y bits  | 1 1111               |

| EE3h  | RPINR3                | _           | _           | _               |               | 1 ( )               | Input Pin Map      | 0            |         | 1 1111               |

| EE2h  | RPINR2                | _           | —           | _               | -             |                     | Input Pin Map      |              |         | 1 1111               |

| EE1h  | RPINR1                | _           | —           | _               |               | παρτ (IN I 1) to    | Input Pin Map      |              |         | 1 1111               |

| EE0h  | _                     | _           | _           | _               | _             | —                   | _                  | _            | _       | (3)                  |

| EDFh  | -                     | _           | _           |                 |               | —                   | -                  |              | -       | (3)                  |

| EDEh  | _                     | _           | _           |                 |               | _                   |                    |              |         | (3)                  |

| EDDh  | _                     | _           | _           | _               |               | _                   |                    |              | -       | (3)                  |

| EDCh  | _                     | _           | —           |                 | -             | —                   | _                  |              |         | (3)                  |

| EDBh  |                       | —           | —           |                 | —             | —                   |                    |              |         | (3)                  |

| EDAh  |                       | _           | —           | —               | _             | —                   | -                  | —            | -       | (3)                  |

| ED9h  |                       | _           | —           | —               | —             | —                   | -                  | —            | -       | (3)                  |

| ED8h  | RPOR24 <sup>(2)</sup> | —           | —           | -               | Remappable    | Pin RP24 Ou         | tput Signal Sele   | ect bits     |         | 0 0000               |

| ED7h  | RPOR23 <sup>(2)</sup> | —           | —           | —               | Remappable    | Pin RP23 Ou         | tput Signal Sele   | ect bits     |         | 0 0000               |

Note 1: Applicable for 28-pin devices (PIC18F26J13, PIC18F27J13, PIC18LF26J13 and PIC18LF27J13).

2: Applicable for 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

3: Value on POR, BOR.

| REGISTER 9                                                                                                                                                                         | )-7: PIR4: | PERIPHERA      | L INTERRUP | T REQUEST                               | (FLAG) REG       | ISTER 4 (AC | CESS F8Fh) |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------|------------|-----------------------------------------|------------------|-------------|------------|--|

| R/W-0                                                                                                                                                                              | R/W-0      | R/W-0          | R/W-0      | R/W-0                                   | R/W-0            | R/W-0       | R/W-0      |  |

| CCP10IF                                                                                                                                                                            | CCP9IF     | CCP8IF         | CCP7IF     | CCP6IF                                  | CCP5IF           | CCP4IF      | CCP3IF     |  |

| bit 7                                                                                                                                                                              |            |                |            |                                         |                  |             | bit 0      |  |

|                                                                                                                                                                                    |            |                |            |                                         |                  |             |            |  |

| Legend:                                                                                                                                                                            |            |                |            |                                         |                  |             |            |  |

| R = Readable                                                                                                                                                                       | bit        | W = Writable I | oit        | U = Unimplem                            | nented bit, read | d as '0'    |            |  |

| -n = Value at POR '1' = Bit is set                                                                                                                                                 |            |                |            | '0' = Bit is cleared x = Bit is unknown |                  |             |            |  |

| bit 7-1 CCP10IF:CCP4IF: CCP<10:4> Interrupt Flag bits<br>Capture Mode<br>1 = A TMR register capture occurred (must be cleared in software)<br>0 = No TMR register capture occurred |            |                |            |                                         |                  |             |            |  |

### Compare Mode

1 = A TMR register compare match occurred (must be cleared in software)

0 = No TMR register compare match occurred

PWM Mode

Unused in this mode.

### CCP3IF: ECCP3 Interrupt Flag bit

#### Capture Mode

bit 0

1 = A TMR register capture occurred (must be cleared in software)

0 = No TMR register capture occurred

### Compare Mode

1 = A TMR register compare match occurred (must be cleared in software)

0 = No TMR register compare match occurred

#### PWM Mode

Unused in this mode.

| TABLE 10-5:                            | PORTB I             |                 | IARY | (CONTINUED)                |                                                                                                                          |  |  |  |

|----------------------------------------|---------------------|-----------------|------|----------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin                                    | Function            | TRIS<br>Setting | I/O  | l/O<br>Type                | Description                                                                                                              |  |  |  |

| RB4/CCP4/                              | RB4                 | 0               | 0    | DIG                        | LATB<4> data output; not affected by an analog input.                                                                    |  |  |  |

| PMA1/KBI0/<br>SCL2 <sup>(4)</sup> /RP7 |                     | 1               | I    | TTL                        | PORTB<4> data input; weak pull-up when the RBPU bit is cleared. Disabled when an analog input is enabled. <sup>(1)</sup> |  |  |  |

|                                        | CCP4 <sup>(3)</sup> | 1               | Ι    | ST                         | Capture input.                                                                                                           |  |  |  |

|                                        |                     | 0               | 0    | DIG                        | Compare/PWM output.                                                                                                      |  |  |  |

|                                        | PMA1                | х               | I/O  | ST/TTL/<br>DIG             | i                                                                                                                        |  |  |  |

|                                        | KBI0                | 1               |      | TTL                        | Interrupt-on-change pin.                                                                                                 |  |  |  |

|                                        | SCL2 <sup>(4)</sup> | 1               | I    | l <sup>2</sup> C/<br>SMBus | I <sup>2</sup> C clock input (MSSP2 module).                                                                             |  |  |  |

|                                        | RP7                 | 1               |      | ST                         | Remappable Peripheral Pin 7 input.                                                                                       |  |  |  |

|                                        |                     | 0               | 0    | DIG                        | Remappable Peripheral Pin 7 output.                                                                                      |  |  |  |

| RB5/CCP5/                              | RB5                 | 0               | 0    | DIG                        | LATB<5> data output.                                                                                                     |  |  |  |

| PMA0/KBI1/<br>SDA2 <sup>(4)</sup> /RP8 |                     | 1               | Ι    | TTL                        | PORTB<5> data input; weak pull-up when the $\overline{\text{RBPU}}$ bit is cleared.                                      |  |  |  |

|                                        | CCP5 <sup>(3)</sup> | 1               | I    | ST                         | Capture input.                                                                                                           |  |  |  |

|                                        |                     | 0               | 0    | DIG                        | Compare/PWM output.                                                                                                      |  |  |  |

|                                        | PMA0 <sup>(3)</sup> | х               | I/O  | ST/TTL/<br>DIG             | Parallel Master Port address.                                                                                            |  |  |  |

|                                        | KBI1                | 1               | Ι    | TTL                        | Interrupt-on-change pin.                                                                                                 |  |  |  |

|                                        | SDA2 <sup>(4)</sup> | 1               | I    | l <sup>2</sup> C/<br>SMBus | I <sup>2</sup> C data input (MSSP2 module).                                                                              |  |  |  |

|                                        | RP8                 | 1               |      | ST                         | Remappable Peripheral Pin 8 input.                                                                                       |  |  |  |

|                                        |                     | 0               | 0    | DIG                        | Remappable Peripheral Pin 8 output.                                                                                      |  |  |  |

| RB6/CCP6/                              | RB6                 | 0               | 0    | DIG                        | LATB<6> data output.                                                                                                     |  |  |  |

| KBI2/PGC/RP9                           |                     | 1               | I    | TTL                        | PORTB<6> data input; weak pull-up when the RBPU bit is cleared.                                                          |  |  |  |

|                                        | CCP6 <sup>(3)</sup> | 1               | I    | ST                         | Capture input.                                                                                                           |  |  |  |

|                                        |                     | 0               | 0    | DIG                        | Compare/PWM output.                                                                                                      |  |  |  |

|                                        | KBI2                | 1               | Ι    | TTL                        | Interrupt-on-change pin.                                                                                                 |  |  |  |

|                                        | PGC                 | х               | I    | ST                         | Serial execution (ICSP™) clock input for ICSP and ICD operation. <sup>(2)</sup>                                          |  |  |  |

|                                        | RP9                 | 1               | Ι    | ST                         | Remappable Peripheral Pin 9 input.                                                                                       |  |  |  |

|                                        |                     | 0               | 0    | DIG                        | Remappable Peripheral Pin 9 output.                                                                                      |  |  |  |

DODTO UO CUMMA DV (CONTINUED) DI E 40 E.

Legend: DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRISx bit does not affect port direction or is overridden for this option)

Note 1: Pins are configured as analog inputs by default on POR. Using these pins for digital inputs requires setting the appropriate bits in the ANCON1 register.

- 2: All other pin functions are disabled when ICSP<sup>™</sup> or ICD is enabled.

- 3: Only on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

- 4: Only on 28-pin devices (PIC18F26J13, PIC18F27J13, PIC18LF26J13 and PIC18LF27J13).

| TABLE 10-7: PORTC I/O SUMMARY (CONTINUED) |                     |                 |     |                |                                                                                                                               |

|-------------------------------------------|---------------------|-----------------|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------|

| Pin                                       | Function            | TRIS<br>Setting | I/O | I/O<br>Type    | Description                                                                                                                   |

| RC5/SDO1/                                 | RC5                 | 0               | 0   | DIG            | PORTC<5> data output.                                                                                                         |

| RP16                                      | SDO1                | х               | 0   | DIG            | SPI data output (MSSP1 module).                                                                                               |

|                                           | RP16                | 1               | I   | ST             | Remappable Peripheral Pin 16 input.                                                                                           |

|                                           |                     | 0               | 0   | DIG            | Remappable Peripheral Pin 16 output.                                                                                          |

| RC6/CCP9/                                 | RC6                 | 1               | I   | ST             | PORTC<6> data input.                                                                                                          |

| PMA5/TX1/                                 |                     | 0               | 0   | DIG            | LATC<6> data output.                                                                                                          |

| CK1/RP17                                  | CCP9                | 1               | I   | ST             | Capture input.                                                                                                                |

|                                           |                     | 0               | 0   | DIG            | Compare/PWM output.                                                                                                           |

|                                           | PMA5 <sup>(1)</sup> | 1               | Ι   | ST/TTL         | Parallel Master Port io_addr_in<5>.                                                                                           |

|                                           |                     | 0               | 0   | DIG            | Parallel Master Port address.                                                                                                 |

|                                           | TX1                 | 0               | 0   | DIG            | Asynchronous serial transmit data output (EUSART module);<br>takes priority over port data. User must configure as an output. |

|                                           | CK1                 | 1               | Ι   | ST             | Synchronous serial clock input (EUSART module).                                                                               |

|                                           |                     | 0               | 0   | DIG            | Synchronous serial clock output (EUSART module); takes priority over port data.                                               |

|                                           | RP17                | 1               | Ι   | ST             | Remappable Peripheral Pin 17 input.                                                                                           |

|                                           |                     | 0               | 0   | DIG            | Remappable Peripheral Pin 17 output.                                                                                          |

| RC7/CCP10/                                | RC7                 | 1               | Ι   | ST             | PORTC<7> data input.                                                                                                          |

| PMA4/RX1/                                 |                     | 0               | 0   | DIG            | LATC<7> data output.                                                                                                          |

| DT1/RP18                                  | CCP10               | 1               | Ι   | ST             | Capture input.                                                                                                                |

|                                           |                     | 0               | 0   | DIG            | Compare/PWM output.                                                                                                           |

|                                           | PMA4 <sup>(1)</sup> | х               | I/O | ST/TTL/<br>DIG | Parallel Master Port address.                                                                                                 |

|                                           | RX1                 | 1               | I   | ST             | Asynchronous serial receive data input (EUSART module).                                                                       |

|                                           | DT1                 | 1               | 1   | ST             | Synchronous serial data input (EUSART module). User must configure as an input.                                               |

|                                           |                     | 0               | 0   | DIG            | Synchronous serial data output (EUSART module); takes priority over port data.                                                |

|                                           | RP18                | 1               | I   | ST             | Remappable Peripheral Pin 18 input.                                                                                           |

|                                           |                     | 0               | 0   | DIG            | Remappable Peripheral Pin 18 output.                                                                                          |

|                                           |                     |                 |     |                |                                                                                                                               |

|  | <b>TABLE 10-7:</b> | PORTC I/O SUM | MARY (CONTINUED) |

|--|--------------------|---------------|------------------|

|--|--------------------|---------------|------------------|

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; I<sup>2</sup>C/SMB = I<sup>2</sup>C/SMBus input buffer; x = Don't care (TRISx bit does not affect port direction or is overridden for this option)

**Note 1:** This bit is only available on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

### TABLE 10-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name   | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   |

|--------|--------|--------|---------|---------|---------|--------|---------|---------|

| PORTC  | RC7    | RC6    | RC5     | RC4     | RC3     | RC2    | RC1     | RC0     |

| LATC   | LATC7  | LATC6  | LATC5   | LATC4   | LATC3   | LATC2  | LATC1   | LATC0   |

| TRISC  | TRISC7 | TRISC6 | TRISC5  | TRISC4  | TRISC3  | TRISC2 | TRISC1  | TRISC0  |

| ANCON1 | VBGEN  | —      | —       | PCFG12  | PCFG11  | PCFG10 | PCFG9   | PCFG8   |

| CM2CON | CON    | COE    | CPOL    | EVPOL1  | EVPOL0  | CREF   | CCH1    | CCH0    |

| RTCCFG | RTCEN  |        | RTCWREN | RTCSYNC | HALFSEC | RTCOE  | RTCPTR1 | RTCPTR0 |

$\ensuremath{\textcircled{}^\circ}$  2010-2017 Microchip Technology Inc.

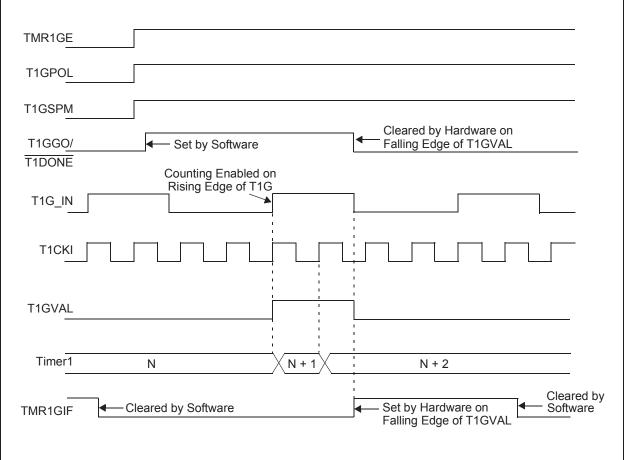

### 13.8.4 TIMER1 GATE SINGLE PULSE MODE

When Timer1 Gate Single Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/T1DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/T1DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/T1DONE bit is once again set in software.

Clearing the T1GSPM <u>bit of the T1GCON</u> register will also clear the T1GGO/T1DONE bit. See Figure 13-6 for timing details.

Enabling the Toggle mode and the Single Pulse mode, simultaneously, will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 13-7 for timing details.

### 13.8.5 TIMER1 GATE VALUE STATUS

When the Timer1 gate value status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

# FIGURE 13-6: TIMER1 GATE SINGLE PULSE MODE

# 16.0 TIMER4/6/8 MODULE

The Timer4/6/8 timer modules have the following features:

- Eight-bit Timer register (TMRx)

- Eight-bit Period register (PRx)

- Readable and writable (all registers)

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

- Interrupt on TMRx match of PRx

| Note: | Throughout this section, generic references      |

|-------|--------------------------------------------------|

|       | are used for register and bit names that are the |

|       | same - except for an 'x' variable that indicates |

|       | the item's association with the Timer4, Timer6   |

|       | or Timer8 module. For example, the control       |

|       | register is named TxCON and refers to            |

|       | T4CON, T6CON and T8CON.                          |

The Timer4/6/8 modules have a control register shown in Register 16-1. Timer4/6/8 can be shut off by clearing control bit, TMRxON (TxCON<2>), to minimize power consumption. The prescaler and postscaler selection of Timer4/6/8 is also controlled by this register. Figure 16-1 is a simplified block diagram of the Timer4/6/8 modules.

### 16.1 Timer4/6/8 Operation

Timer4/6/8 can be used as the PWM time base for the PWM mode of the ECCP modules. The TMRx registers are readable and writable, and are cleared on any device Reset. The input clock (Fosc/4) has a prescale option of 1:1, 1:4 or 1:16, selected by control bits, TxCKPS<1:0> (TxCON<1:0>). The match output of TMRx goes through a four-bit postscaler (that gives a

1:1 to 1:16 inclusive scaling) to generate a TMRx interrupt, latched in the flag bit, TMRxIF. Table 16-1 gives each module's flag bit.

### TABLE 16-1: TIMER4/6/8 FLAG BITS

| Timer Module | Flag Bit |

|--------------|----------|

| 4            | PIR3<3>  |

| 6            | PIR5<3>  |

| 8            | PIR5<4>  |

The interrupt can be enabled or disabled by setting or clearing the Timerx Interrupt Enable bit (TMRxIE), shown in Table 16-2.

### TABLE 16-2: TIMER4/6/8 INTERRUPT ENABLE BITS

| Timer Module | Flag Bit |

|--------------|----------|

| 4            | PIE3<3>  |

| 6            | PIE5<3>  |

| 8            | PIE5<4>  |

The prescaler and postscaler counters are cleared when any of the following occurs:

- A write to the TMRx register

- A write to the TxCON register

- Any device Reset (Power-on Reset (POR), MCLR Reset, Watchdog Timer Reset (WDTR) or Brown-out Reset (BOR))

A TMRx is not cleared when a TxCON is written.

Note: The CCP and ECCP modules use Timers, 1 through 8, for some modes. The assignment of a particular timer to a CCP/ECCP module is determined by the Timer to CCP enable bits in the CCPTMRSx registers. For more details, see Register 18-2, Register 18-3 and Register 19-2.

# TABLE 17-3:RTCVALH AND RTCVALLREGISTER MAPPING

| RTCPTR<1:0> | RTCC Value Register Windo |             |  |  |

|-------------|---------------------------|-------------|--|--|

| RICPIRSI.02 | RTCVAL<15:8>              | RTCVAL<7:0> |  |  |

| 00          | MINUTES                   | SECONDS     |  |  |

| 01          | WEEKDAY                   | HOURS       |  |  |

| 10          | MONTH                     | DAY         |  |  |

| 11          | —                         | YEAR        |  |  |

The Alarm Value register window (ALRMVALH and ALRMVALL) uses the ALRMPTR bits (ALRMCFG<1:0>) to select the desired Alarm register pair.

By reading or writing to the ALRMVALH register, the Alarm Pointer value, ALRMPTR<1:0>, decrements by 1 until it reaches '00'. Once it reaches '00', the ALRMMIN and ALRMSEC value will be accessible through ALRMVALH and ALRMVALL until the pointer value is manually changed.

TABLE 17-4: ALRMVAL REGISTER

| MAPPING        |                |               |  |  |

|----------------|----------------|---------------|--|--|

| ALRMPTR<1:0>   | Alarm Value Re | gister Window |  |  |

| ALRIVIPTRS1.02 | ALRMVAL<15:8>  | ALRMVAL<7:0>  |  |  |

| 00             | ALRMMIN        | ALRMSEC       |  |  |

| 01             | ALRMWD         | ALRMHR        |  |  |

| 10             | ALRMMNTH       | ALRMDAY       |  |  |

| 11             |                |               |  |  |

# 17.2.9 CALIBRATION

The real-time crystal input can be calibrated using the periodic auto-adjust feature. When properly calibrated, the RTCC can provide an error of less than three seconds per month.

To perform this calibration, find the number of error clock pulses and store the value in the lower half of the RTCCAL register. The 8-bit, signed value, loaded into RTCCAL, is multiplied by four and will either be added or subtracted from the RTCC timer, once every minute.

To calibrate the RTCC module:

- 1. Use another timer resource on the device to find the error of the 32.768 kHz crystal.

- 2. Convert the number of error clock pulses per minute (see Equation 17-1).

## EQUATION 17-1: CONVERTING ERROR CLOCK PULSES

(Ideal Frequency (32,768) – Measured Frequency) \* 60 = Error Clocks per Minute

- If the oscillator is *faster* than ideal (negative result from Step 2), the RTCCFG register value needs to be negative. This causes the specified number of clock pulses to be subtracted from the timer counter, once every minute.

- If the oscillator is *slower* than ideal (positive result from Step 2), the RTCCFG register value needs to be positive. This causes the specified number of clock pulses to be added to the timer counter, once every minute.

- 3. Load the RTCCAL register with the correct value.

Writes to the RTCCAL register should occur only when the timer is turned off, or immediately after the rising edge of the seconds pulse.

**Note:** In determining the crystal's error value, it is the user's responsibility to include the crystal's initial error from drift due to temperature or crystal aging.

### 20.3.1 REGISTERS

Each MSSP module has four registers for SPI mode operation. These are:

- MSSPx Control Register 1 (SSPxCON1)

- MSSPx Status Register (SSPxSTAT)

- Serial Receive/Transmit Buffer Register (SSPxBUF)

- MSSPx Shift Register (SSPxSR) Not directly accessible

SSPxCON1 and SSPxSTAT are the control and status registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

SSPxSR is the shift register used for shifting data in or out. SSPxBUF is the buffer register to which data bytes are written to or read from. In receive operations, SSPxSR and SSPxBUF together, create a double-buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not double-buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

Note: Because the SSPxBUF register is double-buffered, using read-modify-write instructions such as BCF, COMF, etc., will not work.

Similarly, when debugging under an in-circuit debugger, performing actions that cause reads of SSPxBUF (mouse hovering, watch, etc.) can consume data that the application code was expecting to receive.

### REGISTER 20-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE) (ACCESS 1, FC7h; 2, F73h)

| R/W-1 | R/W-1              | R-1 | R-1 | R-1 | R-1 | R-1 | R-1   |

|-------|--------------------|-----|-----|-----|-----|-----|-------|

| SMP   | CKE <sup>(1)</sup> | D/Ā | Р   | S   | R/W | UA  | BF    |

| bit 7 |                    |     |     |     |     |     | bit 0 |

Legend:

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | SMP: Sample bit                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------|

|       | SPI Master mode:                                                                                            |

|       | 1 = Input data sampled at the end of data output time                                                       |

|       | 0 = Input data sampled at the middle of data output time                                                    |

|       | SPI Slave mode:                                                                                             |

|       | SMP must be cleared when SPI is used in Slave mode.                                                         |

| bit 6 | CKE: SPI Clock Select bit <sup>(1)</sup>                                                                    |

|       | 1 = Transmit occurs on transition from active to Idle clock state                                           |

|       | 0 = Transmit occurs on transition from Idle to active clock state                                           |

| bit 5 | D/A: Data/Address bit                                                                                       |

|       | Used in I <sup>2</sup> C mode only.                                                                         |

| bit 4 | P: Stop bit                                                                                                 |

|       | Used in I <sup>2</sup> C mode only; this bit is cleared when the MSSP module is disabled, SSPEN is cleared. |

| bit 3 | S: Start bit                                                                                                |

|       | Used in I <sup>2</sup> C mode only.                                                                         |

| bit 2 | R/W: Read/Write Information bit                                                                             |

|       | Used in I <sup>2</sup> C mode only.                                                                         |

| bit 1 | UA: Update Address bit                                                                                      |

|       | Used in I <sup>2</sup> C mode only.                                                                         |

| bit 0 | BF: Buffer Full Status bit                                                                                  |

|       | 1 = Receive complete, SSPxBUF is full                                                                       |

|       | 0 = Receive not complete, SSPxBUF is empty                                                                  |

|       |                                                                                                             |

Note 1: Polarity of the clock state is set by the CKP bit (SSPxCON1<4>).

# 23.5 Comparator Control and Configuration

Each comparator has up to eight possible combinations of inputs: up to four external analog inputs and one of two internal voltage references.

Both comparators allow a selection of the signal from pin, CxINA, or the voltage from the comparator reference (CVREF) on the non-inverting channel. This is compared to either CxINB, CxINC, CxIND, CTMU or the microcontroller's fixed internal reference voltage (VIRV, 0.6V nominal) on the inverting channel.

Table 23-1 provides the comparator inputs and outputs tied to fixed I/O pins.

| Comparator | Input or Output | I/O Pin         |

|------------|-----------------|-----------------|

|            | C1INA (VIN+)    | RA0             |

|            | C1INB (VIN-)    | RA3             |

| 1          | C1INC (VIN-)    | RA5             |

|            | C1IND (VIN-)    | RA2             |

|            | C1OUT           | Remapped<br>RPn |

|            | C2INA(VIN+)     | RA1             |

|            | C2INB(VIN-)     | RA2             |

| 2          | C2INC (VIN-)    | RB2             |

| 2          | C2IND (VIN-)    | RC2             |

|            | C2OUT           | Remapped<br>RPn |

|            | C3INA(VIN+)     | RB3             |

|            | C3INB(VIN-)     | RA2             |

| 3          | C3INC (VIN-)    | RB1             |

| 5          | C3IND (VIN-)    | RB0             |

|            | C3OUT           | Remapped<br>RPn |

### TABLE 23-1: COMPARATOR INPUTS AND OUTPUTS

# 23.5.1 COMPARATOR ENABLE AND INPUT SELECTION

Setting the CON bit of the CMxCON register (CMxCON<7>) enables the comparator for operation. Clearing the CON bit disables the comparator, minimizing current consumption.

The CCH<1:0> bits in the CMxCON register (CMxCON<1:0>) direct either one of three analog input pins, or the Internal Reference Voltage (VIRV), to the comparator, VIN-. Depending on the comparator operating mode, either an external or internal voltage reference may be used. The analog signal present at VIN- is compared to the signal at VIN+ and the digital output of the comparator is adjusted accordingly.

The external reference is used when CREF = 0 (CMxCON<2>) and VIN+ is connected to the CxINA pin. When external voltage references are used, the comparator module can be configured to have the reference sources externally. The reference signal must be between VSS and VDD, and can be applied to either pin of the comparator.

The comparator module also allows the selection of an internally generated voltage reference (CVREF) from the comparator voltage reference module. This module is described in more detail in Section 23.0 "Comparator Module". The reference from the comparator voltage reference module is only available when CREF = 1. In this mode, the internal voltage reference is applied to the comparator's VIN+ pin.

| Note: | The comparator input pin selected by        |

|-------|---------------------------------------------|

|       | CCH<1:0> must be configured as an input     |

|       | by setting both the corresponding TRIS bits |

|       | and PCFG bits in the ANCON1 register.       |

### 23.5.2 COMPARATOR ENABLE AND OUTPUT SELECTION

The comparator outputs are read through the CMSTAT register. The CMSTAT<0> reads the Comparator 1 output, CMSTAT<1> reads the Comparator 2 output and CMSTAT<2> reads the Comparator 3 output. These bits are read-only.

The comparator outputs may also be directly output to the RPn I/O pins by setting the COE bit (CMxCON<6>). When enabled, multiplexers in the output path of the pins switch to the output of the comparator.

By default, the comparator's output is at logic high whenever the voltage on VIN+ is greater than on VIN-. The polarity of the comparator outputs can be inverted using the CPOL bit (CMxCON<5>).

The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications, as discussed in **Section 23.2 "Comparator Operation"**.

# REGISTER 26-2: CTMUCONL: CTMU CONTROL REGISTER LOW (ACCESS FB2h)

| R/W-0         | R/W-0                    | R/W-0                 | R/W-0           | R/W-0             | R/W-0            | R/W-x           | R/W-x    |

|---------------|--------------------------|-----------------------|-----------------|-------------------|------------------|-----------------|----------|

| EDG2POL       | EDG2SEL1                 | EDG2SEL0              | EDG1POL         | EDG1SEL1          | EDG1SEL0         | EDG2STAT        | EDG1STAT |

| bit 7         | -                        | •                     |                 | •                 |                  | •               | bit 0    |

|               |                          |                       |                 |                   |                  |                 |          |

| Legend:       |                          |                       |                 |                   |                  |                 |          |

| R = Readable  | e bit                    | W = Writable I        | oit             | U = Unimplem      | nented bit, read | l as '0'        |          |

| -n = Value at | POR                      | '1' = Bit is set      |                 | '0' = Bit is clea | ared             | x = Bit is unkr | nown     |

|               |                          |                       |                 |                   |                  |                 |          |

| bit 7         | EDG2POL: E               | dge 2 Polarity        | Select bit      |                   |                  |                 |          |

|               |                          | s programmed f        |                 |                   |                  |                 |          |

|               | -                        | s programmed f        | -               | -                 |                  |                 |          |

| bit 6-5       |                          | :0>: Edge 2 So        | urce Select bit | S                 |                  |                 |          |

|               | 11 = CTED1<br>10 = CTED2 | •                     |                 |                   |                  |                 |          |

|               |                          | output compare        | e module        |                   |                  |                 |          |

|               | 00 = Timer1 r            |                       |                 |                   |                  |                 |          |

| bit 4         | EDG1POL: E               | dge 1 Polarity        | Select bit      |                   |                  |                 |          |

|               | •                        | s programmed f        |                 | •                 |                  |                 |          |

|               | 0 = Edge 1 is            | s programmed f        | or a negative e | edge response     |                  |                 |          |

| bit 3-2       | EDG1SEL<1:               | :0>: Edge 1 So        | urce Select bit | S                 |                  |                 |          |

|               | 11 = CTED1               |                       |                 |                   |                  |                 |          |

|               | 10 = CTED2               | pın<br>output compare | module          |                   |                  |                 |          |

|               | 01 = ECCF1               |                       | module          |                   |                  |                 |          |

| bit 1         | EDG2STAT:                | Edge 2 Status b       | it              |                   |                  |                 |          |

|               |                          | vent has occur        |                 |                   |                  |                 |          |

|               |                          | vent has not oc       |                 |                   |                  |                 |          |

| bit 0         | EDG1STAT: E              | Edge 1 Status b       | it              |                   |                  |                 |          |

|               |                          | vent has occurr       |                 |                   |                  |                 |          |

|               | 0 = Edge 1 e             | vent has not oc       | curred          |                   |                  |                 |          |

# 27.5.2 EXITING FAIL-SAFE OPERATION

The Fail-Safe Clock Monitor condition is terminated by either a device Reset or by entering a power-managed mode. On Reset, the controller starts the primary clock source specified in Configuration Register 2H (with any required start-up delays that are required for the oscillator mode, such as the OST or PLL timer). The INTRC oscillator provides the device clock until the primary clock source becomes ready (similar to a Two-Speed Start-up). The clock source is then switched to the primary clock (indicated by the OSTS bit in the OSCCON register becoming set). The FSCM then resumes monitoring the peripheral clock.

The primary clock source may never become ready during start-up. In this case, operation is clocked by the INTRC oscillator. The OSCCON register will remain in its Reset state until a power-managed mode is entered.

### 27.5.3 FSCM INTERRUPTS IN POWER-MANAGED MODES

By entering a power-managed mode, the clock multiplexer selects the clock source selected by the OSCCON register. FSCM of the power-managed clock source resumes in the power-managed mode.

If an oscillator failure occurs during power-managed operation, the subsequent events depend on whether or not the oscillator failure interrupt is enabled. If enabled (OSCFIF = 1), code execution will be clocked by the INTRC multiplexer. An automatic transition back to the failed clock source will not occur.

If the interrupt is disabled, subsequent interrupts while in Idle mode will cause the CPU to begin executing instructions while being clocked by the INTRC source.

### 27.5.4 POR OR WAKE-UP FROM SLEEP

The FSCM is designed to detect oscillator failure at any point after the device has exited Power-on Reset (POR) or low-power Sleep mode. When the primary device clock is either the EC or INTRC modes, monitoring can begin immediately following these events.

For HS or HSPLL modes, the situation is somewhat different. Since the oscillator may require a start-up time considerably longer than the FSCM sample clock time, a false clock failure may be detected. To prevent this, the internal oscillator block is automatically configured as the device clock and functions until the primary clock is stable (the OST and PLL timers have timed out). This is identical to Two-Speed Start-up mode. Once the primary clock is stable, the INTRC returns to its role as the FSCM source.

Note: The same logic that prevents false oscillator failure interrupts on POR, or wake-up from Sleep, will also prevent the detection of the oscillator's failure to start at all following these events. This can be avoided by monitoring the OSTS bit and using a timing routine to determine if the oscillator is taking too long to start. Even so, no oscillator failure interrupt will be flagged.

As noted in Section 27.4.1 "Special Considerations For Using Two-speed Start-up", it is also possible to select another clock configuration and enter an alternate power-managed mode while waiting for the primary clock to become stable. When the new power-managed mode is selected, the primary clock is disabled.

# 27.6 Program Verification and Code Protection

For all devices in the PIC18F47J13 Family of devices, the on-chip program memory space is treated as a single block. Code protection for this block is controlled by one Configuration bit, CP0. This bit inhibits external reads and writes to the program memory space. It has no direct effect in normal execution mode.

### 27.6.1 CONFIGURATION REGISTER PROTECTION

The Configuration registers are protected against untoward changes or reads in two ways. The primary protection is the write-once feature of the Configuration bits, which prevents reconfiguration once the bit has been programmed during a power cycle. To safeguard against unpredictable events, Configuration bit changes resulting from individual cell level disruptions (such as ESD events) will cause a parity error and trigger a device Reset. This is seen by the user as a Configuration Mismatch (CM) Reset.

The data for the Configuration registers is derived from the FCW in program memory. When the CP0 bit is set, the source data for device configuration is also protected as a consequence.

# PIC18F47J13 FAMILY

| MOVFF                                                                       | Move f to f                               | :                                                                |                                          | MOVLB            | Move Liter          | al to Low Ni                                      | bble in BSR                 |

|-----------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------|------------------------------------------|------------------|---------------------|---------------------------------------------------|-----------------------------|

| Syntax:                                                                     | MOVFF f <sub>s</sub>                      | ,f <sub>d</sub>                                                  |                                          | Syntax:          | MOVLW k             | ,                                                 |                             |

| Operands:                                                                   | $0 \le f_s \le 409$                       |                                                                  |                                          | Operands:        | $0 \le k \le 255$   |                                                   |                             |

|                                                                             | $0 \le f_d \le 409$                       | 95                                                               |                                          | Operation:       | $k \to BSR$         |                                                   |                             |

| Operation:                                                                  | $(f_s) \to f_d$                           |                                                                  |                                          | Status Affected: | None                |                                                   |                             |

| Status Affected:                                                            | None                                      |                                                                  |                                          | Encoding:        | 0000                | 0000 0001 kkkk kk                                 |                             |

| Encoding:<br>1st word (source)<br>2nd word (destin.)                        | 1100<br>1111                              | ffff ff:<br>ffff ff:                                             | 5                                        | Description:     | Bank Selec          | eral 'k' is load<br>t Register (B<br>> always rem | SR). The value              |

| Description:                                                                |                                           | ts of source re                                                  |                                          |                  |                     | of the value of                                   |                             |

|                                                                             |                                           | estination regi                                                  | ster 'f <sub>d</sub> '.<br>i be anywhere | Words:           | 1                   |                                                   |                             |

|                                                                             |                                           | -byte data spa                                                   |                                          | Cycles:          | 1                   |                                                   |                             |

|                                                                             |                                           | location of des                                                  |                                          | Q Cycle Activity | :                   |                                                   |                             |

|                                                                             | can also be<br>FFFh.                      | anywhere fro                                                     | m uuun to                                | Q1               | Q2                  | Q3                                                | Q4                          |

|                                                                             | Either sour                               | ce or destinati                                                  | on can be W                              | Decode           | Read<br>literal 'k' | Process<br>Data                                   | Write literal<br>'k' to BSR |

|                                                                             |                                           | ecial situation                                                  |                                          |                  | interar k           | Data                                              | K to DOIN                   |

|                                                                             | peripheral r<br>buffer or an<br>The MOVFF | egister (such a<br>I/O port).<br>instruction ca<br>J, TOSH or TC |                                          | After Instruc    | egister = 02        |                                                   |                             |

| Words:                                                                      | 2                                         |                                                                  |                                          |                  |                     |                                                   |                             |

| Cycles:                                                                     | 2                                         |                                                                  |                                          |                  |                     |                                                   |                             |

| Q Cycle Activity:                                                           |                                           |                                                                  |                                          |                  |                     |                                                   |                             |

| Q1                                                                          | Q2                                        | Q3                                                               | Q4                                       |                  |                     |                                                   |                             |

| Decode                                                                      | Read<br>register 'f'<br>(src)             | Process<br>Data                                                  | No<br>operation                          |                  |                     |                                                   |                             |

| Decode                                                                      | No<br>operation<br>No dummy<br>read       | No<br>operation                                                  | Write<br>register 'f'<br>(dest)          |                  |                     |                                                   |                             |

| Example:<br>Before Instru<br>REG1<br>REG2<br>After Instruct<br>REG1<br>REG2 | ction<br>= 33<br>= 11                     | h                                                                |                                          |                  |                     |                                                   |                             |

# PIC18F47J13 FAMILY