Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 13x10b/12b                                                             |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-VQFN Exposed Pad                                                        |

| Supplier Device Package    | 44-QFN (8x8)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f46j13-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

PIC18F26J13

PIC18F26J13

PIC18F27J13

PIC18F46J13

PIC18F46J13

PIC18F47J13

PIC18LF47J13

#### 1.1 Core Features

#### 1.1.1 XLP TECHNOLOGY

All of the devices in the PIC18F47J13 Family incorporate a range of features that can significantly reduce power consumption during operation. Key features are:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal RC oscillator, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller can also run

with its CPU core disabled but the peripherals still

active. In these states, power consumption can be

reduced even further, to as little as 4% of normal

operational requirements.

- On-the-Fly Mode Switching: The power-managed modes are invoked by user code during operation, allowing the users to incorporate power-saving ideas into their application's software design.

- Deep Sleep: The 2.5V internal core voltage regulator on F parts can be shutdown to cut power consumption to as low as 15 nA (typical). Certain features can remain operating during Deep Sleep, such as the Real-Time Clock Calendar.

- Ultra Low Power Wake-Up: Waking from Sleep or Deep Sleep modes after a period of time can be done without an oscillator/clock source, saving power for applications requiring periodic activity.

# 1.1.2 OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F47J13 Family offer five different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes, using crystals or ceramic resonators.

- Two External Clock modes, offering the option of a divide-by-4 clock output.

- An internal oscillator block, which provides an 8 MHz clock and an INTRC source (approximately 31 kHz, stable over temperature and VDD), as well as a range of six user selectable clock frequencies, between 125 kHz to 4 MHz, for a total of eight clock frequencies. This option frees an oscillator pin for use as an additional general purpose I/O.

- A Phase Lock Loop (PLL) frequency multiplier available to the high-speed crystal, and external and internal oscillators, providing a clock speed up to 48 MHz.

The internal oscillator block provides a stable reference source that gives the PIC18F47J13 Family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly

monitors the main clock source against a reference

signal provided by the internal oscillator. If a clock

failure occurs, the controller is switched to the

internal oscillator, allowing for continued low-speed

operation or a safe application shutdown.

- Two-Speed Start-up: This option allows the internal oscillator to serve as the clock source from Power-on Reset (POR), or wake-up from Sleep mode, until the primary clock source is available.

#### 4.7 Ultra Low-Power Wake-up

The Ultra Low-Power Wake-up (ULPWU) on RA0 allows a slow falling voltage to generate an interrupt-on-change without excess current consumption.

Follow these steps to use this feature:

- Configure a remappable output pin to output the ULPOUT signal.

- 2. Map an INTx interrupt-on-change input function to the same pin as used for the ULPOUT output function. Alternatively, in Step 1, configure ULPOUT to output onto a PORTB interrupt-on-change pin.

- 3. Charge the capacitor on RA0 by configuring the RA0 pin to an output and setting it to '1'.

- 4. Enable interrupt-on-change (PIE bit) for the corresponding pin selected in Step 2.

- 5. Stop charging the capacitor by configuring RA0 as an input.

- 6. Discharge the capacitor by setting the ULPEN and ULPSINK bits in the WDTCON register.

- 7. Configure Sleep mode.

- 8. Enter Sleep mode.

When the voltage on RA0 drops below VIL, an interrupt will be generated, which will cause the device to wake-up and execute the next instruction.

This feature provides a low-power technique for periodically waking up the device from Sleep mode. The time-out is dependent on the discharge time of the RC circuit on RA0.

When the ULPWU module causes the device to wake-up from Sleep mode, the ULPLVL (WDTCON<5>) bit is set. When the ULPWU module causes the device to wake-up from Deep Sleep, the DSULP (DSWAKEL<5>) bit is set. Software can check these bits upon wake-up to determine the wake-up source. Also in Sleep mode, only the remappable output function, ULPWU, will output this bit value to an RPn pin for externally detecting wake-up events.

See Example 4-1 for initializing the ULPWU module.

Note: For module related bit definitions, see the WDTCON register in Section 27.2 "Watchdog Timer (WDT)" and the DSWAKEL register (Register 4-6).

x = Bit is unknown

### 9.3 PIE Registers

Legend:

R = Readable bit

The PIE registers contain the individual enable bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Enable registers (PIE1, PIE2, PIE3). When IPEN = 0, the PEIE bit must be set to enable any of these peripheral interrupts.

### REGISTER 9-9: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1 (ACCESS F9Dh)

| R/W-0                | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|-------|-------|--------|--------|--------|--------|

| PMPIE <sup>(1)</sup> | ADIE  | RC1IE | TX1IE | SSP1IE | CCP1IE | TMR2IE | TMR1IE |

| bit 7                |       |       |       |        |        |        | bit 0  |

U = Unimplemented bit, read as '0'

| -n = Value at | POR '1' = Bit is                                                                      | set                                   | '0' = Bit is cleared             |

|---------------|---------------------------------------------------------------------------------------|---------------------------------------|----------------------------------|

| bit 7         | PMPIE: Parallel Master F  1 = Enables the PMP rea  0 = Disables the PMP rea           | d/write interrupt                     | errupt Enable bit <sup>(1)</sup> |

| bit 6         | <b>ADIE:</b> A/D Converter Intel 1 = Enables the A/D inter 0 = Disables the A/D intel | errupt Enable bit<br>rupt             |                                  |

| bit 5         | RC1IE: EUSART1 Receiv<br>1 = Enables the EUSART<br>0 = Disables the EUSART            | 1 receive interrup                    | t                                |

| bit 4         | <b>TX1IE:</b> EUSART1 Transr<br>1 = Enables the EUSART<br>0 = Disables the EUSART     | 1 transmit interrup                   | ot                               |

| bit 3         | <b>SSP1IE:</b> Master Synchro<br>1 = Enables the MSSP1 i<br>0 = Disables the MSSP1    | nterrupt                              | Interrupt Enable bit             |

| bit 2         | <b>CCP1IE:</b> ECCP1 Interrup  1 = Enables the ECCP1 i  0 = Disables the ECCP1        | nterrupt                              |                                  |

| bit 1         | TMR2IE: TMR2 to PR2 M<br>1 = Enables the TMR2 to<br>0 = Disables the TMR2 to          | PR2 match interru                     | upt                              |

| bit 0         | <b>TMR1IE:</b> TMR1 Overflow 1 = Enables the TMR1 ov 0 = Disables the TMR1 or         | Interrupt Enable by verflow interrupt | •                                |

W = Writable bit

Note 1: These bits are unimplemented on 28-pin devices.

TABLE 10-5: PORTB I/O SUMMARY

| Pin                      | Function            | TRIS<br>Setting | I/O | I/O<br>Type | Description                                                                                                              |

|--------------------------|---------------------|-----------------|-----|-------------|--------------------------------------------------------------------------------------------------------------------------|

| RB0/AN12/<br>C3IND/INT0/ | RB0                 | 1               | I   | TTL         | PORTB<0> data input; weak pull-up when the RBPU bit is cleared. Disabled when analog input is enabled. (1)               |

| RP3                      |                     | 0               | 0   | DIG         | LATB<0> data output; not affected by an analog input.                                                                    |

|                          | AN12                | 1               | Ι   | ANA         | A/D Input Channel 12. <sup>(1)</sup>                                                                                     |

|                          | C3IND               | 1               | I   | ANA         | Comparator 3 Input D.                                                                                                    |

|                          | INT0                | 1               | I   | ST          | External Interrupt 0 input.                                                                                              |

|                          | RP3                 | 1               | Ι   | ST          | Remappable Peripheral Pin 3 input.                                                                                       |

|                          |                     | 0               | 0   | DIG         | Remappable Peripheral Pin 3 output.                                                                                      |

| RB1/AN10/<br>C3INC/PMBE/ | RB1                 | 1               | I   | TTL         | PORTB<1> data input; weak pull-up when the RBPU bit is cleared. Disabled when an analog input is enabled. <sup>(1)</sup> |

| RTCC/RP4                 |                     | 0               | 0   | DIG         | LATB<1> data output; not affected by an analog input.                                                                    |

|                          | AN10                | 1               | I   | ANA         | A/D Input Channel 10. <sup>(1)</sup>                                                                                     |

|                          | C3INC               | 1               | I   | ANA         | Comparator 3 Input C.                                                                                                    |

|                          | PMBE <sup>(3)</sup> | Х               | 0   | DIG         | Parallel Master Port byte enable.                                                                                        |

|                          | RTCC                | 0               | 0   | DIG         | Asynchronous serial transmit data output (USART module).                                                                 |

|                          | RP4                 | 1               | I   | ST          | Remappable Peripheral Pin 4 input.                                                                                       |

|                          |                     | 0               | 0   | DIG         | Remappable Peripheral Pin 4 output.                                                                                      |

| RB2/AN8/<br>C2INC/CTED1/ | RB2                 | 1               | I   | TTL         | PORTB<2> data input; weak pull-up when the RBPU bit is cleared. Disabled when an analog input is enabled. (1)            |

| PMA3/REFO/               |                     | 0               | 0   | DIG         | LATB<2> data output; not affected by an analog input.                                                                    |

| RP5                      | AN8                 | 1               | - 1 | ANA         | A/D Input Channel 8. <sup>(1)</sup>                                                                                      |

|                          | C2INC               | 1               | - 1 | ANA         | Comparator 2 Input C.                                                                                                    |

|                          | CTED1               | 1               |     | ST          | CTMU Edge 1 input.                                                                                                       |

|                          | PMA3 <sup>(3)</sup> | X               | 0   | DIG         | Parallel Master Port address.                                                                                            |

|                          | REFO                | 0               | 0   | DIG         | Reference output clock.                                                                                                  |

|                          | RP5                 | 1               | I   | ST          | Remappable Peripheral Pin 5 input.                                                                                       |

|                          |                     | 0               | 0   | DIG         | Remappable Peripheral Pin 5 output.                                                                                      |

| RB3/AN9/                 | RB3                 | 0               | 0   | DIG         | LATB<3> data output; not affected by analog input.                                                                       |

| C3INA/CTED2/<br>PMA2/RP6 |                     | 1               | I   | TTL         | PORTB<3> data input; weak pull-up when the RBPU bit is cleared. Disabled when analog input is enabled. (1)               |

|                          | AN9                 | 1               | I   | ANA         | A/D Input Channel 9. <sup>(1)</sup>                                                                                      |

|                          | C3INA               | 1               | I   | ANA         | Comparator 3 Input A.                                                                                                    |

|                          | CTED2               | 1               | I   | ST          | CTMU Edge 2 input.                                                                                                       |

|                          | PMA2 <sup>(3)</sup> | Х               | 0   | DIG         | Parallel Master Port address.                                                                                            |

|                          | RP6                 | 1               | Ι   | ST          | Remappable Peripheral Pin 6 input.                                                                                       |

|                          |                     | 0               | 0   | DIG         | Remappable Peripheral Pin 6 output.                                                                                      |

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRISx bit does not affect port direction or is overridden for this option)

- **Note 1:** Pins are configured as analog inputs by default on POR. Using these pins for digital inputs requires setting the appropriate bits in the ANCON1 register.

- **2:** All other pin functions are disabled when ICSP™ or ICD is enabled.

- 3: Only on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

- 4: Only on 28-pin devices (PIC18F26J13, PIC18F27J13, PIC18LF26J13 and PIC18LF27J13).

#### 17.1.4 RTCEN BIT WRITE

An attempt to write to the RTCEN bit while RTCWREN = 0 will be ignored. RTCWREN must be set before a write to RTCEN can take place.

Like the RTCEN bit, the RTCVALH and RTCVALL registers can only be written to when RTCWREN = 1. A write to these registers, while RTCWREN = 0, will be ignored.

#### 17.2 Operation

#### 17.2.1 REGISTER INTERFACE

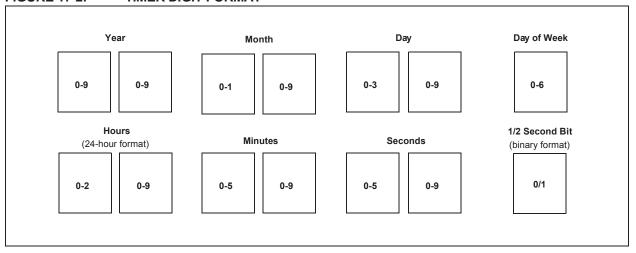

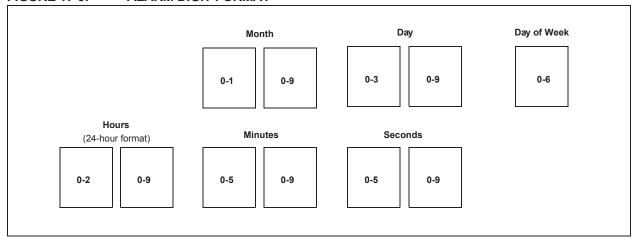

The register interface for the RTCC and alarm values is implemented using the Binary Coded Decimal (BCD) format. This simplifies the firmware when using the module, as each of the digits is contained within its own 4-bit value (see Figure 17-2 and Figure 17-3).

FIGURE 17-2: TIMER DIGIT FORMAT

FIGURE 17-3: ALARM DIGIT FORMAT

#### 17.3 Alarm

The alarm features and characteristics are:

- · Configurable from half a second to one year

- Enabled using the ALRMEN bit (ALRMCFG<7>, Register 17-4)

- · Offers one time and repeat alarm options

#### 17.3.1 CONFIGURING THE ALARM

The alarm feature is enabled using the ALRMEN bit.

This bit is cleared when an alarm is issued. The bit will not be cleared if the CHIME bit = 1 or if ALRMRPT  $\neq 0$ .

The interval selection of the alarm is configured through the ALRMCFG (AMASK<3:0>) bits (see Figure 17-5). These bits determine which and how many digits of the alarm must match the clock value for the alarm to occur.

The alarm can also be configured to repeat based on a preconfigured interval. The number of times this occurs, after the alarm is enabled, is stored in the ALRMRPT register.

Note: While the alarm is enabled (ALRMEN = 1), changing any of the registers, other than the RTCCAL, ALRMCFG and ALRM-RPT registers, and the CHIME bit, can result in a false alarm event leading to a false alarm interrupt. To avoid this, only change the timer and alarm values while

ALRMRPT registers and CHIME bit be changed when RTCSYNC = 0.

the alarm is disabled (ALRMEN = 0). It is

recommended that the ALRMCFG and

#### FIGURE 17-5: ALARM MASK SETTINGS

| Alarm Mask Setting                                        | Day of the | <b>.</b> |     |       |         |         |

|-----------------------------------------------------------|------------|----------|-----|-------|---------|---------|

| AMASK<3:0>                                                | Week       | Month    | Day | Hours | Minutes | Seconds |

| 0000 – Every half second<br>0001 – Every second           |            |          |     |       |         | •       |

| 0010 - Every 10 seconds                                   |            |          |     |       |         | s       |

| 0011 – Every minute                                       |            |          |     |       |         | ss      |

| 0100 – Every 10 minutes                                   |            |          |     |       | m       | s s     |

| 0101 – Every hour                                         |            |          |     |       | m m     | ss      |

| 0110 <b>– Every day</b>                                   |            |          |     | h h   | m m     | ss      |

| 0111 – Every week                                         | d          |          |     | hh    | m m     | s s     |

| 1000 – Every month                                        |            |          | d   | h     | m m     | s s     |

| 1001 – Every year <sup>(1)</sup>                          |            | m m /    | dd  | hh    | m m     | s s     |

| Note 1: Annually, except when configured for February 29. |            |          |     |       |         |         |

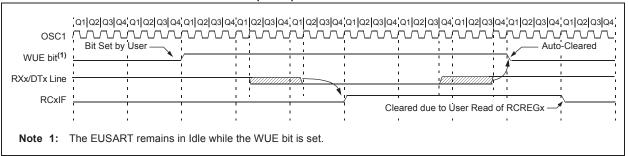

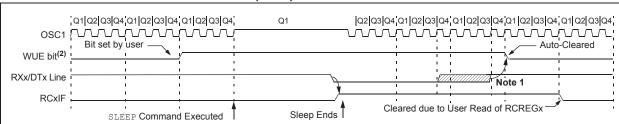

The WUE bit is automatically cleared once a low-to-high transition is observed on the RXx line following the wake-up event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

# 21.2.4.1 Special Considerations Using Auto-Wake-up

Since auto-wake-up functions by sensing rising edge transitions on RXx/DTx, information with any state changes before the Stop bit may signal a false End-Of-Character (EOC) and cause data or framing errors. To work properly, therefore, the initial character in the transmission must be all '0's. This can be 00h (8 bits) for standard RS-232 devices or 000h (12 bits) for LIN/J2602 bus.

Oscillator start-up time must also be considered, especially in applications using oscillators with longer start-up intervals (i.e., HS or HSPLL mode). The Sync Break (or Wake-up Signal) character must be of sufficient length and be followed by a sufficient interval to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

# 21.2.4.2 Special Considerations Using the WUE Bit

The timing of WUE and RCxIF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the EUSART in an Idle mode. The wake-up event causes a receive interrupt by setting the RCxIF bit. The WUE bit is cleared after this when a rising edge is seen on RXx/DTx. The interrupt condition is then cleared by reading the RCREGx register. Ordinarily, the data in RCREGx will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set) and the RCxIF flag is set should not be used as an indicator of the integrity of the data in RCREGx. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process. If a receive operation is not occurring, the WUE bit may then be set just prior to entering Sleep mode.

#### FIGURE 21-9: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

**Note 1:** If the wake-up event requires long oscillator warm-up time, the auto-clear of the WUE bit can occur before the oscillator is ready. This sequence should not depend on the presence of Q clocks.

2: The EUSART remains in Idle while the WUE bit is set.

FIGURE 21-12: SYNCHRONOUS TRANSMISSION (THROUGH TXEN) bit 2 RC7/CCP10/PMA4/RX1/DT1/ bit 0 bit 6 bit 7 bit 1 RP18 Pin RC6/CCP9/PMA5/TX1/CK1/ RP17 Pin Write to TXREG1 reg TX1IF bit TRMT bit TXEN bit Note: This example is equally applicable to EUSART2 (RPn1/TX2/CK2 and RPn2/RX2/DT2).

TABLE 21-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name     | Bit 7                                 | Bit 6         | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1   | Bit 0  |

|----------|---------------------------------------|---------------|--------|--------|---------|--------|---------|--------|

| INTCON   | GIE/GIEH                              | PEIE/GIEL     | TMR0IE | INT0IE | RBIE    | TMR0IF | INT0IF  | RBIF   |

| PIR1     | PMPIF <sup>(1)</sup>                  | ADIF          | RC1IF  | TX1IF  | SSP1IF  | CCP1IF | TMR2IF  | TMR1IF |

| PIE1     | PMPIE <sup>(1)</sup>                  | ADIE          | RC1IE  | TX1IE  | SSP1IE  | CCP1IE | TMR2IE  | TMR1IE |

| IPR1     | PMPIP <sup>(1)</sup>                  | ADIP          | RC1IP  | TX1IP  | SSP1IP  | CCP1IP | TMR2IP  | TMR1IP |

| PIR3     | SSP2IF                                | BCL2IF        | RC2IF  | TX2IF  | TMR4IF  | CTMUIF | TMR3GIF | RTCCIF |

| PIE3     | SSP2IE                                | BCL2IE        | RC2IE  | TX2IE  | TMR4IE  | CTMUIE | TMR3GIE | RTCCIE |

| IPR3     | SSP2IP                                | BCL2IP        | RC2IP  | TX2IP  | TMR4IP  | CTMUIP | TMR3GIP | RTCCIP |

| RCSTAx   | SPEN                                  | RX9           | SREN   | CREN   | ADDEN   | FERR   | OERR    | RX9D   |

| TXREGx   | EUSARTx T                             | ransmit Regis | ster   |        |         |        |         |        |

| TXSTAx   | CSRC                                  | TX9           | TXEN   | SYNC   | SENDB   | BRGH   | TRMT    | TX9D   |

| BAUDCONx | ABDOVF                                | RCIDL         | RXDTP  | TXCKP  | BRG16   | _      | WUE     | ABDEN  |

| SPBRGHx  | EUSARTx Baud Rate Generator High Byte |               |        |        |         |        |         |        |

| SPBRGx   | EUSARTx Baud Rate Generator Low Byte  |               |        |        |         |        |         |        |

| ODCON2   | _                                     | _             | _      | _      | CCP100D | CCP9OD | U2OD    | U10D   |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

Note 1: These pins are only available on 44-pin devices.

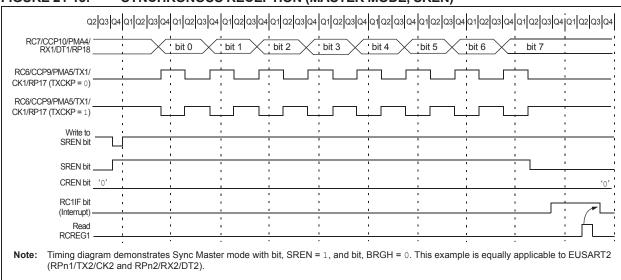

# 21.3.2 EUSART SYNCHRONOUS MASTER RECEPTION

Once Synchronous mode is selected, reception is enabled by setting either the Single Receive Enable bit, SREN (RCSTAx<5>), or the Continuous Receive Enable bit, CREN (RCSTAx<4>). Data is sampled on the RXx pin on the falling edge of the clock.

If enable bit, SREN, is set, only a single word is received. If enable bit, CREN, is set, the reception is continuous until CREN is cleared. If both bits are set, then CREN takes precedence.

To set up a Synchronous Master Reception:

- Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRG16 bit, as required, to achieve the desired baud rate.

- Enable the synchronous master serial port by setting bits, SYNC, SPEN and CSRC.

- 3. Ensure bits, CREN and SREN, are clear.

- 4. If interrupts are desired, set enable bit, RCxIE.

- 5. If 9-bit reception is desired, set bit, RX9.

- 6. If a single reception is required, set bit, SREN. For continuous reception, set bit, CREN.

- 7. Interrupt flag bit, RCxIF, will be set when reception is complete and an interrupt will be generated if the enable bit, RCxIE, was set.

- 8. Read the RCSTAx register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- Read the 8-bit received data by reading the RCREGx register.

- If any error occurred, clear the error by clearing bit, CREN.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### FIGURE 21-13: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

**BNC Branch if Not Carry** Syntax: BNC n Operands:  $\text{-}128 \leq n \leq 127$ if Carry bit is '0', Operation:  $(PC) + 2 + 2n \rightarrow PC$ Status Affected: None Encoding: 1110 0011 nnnn nnnn Description: If the Carry bit is '0', then the program will branch.

> The 2's complement number '2n' is added to the PC. Since the PC will have

incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a

operation

operation

2-cycle instruction.

Words: Cycles: 1(2)

Q Cycle Activity: If Jump:

Q1 Q2 Q3 Q4 Read literal Write to Decode Process 'n' Data PC No No No No

operation If No Jump:

> Q1 Q2 Q3 Q4 Decode Read literal **Process** No 'n' Data operation

Example: HERE BNC Jump

Before Instruction

PC address (HERE)

operation

After Instruction

If Carry PC

address (Jump)

If Carry PC

address (HERE + 2)

**BNN Branch if Not Negative**

Syntax: BNN n Operands:  $-128 \le n \le 127$

Operation: if Negative bit is '0',  $(PC) + 2 + 2n \rightarrow PC$

Status Affected: None

Encoding: 1110 0111 nnnn nnnn

Description: If the Negative bit is '0', then the

program will branch.

The 2's complement number '2n' is added to the PC. Since the PC will have

incremented to fetch the next instruction, the new address will be PC + 2 + 2n. This instruction is then a

2-cycle instruction.

Words:

Cycles: 1(2)

Q Cycle Activity:

If Jump:

| Q1        | Q2           | Q3        | Q4        |

|-----------|--------------|-----------|-----------|

| Decode    | Read literal | Process   | Write to  |

|           | ʻn'          | Data      | PC        |

| No        | No           | No        | No        |

| operation | operation    | operation | operation |

If No Jump:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read literal | Process | No        |

|        | 'n'          | Data    | operation |

Example: HERE BNN Jump

Before Instruction

PC address (HERE)

After Instruction

If Negative PC

address (Jump)

If Negative PC

address (HERE + 2)

**CLRF** Clear f Syntax: CLRF f {,a} Operands:  $0 \le f \le 255$  $a \in \left[0,1\right]$  $000h \rightarrow f$ , Operation:  $1 \rightarrow Z$ Status Affected: Ζ Encoding: 0110 101a ffff ffff Description: Clears the contents of the specified

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

GPR bank (default).

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever  $f \le 95$  (5Fh). See Section 28.2.3 "Byte-Oriented and **Bit-Oriented Instructions in Indexed** Literal Offset Mode" for details.

Words: Cycles:

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4           |

|--------|--------------|---------|--------------|

| Decode | Read         | Process | Write        |

|        | register 'f' | Data    | register 'f' |

Example: CLRF FLAG\_REG,1

Before Instruction

FLAG\_REG 5Ah

After Instruction

FLAG\_REG 00h

| CLRWDT           | Clear Wat                                                                                 | chdog Ti | mer  |      |  |

|------------------|-------------------------------------------------------------------------------------------|----------|------|------|--|

| Syntax:          | CLRWDT                                                                                    | CLRWDT   |      |      |  |

| Operands:        | None                                                                                      | None     |      |      |  |

| Operation:       | 000h → WDT,<br>000h → WDT postscaler,<br>$1 \to \overline{TO}$ ,<br>$1 \to \overline{PD}$ |          |      |      |  |

| Status Affected: | TO, PD                                                                                    |          |      |      |  |

| Encoding:        | 0000                                                                                      | 0000     | 0000 | 0100 |  |

| Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the po                       |          |      |      |  |

PD, are set. Words: 1 Cycles: 1

Q Cycle Activity:

| Q1     | Q2        | Q3      | Q4        |

|--------|-----------|---------|-----------|

| Decode | No        | Process | No        |

|        | operation | Data    | operation |

scaler of the WDT. Status bits, TO and

Example: CLRWDT

Before Instruction

WDT Counter

After Instruction

WDT Counter 00h WDT Postscaler 0 TO PD

**MOVFF** Move f to f Syntax: MOVFF  $f_s, f_d$  $0 \le f_{S} \le 4095$ Operands:  $0 \leq f_d \leq 4095$ Operation:  $(f_s) \rightarrow f_d$ Status Affected: None Encoding: ffffs 1st word (source) 1100 ffff ffff 2nd word (destin.) 1111 ffff ffff  $ffff_d$

The contents of source register 'f<sub>s</sub>' are moved to destination register 'f<sub>d</sub>'.

Location of source 'f<sub>s</sub>' can be anywhere in the 4096-byte data space (000h to FFFh) and location of destination 'f<sub>d</sub>' can also be anywhere from 000h to FFFh.

Either source or destination can be W (a useful special situation).

MOVFF is particularly useful for transferring a data memory location to a peripheral register (such as the transmit buffer or an I/O port).

The MOVFF instruction cannot use the PCL, TOSU, TOSH or TOSL as the destination register

Words: 2

2

Cycles: Q Cycle Activity:

Description:

| Q1     | Q2                                  | Q3              | Q4                              |

|--------|-------------------------------------|-----------------|---------------------------------|

| Decode | Read<br>register 'f'<br>(src)       | Process<br>Data | No<br>operation                 |

| Decode | No<br>operation<br>No dummy<br>read | No<br>operation | Write<br>register 'f'<br>(dest) |

Example: MOVFF REG1, REG2

Before Instruction

REG1 = 33h REG2 = 11h

After Instruction

REG1 = 33h REG2 = 33h

| MOV               | LB                           | Move Literal to Low Nibble in BSR |                                                                                                                                                                           |  |                            |  |  |  |  |

|-------------------|------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------------------------|--|--|--|--|

| Synta             | ax:                          | MOVLW k                           | MOVLW k                                                                                                                                                                   |  |                            |  |  |  |  |

| Oper              | ands:                        | $0 \leq k \leq 255$               |                                                                                                                                                                           |  |                            |  |  |  |  |

| Oper              | ation:                       | $k \to BSR$                       |                                                                                                                                                                           |  |                            |  |  |  |  |

| Statu             | s Affected:                  | None                              |                                                                                                                                                                           |  |                            |  |  |  |  |

| Enco              | Encoding: 0000 0001 kkkk kkk |                                   |                                                                                                                                                                           |  |                            |  |  |  |  |

| Desc              | ription:                     | Bank Selection of BSR<7:4         | The 8-bit literal 'k' is loaded into the Bank Select Register (BSR). The value of BSR<7:4> always remains '0' regardless of the value of k <sub>7</sub> :k <sub>4</sub> . |  |                            |  |  |  |  |

| Word              | ls:                          | 1                                 | 1                                                                                                                                                                         |  |                            |  |  |  |  |

| Cycle             | es:                          | 1                                 | 1                                                                                                                                                                         |  |                            |  |  |  |  |

| Q Cycle Activity: |                              |                                   |                                                                                                                                                                           |  |                            |  |  |  |  |

| Q1                |                              | Q2                                | Q2 Q3                                                                                                                                                                     |  | Q4                         |  |  |  |  |

|                   | Decode                       | Read<br>literal 'k'               | Proce<br>Data                                                                                                                                                             |  | Vrite literal<br>k' to BSR |  |  |  |  |

Example: MOVLB 5

Before Instruction

BSR Register = 02h

After Instruction

BSR Register = 05h

**TSTFSZ** Test f, Skip if 0 Syntax: TSTFSZ f {,a} Operands:  $0 \leq f \leq 255$  $a\in \left[ 0,1\right]$ skip if f = 0 Operation: Status Affected: None Encoding: 0110 011a ffff ffff

Description: If 'f' = 0, the next instruction fetched during the current instruction execution is discarded and a NOP is executed, making this a 2-cycle instruction.

If 'a' is '0', the Access Bank is selected. If 'a' is '1', the BSR is used to select the

GPR bank (default).

If 'a' is '0' and the extended instruction set is enabled, this instruction operates in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 28.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details.

Words: 1 Cycles: 1(2)

Note: 3 cycles if skip and followed

by a 2-word instruction.

#### Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4        |  |

|--------|--------------|---------|-----------|--|

| Decode | Read         | Process | No        |  |

|        | register 'f' | Data    | operation |  |

If skip:

| Q1        | Q2        | Q3        | Q4        |

|-----------|-----------|-----------|-----------|

| No        | No        | No        | No        |

| operation | operation | operation | operation |

If skip and followed by 2-word instruction:

|   | Q1        | Q2        | Q3        | Q4        |

|---|-----------|-----------|-----------|-----------|

| ĺ | No        | No        | No        | No        |

| l | operation | operation | operation | operation |

| ĺ | No        | No        | No        | No        |

| l | operation | operation | operation | operation |

Example: HERE TSTFSZ CNT, 1 NZERO :

ZERO :

Before Instruction

PC = Address (HERE)

After Instruction

If CNT

=

00h,

PC

=

Address (ZERO)

If CNT

≠

00h,

PC

=

Address (NZERO)

**XORLW Exclusive OR Literal with W** Syntax: XORLW k Operands:  $0 \le k \le 255$ Operation: (W) .XOR.  $k \rightarrow W$ Status Affected: N, Z Encoding: 0000 1010 kkkk kkkk The contents of W are XORed with Description: the 8-bit literal 'k'. The result is placed in W. Words: Cycles: 1 Q Cycle Activity: Q2 Q3 Q4 Q1 Write to Decode Read **Process**

Example: XORLW 0xAF

literal 'k'

Data

W

Before Instruction W = B5h

After Instruction

W = 1Ah

# 28.2.3 BYTE-ORIENTED AND BIT-ORIENTED INSTRUCTIONS IN INDEXED LITERAL OFFSET MODE

**Note:** Enabling the PIC18 instruction set extension may cause legacy applications to behave erratically or fail entirely.

In addition to eight new commands in the extended set, enabling the extended instruction set also enables Indexed Literal Offset Addressing (Section 6.6.1 "Indexed Addressing with Literal Offset"). This has a significant impact on the way that many commands of the standard PIC18 instruction set are interpreted.

When the extended set is disabled, addresses embedded in opcodes are treated as literal memory locations: either as a location in the Access Bank (a = 0) or in a GPR bank designated by the BSR (a = 1). When the extended instruction set is enabled and a = 0, however, a file register argument of 5Fh or less is interpreted as an offset from the pointer value in FSR2 and not as a literal address. For practical purposes, this means that all instructions that use the Access RAM bit as an argument – that is, all byte-oriented and bit-oriented instructions, or almost half of the core PIC18 instructions – may behave differently when the extended instruction set is enabled.

When the content of FSR2 is 00h, the boundaries of the Access RAM are essentially remapped to their original values. This may be useful in creating backward-compatible code. If this technique is used, it may be necessary to save the value of FSR2 and restore it when moving back and forth between C and assembly routines in order to preserve the Stack Pointer. Users must also keep in mind the syntax requirements of the extended instruction set (see Section 28.2.3.1 "Extended Instruction Syntax with Standard PIC18 Commands").

Although the Indexed Literal Offset mode can be very useful for dynamic stack and pointer manipulation, it can also be very annoying if a simple arithmetic operation is carried out on the wrong register. Users who are accustomed to the PIC18 programming must keep in mind that, when the extended instruction set is enabled, register addresses of 5Fh or less are used for Indexed Literal Offset Addressing.

Representative examples of typical byte-oriented and bit-oriented instructions in the Indexed Literal Offset mode are provided on the following page to show how execution is affected. The operand conditions shown in the examples are applicable to all instructions of these types.

# 28.2.3.1 Extended Instruction Syntax with Standard PIC18 Commands

When the extended instruction set is enabled, the file register argument, 'f', in the standard byte-oriented and bit-oriented commands is replaced with the literal offset value, 'k'. As already noted, this occurs only when 'f' is less than or equal to 5Fh. When an offset value is used, it must be indicated by square brackets ("[]"). As with the extended instructions, the use of brackets indicates to the compiler that the value is to be interpreted as an index or an offset. Omitting the brackets, or using a value greater than 5Fh within the brackets, will generate an error in the MPASM Assembler.

If the index argument is properly bracketed for Indexed Literal Offset Addressing, the Access RAM argument is never specified; it will automatically be assumed to be '0'. This is in contrast to standard operation (extended instruction set disabled), when 'a' is set on the basis of the target address. Declaring the Access RAM bit in this mode will also generate an error in the MPASM Assembler.

The destination argument 'd' functions as before.

In the latest versions of the MPASM Assembler, language support for the extended instruction set must be explicitly invoked. This is done with either the command line option, /y, or the PE directive in the source listing.

# 28.2.4 CONSIDERATIONS WHEN ENABLING THE EXTENDED INSTRUCTION SET

It is important to note that the extensions to the instruction set may not be beneficial to all users. In particular, users who are not writing code that uses a software stack may not benefit from using the extensions to the instruction set.

Additionally, the Indexed Literal Offset Addressing mode may create issues with legacy applications written to the PIC18 assembler. This is because instructions in the legacy code may attempt to address registers in the Access Bank below 5Fh. Since these addresses are interpreted as literal offsets to FSR2 when the instruction set extension is enabled, the application may read or write to the wrong data addresses.

When porting an application to the PIC18F47J13 Family, it is very important to consider the type of code. A large, re-entrant application that is written in C and would benefit from efficient compilation will do well when using the instruction set extensions. Legacy applications that heavily use the Access Bank will most likely not benefit from using the extended instruction set.

#### 29.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

#### 29.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 29.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 29.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- MPLAB X IDE compatibility

### 29.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM™ and dsPICDEM™ demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELoq® security ICs, CAN, IrDA®, PowerSmart battery management, SEEVAL® evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 29.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

### 30.1 DC Characteristics: Supply Voltage PIC18F47J13 Family (Industrial)

| PIC18F47J13 Family |         | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial |           |     |           |       |                                                        |

|--------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----|-----------|-------|--------------------------------------------------------|

| Param<br>No.       | Symbol  | Characteristic                                                                                                                                           | Min       | Тур | Max       | Units | Conditions                                             |

| D001               | VDD     | Supply Voltage                                                                                                                                           | 2.15      | _   | 3.6       | V     | PIC18F4XJ13, PIC18F2XJ13                               |

| D001A              | VDD     | Supply Voltage                                                                                                                                           | 2.0       |     | 3.6       | V     | PIC18LF4XJ13, PIC18LF2XJ13                             |

| D001B              | VDDCORE | External Supply for Microcontroller Core                                                                                                                 | 2.0       | _   | 2.75      | V     | PIC18LF4XJ13, PIC18LF2XJ13                             |

| D001C              | AVDD    | Analog Supply Voltage                                                                                                                                    | VDD - 0.3 | _   | VDD + 0.3 | V     |                                                        |

| D001D              | AVss    | Analog Ground Potential                                                                                                                                  | Vss - 0.3 | _   | Vss + 0.3 | V     |                                                        |

| D002               | VDR     | RAM Data Retention Voltage <sup>(1)</sup>                                                                                                                | 1.5       | _   | _         | V     |                                                        |

| D003               | VPOR    | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal                                                                                         | _         | _   | 0.7       | V     | See Section 5.3 "Power-on<br>Reset (POR)" for details  |

| D004               | SVDD    | VDD Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal                                                                                             | 0.05      | _   | _         | V/ms  | See Section 5.3 "Power-on<br>Reset (POR)" for details  |

| D005               | VBOR    | VDDCORE Brown-out Reset Voltage                                                                                                                          | _         | 2.0 | 2.15      | V     | PIC18F4XJ13, PIC18F2XJ13 only                          |

| D006               | VDSBOR  | VDD Brown-out Reset<br>Voltage                                                                                                                           | _         | 1.8 | _         | V     | DSBOREN = 1 on "LF" device or "F" device in Deep Sleep |

Note 1: This is the limit to which VDDCORE can be lowered in Sleep mode, or during a device Reset, without losing RAM data.

### 30.3 DC Characteristics: PIC18F47J13 Family (Industrial)

| DC CHARACTERISTICS |       |                                                                              | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for industrial |          |       |                          |  |

|--------------------|-------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|--------------------------|--|

| Param<br>No.       |       | Characteristic                                                               | Min Max                                                                                                                                                  |          | Units | Conditions               |  |

|                    | VIL   | Input Low Voltage                                                            |                                                                                                                                                          |          |       |                          |  |

|                    |       | All I/O Ports:                                                               |                                                                                                                                                          |          |       |                          |  |

| D030               |       | with TTL Buffer                                                              | Vss                                                                                                                                                      | 0.15 VDD | V     | VDD < 3.3V               |  |

| D030A              |       | with TTL Buffer                                                              | Vss                                                                                                                                                      | 0.8      | V     | 3.3V ≤ VDD ≤ 3.6V        |  |

| D031               |       | with Schmitt Trigger Buffer                                                  | Vss                                                                                                                                                      | 0.2 VDD  | V     |                          |  |

| D031A              |       | SCLx/SDAx                                                                    | _                                                                                                                                                        | 0.3 VDD  | V     | I <sup>2</sup> C enabled |  |

| D031B              |       | SCLx/SDAx                                                                    | _                                                                                                                                                        | 0.8      | V     | SMBus enabled            |  |

| D032               |       | MCLR                                                                         | Vss                                                                                                                                                      | 0.2 VDD  | V     |                          |  |

| D033               |       | OSC1                                                                         | Vss                                                                                                                                                      | 0.3 VDD  | V     | HS, HSPLL modes          |  |

| D033A              |       | OSC1                                                                         | Vss                                                                                                                                                      | 0.2 VDD  | V     | EC, ECPLL modes          |  |

| D034               |       | T1OSI                                                                        | Vss                                                                                                                                                      | 0.3      | V     | T10SCEN = 1              |  |

|                    | VIH   | Input High Voltage                                                           |                                                                                                                                                          |          |       |                          |  |

|                    |       | I/O Ports without 5.5V Tolerance:                                            |                                                                                                                                                          |          |       |                          |  |

| D040               |       | with TTL Buffer                                                              | 0.25 VDD + 0.8V                                                                                                                                          | VDD      | V     | VDD < 3.3V               |  |

| D040A              |       | with TTL Buffer                                                              | 2.0                                                                                                                                                      | VDD      | V     | 3.3V ≤ VDD ≤ 3.6V        |  |

| D041               |       | with Schmitt Trigger Buffer                                                  | 0.8 Vdd                                                                                                                                                  | VDD      | V     |                          |  |

|                    |       | I/O Ports with 5.5V Tolerance:(4)                                            |                                                                                                                                                          |          |       |                          |  |

| Dxxx               |       | with TTL Buffer                                                              | 0.25 VDD + 0.8V                                                                                                                                          | 5.5      | V     | VDD < 3.3V               |  |

| DxxxA              |       |                                                                              | 2.0                                                                                                                                                      | 5.5      | V     | $3.3V \le VDD \le 3.6V$  |  |

| Dxxx               |       | with Schmitt Trigger Buffer                                                  | 0.8 VDD                                                                                                                                                  | 5.5      | V     |                          |  |

| D041A              |       | SCLx/SDAx                                                                    | 0.7 VDD                                                                                                                                                  | _        | V     | I <sup>2</sup> C enabled |  |

| D041B              |       | SCLx/SDAx                                                                    | 2.1                                                                                                                                                      | _        | V     | SMBus enabled; VDD ≥ 3V  |  |

| D042               |       | MCLR                                                                         | 0.8 VDD                                                                                                                                                  | 5.5      | V     |                          |  |

| D043               |       | OSC1                                                                         | 0.7 VDD                                                                                                                                                  | VDD      | V     | HS, HSPLL modes          |  |

| D043A              |       | OSC1                                                                         | 0.8 VDD                                                                                                                                                  | VDD      | V     | EC, ECPLL modes          |  |

| D044               |       | T10SI                                                                        | 1.6                                                                                                                                                      | VDD      | V     | T10SCEN = 1              |  |

|                    | IPU   | Weak Pull-up Current                                                         |                                                                                                                                                          |          |       |                          |  |

| D070               | IPURB | PORTB, PORTD <sup>(3)</sup> and<br>PORTE <sup>(3)</sup> Weak Pull-up Current | 80                                                                                                                                                       | 400      | μА    | VDD = 3.3V, VPIN = VSS   |  |

Note 1: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 2: Negative current is defined as current sourced by the pin.

- 3: Only available in 44-pin devices.

- **4:** Refer to Table 10-2 for pin tolerance levels.

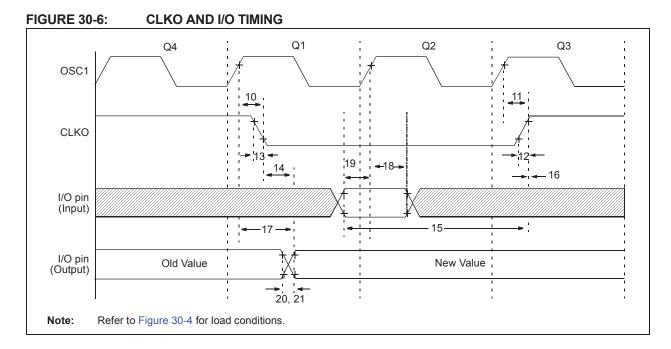

TABLE 30-13: CLKO AND I/O TIMING REQUIREMENTS

| Param<br>No. | Symbol   | Characteristic                                             | Min           | Тур | Max          | Units | Conditions |

|--------------|----------|------------------------------------------------------------|---------------|-----|--------------|-------|------------|

| 10           | TosH2ckL | OSC1 ↑ to CLKO ↓                                           | _             | 75  | 200          | ns    | (Note 1)   |

| 11           | TosH2ckH | OSC1 ↑ to CLKO ↑                                           | _             | 75  | 200          | ns    | (Note 1)   |

| 12           | TCKR     | CLKO Rise Time                                             | _             | 15  | 30           | ns    | (Note 1)   |

| 13           | TCKF     | CLKO Fall Time                                             | _             | 15  | 30           | ns    | (Note 1)   |

| 14           | TckL2ioV | CLKO ↓ to Port Out Valid                                   | _             | _   | 0.5 Tcy + 20 | ns    |            |

| 15           | TioV2ckH | Port In Valid before CLKO ↑                                | 0.25 Tcy + 25 | _   | _            | ns    |            |

| 16           | TckH2ioI | Port In Hold after CLKO ↑                                  | 0             | _   | _            | ns    |            |

| 17           | TosH2ioV | OSC1 ↑ (Q1 cycle) to Port Out Valid                        | _             | 50  | 150          | ns    |            |

| 18           | TosH2ıoI | OSC1 ↑ (Q2 cycle) to Port Input Invalid (I/O in hold time) | 100           | _   | _            | ns    |            |

| 19           | TioV2osH | Port Input Valid to OSC1 ↑ (I/O in setup time)             | 0             | _   | _            | ns    |            |

| 20           | TioR     | Port Output Rise Time                                      | _             | _   | 6            | ns    |            |

| 21           | TioF     | Port Output Fall Time                                      | _             | _   | 5            | ns    |            |

| 22†          | TINP     | INTx pin High or Low Time                                  | Tcy           | _   | _            | ns    |            |

| 23†          | TRBP     | RB<7:4> Change INTx High or Low Time                       | Tcy           | _   | _            | ns    |            |

<sup>†</sup> These parameters are asynchronous events not related to any internal clock edges.

Note 1: Measurements are taken in EC mode, where CLKO output is 4 x Tosc.

### 44-Lead Plastic Quad Flat, No Lead Package (ML) - 8x8 mm Body [QFN or VQFN]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | MILLIMETERS |                |          |      |  |

|-------------------------|-------------|----------------|----------|------|--|

| Dimension               | Limits      | MIN            | NOM      | MAX  |  |

| Number of Pins          | N           |                | 44       |      |  |

| Pitch                   | е           |                | 0.65 BSC |      |  |

| Overall Height          | Α           | 0.80 0.90 1.00 |          |      |  |

| Standoff                | A1          | 0.00           | 0.02     | 0.05 |  |

| Terminal Thickness A3   |             |                | 0.20 REF |      |  |

| Overall Width           | Е           | 8.00 BSC       |          |      |  |

| Exposed Pad Width       | E2          | 6.25 6.45 6.60 |          |      |  |

| Overall Length          | D           | 8.00 BSC       |          |      |  |

| Exposed Pad Length      | D2          | 6.25 6.45 6.60 |          |      |  |

| Terminal Width          | b           | 0.20 0.30 0.35 |          |      |  |

| Terminal Length         | L           | 0.30 0.40 0.50 |          |      |  |

| Terminal-to-Exposed-Pad | K           | 0.20           |          |      |  |

#### Notes:

Note:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M  $\,$

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-103D Sheet 2 of 2