Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 48MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 64KB (32K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 3.8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.15V ~ 3.6V                                                               |

| Data Converters            | A/D 13x10b/12b                                                             |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

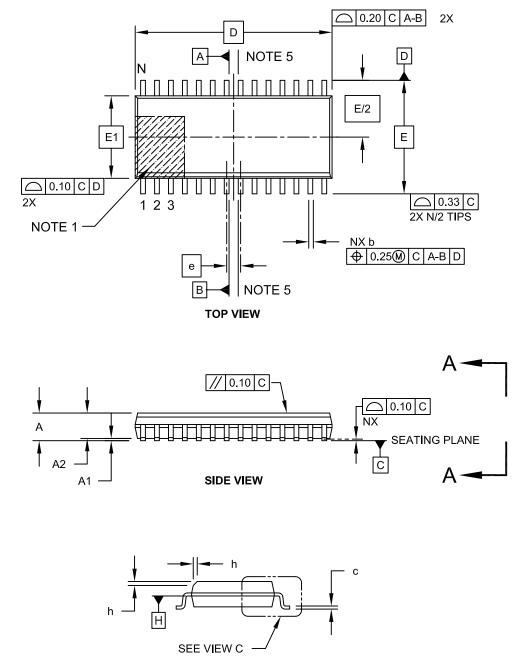

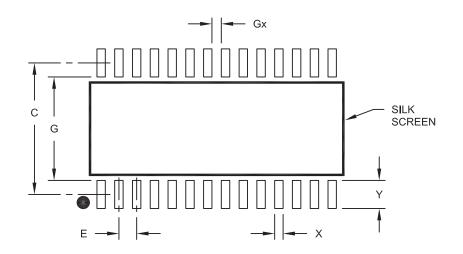

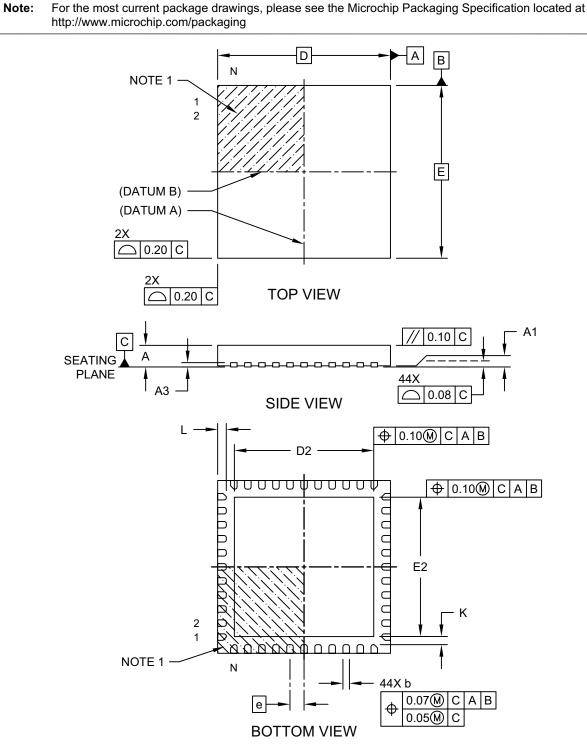

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f46j13-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 9.1 INTCON Registers

The INTCON registers are readable and writable registers, which contain various enable, priority and flag bits.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global interrupt enable bit. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt. This feature allows for software polling.

#### REGISTER 9-1: INTCON: INTERRUPT CONTROL REGISTER (ACCESS FF2h)

| R/W-0    | R/W-0     | R/W-0  | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-x               |

|----------|-----------|--------|--------|-------|--------|--------|---------------------|

| GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF <sup>(1)</sup> |

| bit 7    |           |        |        |       |        |        | bit 0               |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| bit 7  | GIE/GIEH: Global Interrupt Enable bit                                                                                                             |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|        | When IPEN = 0:                                                                                                                                    |

|        | 1 = Enables all unmasked interrupts                                                                                                               |

|        | 0 = Disables all interrupts                                                                                                                       |

|        | When IPEN = 1:                                                                                                                                    |

|        | 1 = Enables all high-priority interrupts                                                                                                          |

| h:+ 0  | 0 = Disables all interrupts                                                                                                                       |

| bit 6  | PEIE/GIEL: Peripheral Interrupt Enable bit                                                                                                        |

|        | <u>When IPEN = 0:</u><br>1 = Enables all unmasked peripheral interrupts                                                                           |

|        | 0 = Disables all peripheral interrupts                                                                                                            |

|        | When IPEN = 1:                                                                                                                                    |

|        | 1 = Enables all low-priority peripheral interrupts                                                                                                |

|        | 0 = Disables all low-priority peripheral interrupts                                                                                               |

| bit 5  | TMR0IE: TMR0 Overflow Interrupt Enable bit                                                                                                        |

|        | 1 = Enables the TMR0 overflow interrupt                                                                                                           |

|        | 0 = Disables the TMR0 overflow interrupt                                                                                                          |

| bit 4  | INTOIE: INTO External Interrupt Enable bit                                                                                                        |

|        | 1 = Enables the INTO external interrupt                                                                                                           |

|        | 0 = Disables the INT0 external interrupt                                                                                                          |

| bit 3  | RBIE: RB Port Change Interrupt Enable bit                                                                                                         |

|        | 1 = Enables the RB port change interrupt                                                                                                          |

|        | 0 = Disables the RB port change interrupt                                                                                                         |

| bit 2  | TMR0IF: TMR0 Overflow Interrupt Flag bit                                                                                                          |

|        | <ul> <li>1 = The TMR0 register has overflowed (must be cleared in software)</li> <li>0 = The TMR0 register did not overflow</li> </ul>            |

| bit 1  |                                                                                                                                                   |

| DILI   | INTOIF: INTO External Interrupt Flag bit                                                                                                          |

|        | <ul> <li>1 = The INT0 external interrupt occurred (must be cleared in software)</li> <li>0 = The INT0 external interrupt did not occur</li> </ul> |

| bit 0  | <b>RBIF:</b> RB Port Change Interrupt Flag bit <sup>(1)</sup>                                                                                     |

| DIL U  | 1 = At least one of the RB<7:4> pins changed state (must be cleared in software)                                                                  |

|        | 0 = None of the RB<7:4> pins have changed state (must be cleared in software)                                                                     |

| Note 1 |                                                                                                                                                   |

|        |                                                                                                                                                   |

**Note 1:** A mismatch condition will continue to set this bit. Reading PORTB and waiting 1 TCY will end the mismatch condition and allow the bit to be cleared.

| REGISTER 10-1: ODCON1: PERIPHERAL OPEN-DRAIN CONTROL REGISTER 1 (BANKED F42h) |                                      |                                        |                |                   |                  |                 |         |  |  |  |

|-------------------------------------------------------------------------------|--------------------------------------|----------------------------------------|----------------|-------------------|------------------|-----------------|---------|--|--|--|

| R/W-0                                                                         | R/W-0                                | R/W-0                                  | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |  |  |

| CCP8OD                                                                        | CCP7OD                               | CCP6OD                                 | CCP5OD         | CCP4OD            | ECCP3OD          | ECCP2OD         | ECCP10D |  |  |  |

| bit 7                                                                         |                                      | •                                      |                |                   |                  |                 | bit 0   |  |  |  |

|                                                                               |                                      |                                        |                |                   |                  |                 |         |  |  |  |

| Legend:                                                                       |                                      |                                        |                |                   |                  |                 |         |  |  |  |

| R = Readable                                                                  |                                      | W = Writable                           |                | •                 | nented bit, read |                 |         |  |  |  |

| -n = Value at                                                                 | POR                                  | '1' = Bit is set                       |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |  |  |  |

| hit 7                                                                         |                                      | CD9 Onen Drei                          | - Output Ench  | a hit             |                  |                 |         |  |  |  |

| bit 7                                                                         |                                      | CP8 Open-Drai<br>ain capability is     |                | e bit             |                  |                 |         |  |  |  |

|                                                                               |                                      | ain capability is                      |                |                   |                  |                 |         |  |  |  |

| bit 6                                                                         |                                      | CP7 Open-Drai                          |                | e bit             |                  |                 |         |  |  |  |

|                                                                               |                                      | ain capability is                      | •              |                   |                  |                 |         |  |  |  |

|                                                                               |                                      | ain capability is                      |                |                   |                  |                 |         |  |  |  |

| bit 5                                                                         | CCP6OD: CO                           | CP6 Open-Drai                          | n Output Enabl | e bit             |                  |                 |         |  |  |  |

|                                                                               | 1 = Open-drain capability is enabled |                                        |                |                   |                  |                 |         |  |  |  |

|                                                                               | •                                    | ain capability is                      |                |                   |                  |                 |         |  |  |  |

| bit 4                                                                         |                                      | CP5 Open-Drai                          | •              | e bit             |                  |                 |         |  |  |  |

|                                                                               |                                      | ain capability is<br>ain capability is |                |                   |                  |                 |         |  |  |  |

| bit 3                                                                         | •                                    | CP4 Open-Drai                          |                | a bit             |                  |                 |         |  |  |  |

| DIL 3                                                                         |                                      | ain capability is                      |                | e bit             |                  |                 |         |  |  |  |

|                                                                               |                                      | ain capability is                      |                |                   |                  |                 |         |  |  |  |

| bit 2                                                                         | •                                    | ECCP3 Open-D                           |                | able bit          |                  |                 |         |  |  |  |

|                                                                               |                                      | ain capability is                      | •              |                   |                  |                 |         |  |  |  |

|                                                                               | 0 = Open-dra                         | ain capability is                      | disabled       |                   |                  |                 |         |  |  |  |

| bit 1                                                                         | ECCP2OD: E                           | ECCP2 Open-D                           | rain Output En | able bit          |                  |                 |         |  |  |  |

|                                                                               |                                      | ain capability is                      |                |                   |                  |                 |         |  |  |  |

|                                                                               |                                      | ain capability is                      |                |                   |                  |                 |         |  |  |  |

| bit 0                                                                         |                                      | ECCP1 Open-D                           |                | able bit          |                  |                 |         |  |  |  |

|                                                                               |                                      | ain capability is<br>ain capability is |                |                   |                  |                 |         |  |  |  |

|                                                                               |                                      | an capability is                       | นเรสมเย่น      |                   |                  |                 |         |  |  |  |

| REGISTER 10-2: ODCON2: PERIPHERAL OPEN-DRAIN CONTROL REGISTER 2 (BANKED F41h) |                                                                                                                                                                                                              |                                   |                            |                   |        |                 |      |  |  |  |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----------------------------|-------------------|--------|-----------------|------|--|--|--|

| U-0                                                                           | U-0 U-0 U-0 U-0 R/W-0 R/W-0 R/W-0 R/W-0                                                                                                                                                                      |                                   |                            |                   |        |                 |      |  |  |  |

| _                                                                             | —                                                                                                                                                                                                            | —                                 | —                          | CCP10OD           | CCP90D | U2OD            | U10D |  |  |  |

| bit 7 bit 0                                                                   |                                                                                                                                                                                                              |                                   |                            |                   |        |                 |      |  |  |  |

|                                                                               |                                                                                                                                                                                                              |                                   |                            |                   |        |                 |      |  |  |  |

| Legend:                                                                       |                                                                                                                                                                                                              |                                   |                            |                   |        |                 |      |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'          |                                                                                                                                                                                                              |                                   |                            |                   |        |                 |      |  |  |  |

| -n = Value a                                                                  | at POR                                                                                                                                                                                                       | '1' = Bit is set                  |                            | '0' = Bit is clea | ared   | x = Bit is unkr | nown |  |  |  |

| bit 3                                                                         | <ul> <li>it 7-4 Unimplemented: Read as '0'</li> <li>it 3 CCP10OD: CCP10 Open-Drain Output Enable bit</li> <li>1 = Open-drain capability is enabled</li> <li>0 = Open-drain capability is disabled</li> </ul> |                                   |                            |                   |        |                 |      |  |  |  |

| bit 2                                                                         | <b>CCP9OD:</b> CCP9 Open-Drain Output Enable bit<br>1 = Open-drain capability is enabled<br>0 = Open-drain capability is disabled                                                                            |                                   |                            |                   |        |                 |      |  |  |  |

| bit 1                                                                         | <b>U2OD:</b> USART2 Open-Drain Output Enable bit<br>1 = Open-drain capability is enabled<br>0 = Open-drain capability is disabled                                                                            |                                   |                            |                   |        |                 |      |  |  |  |

| bit 0                                                                         |                                                                                                                                                                                                              | T1 Open-Drain<br>in capability is | n Output Enable<br>enabled | e bit             |        |                 |      |  |  |  |

0 = Open-drain capability is disabled

# REGISTER 10-3: ODCON3: PERIPHERAL OPEN-DRAIN CONTROL REGISTER 3 (BANKED F40h)

| R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  |

|--------|-----|-----|-----|-----|-----|--------|--------|

| CTMUDS | —   | —   | —   | —   | —   | SPI2OD | SPI10D |

| bit 7  |     |     |     |     |     |        | bit 0  |

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 7   | CTMUDS: CTMU Pulse Delay Enable bit                                                                  |

|---------|------------------------------------------------------------------------------------------------------|

|         | 1 = Pulse delay input for CTMU enabled on pin, RA1                                                   |

| bit 6-2 | Unimplemented: Read as '0'                                                                           |

| bit 1   | SPI2OD: SPI2 Open-Drain Output Enable bit                                                            |

|         | <ul><li>1 = Open-drain capability is enabled</li><li>0 = Open-drain capability is disabled</li></ul> |

| bit 0   | SPI10D: SPI1 Open-Drain Output Enable bit                                                            |

|         | <ul><li>1 = Open-drain capability is enabled</li><li>0 = Open-drain capability is disabled</li></ul> |

| IABLE 10-7: | ABLE 10-7: PORTC I/O SUMMARY (CONTINUED) |                 |     |                |                                                                                                                               |  |

|-------------|------------------------------------------|-----------------|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------|--|

| Pin         | Function                                 | TRIS<br>Setting | I/O | I/O<br>Type    | Description                                                                                                                   |  |

| RC5/SDO1/   | RC5                                      | 0               | 0   | DIG            | PORTC<5> data output.                                                                                                         |  |

| RP16        | SDO1                                     | X               | 0   | DIG            | SPI data output (MSSP1 module).                                                                                               |  |

|             | RP16                                     | 1               | I   | ST             | Remappable Peripheral Pin 16 input.                                                                                           |  |

|             |                                          | 0               | 0   | DIG            | Remappable Peripheral Pin 16 output.                                                                                          |  |

| RC6/CCP9/   | RC6                                      | 1               | I   | ST             | PORTC<6> data input.                                                                                                          |  |

| PMA5/TX1/   |                                          | 0               | 0   | DIG            | LATC<6> data output.                                                                                                          |  |

| CK1/RP17    | CCP9                                     | 1               | I   | ST             | Capture input.                                                                                                                |  |

|             |                                          | 0               | 0   | DIG            | Compare/PWM output.                                                                                                           |  |

|             | PMA5 <sup>(1)</sup>                      | 1               | Ι   | ST/TTL         | Parallel Master Port io_addr_in<5>.                                                                                           |  |

|             |                                          | 0               | 0   | DIG            | Parallel Master Port address.                                                                                                 |  |

|             | TX1                                      | 0               | 0   | DIG            | Asynchronous serial transmit data output (EUSART module);<br>takes priority over port data. User must configure as an output. |  |

|             | CK1                                      | 1               | Ι   | ST             | Synchronous serial clock input (EUSART module).                                                                               |  |

|             |                                          | 0               | 0   | DIG            | Synchronous serial clock output (EUSART module); takes priority over port data.                                               |  |

|             | RP17                                     | 1               | Ι   | ST             | Remappable Peripheral Pin 17 input.                                                                                           |  |

|             |                                          | 0               | 0   | DIG            | Remappable Peripheral Pin 17 output.                                                                                          |  |

| RC7/CCP10/  | RC7                                      | 1               | Ι   | ST             | PORTC<7> data input.                                                                                                          |  |

| PMA4/RX1/   |                                          | 0               | 0   | DIG            | LATC<7> data output.                                                                                                          |  |

| DT1/RP18    | CCP10                                    | 1               | Ι   | ST             | Capture input.                                                                                                                |  |

|             |                                          | 0               | 0   | DIG            | Compare/PWM output.                                                                                                           |  |

|             | PMA4 <sup>(1)</sup>                      | х               | I/O | ST/TTL/<br>DIG | Parallel Master Port address.                                                                                                 |  |

|             | RX1                                      | 1               | I   | ST             | Asynchronous serial receive data input (EUSART module).                                                                       |  |

|             | DT1                                      | 1               | 1   | ST             | Synchronous serial data input (EUSART module). User must configure as an input.                                               |  |

|             |                                          | 0               | 0   | DIG            | Synchronous serial data output (EUSART module); takes priority over port data.                                                |  |

|             | RP18                                     | 1               | I   | ST             | Remappable Peripheral Pin 18 input.                                                                                           |  |

|             |                                          | 0               | 0   | DIG            | Remappable Peripheral Pin 18 output.                                                                                          |  |

|             |                                          |                 |     |                |                                                                                                                               |  |

|  | <b>TABLE 10-7:</b> | PORTC I/O SUM | MARY (CONTINUED) |

|--|--------------------|---------------|------------------|

|--|--------------------|---------------|------------------|

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; I<sup>2</sup>C/SMB = I<sup>2</sup>C/SMBus input buffer; x = Don't care (TRISx bit does not affect port direction or is overridden for this option)

**Note 1:** This bit is only available on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

#### TABLE 10-8: SUMMARY OF REGISTERS ASSOCIATED WITH PORTC

| Name   | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   |

|--------|--------|--------|---------|---------|---------|--------|---------|---------|

| PORTC  | RC7    | RC6    | RC5     | RC4     | RC3     | RC2    | RC1     | RC0     |

| LATC   | LATC7  | LATC6  | LATC5   | LATC4   | LATC3   | LATC2  | LATC1   | LATC0   |

| TRISC  | TRISC7 | TRISC6 | TRISC5  | TRISC4  | TRISC3  | TRISC2 | TRISC1  | TRISC0  |

| ANCON1 | VBGEN  | —      | —       | PCFG12  | PCFG11  | PCFG10 | PCFG9   | PCFG8   |

| CM2CON | CON    | COE    | CPOL    | EVPOL1  | EVPOL0  | CREF   | CCH1    | CCH0    |

| RTCCFG | RTCEN  |        | RTCWREN | RTCSYNC | HALFSEC | RTCOE  | RTCPTR1 | RTCPTR0 |

$\ensuremath{\textcircled{}^\circ}$  2010-2017 Microchip Technology Inc.

| Pin                   | Function            | TRIS<br>Setting | I/O | I/O<br>Type | Description                          |

|-----------------------|---------------------|-----------------|-----|-------------|--------------------------------------|

| RD6/PMD6/ RD6<br>RP23 |                     | 1               | Ι   | ST          | PORTD<6> data input.                 |

|                       |                     | 0               | 0   | DIG         | LATD<6> data output.                 |

|                       | PMD6 <sup>(1)</sup> | 1               | Ι   | ST/TTL      | Parallel Master Port data in.        |

| RP23                  |                     | 0               | 0   | DIG         | Parallel Master Port data out.       |

|                       |                     | 1               | Ι   | ST          | Remappable Peripheral Pin 23 input.  |

|                       |                     | 0               | 0   | DIG         | Remappable Peripheral Pin 23 output. |

| RD7/PMD7/             | RD7                 | 1               | Ι   | ST          | PORTD<7> data input.                 |

| RP24                  |                     | 0               | 0   | DIG         | LATD<7> data output.                 |

|                       | PMD7 <sup>(1)</sup> | 1               | Ι   | ST/TTL      | Parallel Master Port data in.        |

|                       |                     | 0               | 0   | DIG         | Parallel Master Port data out.       |

|                       | RP24                | 1               | Ι   | ST          | Remappable Peripheral Pin 24 input.  |

|                       |                     | 0               | 0   | DIG         | Remappable Peripheral Pin 24 output. |

#### TABLE 10-9: PORTD I/O SUMMARY (CONTINUED)

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer;  $I^2C/SMB = I^2C/SMB$ us input buffer; x = Don't care (TRISx bit does not affect port direction or is overridden for this option).

Note 1: Only on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

#### TABLE 10-10: SUMMARY OF REGISTERS ASSOCIATED WITH PORTD

| Name                 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|----------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| PORTD <sup>(1)</sup> | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    |

| LATD <sup>(1)</sup>  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  |

| TRISD <sup>(1)</sup> | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTD.

Note 1: These registers are not available in 28-pin devices (PIC18F26J13, PIC18F27J13, PIC18LF26J13 and PIC18LF26J13).

#### REGISTER 10-14: RPINR12: PERIPHERAL PIN SELECT INPUT REGISTER 12 (BANKED EF2h)

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | T1GR4 | T1GR3 | T1GR2 | T1GR1 | T1GR0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |                    |  |  |  |

|-------------------|-------------------------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                                            | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 7-5 Unimplemented: Read as '0'

bit 4-0 **T1GR<4:0>:** Timer1 Gate Input (T1G) to the Corresponding RPn Pin bits

#### REGISTER 10-15: RPINR13: PERIPHERAL PIN SELECT INPUT REGISTER 13 (BANKED EF3h)

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | T3GR4 | T3GR3 | T3GR2 | T3GR1 | T3GR0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | R/W = Readable bit, | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |  |  |  |  |

|-------------------|---------------------|-------------------------------------------------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit                                       | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared                                        | x = Bit is unknown                 |  |  |  |  |

bit 4-0 T3GR<4:0>: Timer3 Gate Input (T3G) to the Corresponding RPn Pin bits

#### REGISTER 10-16: RPINR14: PERIPHERAL PIN SELECT INPUT REGISTER 14 (BANKED EF4h)

| U-0   | U-0 | U-0 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | T5GR4 | T5GR3 | T5GR2 | T5GR1 | T5GR0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | R/W = Readable bit, Writa | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                    |  |  |  |  |

|-------------------|---------------------------|-------------------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read as '0'                          |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared                                        | x = Bit is unknown |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **T5GR<4:0>:** Timer5 Gate Input (T5G) to the Corresponding RPn Pin bits

#### REGISTER 10-39: RPOR15: PERIPHERAL PIN SELECT OUTPUT REGISTER 15 (BANKED ECFh)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP15R4 | RP15R3 | RP15R2 | RP15R1 | RP15R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |                    |  |  |  |

|-------------------|-------------------------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                                            | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP15R<4:0>:** Peripheral Output Function is Assigned to RP15 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-40: RPOR16: PERIPHERAL PIN SELECT OUTPUT REGISTER 16 (BANKED ED0h)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP16R4 | RP16R3 | RP16R2 | RP16R1 | RP16R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | R/W = Readable bit, \ | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                    |  |  |  |

|-------------------|-----------------------|-------------------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit                                       | , read as '0'      |  |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared                                        | x = Bit is unknown |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP16R<4:0>:** Peripheral Output Function is Assigned to RP16 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-41: RPOR17: PERIPHERAL PIN SELECT OUTPUT REGISTER 17 (BANKED ED1h)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP17R4 | RP17R3 | RP17R2 | RP17R1 | RP17R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |                    |  |  |

|-------------------|-------------------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                            | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP17R<4:0>:** Peripheral Output Function is Assigned to RP17 Output Pin bits (see Table 10-14 for peripheral function numbers)

Calibration of the crystal can be done through this module to yield an error of 3 seconds or less per month.

(For further details, see Section 17.2.9 "Calibration".)

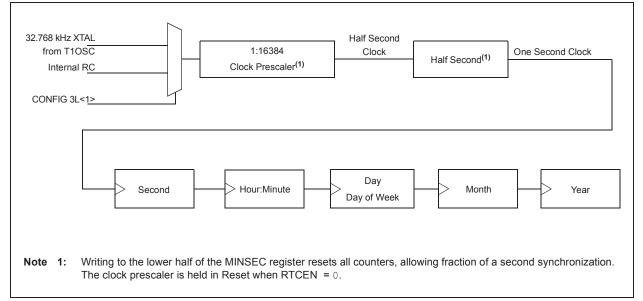

#### 17.2.2 CLOCK SOURCE

As mentioned earlier, the RTCC module is intended to be clocked by an external Real-Time Clock (RTC) crystal oscillating at 32.768 kHz, but can also be clocked by the INTRC. The RTCC clock selection is decided by the RTCOSC bit (CONFIG3L<1>).

FIGURE 17-4: CLOCK SOURCE MULTIPLEXING

#### 17.2.2.1 Real-Time Clock Enable

The RTCC module can be clocked by an external, 32.768 kHz crystal (Timer1 oscillator or T1CKI input) or the INTRC oscillator, which can be selected in CON-FIG3L<1>.

If the Timer1 oscillator will be used as the clock source for the RTCC, make sure to enable it by setting T1CON<3> (T1OSCEN). The selected RTC clock can be brought out to the RTCC pin by the RTSECSEL<1:0> bits in the PADCFG1 register.

#### 17.2.3 DIGIT CARRY RULES

This section explains which timer values are affected when there is a rollover.

- Time of Day: From 23:59:59 to 00:00:00 with a carry to the Day field

- Month: From 12/31 to 01/01 with a carry to the Year field

- Day of Week: From 6 to 0 with no carry (see Table 17-1)

- Year Carry: From 99 to 00; this also surpasses the use of the RTCC

For the day to month rollover schedule, see Table 17-2.

Considering that the following values are in BCD format, the carry to the upper BCD digit will occur at a count of 10 and not at 16 (SECONDS, MINUTES, HOURS, WEEKDAY, DAYS and MONTHS).

| TABLE 17-1: | DAY OF WEEK SCHEDULE |

|-------------|----------------------|

|-------------|----------------------|

| Day of Week |   |  |  |  |  |

|-------------|---|--|--|--|--|

| Sunday      | 0 |  |  |  |  |

| Monday      | 1 |  |  |  |  |

| Tuesday     | 2 |  |  |  |  |

| Wednesday   | 3 |  |  |  |  |

| Thursday    | 4 |  |  |  |  |

| Friday      | 5 |  |  |  |  |

| Saturday    | 6 |  |  |  |  |

#### 18.1 CCP Module Configuration

Each Capture/Compare/PWM module is associated with a control register (generically, CCPxCON) and a data register (CCPRx). The data register, in turn, is comprised of two 8-bit registers: CCPRxL (low byte) and CCPRxH (high byte). All registers are both readable and writable.

#### 18.1.1 CCP MODULES AND TIMER RESOURCES

The CCP modules utilize Timers, 1 through 8, varying with the selected mode. Various timers are available to the CCP modules in Capture, Compare or PWM modes, as shown in Table 18-1.

#### TABLE 18-1: CCP MODE – TIMER RESOURCE

| CCP Mode | Timer Resource                   |  |  |  |

|----------|----------------------------------|--|--|--|

| Capture  | Timert, Timer2 or Timer5         |  |  |  |

| Compare  | Timer1, Timer3 or Timer5         |  |  |  |

| PWM      | Timer2, Timer4, Timer6 or Timer8 |  |  |  |

The assignment of a particular timer to a module is determined by the Timer to CCP enable bits in the CCPTMRSx registers. (See Register 18-2 and Register 18-3.) All of the modules may be active at once and may share the same timer resource if they are configured to operate in the same mode (Capture/Compare or PWM), at the same time.

The CCPTMRS1 register selects the timers for CCP modules, 7, 6, 5 and 4, and the CCPTMRS2 register selects the timers for CCP modules, 10, 9 and 8. The possible configurations are shown in Table 18-2 and Table 18-3.

#### TABLE 18-2: TIMER ASSIGNMENTS FOR CCP MODULES 4, 5, 6 AND 7

|                 | CCPTMRS1 Register           |                   |         |                             |             |         |                             |             |                 |                             |             |  |

|-----------------|-----------------------------|-------------------|---------|-----------------------------|-------------|---------|-----------------------------|-------------|-----------------|-----------------------------|-------------|--|

|                 | CCP4                        |                   |         | CCP5                        |             |         | CCP6                        |             |                 | CCP7                        |             |  |

| C4TSEL<br><1:0> | Capture/<br>Compare<br>Mode | PWM<br>Mode       | C5TSEL0 | Capture/<br>Compare<br>Mode | PWM<br>Mode | C6TSEL0 | Capture/<br>Compare<br>Mode | PWM<br>Mode | C7TSEL<br><1:0> | Capture/<br>Compare<br>Mode | PWM<br>Mode |  |

| 0 0             | TMR1                        | TMR2              | 0       | TMR1                        | TMR2        | 0       | TMR1                        | TMR2        | 0 0             | TMR1                        | TMR2        |  |

| 0 1             | TMR3                        | TMR4              | 1       | TMR5                        | TMR4        | 1       | TMR5                        | TMR2        | 0 1             | TMR5                        | TMR4        |  |

| 1 0             | TMR3                        | TMR6              |         |                             |             |         |                             |             | 1 0             | TMR5                        | TMR6        |  |

| 1 1             | Reserv                      | ed <sup>(1)</sup> |         |                             |             |         |                             |             | 1 1             | TMR5                        | TMR8        |  |

**Note 1:** Do not use the reserved bit configuration.

#### TABLE 18-3: TIMER ASSIGNMENTS FOR CCP MODULES 8, 9 AND 10

|                 | CCPTMRS2 Register           |                   |                 |                             |                   |         |                             |             |          |                             |                   |

|-----------------|-----------------------------|-------------------|-----------------|-----------------------------|-------------------|---------|-----------------------------|-------------|----------|-----------------------------|-------------------|

|                 | CCP8                        |                   |                 | CCP8 CCP9 CCP9              |                   |         |                             |             | CCP10    |                             |                   |

| C8TSEL<br><1:0> | Capture/<br>Compare<br>Mode | PWM<br>Mode       | C8TSEL<br><1:0> | Capture/<br>Compare<br>Mode | PWM<br>Mode       | C9TSEL0 | Capture/<br>Compare<br>Mode | PWM<br>Mode | C10TSEL0 | Capture/<br>Compare<br>Mode | PWM<br>Mode       |

| 0 0             | TMR1                        | TMR2              | 0 0             | TMR1                        | TMR2              | 0       | TMR1                        | TMR2        | 0        | TMR1                        | TMR2              |

| 0 1             | TMR1                        | TMR4              | 0 1             | TMR1                        | TMR4              | 1       | TMR1                        | TMR4        | 1        | Reserve                     | ed <sup>(1)</sup> |

| 1 0             | TMR1                        | TMR6              | 1 0             | TMR1                        | TMR6              |         |                             |             |          |                             |                   |

| 1 1             | Reserv                      | ed <sup>(1)</sup> | 1 1             | Reserv                      | ed <sup>(1)</sup> |         |                             |             |          |                             |                   |

**Note 1:** Do not use the reserved bit configuration.

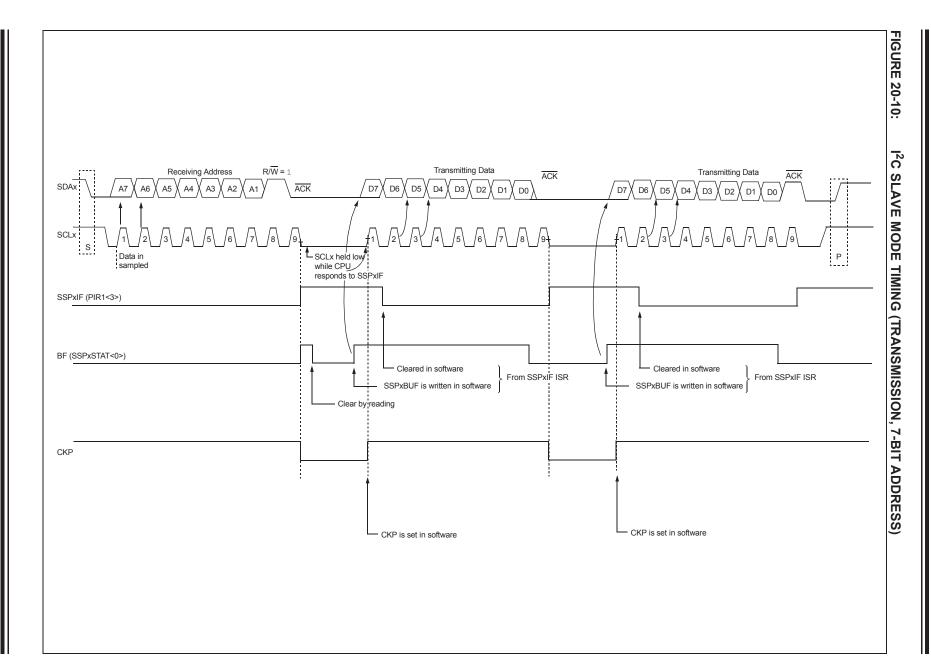

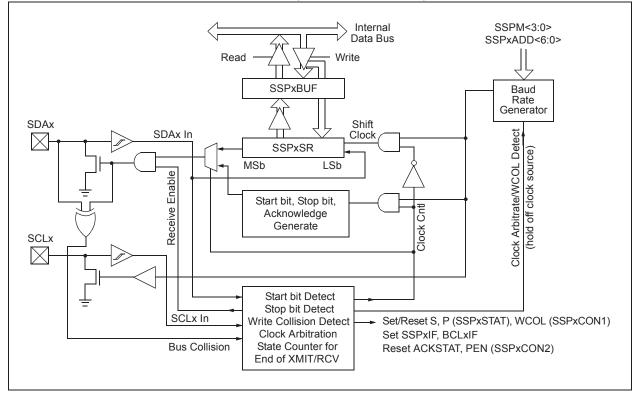

Note: The MSSP module, when configured in I<sup>2</sup>C Master mode, does not allow queueing of events. For instance, the user is not allowed to initiate a Start condition and immediately write the SSPxBUF register to initiate transmission before the Start condition is complete. In this case, the SSPxBUF will not be written to and the WCOL bit will be set, indicating that a write to the SSPxBUF did not occur. The following events will cause the MSSP Interrupt Flag bit, SSPxIF, to be set (and MSSP interrupt, if enabled):

- · Start condition

- Stop condition

- · Data transfer byte transmitted/received

- · Acknowledge transmitted

- Repeated Start

#### FIGURE 20-18: MSSPx BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

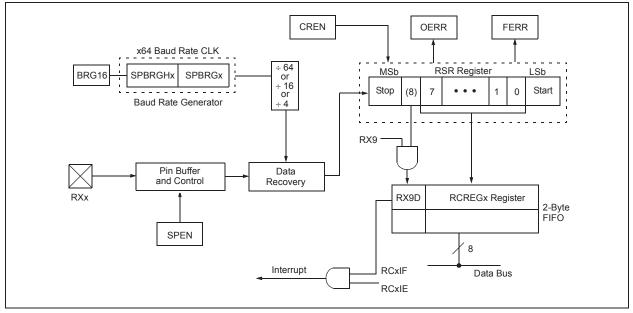

#### 21.2.2 EUSART ASYNCHRONOUS RECEIVER

The receiver block diagram is displayed in Figure 21-6. The data is received on the RXx pin and drives the data recovery block. The data recovery block is actually a high-speed shifter, operating at x16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc. This mode would typically be used in RS-232 systems.

To set up an Asynchronous Reception:

- 1. Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing bit, SYNC, and setting bit, SPEN.

- 3. If interrupts are desired, set enable bit, RCxIE.

- 4. If 9-bit reception is desired, set bit, RX9.

- 5. Enable the reception by setting bit, CREN.

- Flag bit, RCxIF, will be set when reception is complete and an interrupt will be generated if enable bit, RCxIE, was set.

- Read the RCSTAx register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading the RCREGx register.

- 9. If any error occurred, clear the error by clearing enable bit, CREN.

- 10. If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

#### 21.2.3 SETTING UP 9-BIT MODE WITH ADDRESS DETECT

This mode would typically be used in RS-485 systems. To set up an Asynchronous Reception with Address Detect Enable:

- Initialize the SPBRGHx:SPBRGx registers for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are required, set the RCEN bit and select the desired priority level with the RCxIP bit.

- 4. Set the RX9 bit to enable 9-bit reception.

- 5. Set the ADDEN bit to enable address detect.

- 6. Enable reception by setting the CREN bit.

- 7. The RCxIF bit will be set when reception is complete. The interrupt will be Acknowledged if the RCxIE and GIE bits are set.

- 8. Read the RCSTAx register to determine if any error occurred during reception, as well as read bit 9 of data (if applicable).

- 9. Read RCREGx to determine if the device is being addressed.

- 10. If any error occurred, clear the CREN bit.

- 11. If the device has been addressed, clear the ADDEN bit to allow all received data into the receive buffer and interrupt the CPU.

#### FIGURE 21-6: EUSARTX RECEIVE BLOCK DIAGRAM

#### **COMPARATOR VOLTAGE** 24.0 **REFERENCE MODULE**

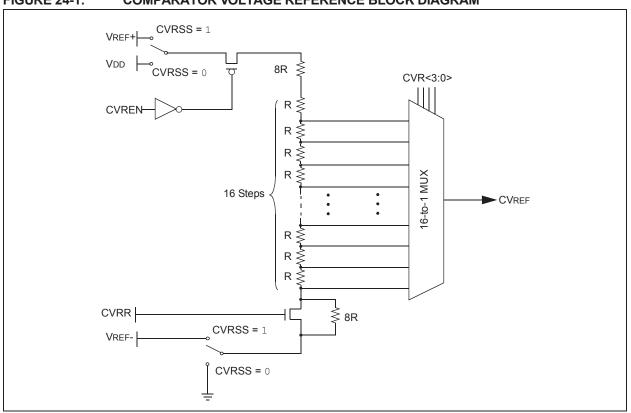

The comparator voltage reference is a 16-tap resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it may also be used independently of them.

Figure 24-1 provides a block diagram of the module. The resistor ladder is segmented to provide two ranges of CVREF values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/VSS or an external voltage reference.

#### FIGURE 24-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

#### 24.2 Voltage Reference Accuracy/Error

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (see Figure 24-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the CVREF output changes with fluctuations in that source. The tested absolute accuracy of the voltage reference can be found in Section 30.0 "Electrical Characteristics".

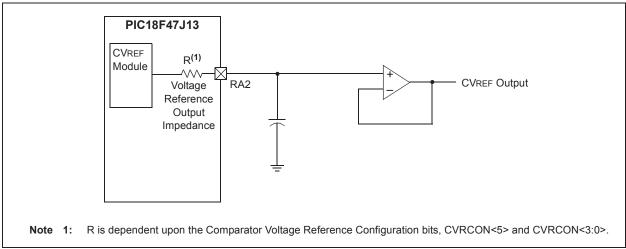

#### 24.3 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the CVROE bit is set. Enabling the voltage reference output onto RA2 when it is configured as a digital input will increase current consumption. Connecting RA2 as a digital output with CVRSS enabled will also increase current consumption. The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, a buffer must be used on the voltage reference output for external connections to VREF. See Figure 24-2 for an example buffering technique.

# 24.4 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

#### 24.5 Effects of a Reset

A device Reset disables the voltage reference by clearing bit, CVREN (CVRCON<7>). This Reset also disconnects the reference from the RA2 pin by clearing bit, CVROE (CVRCON<6>) and selects the high-voltage range by clearing bit, CVRR (CVRCON<5>). The CVR value select bits are also cleared.

| Name   | Bit 7                | Bit 6                | Bit 5                | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|--------|----------------------|----------------------|----------------------|--------|--------|--------|--------|--------|

| CVRCON | CVREN                | CVROE                | CVRR                 | CVRSS  | CVR3   | CVR2   | CVR1   | CVR0   |

| CM1CON | CON                  | COE                  | CPOL                 | EVPOL1 | EVPOL0 | CREF   | CCH1   | CCH0   |

| CM2CON | CON                  | COE                  | CPOL                 | EVPOL1 | EVPOL0 | CREF   | CCH1   | CCH0   |

| CM3CON | CON                  | COE                  | CPOL                 | EVPOL1 | EVPOL0 | CREF   | CCH1   | CCH0   |

| TRISA  | TRISA7               | TRISA6               | TRISA5               | —      | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| ANCON0 | PCFG7 <sup>(1)</sup> | PCFG6 <sup>(1)</sup> | PCFG5 <sup>(1)</sup> | PCFG4  | PCFG3  | PCFG2  | PCFG1  | PCFG0  |

**Legend:** — = unimplemented, read as '0', r = reserved. Shaded cells are not used with the comparator voltage reference.

Note 1: These bits are only available on 44-pin devices.

# PIC18F47J13 FAMILY

| 1                   | Multiply I                                                                          | Multiply Literal with W                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|---------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                     | MULLW                                                                               | k                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| ds:                 | $0 \le k \le 25$                                                                    | $0 \le k \le 255$                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| on:                 | (W) x k $\rightarrow$                                                               | PRODH:                                                                                                                                                                                                                                                                                          | PRODL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| ffected:            | None                                                                                |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |