Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                  |

| Data Converters            | A/D 10x10b/12b                                                              |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26j13-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                 | Pin N      | Pin Number  |             | Buffer        |                                                                      |

|---------------------------------|------------|-------------|-------------|---------------|----------------------------------------------------------------------|

| Pin Name                        | 44-<br>QFN | 44-<br>TQFP | Pin<br>Type | Туре          | Description                                                          |

|                                 |            |             |             |               | PORTB is a bidirectional I/O port. PORTB can be                      |

|                                 |            |             |             |               | software programmed for internal weak pull-ups or                    |

|                                 |            |             |             |               | all inputs.                                                          |

| RB0/AN12/C3IND/INT0/RP3         | 9          | 8           |             |               |                                                                      |

| RB0                             |            |             | I/O         | TTL/DIG       | 8                                                                    |

| AN12                            |            |             |             | Analog        | Analog Input 12.                                                     |

| C3IND                           |            |             |             | Analog        | Comparator 3 Input D.                                                |

| INT0                            |            |             |             | ST            | External Interrupt 0.                                                |

| RP3                             |            |             | I/O         | ST/DIG        | Remappable Peripheral Pin 3 input/output.                            |

| RB1/AN10/C3INC/PMBE/RTCC/       | 10         | 9           |             |               |                                                                      |

| RP4                             |            |             |             |               |                                                                      |

| RB1                             |            |             | I/O         | TTL/DIG       | 5                                                                    |

| AN10                            |            |             |             | Analog        | Analog Input 10.                                                     |

| C3INC                           |            |             |             | Analog        | Comparator 3 Input C.                                                |

| PMBE <sup>(2)</sup>             |            |             | 0           | DIG           | Parallel Master Port byte enable.                                    |

| RTCC                            |            |             | 0           | DIG           | Asynchronous serial transmit data output.                            |

| RP4                             |            |             | I/O         | ST/DIG        | Remappable Peripheral Pin 4 input/output.                            |

| RB2/AN8/C2INC/CTED1/PMA3/       | 11         | 10          |             |               |                                                                      |

| REFO/RP5                        |            |             |             |               |                                                                      |

| RB2                             |            |             | I/O         | TTL/DIG       | 0                                                                    |

| AN8                             |            |             |             | Analog        | Analog Input 8.                                                      |

| C2INC                           |            |             |             | Analog        | Comparator 2 Input C.                                                |

| CTED1<br>PMA3 <sup>(2)</sup>    |            |             |             | ST            | CTMU Edge 1 input.                                                   |

| REFO                            |            |             | 0           | DIG           | Parallel Master Port address.                                        |

| REFO<br>RP5                     |            |             | 0<br>1/0    | DIG<br>ST/DIG | Reference output clock.<br>Remappable Peripheral Pin 5 input/output. |

| KF3                             |            |             | 1/0         | 31/DIG        | Remappable Peripheral Pill 5 inputoulput.                            |

| RB3/AN9/C3INA/CTED2/PMA2/       | 12         | 11          |             |               |                                                                      |

| RP6<br>RB3                      |            |             | I/O         | TTL/DIG       | Digital I/O.                                                         |

| AN9                             |            |             |             | Analog        | Analog Input 9.                                                      |

| C3INA                           |            |             | i           | Analog        | Comparator 3 Input A.                                                |

| CTED2                           |            |             | i           | ST            | CTMU Edge 2 input.                                                   |

| PMA2 <sup>(2)</sup>             |            |             | 0           | DIG           | Parallel Master Port address.                                        |

| RP6                             |            |             | I/O         | ST/DIG        | Remappable Peripheral Pin 6 input/output.                            |

| Legend: TTL = TTL compatible i  | input      |             |             |               | CMOS = CMOS compatible input or output                               |

| ST = Schmitt Trigger i          |            | h CMO       | S level     | s             | Analog = Analog input                                                |

| I = Input                       | -          |             |             |               | O = Output                                                           |

| P = Power                       |            |             |             |               | OD = Open-Drain (no P diode to VDD)                                  |

| DIG = Digital output            |            |             |             |               | I <sup>2</sup> C = Open-Drain, I <sup>2</sup> C specific             |

| Note 1: RA7 and RA6 will be dis | sabled i   | f OSC1      | and O       | SC2 are i     | used for the clock function.                                         |

| 2: Available only on 44-pin     | device     | s (PIC1     | 8F46J       | 13, PIC18     | 3F47J13, PIC18LF46J13 and PIC18LF47J13).                             |

|                                 |            |             |             |               | ,                                                                    |

## TABLE 1-4: PIC18F4XJ13 PINOUT I/O DESCRIPTIONS (CONTINUED)

**3:** 5.5V tolerant.

|                                                                        | Pin Number        |                   |            | Buffer                   |                                                                               |

|------------------------------------------------------------------------|-------------------|-------------------|------------|--------------------------|-------------------------------------------------------------------------------|

| Pin Name                                                               | 44-<br>QFN        | 44-<br>TQFP       | Type Type  |                          | Description                                                                   |

|                                                                        |                   |                   |            |                          | PORTD is a bidirectional I/O port.                                            |

| RD0/PMD0/SCL2<br>RD0<br>PMD0                                           | 38 <sup>(3)</sup> | 38 <sup>(3)</sup> | I/O<br>I/O | ST/DIG<br>ST/TTL/<br>DIG | Digital I/O.<br>Parallel Master Port data.                                    |

| SCL2                                                                   |                   |                   | I/O        | I <sup>2</sup> C         | I <sup>2</sup> C data input/output.                                           |

| RD1/PMD1/SDA2<br>RD1<br>PMD1                                           | 39 <b>(3</b> )    | 39 <b>(3)</b>     | I/O<br>I/O | ST/DIG<br>ST/TTL/<br>DIG | Digital I/O.<br>Parallel Master Port data.                                    |

| SDA2                                                                   |                   |                   | I/O        | I <sup>2</sup> C         | I <sup>2</sup> C data input/output.                                           |

| RD2/PMD2/RP19<br>RD2<br>PMD2                                           | 40 <sup>(3)</sup> | 40 <sup>(3)</sup> | I/O<br>I/O | ST/DIG<br>ST/TTL/        | Digital I/O.<br>Parallel Master Port data.                                    |

|                                                                        |                   |                   |            | DIG                      |                                                                               |

| RP19                                                                   | (2)               | (0)               | I/O        | ST/DIG                   | Remappable Peripheral Pin 19 input/output.                                    |

| RD3/PMD3/RP20<br>RD3<br>PMD3                                           | 41 <sup>(3)</sup> | 41 <sup>(3)</sup> | I/O<br>I/O | ST/DIG<br>ST/TTL/<br>DIG | Digital I/O.<br>Parallel Master Port data.                                    |

| RP20                                                                   |                   |                   | I/O        | ST/DIG                   | Remappable Peripheral Pin 20 input/output.                                    |

| RD4/PMD4/RP21<br>RD4<br>PMD4                                           | 2 <sup>(3)</sup>  | 2 <sup>(3)</sup>  | I/O<br>I/O | ST/DIG<br>ST/TTL/<br>DIG | Digital I/O.<br>Parallel Master Port data.                                    |

| RP21                                                                   |                   |                   | I/O        | ST/DIG                   | Remappable Peripheral Pin 21 input/output.                                    |

| RD5/PMD5/RP22<br>RD5<br>PMD5                                           | 3(3)              | 3(3)              | I/O<br>I/O | ST/DIG<br>ST/TTL/<br>DIG | Digital I/O.<br>Parallel Master Port data.                                    |

| RP22                                                                   |                   |                   | I/O        | ST/DIG                   | Remappable Peripheral Pin 22 input/output.                                    |

| RD6/PMD6/RP23<br>RD6<br>PMD6                                           | 4(3)              | 4(3)              | I/O<br>I/O | ST/DIG<br>ST/TTL/<br>DIG | Digital I/O.<br>Parallel Master Port data.                                    |

| RP23                                                                   |                   |                   | I/O        | ST/DIG                   | Remappable Peripheral Pin 23 input/output.                                    |

| RD7/PMD7/RP24<br>RD7<br>PMD7                                           | 5 <sup>(3)</sup>  | 5 <sup>(3)</sup>  | 1/0<br>1/0 | ST/DIG<br>ST/TTL/        | Digital I/O.<br>Parallel Master Port data.                                    |

| RP24                                                                   |                   |                   | I/O        | DIG<br>ST/DIG            | Remappable Peripheral Pin 24 input/output.                                    |

| Legend: TTL = TTL compatible i<br>ST = Schmitt Trigger in<br>I = Input |                   | h CMO             |            | s                        | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output |

| P = Power<br>DIG = Digital output                                      |                   |                   |            |                          | OD = Open-Drain (no P diode to VDD)<br>$l^2C$ = Open-Drain, $l^2C$ specific   |

| - ·                                                                    | abled if          | OSC1              | and O      |                          | used for the clock function.                                                  |

#### TABLE 1-4: PIC18F4XJ13 PINOUT I/O DESCRIPTIONS (CONTINUED)

2: Available only on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

3: 5.5V tolerant.

## 5.5 Configuration Mismatch (CM)

The Configuration Mismatch (CM) Reset is designed to detect, and attempt to recover from, random memory corrupting events. These include Electrostatic Discharge (ESD) events, which can cause widespread single bit changes throughout the device and result in catastrophic failure.

In PIC18FXXJ Flash devices, the device Configuration registers (located in the configuration memory space) are continuously monitored during operation by comparing their values to complimentary shadow registers. If a mismatch is detected between the two sets of registers, a CM Reset automatically occurs. These events are captured by the CM bit (RCON<5>). The state of the bit is set to '0' whenever a CM event occurs; it does not change for any other Reset event.

A CM Reset behaves similarly to MCLR, RESET instruction, WDT time-out or Stack Event Resets. As with all hard and power Reset events, the device Configuration Words are reloaded from the Flash Configuration Words in program memory as the device restarts.

#### 5.6 Power-up Timer (PWRT)

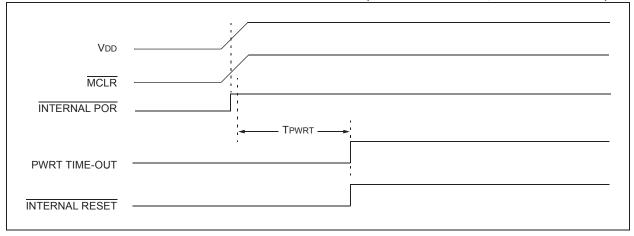

PIC18F47J13 Family devices incorporate an on-chip PWRT to help regulate the POR process. The PWRT is always enabled. The main function is to ensure that the device voltage is stable before code is executed.

The Power-up Timer (PWRT) of the PIC18F47J13 Family devices is a counter which uses the INTRC source as the clock input. While the PWRT is counting, the device is held in Reset.

The power-up time delay depends on the INTRC clock and will vary from chip-to-chip due to temperature and process variation. See DC parameter 33 (TPWRT) for details.

#### 5.6.1 TIME-OUT SEQUENCE

The PWRT time-out is invoked after the POR pulse has cleared. The total time-out will vary based on the status of the PWRT. Figure 5-2, Figure 5-3, Figure 5-4 and Figure 5-5 all depict time-out sequences on power-up with the PWRT.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the PWRT will expire. Bringing  $\overline{\text{MCLR}}$  high will begin execution immediately if a clock source is available (Figure 5-4). This is useful for testing purposes or to synchronize more than one PIC18F device operating in parallel.

#### FIGURE 5-2: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD, VDD RISE < TPWRT)

## 7.5 Writing to Flash Program Memory

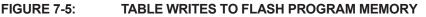

The programming block is 32 words or 64 bytes. Programming one word or 2 bytes at a time is also supported.

Table writes are used internally to load the holding registers needed to program the Flash memory. There are 64 holding registers used by the table writes for programming.

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction may need to be executed 64 times for each programming operation (if WPROG = 0). All of the table write operations will essentially be short writes because only the holding registers are written. At the end of updating the 64 holding registers, the EECON1 register must be written to in order to start the programming operation with a long write.

The long write is necessary for programming the internal Flash. Instruction execution is Halted while in a long write cycle. The long write will be terminated by the internal programming timer.

The on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

- Note 1: Unlike previous PIC<sup>®</sup> devices, devices of the PIC18F47J13 Family do not reset the holding registers after a write occurs. The holding registers must be cleared or overwritten before a programming sequence.

- 2: To maintain the endurance of the program memory cells, each Flash byte should not be programmed more than once between erase operations. Before attempting to modify the contents of the target cell a second time, an erase of the target page, or a bulk erase of the entire memory, must be performed.

#### 7.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 1024 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load the Table Pointer register with address being erased.

- 4. Execute the erase procedure.

- 5. Load the Table Pointer register with the address of the first byte being written, minus 1.

- 6. Write the 64 bytes into the holding registers with auto-increment.

- Set the WREN bit (EECON1<2>) to enable byte writes.

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write 0AAh to EECON2.

- 11. Set the WR bit; this will begin the write cycle.

- 12. The CPU will stall for the duration of the write for TIW (see parameter D133A).

- 13. Re-enable interrupts.

- 14. Repeat Steps 6 through 13 until all 1024 bytes are written to program memory.

- 15. Verify the memory (table read).

An example of the required code is provided in Example 7-3 on the following page.

Note: Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the 64 bytes in the holding register.

| R/W-0         | R/W-0          | R-0                                | R-0              | R/W-0             | R/W-0           | R/W-0           | R/W-0  |

|---------------|----------------|------------------------------------|------------------|-------------------|-----------------|-----------------|--------|

| SSP2IF        | BCL2IF         | RC2IF                              | TX2IF            | TMR4IF            | CTMUIF          | TMR3GIF         | RTCCIF |

| bit 7         |                |                                    |                  | ·                 |                 | •               | bit 0  |

|               |                |                                    |                  |                   |                 |                 |        |

| Legend:       |                |                                    |                  |                   |                 |                 |        |

| R = Readable  | e bit          | W = Writable                       |                  | U = Unimplen      | nented bit, rea | d as '0'        |        |

| -n = Value at | POR            | '1' = Bit is set                   |                  | '0' = Bit is clea | ared            | x = Bit is unkn | own    |

| bit 7         | SSP2IF: Mag    | ster Synchrono                     | is Serial Port 2 | PInterrunt Flag   | hit             |                 |        |

|               |                | ismission/recep                    |                  |                   |                 | e)              |        |

|               |                | to transmit/rece                   | •                |                   |                 | - /             |        |

| bit 6         | BCL2IF: Bus    | Collision Interi                   | upt Flag bit (N  | SSP2 module)      |                 |                 |        |

|               |                | ollision occurred                  | •                | red in software   | )               |                 |        |

|               |                | collision occurre                  | -                |                   |                 |                 |        |

| bit 5         |                | ART2 Receive                       |                  |                   |                 |                 |        |

|               |                | SART2 receive                      |                  |                   | ed when RCRE    | G2 is read)     |        |

| bit 4         |                | ART2 Transmit                      | 1,3              |                   |                 |                 |        |

|               |                |                                    |                  |                   | eared when T>   | REG2 is writter | ר)     |

|               | 0 = The EUS    | SART2 transmit                     | buffer is full   |                   |                 |                 |        |

| bit 3         | TMR4IF: TM     | R4 to PR4 Mate                     | ch Interrupt Fla | ıg bit            |                 |                 |        |

|               |                | to PR4 match                       | ```              | t be cleared in s | software)       |                 |        |

|               |                | 4 to PR4 match                     |                  |                   | •.              |                 |        |

| bit 2         |                | arge Time Mea                      |                  |                   |                 |                 |        |

|               |                | J event has occ<br>J event has not | `                | cleared in som    | ware)           |                 |        |

| bit 1         | TMR3GIF: ⊤     | imer3 Gate Eve                     | nt Interrupt Fla | ag bit            |                 |                 |        |

|               |                | 3 gate event co                    | •                | •                 | oftware)        |                 |        |

|               | 0 = No Time    | er3 gate event c                   | ompleted         |                   |                 |                 |        |

| bit 0         |                | CC Interrupt Fla                   | •                |                   |                 |                 |        |

|               | 1 = An RTCC    | C interrupt occu                   | rred (must be o  | cleared in softw  | are)            |                 |        |

|               | $0 = N_0 RTCO$ | C interrupt occu                   | rred             |                   |                 |                 |        |

| TADLE 10-3. F  |          |                 |     |                                                             | ,                                                                 |

|----------------|----------|-----------------|-----|-------------------------------------------------------------|-------------------------------------------------------------------|

| Pin            | Function | TRIS<br>Setting | I/O | I/O<br>Type                                                 | Description                                                       |

| RA5/AN4/C1INC/ | RA5      | 0               | 0   | DIG                                                         | LATA<5> data output; not affected by analog input.                |

| SS1/HLVDIN/    |          | 1               | Ι   | PORTA<5> data input; disabled when analog input is enabled. |                                                                   |

| RP2            | AN4      | 1               | Ι   | ANA                                                         | A/D Input Channel 4. Default configuration on POR.                |

|                | C1INC    | 0               | 0   | DIG                                                         | Comparator 1 Input C.                                             |

|                | SS1      | 1               | Ι   | TTL                                                         | Slave select input for MSSP1.                                     |

|                | HLVDIN   | 1               | Ι   | ANA                                                         | High/Low-Voltage Detect external trip point reference input.      |

| RP2            |          | 1               | Ι   | ST                                                          | Remappable Peripheral Pin 2 input.                                |

|                |          | 0               | 0   | DIG                                                         | Remappable Peripheral Pin 2 output.                               |

| OSC2/CLKO/     | OSC2     | х               | 0   | ANA                                                         | Main oscillator feedback output connection (HS mode).             |

| RA6            | CLKO     | Х               | 0   | DIG                                                         | System cycle clock output (Fosc/4) in RC and EC Oscillator modes. |

|                | RA6      | 1               | Ι   | TTL                                                         | PORTA<6> data input.                                              |

|                |          | 0               | 0   | DIG                                                         | LATA<6> data output.                                              |

| OSC1/CLKI/RA7  | OSC1     | 1               | Ι   | ANA                                                         | Main oscillator input connection.                                 |

|                | CLKI     | 1               | I   | ANA                                                         | Main clock input connection.                                      |

|                | RA7      | 1               | Ι   | TTL                                                         | PORTA<6> data input.                                              |

|                |          | 0               | 0   | DIG                                                         | LATA<6> data output.                                              |

#### TABLE 10-3: PORTA I/O SUMMARY (CONTINUED)

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRISx bit does not affect port direction or is overridden for this option)

**Note 1:** This bit is only available on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

| TABLE 10-4: SUMMAI | Y OF REGISTERS | ASSOCIATED WITH PORTA |

|--------------------|----------------|-----------------------|

|--------------------|----------------|-----------------------|

| Name    | Bit 7                | Bit 6                | Bit 5                | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  |

|---------|----------------------|----------------------|----------------------|--------|--------|--------|---------|--------|

| PORTA   | RA7                  | RA6                  | RA5                  |        | RA3    | RA2    | RA1     | RA0    |

| LATA    | LAT7                 | LAT6                 | LAT5                 | _      | LAT3   | LAT2   | LAT1    | LAT0   |

| TRISA   | TRIS7                | TRIS6                | TRISA5               | —      | TRISA3 | TRISA2 | TRISA1  | TRISA0 |

| ANCON0  | PCFG7 <sup>(1)</sup> | PCFG6 <sup>(1)</sup> | PCFG5 <sup>(1)</sup> | PCFG4  | PCFG3  | PCFG2  | PCFG1   | PCFG0  |

| CMxCON  | CON                  | COE                  | CPOL                 | EVPOL1 | EVPOL0 | CREF   | CCH1    | CCH0   |

| CVRCON  | CVREN                | CVROE                | CVRR                 | CVRSS  | CVR3   | CVR2   | CVR1    | CVR0   |

| WDTCON  | REGSLP               | LVDSTAT              | ULPLVL               | VBGOE  | DS     | ULPEN  | ULPSINK | SWDTEN |

| HLVDCON | VDIRMAG              | BGVST                | IRVST                | HLVDEN | HLVDL3 | HLVDL2 | HLVDL1  | HLVDL0 |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by PORTA.

**Note 1:** These bits are only available in 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

| Pin               | Function | TRIS<br>Setting | I/O | l/O<br>Type | Description                                                                         |

|-------------------|----------|-----------------|-----|-------------|-------------------------------------------------------------------------------------|

| RB7/CCP7/         | RB7      | 0               | 0   | DIG         | LATB<7> data output.                                                                |

| KBI3/PGD/<br>RP10 |          | 1               | Ι   | TTL         | PORTB<7> data input; weak pull-up when the $\overline{\text{RBPU}}$ bit is cleared. |

|                   | CCP7     |                 | Ι   | ST          | Capture input.                                                                      |

|                   |          | 0               | 0   | DIG         | Compare/PWM output.                                                                 |

|                   | KBI3     | 1               | 0   | TTL         | Interrupt-on-change pin.                                                            |

|                   | PGD      | х               | 0   | DIG         | Serial execution data output for ICSP and ICD operation. <sup>(2)</sup>             |

|                   |          | х               | Ι   | ST          | Serial execution data input for ICSP and ICD operation. <sup>(2)</sup>              |

| <b>RP10</b> 1     |          | 1               | Ι   | ST          | Remappable Peripheral Pin 10 input.                                                 |

|                   |          | 0               | 0   | DIG         | Remappable Peripheral Pin 10 output.                                                |

TABLE 10-5: PORTB I/O SUMMARY (CONTINUED)

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRISx bit does not affect port direction or is overridden for this option)

**Note 1:** Pins are configured as analog inputs by default on POR. Using these pins for digital inputs requires setting the appropriate bits in the ANCON1 register.

- **2:** All other pin functions are disabled when ICSP<sup>™</sup> or ICD is enabled.

- 3: Only on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

- 4: Only on 28-pin devices (PIC18F26J13, PIC18F27J13, PIC18LF26J13 and PIC18LF27J13).

| Name    | Bit 7    | Bit 6     | Bit 5   | Bit 4         | Bit 3   | Bit 2     | Bit 1     | Bit 0   |

|---------|----------|-----------|---------|---------------|---------|-----------|-----------|---------|

| PORTB   | RB7      | RB6       | RB5     | RB4           | RB3     | RB2       | RB1       | RB0     |

| LATB    | LATB7    | LATB6     | LATB5   | LATB4         | LATB3   | LATB2     | LATB1     | LATB0   |

| TRISB   | TRISB7   | TRISB6    | TRISB5  | TRISB4        | TRISB3  | TRISB2    | TRISB1    | TRISB0  |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE  | <b>INTOIE</b> | RBIE    | TMR0IF    | INT0IF    | RBIF    |

| INTCON2 | RBPU     | INTEDG0   | INTEDG1 | INTEDG2       | INTEDG3 | TMR0IP    | INT3IP    | RBIP    |

| INTCON3 | INT2IP   | INT1IP    | INT3IE  | INT2IE        | INT1IE  | INT3IF    | INT2IF    | INT1IF  |

| ANCON1  | VBGEN    | —         | —       | PCFG12        | PCFG11  | PCFG10    | PCFG9     | PCFG8   |

| REFOCON | ROON     | —         | ROSSLP  | ROSEL         | RODIV3  | RODIV2    | RODIV1    | RODIV0  |

| CM3CON  | CON      | COE       | CPOL    | EVPOL1        | EVPOL0  | CREF      | CCH1      | CCH0    |

| PADCFG1 | _        | —         | —       | —             | _       | RTSECSEL1 | RTSECSEL0 | PMPTTL  |

| RTCCFG  | RTCEN    | _         | RTCWREN | RTCSYNC       | HALFSEC | RTCOE     | RTCPTR1   | RTCPTR0 |

#### TABLE 10-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTB.

#### 10.7.3.3 Mapping Limitations

The control schema of the PPS is extremely flexible. Other than systematic blocks that prevent signal contention caused by two physical pins being configured as the same functional input or two functional outputs configured as the same pin, there are no hardware enforced lockouts. The flexibility extends to the point of allowing a single input to drive multiple peripherals or a single functional output to drive multiple output pins.

## 10.7.4 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC18F devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- Continuous state monitoring

- Configuration bit remapping lock

### 10.7.4.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes will appear to execute normally, but the contents of the registers will remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (PPSCON<0>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear IOLOCK, a specific command sequence must be executed:

- 1. Write 55h to EECON2<7:0>.

- 2. Write AAh to EECON2<7:0>.

- 3. Clear (or set) IOLOCK as a single operation.

IOLOCK remains in one state until changed. This allows all of the PPS registers to be configured with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

#### 10.7.4.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a Configuration Mismatch Reset will be triggered.

### 10.7.4.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (CON-FIG3H<0>) Configuration bit blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure will not execute and the PPS Control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session. Programming IOL1WAY allows users unlimited access (with the proper use of the unlock sequence) to the PPS registers.

#### 10.7.5 CONSIDERATIONS FOR PERIPHERAL PIN SELECTION

The ability to control Peripheral Pin Selection introduces several considerations into application design that could be overlooked. This is particularly true for several common peripherals that are available only as remappable peripherals.

The main consideration is that the PPS is not available on default pins in the device's default (Reset) state. Since all RPINRx registers reset to '11111' and all RPORx registers reset to '00000', all PPS inputs are tied to RP31 and all PPS outputs are disconnected.

Note: In tying PPS inputs to RP31, RP31 does not have to exist on a device for the registers to be reset to it.

This situation requires the user to initialize the device with the proper peripheral configuration before any other application code is executed. Since the IOLOCK bit resets in the unlocked state, it is not necessary to execute the unlock sequence after the device has come out of Reset.

For application safety, however, it is best to set IOLOCK and lock the configuration after writing to the control registers.

The unlock sequence is timing-critical. Therefore, it is recommended that the unlock sequence be executed as an assembly language routine with interrupts temporarily disabled. If the bulk of the application is written in C or another high-level language, the unlock sequence should be performed by writing in-line assembly.

## REGISTER 11-4: PMMODEL: PARALLEL PORT MODE REGISTER LOW BYTE (BANKED F5Ch)<sup>(1)</sup>

| R/W-0                 | R/W-0                 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0                 | R/W-0                 |

|-----------------------|-----------------------|--------|--------|--------|--------|-----------------------|-----------------------|

| WAITB1 <sup>(2)</sup> | WAITB0 <sup>(2)</sup> | WAITM3 | WAITM2 | WAITM1 | WAITM0 | WAITE1 <sup>(2)</sup> | WAITE0 <sup>(2)</sup> |

| bit 7                 |                       |        |        |        |        |                       | bit 0                 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-6 | WAITB<1:0>: Data Setup to Read/Write Wait State Configuration bits <sup>(2)</sup><br>11 = Data Wait of 4 Tcy; multiplexed address phase of 4 Tcy<br>10 = Data Wait of 3 Tcy; multiplexed address phase of 3 Tcy<br>01 = Data Wait of 2 Tcy; multiplexed address phase of 2 Tcy<br>00 = Data Wait of 1 Tcy; multiplexed address phase of 1 Tcy |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-2 | WAITM<3:0>: Read to Byte Enable Strobe Wait State Configuration bits<br>1111 = Wait of additional 15 Tcy                                                                                                                                                                                                                                      |

|         | 0001 = Wait of additional 1 Tcy<br>0000 = No additional Wait cycles (operation forced into one Tcy)                                                                                                                                                                                                                                           |

| bit 1-0 | WAITE<1:0>: Data Hold After Strobe Wait State Configuration bits <sup>(2)</sup><br>11 = Wait of 4 Tcy<br>10 = Wait of 3 Tcy<br>01 = Wait of 2 Tcy<br>00 = Wait of 1 Tcy                                                                                                                                                                       |

| Note 1  | This register is only systemed on 44 nin devises                                                                                                                                                                                                                                                                                              |

Note 1: This register is only available on 44-pin devices.

2: WAITBx and WAITEx bits are ignored whenever WAITM<3:0> = 0000.

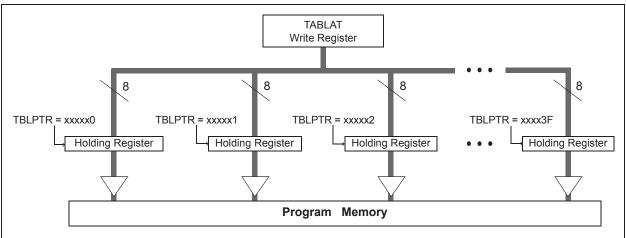

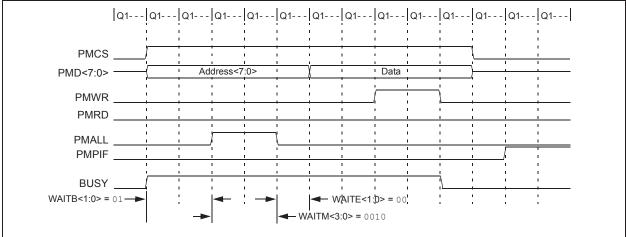

## FIGURE 11-16: WRITE TIMING, 8-BIT DATA, WAIT STATES ENABLED, PARTIALLY MULTIPLEXED ADDRESS

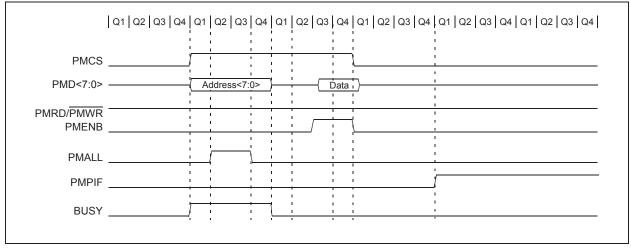

## FIGURE 11-17: READ TIMING, 8-BIT DATA, PARTIALLY MULTIPLEXED ADDRESS, ENABLE STROBE

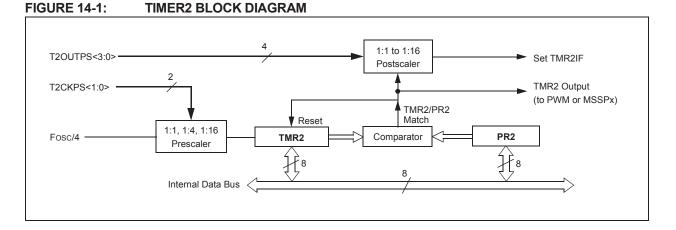

## 14.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2 to PR2 match) provides the input for the 4-bit output counter/postscaler. This counter generates the TMR2 Match Interrupt Flag, which is latched in TMR2IF (PIR1<1>). The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE (PIE1<1>).

A range of 16 postscaler options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0> (T2CON<6:3>).

## 14.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the ECCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP modules operating in SPI mode. Additional information is provided in Section 20.0 "Master Synchronous Serial Port (MSSP) Module".

#### TABLE 14-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| Name   | Bit 7                | Bit 6       | Bit 5                  | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   |  |  |  |

|--------|----------------------|-------------|------------------------|----------|----------|--------|---------|---------|--|--|--|

| INTCON | GIE/GIEH             | PEIE/GIEL   | TMR0IE                 | INT0IE   | RBIE     | TMR0IF | INT0IF  | RBIF    |  |  |  |

| PIR1   | PMPIF <sup>(1)</sup> | ADIF        | RC1IF                  | TX1IF    | SSP1IF   | CCP1IF | TMR2IF  | TMR1IF  |  |  |  |

| PIE1   | PMPIE <sup>(1)</sup> | ADIE        | RC1IE                  | TX1IE    | SSP1IE   | CCP1IE | TMR2IE  | TMR1IE  |  |  |  |

| IPR1   | PMPIP <sup>(1)</sup> | ADIP        | RC1IP                  | TX1IP    | SSP1IP   | CCP1IP | TMR2IP  | TMR1IP  |  |  |  |

| TMR2   | Timer2 Register      |             |                        |          |          |        |         |         |  |  |  |

| T2CON  | —                    | T2OUTPS3    | T2OUTPS2               | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |  |  |  |

| PR2    | Timer2 Peri          | od Register | Timer2 Period Register |          |          |        |         |         |  |  |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

**Note 1:** These bits are only available in 44-pin devices.

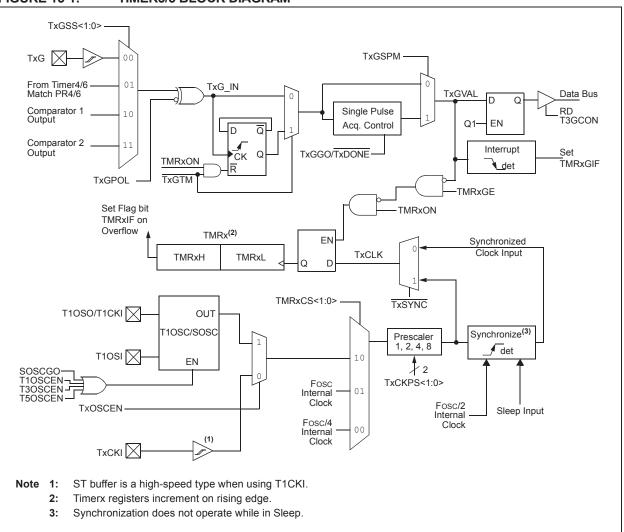

## 15.0 TIMER3/5 MODULE

The Timer3/5 timer/counter modules incorporate these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMRxH and TMRxL)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt-on-overflow

- Module Reset on ECCP Special Event Trigger

**Note:** Throughout this section, generic references are used for register and bit names that are the same – except for an 'x' variable that indicates the item's association with the Timer3 or Timer5 module. For example, the control register is named TxCON, and refers to T3CON and T5CON.

A simplified block diagram of the Timer3/5 module is shown in Figure 15-1.

The Timer3/5 module is controlled through the TxCON register (Register 15-1). It also selects the clock source options for the ECCP modules. (For more information, see Section 19.1.1 "ECCP Module and Timer Resources".)

The Fosc clock source should not be used with the ECCP capture/compare features. If the timer will be used with the capture or compare features, always select one of the other timer clocking options.

The operating mode is determined by the clock select

bits, TMRxCSx (TxCON<7:6>). When the TMRxCSx bits

are cleared (= 00), Timer3/5 increments on every internal

instruction cycle (Fosc/4). When TMRxCSx = 01, the Timer3/5 clock source is the system clock (Fosc), and

when it is '10', Timer3/5 works as a counter from the

external clock from the TxCKI pin (on the rising edge after

the first falling edge) or the Timer1 oscillator.

## 15.2 Timer3/5 Operation

Timer3 and Timer5 can operate in these modes:

- Timer

- Synchronous Counter

- Asynchronous Counter

- Timer with Gated Control

## FIGURE 15-1: TIMER3/5 BLOCK DIAGRAM

## REGISTER 26-2: CTMUCONL: CTMU CONTROL REGISTER LOW (ACCESS FB2h)

| R/W-0         | R/W-0                                              | R/W-0            | R/W-0           | R/W-0             | R/W-0            | R/W-x              | R/W-x    |  |  |

|---------------|----------------------------------------------------|------------------|-----------------|-------------------|------------------|--------------------|----------|--|--|

| EDG2POL       | EDG2SEL1                                           | EDG2SEL0         | EDG1POL         | EDG1SEL1          | EDG1SEL0         | EDG2STAT           | EDG1STAT |  |  |

| bit 7         | -                                                  | •                |                 | •                 | •                | •                  | bit 0    |  |  |

|               |                                                    |                  |                 |                   |                  |                    |          |  |  |

| Legend:       |                                                    |                  |                 |                   |                  |                    |          |  |  |

| R = Readable  | e bit                                              | W = Writable I   | oit             | U = Unimplem      | nented bit, read | l as '0'           |          |  |  |

| -n = Value at | POR                                                | '1' = Bit is set |                 | '0' = Bit is clea | ared             | x = Bit is unknown |          |  |  |

|               |                                                    |                  |                 |                   |                  |                    |          |  |  |

| bit 7         | EDG2POL: E                                         | dge 2 Polarity   | Select bit      |                   |                  |                    |          |  |  |

|               |                                                    | s programmed f   |                 |                   |                  |                    |          |  |  |

|               | -                                                  | s programmed f   | -               | -                 |                  |                    |          |  |  |

| bit 6-5       |                                                    | :0>: Edge 2 So   | urce Select bit | S                 |                  |                    |          |  |  |

|               | 11 = CTED1<br>10 = CTED2                           | •                |                 |                   |                  |                    |          |  |  |

|               |                                                    | output compare   | e module        |                   |                  |                    |          |  |  |

|               | 00 = Timer1 r                                      |                  |                 |                   |                  |                    |          |  |  |

| bit 4         | EDG1POL: E                                         | dge 1 Polarity   | Select bit      |                   |                  |                    |          |  |  |

|               | •                                                  | s programmed f   |                 | •                 |                  |                    |          |  |  |

|               | 0 = Edge 1 is                                      | s programmed f   | or a negative e | edge response     |                  |                    |          |  |  |

| bit 3-2       |                                                    | :0>: Edge 1 So   | urce Select bit | S                 |                  |                    |          |  |  |

|               | 11 = CTED1 pin                                     |                  |                 |                   |                  |                    |          |  |  |

|               | 10 = CTED2 pin<br>01 = ECCP1 output compare module |                  |                 |                   |                  |                    |          |  |  |

|               | 00 = Timer1 r                                      |                  | modulo          |                   |                  |                    |          |  |  |

| bit 1         | EDG2STAT: Edge 2 Status bit                        |                  |                 |                   |                  |                    |          |  |  |

|               | 1 = Edge 2 event has occurred                      |                  |                 |                   |                  |                    |          |  |  |

|               | 0 = Edge 2 e                                       | vent has not oc  | curred          |                   |                  |                    |          |  |  |

| bit 0         | EDG1STAT: E                                        | Edge 1 Status b  | it              |                   |                  |                    |          |  |  |

|               |                                                    | vent has occurr  |                 |                   |                  |                    |          |  |  |

|               | 0 = Edge 1 e                                       | vent has not oc  | curred          |                   |                  |                    |          |  |  |

#### 27.7 In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

PIC18F47J13 Family microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

## 27.8 In-Circuit Debugger

When the DEBUG Configuration bit is programmed to a '0', the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB<sup>®</sup> IDE. When the microcontroller has this feature enabled, some resources are not available for general use.

Table 27-4 lists the resources required by the background debugger.

TABLE 27-4: DEBUGGER RESOURCES

| I/O Pins: | RB6, RB7                 |

|-----------|--------------------------|

|           | TOSx registers reserved. |

# PIC18F47J13 FAMILY

| RET   | JRN                                   | Return fro                                                                                                                                 | Return from Subroutine                                                                                                                                        |                                                        |                                          |                                                         |  |  |

|-------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------|---------------------------------------------------------|--|--|

| Synta | ax:                                   | RETURN                                                                                                                                     | {s}                                                                                                                                                           |                                                        |                                          |                                                         |  |  |

| Oper  | ands:                                 | $s \in [0,1]$                                                                                                                              |                                                                                                                                                               |                                                        |                                          |                                                         |  |  |

| Oper  | ation:                                | if s = 1,<br>(WS) $\rightarrow$ W<br>(STATUSS<br>(BSRS) $\rightarrow$                                                                      | $(TOS) \rightarrow PC;$<br>if s = 1,<br>$(WS) \rightarrow W,$<br>$(STATUSS) \rightarrow STATUS,$<br>$(BSRS) \rightarrow BSR,$<br>PCLATU, PCLATH are unchanged |                                                        |                                          |                                                         |  |  |

| Statu | s Affected:                           | None                                                                                                                                       |                                                                                                                                                               |                                                        |                                          |                                                         |  |  |

| Enco  | ding:                                 | 0000                                                                                                                                       | 0000                                                                                                                                                          | 000                                                    | 1                                        | 001s                                                    |  |  |

| Desc  | ription:                              | Return from<br>popped and<br>is loaded in<br>'s'= 1, the of<br>registers, V<br>are loaded<br>registers, V<br>'s' = 0, no of<br>occurs (det | d the top<br>nto the pr<br>contents<br>VS, STAT<br>into their<br>V, STATL<br>update of                                                                        | of the<br>ogram<br>of the<br>USS a<br>corres<br>JS and | stac<br>cou<br>shac<br>and<br>spor<br>BS | ck (TOS)<br>unter. If<br>dow<br>BSRS,<br>nding<br>R. If |  |  |

| Word  | ls:                                   | 1                                                                                                                                          | 1                                                                                                                                                             |                                                        |                                          |                                                         |  |  |

| Cycle | es:                                   | 2                                                                                                                                          | 2                                                                                                                                                             |                                                        |                                          |                                                         |  |  |

| QC    | ycle Activity:                        |                                                                                                                                            |                                                                                                                                                               |                                                        |                                          |                                                         |  |  |

|       | Q1                                    | Q2                                                                                                                                         | Q                                                                                                                                                             | 3                                                      |                                          | Q4                                                      |  |  |

|       | Decode                                | No<br>operation                                                                                                                            | Proce<br>Data                                                                                                                                                 |                                                        | •                                        | OP PC<br>m stack                                        |  |  |

|       | No                                    | No                                                                                                                                         | No                                                                                                                                                            |                                                        |                                          | No                                                      |  |  |

|       | operation                             | operation                                                                                                                                  | operat                                                                                                                                                        | tion                                                   | ор                                       | eration                                                 |  |  |

|       | Example: RETURN<br>After Instruction: |                                                                                                                                            |                                                                                                                                                               |                                                        |                                          |                                                         |  |  |

After Instruction: PC = TOS

| RLCF                               | Rotate Lef                              |                                                                                                                                                                                                               | in Carry                                       | /                                 |  |  |  |

|------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------|--|--|--|

| Syntax:                            | RLCF f                                  | {,d {,a}}                                                                                                                                                                                                     |                                                |                                   |  |  |  |

| Operands:                          | $0 \le f \le 255$                       |                                                                                                                                                                                                               |                                                |                                   |  |  |  |

|                                    | d ∈ [0,1]<br>a ∈ [0,1]                  |                                                                                                                                                                                                               |                                                |                                   |  |  |  |

| Operation:                         | $(f < n >) \rightarrow dest < n + 1 >,$ |                                                                                                                                                                                                               |                                                |                                   |  |  |  |

| operation.                         | $(f<7>) \rightarrow C,$                 |                                                                                                                                                                                                               |                                                |                                   |  |  |  |

|                                    | $(C) \rightarrow dest$                  | <0>                                                                                                                                                                                                           |                                                |                                   |  |  |  |

| Status Affected:                   | C, N, Z                                 |                                                                                                                                                                                                               |                                                |                                   |  |  |  |

| Encoding:                          | 0011                                    | 01da                                                                                                                                                                                                          | ffff                                           | ffff                              |  |  |  |

| Description:                       | one bit to th<br>If 'd' is '0', t       | The contents of register 'f' are rotated<br>one bit to the left through the Carry flag.<br>If 'd' is '0', the result is placed in W. If 'd'<br>is '1', the result is stored back in register<br>'f' (default) |                                                |                                   |  |  |  |

|                                    |                                         | he BSR i                                                                                                                                                                                                      |                                                | is selected.<br>to select the     |  |  |  |

|                                    | in Indexed<br>mode wher<br>Section 28   | led, this i<br>Literal Of<br>never $f \leq s$                                                                                                                                                                 | nstructic<br>fset Ado<br>95 (5Fh)              | on operates<br>fressing<br>). See |  |  |  |

|                                    |                                         |                                                                                                                                                                                                               | ctions i                                       | n Indexed                         |  |  |  |

|                                    | Bit-Oriente                             | set Mode                                                                                                                                                                                                      | ctions i                                       | n Indexed<br>tails.               |  |  |  |

|                                    | Literal Off                             | set Mode                                                                                                                                                                                                      | ctions i<br>" for de                           | n Indexed<br>tails.               |  |  |  |

| Words:                             | Literal Off                             | set Mode                                                                                                                                                                                                      | ctions i<br>" for de                           | n Indexed<br>tails.               |  |  |  |

| Cycles:                            | Literal Off                             | set Mode                                                                                                                                                                                                      | ctions i<br>" for de                           | n Indexed<br>tails.               |  |  |  |

| Cycles:<br>Q Cycle Activity:       | Literal Offs<br>C<br>1<br>1             | set Mode                                                                                                                                                                                                      | ctions i<br>" for de<br>egister f              | n Indexed<br>tails.               |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1 | Literal Offs<br>C<br>1<br>1<br>Q2       | set Mode                                                                                                                                                                                                      | ctions i<br>" for de<br>egister f              | n Indexed<br>tails.               |  |  |  |

| Cycles:<br>Q Cycle Activity:       | Literal Offs<br>C<br>1<br>1             | set Mode                                                                                                                                                                                                      | ctions i<br>"" for de<br>egister f<br>3<br>ess | n Indexed<br>tails.               |  |  |  |

## 30.5 AC (Timing) Characteristics

#### 30.5.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2ppS                | 8                               | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|----------------------------|---------------------------------|-----------|----------------------------------------|

| 2. TppS                    |                                 | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                          |                                 |           |                                        |

| F                          | Frequency                       | Т         | Time                                   |

| Lowercase le               | etters (pp) and their meanings: |           |                                        |

| рр                         |                                 |           |                                        |

| сс                         | CCP1                            | osc       | OSC1                                   |

| ck                         | CLKO                            | rd        | RD                                     |

| cs                         | CS                              | rw        | RD or WR                               |

| di                         | SDI                             | sc        | SCK                                    |

| do                         | SDO                             | ss        | SS                                     |

| dt                         | Data in                         | tO        | TOCKI                                  |

| io                         | I/O port                        | t1        | T13CKI                                 |

| mc                         | MCLR                            | wr        | WR                                     |

| Uppercase le               | etters and their meanings:      |           |                                        |

| S                          |                                 |           |                                        |

| F                          | Fall                            | Р         | Period                                 |

| н                          | High                            | R         | Rise                                   |

| I                          | Invalid (High-impedance)        | V         | Valid                                  |

| L                          | Low                             | Z         | High-impedance                         |

| I <sup>2</sup> C only      |                                 |           |                                        |

| AA                         | output access                   | High      | High                                   |

| BUF                        | Bus free                        | Low       | Low                                    |

| TCC:ST (I <sup>2</sup> C s | specifications only)            | •         |                                        |

| CC                         |                                 |           |                                        |

| HD                         | Hold                            | SU        | Setup                                  |

| ST                         |                                 |           |                                        |

| DAT                        | DATA input hold                 | STO       | Stop condition                         |

| STA                        | Start condition                 |           |                                        |

# PIC18F47J13 FAMILY

| Param.<br>No. | Symbol | Characteristic | Min | Тур | Мах | Units | Conditions                                    |

|---------------|--------|----------------|-----|-----|-----|-------|-----------------------------------------------|

| W1            | Wds    | Deep Sleep     | —   | 500 |     | μS    | REGSLP = 1                                    |

| W2            | WSLEEP | Sleep          | —   | 35  |     | μS    | REGSLP = 1, PLLEN = 0,<br>Fosc = 8 MHz INTOSC |

| W3            | WDOZE1 | Sleep          | —   | 12  | —   | μS    | REGSLP = 0, PLLEN = 0,<br>Fosc = 8 MHz INTOSC |

| W4            | WDOZE2 | Sleep          | —   | 1.1 | —   | μS    | REGSLP = 0, PLLEN = 0,<br>Fosc = 8 MHz EC     |

| W5            | WDOZE3 | Sleep          | —   | 230 | —   | ns    | REGSLP = 0, PLLEN = 0,<br>Fosc = 48 MHz EC    |

| W6            | WIDLE  | Idle           | —   | 230 | _   | ns    | Fosc = 48 MHz EC                              |

#### TABLE 30-15: LOW-POWER WAKE-UP TIME

## APPENDIX A: REVISION HISTORY

## **Revision A (March 2010)**

Original data sheet for PIC18F47J13 Family devices.

## Revision B (9/2016)

Removed Preliminary from the data sheet; Updated Packages; Other minor corrections.

## Revision C (3/2017)

Replaced ADC chapter with version from Revision A of the document; Minor changes to the entire document.

## THE MICROCHIP WEBSITE

Microchip provides online support via our website at www.microchip.com. This website is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the website contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Micro-chip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip website at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the website at: http://microchip.com/support