Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 48MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 22                                                                           |

| Program Memory Size        | 64KB (32K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 3.8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                   |

| Data Converters            | A/D 10x10b/12b                                                               |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26j13t-i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

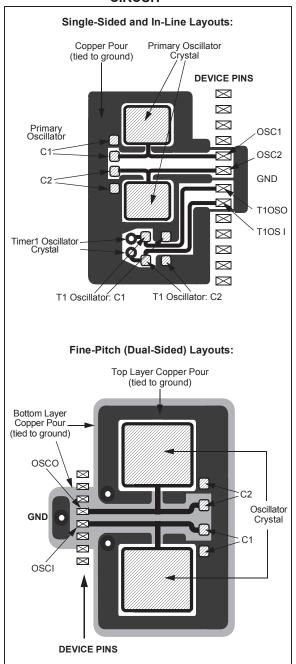

## 2.6 External Oscillator Pins

Many microcontrollers have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 3.0 "Oscillator Configurations**" for details).

The oscillator circuit should be placed on the same side of the board as the device. Place the oscillator circuit close to the respective oscillator pins with no more than 0.5 inch (12 mm) between the circuit components and the pins. The load capacitors should be placed next to the oscillator itself, on the same side of the board.

Use a grounded copper pour around the oscillator circuit to isolate it from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed.

Layout suggestions are shown in Figure 2-4. In-line packages may be handled with a single-sided layout that completely encompasses the oscillator pins. With fine-pitch packages, it is not always possible to completely surround the pins and components. A suitable solution is to tie the broken guard sections to a mirrored ground layer. In all cases, the guard trace(s) must be returned to ground.

In planning the application's routing and I/O assignments, ensure that adjacent port pins and other signals in close proximity to the oscillator are benign (i.e., free of high frequencies, short rise and fall times, and other similar noise).

For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate website (www.microchip.com):

- AN826, Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices

- AN849, Basic PICmicro<sup>®</sup> Oscillator Design

- AN943, Practical PICmicro<sup>®</sup> Oscillator Analysis and Design

- AN949, Making Your Oscillator Work

## 2.7 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic low state. Alternatively, connect a 1 k $\Omega$  to 10 k $\Omega$  resistor to Vss on unused pins and drive the output to logic low.

## FIGURE 2-4:

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

### REGISTER 9-3: INTCON3: INTERRUPT CONTROL REGISTER 3 (ACCESS FF0h)

| R/W-1                | R/W-1                                 | R/W-0                                  | R/W-0            | R/W-0            | R/W-0           | R/W-0            | R/W-0        |

|----------------------|---------------------------------------|----------------------------------------|------------------|------------------|-----------------|------------------|--------------|

| INT2IP               | INT1IP                                | INT3IE                                 | INT2IE           | INT1IE           | INT3IF          | INT2IF           | INT1IF       |

| bit 7                |                                       |                                        |                  |                  |                 |                  | bit (        |

| Locondu              |                                       |                                        |                  |                  |                 |                  |              |

| Legend:<br>R = Reada | ahla hit                              | W = Writable                           | hit              | II = I Inimplen  | nented bit, rea | nd as 'O'        |              |

| -n = Value           |                                       | '1' = Bit is set                       |                  | '0' = Bit is cle |                 | x = Bit is unkr  | nown         |

|                      |                                       | 1 Bit io oot                           |                  |                  |                 |                  |              |

| bit 7                | INT2IP: INT2                          | External Interr                        | upt Priority bit |                  |                 |                  |              |

|                      | 1 = High pric                         |                                        |                  |                  |                 |                  |              |

|                      | 0 = Low prio                          | rity                                   |                  |                  |                 |                  |              |

| bit 6                |                                       | External Interr                        | upt Priority bit |                  |                 |                  |              |

|                      | 1 = High pric<br>0 = Low prio         |                                        |                  |                  |                 |                  |              |

| bit 5                | •                                     | External Interr                        | unt Enable hit   |                  |                 |                  |              |

|                      |                                       | the INT3 exteri                        | •                |                  |                 |                  |              |

|                      |                                       | the INT3 exter                         |                  |                  |                 |                  |              |

| bit 4                | INT2IE: INT2                          | External Interr                        | upt Enable bit   |                  |                 |                  |              |

|                      |                                       | the INT2 extern                        | •                |                  |                 |                  |              |

| 1.1.0                |                                       | the INT2 exter                         |                  |                  |                 |                  |              |

| bit 3                |                                       | External Interr                        | -                |                  |                 |                  |              |

|                      |                                       | the INT1 extern<br>the INT1 extern     |                  |                  |                 |                  |              |

| bit 2                |                                       | External Interr                        |                  |                  |                 |                  |              |

|                      |                                       |                                        |                  | must be cleared  | d in software)  |                  |              |

|                      |                                       | 3 external inter                       |                  | cur              |                 |                  |              |

| bit 1                |                                       | External Interr                        |                  |                  |                 |                  |              |

|                      |                                       | 2 external interi<br>2 external interi |                  | must be cleared  | d in software)  |                  |              |

| bit 0                |                                       | External Interr                        | •                | Sui              |                 |                  |              |

|                      |                                       |                                        |                  | must be cleared  | d in software)  |                  |              |

|                      |                                       | 1 external interi                      |                  |                  |                 |                  |              |

| Note                 | Interrupt floor bits                  | oro oot when                           | on interrunt     | ndition accura   | rogardiaca of   | the state of its | oorroopandin |

| Note:                | Interrupt flag bits enable bit or the |                                        |                  |                  |                 |                  |              |

|                      | are clear prior to                    | •                                      |                  |                  |                 |                  | . 5          |

| REGISTER 10-2: ODCON2: PERIPHERAL OPEN-DRAIN CONTROL REGISTER 2 (BANKED F41h) |                                                                                                                                                            |                                                                                                                                   |                            |                   |                  |                 |       |

|-------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------|------------------|-----------------|-------|

| U-0                                                                           | U-0                                                                                                                                                        | U-0                                                                                                                               | U-0                        | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| _                                                                             | —                                                                                                                                                          | —                                                                                                                                 | —                          | CCP10OD           | CCP90D           | U2OD            | U10D  |

| bit 7                                                                         |                                                                                                                                                            |                                                                                                                                   |                            | -                 |                  |                 | bit 0 |

|                                                                               |                                                                                                                                                            |                                                                                                                                   |                            |                   |                  |                 |       |

| Legend:                                                                       |                                                                                                                                                            |                                                                                                                                   |                            |                   |                  |                 |       |

| R = Readal                                                                    | ble bit                                                                                                                                                    | W = Writable                                                                                                                      | bit                        | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value a                                                                  | at POR                                                                                                                                                     | '1' = Bit is set                                                                                                                  |                            | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

| bit 3                                                                         | Unimplemented: Read as '0'<br>CCP10OD: CCP10 Open-Drain Output Enable bit<br>1 = Open-drain capability is enabled<br>0 = Open-drain capability is disabled |                                                                                                                                   |                            |                   |                  |                 |       |

| bit 2                                                                         | 1 = Open-dra                                                                                                                                               | <b>CCP9OD:</b> CCP9 Open-Drain Output Enable bit<br>1 = Open-drain capability is enabled<br>0 = Open-drain capability is disabled |                            |                   |                  |                 |       |

| bit 1                                                                         | bit 1 U2OD: USART2 Open-Drain Output Enable bit<br>1 = Open-drain capability is enabled<br>0 = Open-drain capability is disabled                           |                                                                                                                                   |                            |                   |                  |                 |       |

| bit 0                                                                         |                                                                                                                                                            | T1 Open-Drain<br>in capability is                                                                                                 | n Output Enable<br>enabled | e bit             |                  |                 |       |

0 = Open-drain capability is disabled

## REGISTER 10-3: ODCON3: PERIPHERAL OPEN-DRAIN CONTROL REGISTER 3 (BANKED F40h)

| R/W-0       | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0  | R/W-0  |

|-------------|-----|-----|-----|-----|-----|--------|--------|

| CTMUDS      | —   | —   | —   | —   | —   | SPI2OD | SPI10D |

| bit 7 bit 0 |     |     |     |     |     |        |        |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | CTMUDS: CTMU Pulse Delay Enable bit                                                                  |

|---------|------------------------------------------------------------------------------------------------------|

|         | 1 = Pulse delay input for CTMU enabled on pin, RA1                                                   |

| bit 6-2 | Unimplemented: Read as '0'                                                                           |

| bit 1   | SPI2OD: SPI2 Open-Drain Output Enable bit                                                            |

|         | <ul><li>1 = Open-drain capability is enabled</li><li>0 = Open-drain capability is disabled</li></ul> |

| bit 0   | SPI10D: SPI1 Open-Drain Output Enable bit                                                            |

|         | <ul><li>1 = Open-drain capability is enabled</li><li>0 = Open-drain capability is disabled</li></ul> |

## 11.1 Module Registers

The PMP module has a total of 14 Special Function Registers (SFRs) for its operation, plus one additional register to set configuration options. Of these, eight registers are used for control and six are used for PMP data transfer.

#### 11.1.1 CONTROL REGISTERS

The eight PMP Control registers are:

- PMCONH and PMCONL

- PMMODEH and PMMODEL

- PMSTATL and PMSTATH

- PMEH and PMEL

The PMCON registers (Register 11-1 and Register 11-2) control basic module operations, including turning the module on or off. They also configure address multiplexing and control strobe configuration.

The PMMODE registers (Register 11-3 and Register 11-4) configure the various Master and Slave modes, the data width and interrupt generation.

The PMEH and PMEL registers (Register 11-5 and Register 11-6) configure the module's operation at the hardware (I/O pin) level.

The PMSTAT registers (Register 11-5 and Register 11-6) provide status flags for the module's input and output buffers, depending on the operating mode.

#### REGISTER 11-1: PMCONH: PARALLEL PORT CONTROL REGISTER HIGH BYTE (BANKED F5Fh)<sup>(1)</sup>

| R/W-0       | U-0 | U-0 | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------------|-----|-----|---------|---------|--------|--------|--------|

| PMPEN       | —   | —   | ADRMUX1 | ADRMUX0 | PTBEEN | PTWREN | PTRDEN |

| bit 7 bit 0 |     |     |         |         |        |        |        |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | PMPEN: Parallel Master Port Enable bit                                                                                |

|---------|-----------------------------------------------------------------------------------------------------------------------|

|         | 1 = PMP enabled                                                                                                       |

|         | 0 = PMP disabled, no off-chip access performed                                                                        |

| bit 6-5 | Unimplemented: Read as '0'                                                                                            |

| bit 4-3 | ADRMUX<1:0>: Address/Data Multiplexing Selection bits                                                                 |

|         | 11 = Reserved                                                                                                         |

|         | 10 = All 16 bits of address are multiplexed on PMD<7:0> pins                                                          |

|         | 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins (only eight bits of address are available in this mode) |

|         | 00 = Address and data appear on separate pins (only eight bits of address are available in this mode)                 |

| bit 2   | PTBEEN: Byte Enable Port Enable bit (16-Bit Master mode)                                                              |

|         | 1 = PMBE port enabled                                                                                                 |

|         | 0 = PMBE port disabled                                                                                                |

| bit 1   | PTWREN: Write Enable Strobe Port Enable bit                                                                           |

|         | 1 = PMWR/PMENB port enabled                                                                                           |

|         | 0 = PMWR/PMENB port disabled                                                                                          |

| bit 0   | PTRDEN: Read/Write Strobe Port Enable bit                                                                             |

|         | 1 = PMRD/PMWR port enabled                                                                                            |

|         | 0 = PMRD/PMWR port disabled                                                                                           |

|         |                                                                                                                       |

**Note 1:** This register is only available on 44-pin devices.

## 12.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software selectable operation as a timer or counter in both 8-bit or 16-bit modes

- · Readable and writable registers

- Dedicated 8-bit, software programmable

prescaler

- Selectable clock source (internal or external)

- · Edge select for external clock

- Interrupt-on-overflow

The T0CON register (Register 12-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

Figure 12-1 provides a simplified block diagram of the Timer0 module in 8-bit mode. Figure 12-2 provides a simplified block diagram of the Timer0 module in 16-bit mode.

#### REGISTER 12-1: T0CON: TIMER0 CONTROL REGISTER (ACCESS FD5h)

| R/W-1       | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|-------------|--------|-------|-------|-------|-------|-------|-------|

| TMR00N      | T08BIT | TOCS  | T0SE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7 bit 0 |        |       |       |       |       |       |       |

| Legend:                           |                                                                                       |                                                            |                      |                    |  |  |  |  |

|-----------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------|----------------------|--------------------|--|--|--|--|

| R = Readable bit W = Writable bit |                                                                                       | U = Unimplemented bit                                      | , read as '0'        |                    |  |  |  |  |

| -n = Value                        | at POR                                                                                | '1' = Bit is set                                           | '0' = Bit is cleared | x = Bit is unknown |  |  |  |  |

|                                   |                                                                                       |                                                            |                      |                    |  |  |  |  |

| bit 7                             |                                                                                       | : Timer0 On/Off Control bit                                |                      |                    |  |  |  |  |

|                                   |                                                                                       | les Timer0                                                 |                      |                    |  |  |  |  |

|                                   | 0 = Stops                                                                             | 5 Timer0                                                   |                      |                    |  |  |  |  |

| bit 6                             | T08BIT: 1                                                                             | Timer0 8-Bit/16-Bit Control bit                            | t                    |                    |  |  |  |  |

|                                   |                                                                                       | 0 is configured as an 8-bit tir                            |                      |                    |  |  |  |  |

|                                   | 0 = Timei                                                                             | 0 is configured as a 16-bit tir                            | mer/counter          |                    |  |  |  |  |

| bit 5                             | TOCS: Tir                                                                             | TOCS: Timer0 Clock Source Select bit                       |                      |                    |  |  |  |  |

|                                   | 1 = Transition on T0CKI pin input edge                                                |                                                            |                      |                    |  |  |  |  |

|                                   | 0 = Internal clock (Fosc/4)                                                           |                                                            |                      |                    |  |  |  |  |

| bit 4                             | T0SE: Timer0 Source Edge Select bit                                                   |                                                            |                      |                    |  |  |  |  |

|                                   | 1 = Increment on high-to-low transition on TOCKI pin                                  |                                                            |                      |                    |  |  |  |  |

|                                   | 0 = Increment on low-to-high transition on T0CKI pin                                  |                                                            |                      |                    |  |  |  |  |

| bit 3                             | PSA: Timer0 Prescaler Assignment bit                                                  |                                                            |                      |                    |  |  |  |  |

|                                   | 1 = Timer0 prescaler is not assigned. Timer0 clock input bypasses prescaler.          |                                                            |                      |                    |  |  |  |  |

|                                   | 0 = Timer0 prescaler is assigned. Timer0 clock input comes from the prescaler output. |                                                            |                      |                    |  |  |  |  |

| bit 2-0                           | T0PS<2:                                                                               | 0>: Timer0 Prescaler Select I                              | oits                 |                    |  |  |  |  |

|                                   | 111 = 1:256 Prescale value                                                            |                                                            |                      |                    |  |  |  |  |

|                                   | 110 <b>= 1</b> :1                                                                     | 110 = 1:128 Prescale value                                 |                      |                    |  |  |  |  |

|                                   |                                                                                       | A Prescale value                                           |                      |                    |  |  |  |  |

|                                   |                                                                                       | 32 Prescale value                                          |                      |                    |  |  |  |  |

|                                   |                                                                                       | 6 Prescale value                                           |                      |                    |  |  |  |  |

|                                   |                                                                                       | <ul> <li>Prescale value</li> <li>Prescale value</li> </ul> |                      |                    |  |  |  |  |

|                                   | 001 = 1.4<br>000 = 1.2                                                                |                                                            |                      |                    |  |  |  |  |

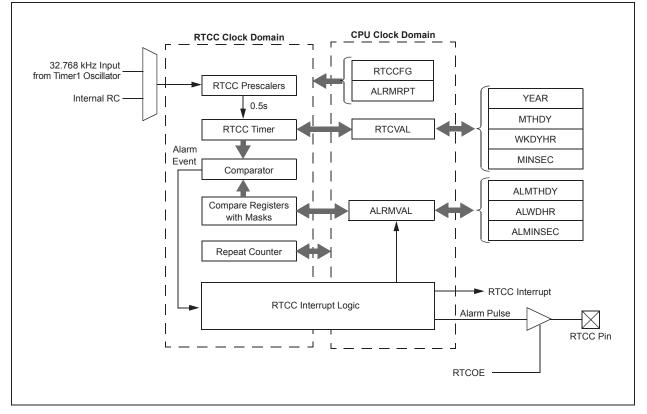

## 17.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

The key features of the Real-Time Clock and Calendar (RTCC) module are:

- · Time: hours, minutes and seconds

- 24-hour format (military time)

- Calendar: weekday, date, month and year

- · Alarm configurable

- Year range: 2000 to 2099

- · Leap year correction

- BCD format for compact firmware

- · Optimized for low-power operation

- · User calibration with auto-adjust

- Calibration range: ±2.64 seconds error per month

- Requirements: external 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

The RTCC module is intended for applications where accurate time must be maintained for an extended period with minimum to no intervention from the CPU. The module is optimized for low-power usage in order to provide extended battery life while keeping track of time.

The module is a 100-year clock and calendar with automatic leap year detection. The range of the clock is from 00:00:00 (midnight) on January 1, 2000 to 23:59:59 on December 31, 2099. Hours are measured in 24-hour (military time) format. The clock provides a granularity of one second with half second visibility to the user.

#### FIGURE 17-1: RTCC BLOCK DIAGRAM

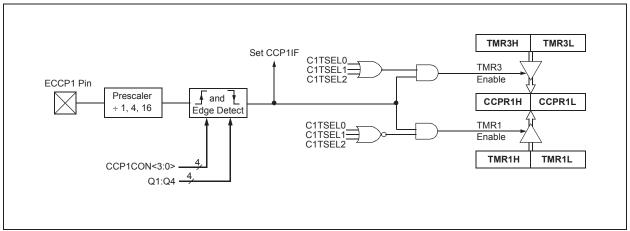

### 19.2.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer to be used with each ECCP module is selected in the CCPTMRS0 register (Register 19-2).

#### 19.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit clear to avoid false interrupts. The interrupt flag bit, CCPxIF, should also be cleared following any such change in operating mode.

#### 19.2.4 ECCP PRESCALER

There are four prescaler settings in Capture mode; they are specified as part of the operating mode selected by the mode select bits (CCPxM<3:0>). Whenever the

ECCP module is turned off, or Capture mode is disabled, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 19-1 provides the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 19-1: CHANGING BETWEEN CAPTURE PRESCALERS

|       |             |   | Turn ECCP module off |

|-------|-------------|---|----------------------|

| MOVLW | NEW_CAPT_PS | ; | Load WREG with the   |

|       |             | ; | new prescaler mode   |

|       |             | ; | value and ECCP ON    |

| MOVWF | CCP1CON     | ; | Load ECCP1CON with   |

|       |             | ; | this value           |

|       |             |   |                      |

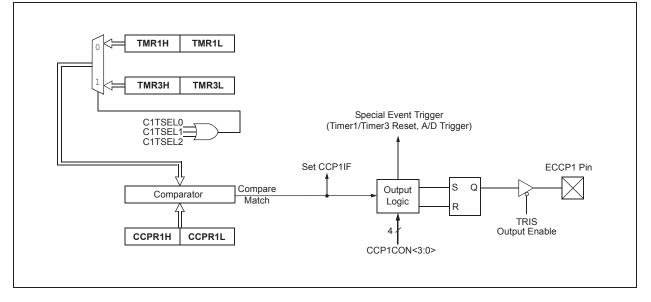

## 19.3 Compare Mode

In Compare mode, the 16-bit CCPRx register pair value is constantly compared against either the TMR1 or TMR3 register pair value. When a match occurs, the ECCPx pin can be:

- Driven high

- Driven low

- Toggled (high-to-low or low-to-high)

- Unchanged (that is, reflecting the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCPxM<3:0>). At the same time, the interrupt flag bit, CCPxIF, is set.

#### 19.3.1 ECCP PIN CONFIGURATION

Users must configure the ECCPx pin as an output by clearing the appropriate TRISx bit.

| Note: | Clearing the CCPxCON register will force   |

|-------|--------------------------------------------|

|       | the ECCPx compare output latch             |

|       | (depending on device configuration) to the |

|       | default low level. This is not the PORTx   |

|       | I/O data latch.                            |

## 19.3.2 TIMER1/TIMER3 MODE SELECTION

Timer1 and/or Timer3 must be running in Timer mode or Synchronized Counter mode if the ECCP module is using the compare feature. In Asynchronous Counter mode, the compare operation will not work reliably.

#### 19.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCPxM<3:0> = 1010), the ECCPx pin is not affected; only the CCPxIF interrupt flag is affected.

#### 19.3.4 SPECIAL EVENT TRIGGER

The ECCP module is equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode (CCPxM<3:0> = 1011).

The Special Event Trigger resets the Timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPRx registers to serve as a Programmable Period register for either timer.

The Special Event Trigger can also start an A/D conversion. In order to do this, the A/D Converter must already be enabled.

### FIGURE 19-2: COMPARE MODE OPERATION BLOCK DIAGRAM

When a shutdown event occurs, two things happen:

- The ECCPxASE bit is set to '1'. The ECCPxASE will remain set until cleared in firmware or an auto-restart occurs. (See Section 19.4.5 "Auto-Restart Mode".)

- The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs (PxA/PxC and

PxB/PxD). The state of each pin pair is determined by the PSSxAC and PSSxBD bits (ECCPxAS<3:0>).

Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

### REGISTER 19-4: ECCPxAS: ECCP1/2/3 AUTO-SHUTDOWN CONTROL REGISTER (1, ACCESS FBEh; 2, FB8h; 3, BANKED F19h)

| R/W-0       | R/W-0    | R/W-0    | R/W-0    | R/W-0   | R/W-0   | R/W-0   | R/W-0   |  |

|-------------|----------|----------|----------|---------|---------|---------|---------|--|

| ECCPxASE    | ECCPxAS2 | ECCPxAS1 | ECCPxAS0 | PSSxAC1 | PSSxAC0 | PSSxBD1 | PSSxBD0 |  |

| bit 7 bit 0 |          |          |          |         |         |         |         |  |

| Legend:                                                              |                  |                      |                    |  |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |  |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

| bit 7   | ECCPxASE: ECCP Auto-Shutdown Event Status bit                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = A shutdown event has occurred; ECCP outputs are in a shutdown state</li> <li>0 = ECCP outputs are operating</li> </ul>                                                                                                                                                                                                                                                                                                                                       |

| bit 6-4 | ECCPxAS<2:0>: ECCP Auto-Shutdown Source Select bits                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>000 = Auto-shutdown is disabled</li> <li>001 = Comparator, C1OUT, output is high</li> <li>010 = Comparator, C2OUT, output is high</li> <li>011 = Either comparator, C1OUT or C2OUT, is high</li> <li>100 = VIL on FLT0 pin</li> <li>101 = VIL on FLT0 pin or comparator, C1OUT, output is high</li> <li>110 = VIL on FLT0 pin or comparator, C2OUT, output is high</li> <li>111 = VIL on FLT0 pin or comparator, C1OUT, or comparator, C2OUT, is high</li> </ul> |

| bit 3-2 | <b>PSSxAC&lt;1:0&gt;:</b> PxA and PxC Pins Shutdown State Control bits<br>00 = Drive pins, PxA and PxC, to '0'                                                                                                                                                                                                                                                                                                                                                            |

|         | 01 = Drive pins, PxA and PxC, to '1'<br>1x = PxA and PxC pins tri-state                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 1-0 | PSSxBD<1:0>: PxB and PxD Pins Shutdown State Control bits<br>00 = Drive pins, PxB and PxD, to '0'<br>01 = Drive pins, PxB and PxD, to '1'<br>1x = PxB and PxD pins tri-state                                                                                                                                                                                                                                                                                              |

| Note 1: | The auto-shutdown condition is a level-based signal, not an edge-based signal. As long as the present, the auto-shutdown will persist.                                                                                                                                                                                                                                                                                                                                    |

| 2:      | Writing to the ECCPxASE bit is disabled while an auto-shutdown condition persists.                                                                                                                                                                                                                                                                                                                                                                                        |

3: Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart), the PWM signal will always restart at the beginning of the next PWM period.

level is

## 20.3.2 OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSPxCON1<5:0> and SSPxSTAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCKx is the clock output)

- Slave mode (SCKx is the clock input)

- Clock Polarity (Idle state of SCKx)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCKx)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

Each MSSP module consists of a Transmit/Receive Shift register (SSPxSR) and a Buffer register (SSPxBUF). The SSPxSR shifts the data in and out of the device, MSb first. The SSPxBUF holds the data that was written to the SSPxSR until the received data is ready. Once the 8 bits of data have been received, that byte is moved to the SSPxBUF register. Then, the Buffer Full (BF) detect bit (SSPxSTAT<0>) and the interrupt flag bit, SSPxIF, are set. This double-buffering of the received data (SSPxBUF) allows the next byte to start reception before reading the data that was just received.

Any write to the SSPxBUF register during transmission or reception of data will be ignored and the Write Collision Detect bit, WCOL (SSPxCON1<7>), will be set. User software must clear the WCOL bit so that it can be determined if the following write(s) to the SSPxBUF register completed successfully.

| Note: | When the application software is expecting to receive valid data, the SSPxBUF should |

|-------|--------------------------------------------------------------------------------------|

|       | be read before the next byte of transfer                                             |

|       | data is written to the SSPxBUF. Application                                          |

|       | software should follow this process even                                             |

|       | when the current contents of SSPxBUF                                                 |

|       | are not important.                                                                   |

The Buffer Full bit, BF (SSPxSTAT<0>), indicates when SSPxBUF has been loaded with the received data (transmission is complete). When the SSPxBUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

Example 20-1 provides the loading of the SSPxBUF (SSPxSR) for data transmission.

The SSPxSR is not directly readable or writable and can only be accessed by addressing the SSPxBUF register. Additionally, the SSPxSTAT register indicates the various status conditions.

## 20.3.3 OPEN-DRAIN OUTPUT OPTION

The drivers for the SDOx output and SCKx clock pins can be optionally configured as open-drain outputs. This feature allows the voltage level on the pin to be pulled to a higher level through an external pull-up resistor, provided the SDOx or SCKx pin is not multiplexed with an ANx analog function. This allows the output to communicate with external circuits without the need for additional level shifters. For more information, see Section 10.1.4 "Open-Drain Outputs".

The open-drain output option is controlled by the SPI2OD and SPI1OD bits (ODCON3<1:0>). Setting an SPIxOD bit configures both the SDOx and SCKx pins for the corresponding open-drain operation.

#### EXAMPLE 20-1: LOADING THE SSP1BUF (SSP1SR) REGISTER

| LOOP | BTFSS<br>BRA<br>MOVF | LOOP                 | ;Has data been received (transmit complete)?<br>;No<br>;WREG reg = contents of SSP1BUF |

|------|----------------------|----------------------|----------------------------------------------------------------------------------------|

|      | MOVWF                | RXDATA               | ;Save in user RAM, if data is meaningful                                               |

|      | MOVF<br>MOVWF        | TXDATA, W<br>SSP1BUF | ;W reg = contents of TXDATA<br>;New data to xmit                                       |

## 20.5.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDAx while SCLx outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted, 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. S and P conditions are output to indicate the beginning and end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the  $R/\overline{W}$  bit. In this case, the  $R/\overline{W}$  bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address, followed by a '1' to indicate the receive bit. Serial data is received via SDAx, while SCLx outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. S and P conditions indicate the beginning and end of transmission.

The BRG used for the SPI mode operation is used to set the SCLx clock frequency for either 100 kHz, 400 kHz or 1 MHz  $I^2$ C operation. See Section 20.5.7 "Baud Rate" for more details.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start Enable bit, SEN (SSPxCON2<0>).

- SSPxIF is set. The MSSP module will wait for the required start time before any other operation takes place.

- 3. The user loads the SSPxBUF with the slave address to transmit.

- 4. The address is shifted out of the SDAx pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPx-CON2 register (SSPxCON2<6>).

- The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 7. The user loads the SSPxBUF with 8 bits of data.

- 8. Data is shifted out of the SDAx pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPx-CON2 register (SSPxCON2<6>).

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPxIF bit.

- 11. The user generates a Stop condition by setting the Stop Enable bit, PEN (SSPxCON2<2>).

- 12. The interrupt is generated once the Stop condition is complete.

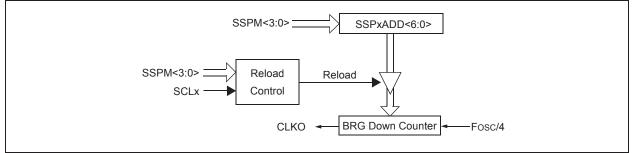

### 20.5.7 BAUD RATE

In I<sup>2</sup>C Master mode, the BRG reload value is placed in the lower seven bits of the SSPxADD register (Figure 20-19). When a write occurs to SSPxBUF, the Baud Rate Generator will automatically begin counting. The BRG counts down to 0 and stops until another reload has taken place. The BRG count is decremented twice per instruction cycle (TcY) on the Q2 and Q4 clocks. In I<sup>2</sup>C Master mode, the BRG is reloaded automatically.

Once the given operation is complete (i.e., transmission of the last data bit is followed by ACK), the internal clock will automatically stop counting and the SCLx pin will remain in its last state.

Table 20-3 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSPxADD. The SSPADD BRG value of 0x00 is not supported.

### 20.5.7.1 Baud Rate and Module Interdependence

Because MSSP1 and MSSP2 are independent, they can operate simultaneously in I<sup>2</sup>C Master mode at different baud rates. This is done by using different BRG reload values for each module.

Because this mode derives its basic clock source from the system clock, any changes to the clock will affect both modules in the same proportion. It may be possible to change one or both baud rates back to a previous value by changing the BRG reload value.

## FIGURE 20-19: BAUD RATE GENERATOR BLOCK DIAGRAM

## TABLE 20-3: I<sup>2</sup>C CLOCK RATE w/BRG

| Fosc   | Fcy    | Fcy * 2 | BRG Value | FscL<br>(2 Rollovers of BRG) |

|--------|--------|---------|-----------|------------------------------|

| 40 MHz | 10 MHz | 20 MHz  | 18h       | 400 kHz                      |

| 40 MHz | 10 MHz | 20 MHz  | 1Fh       | 312.5 kHz                    |

| 40 MHz | 10 MHz | 20 MHz  | 63h       | 100 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 09h       | 400 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 0Ch       | 308 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 27h       | 100 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 02h       | 333 kHz                      |

| 4 MHz  | 1 MHz  | 2 MHz   | 09h       | 100 kHz                      |

| 16 MHz | 4 MHz  | 8 MHz   | 03h       | 1 MHz <sup>(1)</sup>         |

**Note 1:** The I<sup>2</sup>C interface does not conform to the 400 kHz I<sup>2</sup>C specification (which applies to rates greater than 100 kHz) in all details, but may be used with care where higher rates are required by the application.

| R/W-0         | R-1                                | R/W-0                                                    | R/W-0            | R/W-0                             | U-0            | R/W-0             | R/W-0          |

|---------------|------------------------------------|----------------------------------------------------------|------------------|-----------------------------------|----------------|-------------------|----------------|

| ABDOVF        | RCIDL                              | RXDTP                                                    | TXCKP            | BRG16                             | _              | WUE               | ABDEN          |

| bit 7         |                                    | ·                                                        | ·                |                                   |                | ·                 | bit            |

| Legend:       |                                    |                                                          |                  |                                   |                |                   |                |

| R = Readabl   | e bit                              | W = Writable                                             | bit              | U = Unimplem                      | ented bit, rea | d as '0'          |                |

| -n = Value at | POR                                | '1' = Bit is set                                         |                  | '0' = Bit is clea                 | red            | x = Bit is unki   | nown           |

| bit 7         | 1 = A BRG r                        | uto-Baud Acquis<br>ollover has occi<br>rollover has oc   | urred during A   | Status bit<br>uto-Baud Rate I     | Detect mode (  | must be cleare    | d in software) |

| bit 6         | RCIDL: Rece                        | eive Operation I                                         | dle Status bit   |                                   |                |                   |                |

|               |                                    | operation is Idle<br>operation is acti                   |                  |                                   |                |                   |                |

| bit 5         | RXDTP: Data                        | a/Receive Polar                                          | ity Select bit   |                                   |                |                   |                |

|               |                                    | i <u>s mode:</u><br>data (RXx) is in<br>data (RXx) is no |                  |                                   |                |                   |                |

|               |                                    | <u>s mode:</u><br>x) is inverted (a<br>x) is not inverte |                  | )                                 |                |                   |                |

| bit 4         | TXCKP: Syn                         | chronous Clock                                           | Polarity Selec   | ct bit                            |                |                   |                |

|               |                                    | i <u>s mode:</u><br>for transmit (T)<br>for transmit (T) |                  |                                   |                |                   |                |

|               |                                    | <u>s mode:</u><br>s for clock (CKx)<br>s for clock (CKx) |                  | I                                 |                |                   |                |

| bit 3         | BRG16: 16-E                        | Bit Baud Rate R                                          | egister Enable   | e bit                             |                |                   |                |

|               |                                    |                                                          |                  | Hx and SPBRGX<br>only (Compatible |                | BRGHx value is    | ignored        |

| bit 2         | Unimplemer                         | ted: Read as '                                           | כ'               |                                   |                |                   |                |

| bit 1         | WUE: Wake-                         | up Enable bit                                            |                  |                                   |                |                   |                |

|               | cleared                            |                                                          | the following ri |                                   | upt is genera  | ited on the falli | ng edge; bit i |

|               | Synchronous<br>Unused in th        |                                                          |                  |                                   |                |                   |                |

| bit 0         | ABDEN: Aut                         | o-Baud Detect I                                          | Enable bit       |                                   |                |                   |                |

|               | cleared                            |                                                          | on completion    | e next characte                   | r; requires re | ception of a Sy   | nc field (55h/ |

|               | <u>Synchronous</u><br>Unused in th |                                                          |                  |                                   |                |                   |                |

## 21.4 EUSART Synchronous Slave Mode

Synchronous Slave mode is entered by clearing bit, CSRC (TXSTAx<7>). This mode differs from the Synchronous Master mode in that the shift clock is supplied externally at the CKx pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in any low-power mode.

#### 21.4.1 EUSART SYNCHRONOUS SLAVE TRANSMISSION

The operation of the Synchronous Master and Slave modes is identical, except in the case of Sleep mode.

If two words are written to the TXREGx, and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in the TXREGx register.

- c) Flag bit, TXxIF, will not be set.

- d) When the first word has been shifted out of TSR, the TXREGx register will transfer the second word to the TSR and flag bit, TXxIF, will now be set.

e) If enable bit, TXxIE, is set, the interrupt will wake the chip from Sleep. If the global interrupt is enabled, the program will branch to the interrupt vector.

To set up a Synchronous Slave Transmission:

- Enable the synchronous slave serial port by setting bits, SYNC and SPEN, and clearing bit, CSRC.

- 2. Clear bits, CREN and SREN.

- 3. If interrupts are desired, set enable bit, TXxIE.

- 4. If 9-bit transmission is desired, set bit, TX9.

- 5. Enable the transmission by setting enable bit, TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit, TX9D.

- 7. Start transmission by loading data to the TXREGx register.

- If using interrupts, ensure that the GIE and PEIE bits in the INTCON register (INTCON<7:6>) are set.

| Name     | Bit 7                | Bit 6                                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1   | Bit 0  |  |

|----------|----------------------|---------------------------------------|--------|--------|--------|--------|---------|--------|--|

| INTCON   | GIE/GIEH             | PEIE/GIEL                             | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF  | RBIF   |  |

| PIR1     | PMPIF <sup>(1)</sup> | ADIF                                  | RC1IF  | TX1IF  | SSP1IF | CCP1IF | TMR2IF  | TMR1IF |  |

| PIE1     | PMPIE <sup>(1)</sup> | ADIE                                  | RC1IE  | TX1IE  | SSP1IE | CCP1IE | TMR2IE  | TMR1IE |  |

| IPR1     | PMPIP <sup>(1)</sup> | ADIP                                  | RC1IP  | TX1IP  | SSP1IP | CCP1IP | TMR2IP  | TMR1IP |  |

| PIR3     | SSP2IF               | BCL2IF                                | RC2IF  | TX2IF  | TMR4IF | CTMUIF | TMR3GIF | RTCCIF |  |

| PIE3     | SSP2IE               | BCL2IE                                | RC2IE  | TX2IE  | TMR4IE | CTMUIE | TMR3GIE | RTCCIE |  |

| IPR3     | SSP2IP               | BCL2IP                                | RC2IP  | TX2IP  | TMR4IP | CTMUIP | TMR3GIP | RTCCIP |  |

| RCSTAx   | SPEN                 | RX9                                   | SREN   | CREN   | ADDEN  | FERR   | OERR    | RX9D   |  |

| TXREGx   | EUSARTx T            | ransmit Regis                         | ter    |        |        |        |         |        |  |

| TXSTAx   | CSRC                 | TX9                                   | TXEN   | SYNC   | SENDB  | BRGH   | TRMT    | TX9D   |  |

| BAUDCONx | ABDOVF               | RCIDL                                 | RXDTP  | TXCKP  | BRG16  | _      | WUE     | ABDEN  |  |

| SPBRGHx  | EUSARTx B            | EUSARTx Baud Rate Generator High Byte |        |        |        |        |         |        |  |

| SPBRGx   | EUSARTx B            | EUSARTx Baud Rate Generator Low Byte  |        |        |        |        |         |        |  |

## TABLE 21-9: REGISTERS ASSOCIATED WITH SYNCHRONOUS SLAVE TRANSMISSION

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used for synchronous slave transmission.

Note 1: These pins are only available on 44-pin devices.

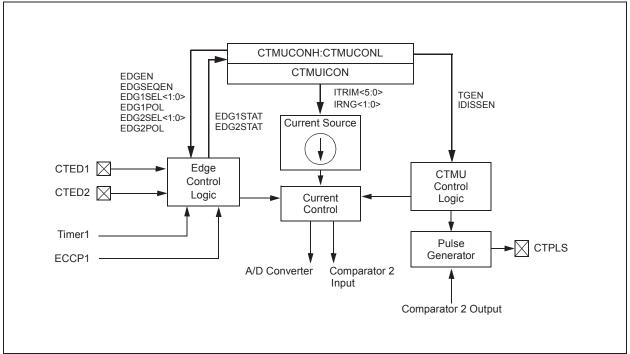

## 26.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

The Charge Time Measurement Unit (CTMU) is a flexible analog module that provides accurate differential time measurement between pulse sources, as well as asynchronous pulse generation. By working with other on-chip analog modules, the CTMU can be used to precisely measure time, measure capacitance, measure relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

The module includes the following key features:

- Up to 13 channels available for capacitive or time measurement input

- · On-chip precision current source

- Four-edge input trigger sources

- · Polarity control for each edge source

- · Control of edge sequence

- · Control of response to edges

- · Time measurement resolution of 1 nanosecond

- High-precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- Accurate current source suitable for capacitive measurement

The CTMU works in conjunction with the A/D Converter to provide up to 13 channels for time or charge measurement, depending on the specific device and the number of A/D channels available. When configured for time delay, the CTMU is connected to one of the analog comparators. The level-sensitive input edge sources can be selected from four sources: two external inputs, Timer1 or Output Compare Module 1.

Figure 26-1 provides a block diagram of the CTMU.

#### FIGURE 26-1: CTMU BLOCK DIAGRAM

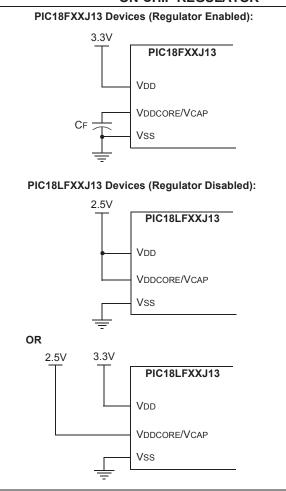

# FIGURE 27-2: CONNECTIONS FOR THE ON-CHIP REGULATOR

## 27.3.2 ON-CHIP REGULATOR AND BOR

When the on-chip regulator is enabled, PIC18F47J13 Family devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a minimum output level, the regulator Reset circuitry will generate a <u>Brown</u>-out Reset (BOR). This event is captured by the <u>BOR</u> flag bit (RCON<0>).

The operation of the BOR is described in more detail in Section 5.4 "Brown-out Reset (BOR)" and Section 5.4.1 "Detecting BOR". The brown-out voltage levels are specific in Section 30.1 "DC Characteristics: Supply Voltage PIC18F47J13 Family (Industrial)".

## 27.3.3 POWER-UP REQUIREMENTS

The on-chip regulator is designed to meet the power-up requirements for the device. If the application does not use the regulator, then strict power-up conditions must be adhered to. While powering up, VDDCORE should not exceed VDD by 0.3 volts.

## 27.3.4 OPERATION IN SLEEP MODE

When enabled, the on-chip regulator always consumes a small incremental amount of current over IDD. This includes when the device is in Sleep mode, even though the core digital logic does not require much power. To provide additional savings in applications where power resources are critical, the regulator can be configured to automatically enter a lower quiescent draw Standby mode whenever the device goes into Sleep mode. This feature is controlled by the REGSLP bit (WDTCON<7>, Register 27-11). If this bit is set upon entry into Sleep mode, the regulator will transition into a lower power state. In this state, the regulator still provides a regulated output voltage necessary to maintain SRAM state information, but consumes less quiescent current.

Substantial Sleep mode power savings can be obtained by setting the REGSLP bit, but device wake-up time will increase in order to insure the regulator has enough time to stabilize.

# PIC18F47J13 FAMILY

| INCF        | SZ                      | Increment                                                                          | Increment f, Skip if 0                                                                                                                                                                                                                                                               |                 |  |  |  |  |

|-------------|-------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|

| Synta       | ax:                     | INCFSZ f                                                                           | {,d {,a}}                                                                                                                                                                                                                                                                            |                 |  |  |  |  |

| Oper        | ands:                   | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$ | $d \in [0,1]$                                                                                                                                                                                                                                                                        |                 |  |  |  |  |

| Operation:  |                         | .,                                                                                 | (f) + 1 $\rightarrow$ dest,<br>skip if result = 0                                                                                                                                                                                                                                    |                 |  |  |  |  |

| Statu       | s Affected:             | None                                                                               |                                                                                                                                                                                                                                                                                      |                 |  |  |  |  |

| Enco        | ding:                   | 0011                                                                               | 11da ffi                                                                                                                                                                                                                                                                             | ff ffff         |  |  |  |  |

| Desc        | ription:                | incremented placed in W                                                            | The contents of register 'f' are<br>incremented. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed back in register 'f'. (default)                                                                                                                 |                 |  |  |  |  |

|             |                         | which is alre                                                                      | is '0', the next<br>eady fetched is<br>s executed ins<br>instruction.                                                                                                                                                                                                                | s discarded     |  |  |  |  |

|             |                         |                                                                                    | he Access Bar<br>he BSR is use<br>(default).                                                                                                                                                                                                                                         |                 |  |  |  |  |

|             |                         | set is enable<br>in Indexed I<br>mode when<br>Section 28<br>Bit-Oriente            | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 28.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                 |  |  |  |  |

| Word        | s:                      | 1                                                                                  | 1                                                                                                                                                                                                                                                                                    |                 |  |  |  |  |

| Cycle       | es:                     |                                                                                    | ycles if skip a<br>a 2-word instr                                                                                                                                                                                                                                                    |                 |  |  |  |  |

| QC          | ycle Activity:          |                                                                                    |                                                                                                                                                                                                                                                                                      |                 |  |  |  |  |

|             | Q1                      | Q2                                                                                 | Q3                                                                                                                                                                                                                                                                                   | Q4              |  |  |  |  |

|             | Decode                  | Read                                                                               | Process                                                                                                                                                                                                                                                                              | Write to        |  |  |  |  |

| الا مار     | ·                       | register 'f'                                                                       | Data                                                                                                                                                                                                                                                                                 | destination     |  |  |  |  |

| lf sk       | ip:<br>Q1               | Q2                                                                                 | Q3                                                                                                                                                                                                                                                                                   | Q4              |  |  |  |  |

| 1           | No                      | No                                                                                 | No                                                                                                                                                                                                                                                                                   | No              |  |  |  |  |

|             | operation               | operation                                                                          | operation                                                                                                                                                                                                                                                                            | operation       |  |  |  |  |

| lf sk       | ip and followe          | d by 2-word ins                                                                    | struction:                                                                                                                                                                                                                                                                           |                 |  |  |  |  |

|             | Q1                      | Q2                                                                                 | Q3                                                                                                                                                                                                                                                                                   | Q4              |  |  |  |  |

|             | No                      | No                                                                                 | No                                                                                                                                                                                                                                                                                   | No              |  |  |  |  |

|             | operation               | operation                                                                          | operation                                                                                                                                                                                                                                                                            | operation       |  |  |  |  |

|             | No<br>operation         | No<br>operation                                                                    | No<br>operation                                                                                                                                                                                                                                                                      | No<br>operation |  |  |  |  |

| ļ           | operation               | operation                                                                          | operation                                                                                                                                                                                                                                                                            | operation       |  |  |  |  |