Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 48MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 22                                                                           |

| Program Memory Size        | 64KB (32K x 16)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 3.8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                   |

| Data Converters            | A/D 10x10b/12b                                                               |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

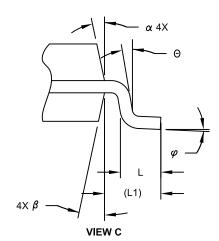

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 28-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf26j13t-i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: | DEVICE FEATURES FOR THE PIC18F2XJ13 (28-PIN DEVICES) |

|------------|------------------------------------------------------|

|            |                                                      |

| Features                             | PIC18F26J13                                                                  | PIC18F27J13            |  |

|--------------------------------------|------------------------------------------------------------------------------|------------------------|--|

| Operating Frequency                  | DC – 48 MHz                                                                  | DC – 48 MHz            |  |

| Program Memory (Kbytes)              | 64                                                                           | 128                    |  |

| Program Memory (Instructions)        | 32,768                                                                       | 65,536                 |  |

| Data Memory (Kbytes)                 | 3.8                                                                          | 3.8                    |  |

| Interrupt Sources                    | 3                                                                            | 0                      |  |

| I/O Ports                            | Ports /                                                                      | A, B, C                |  |

| Timers                               | 8                                                                            | 3                      |  |

| Enhanced Capture/Compare/PWM Modules | 3 ECCP a                                                                     | ind 7 CCP              |  |

| Serial Communications                | MSSP (2), Enha                                                               | nced USART (2)         |  |

| Parallel Communications (PMP/PSP)    | N                                                                            | lo                     |  |

| 10/12-Bit Analog-to-Digital Module   | 10 Input                                                                     | Channels               |  |

| Resets (and Delays)                  | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCI<br>(PWRT, OST) |                        |  |

| Instruction Set                      | 75 Instructions, 83 with Extended Instruction Set Enabled                    |                        |  |

| Packages                             | 28-Pin QFN, SOIC, SSO                                                        | OP and SPDIP (300 mil) |  |

### TABLE 1-2: DEVICE FEATURES FOR THE PIC18F4XJ13 (44-PIN DEVICES)

| Features                             | PIC18F46J13                    | PIC18F47J13                                   |

|--------------------------------------|--------------------------------|-----------------------------------------------|

| Operating Frequency                  | DC – 48 MHz                    | DC – 48 MHz                                   |

| Program Memory (Kbytes)              | 64                             | 128                                           |

| Program Memory (Instructions)        | 32,768                         | 65,536                                        |

| Data Memory (Kbytes)                 | 3.8                            | 3.8                                           |

| Interrupt Sources                    | 3                              | 0                                             |

| I/O Ports                            | Ports A, E                     | B, C, D, E                                    |

| Timers                               | 8                              | 3                                             |

| Enhanced Capture/Compare/PWM Modules | 3 ECCP a                       | IND 7 CCP                                     |

| Serial Communications                | MSSP (2), Enha                 | nced USART (2)                                |

| Parallel Communications (PMP/PSP)    | Ye                             | es                                            |

| 10/12-Bit Analog-to-Digital Module   | 13 Input                       | Channels                                      |

| Resets (and Delays)                  |                                | k Full, Stack Underflow, MCLR, WDT<br>T, OST) |

| Instruction Set                      | 75 Instructions, 83 with Exter | nded Instruction Set Enabled                  |

| Packages                             | 44-Pin QFN                     | and TQFP                                      |

#### REGISTER 4-3: DSGPR0: DEEP SLEEP PERSISTENT GENERAL PURPOSE REGISTER 0 (BANKED F4Eh)

| R/W-xxx                 | <sub>(</sub> (1)    |

|-------------------------|---------------------|

| Deep Sleep Persistent G | eneral Purpose bits |

| bit 7                   | bit 0               |

|                         |                     |

| Legend:                 |                     |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 Deep Sleep Persistent General Purpose bits Contents are retained even in Deep Sleep mode.

**Note 1:** All register bits are maintained unless VDDCORE drops below the normal BOR threshold outside of Deep Sleep, or the device is in Deep Sleep and the dedicated DSBOR is enabled and VDD drops below the DSBOR threshold, or DSBOR is enabled or disabled, but VDD is hard cycled to near VSS.

#### REGISTER 4-4: DSGPR1: DEEP SLEEP PERSISTENT GENERAL PURPOSE REGISTER 1 (BANKED F4Fh)

| R/W-xxxx <sup>(1)</sup>                    |       |

|--------------------------------------------|-------|

| Deep Sleep Persistent General Purpose bits |       |

| bit 7                                      | bit 0 |

|                                            |       |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-0 Deep Sleep Persistent General Purpose bits

Contents are retained even in Deep Sleep mode.

**Note 1:** All register bits are maintained unless VDDCORE drops below the normal BOR threshold outside of Deep Sleep, or the device is in Deep Sleep and the dedicated DSBOR is enabled and VDD drops below the DSBOR threshold, or DSBOR is enabled or disabled, but VDD is hard cycled to near Vss.

### REGISTER 4-5: DSWAKEH: DEEP SLEEP WAKE HIGH BYTE REGISTER (BANKED F4Bh)

| U-0             | U-0 | U-0              | U-0 | U-0                                     | U-0 | U-0 | R/W-0  |

|-----------------|-----|------------------|-----|-----------------------------------------|-----|-----|--------|

| —               | —   | —                | —   | —                                       | —   | —   | DSINT0 |

| bit 7           | •   |                  |     |                                         | •   | -   | bit 0  |

|                 |     |                  |     |                                         |     |     |        |

| Legend:         |     |                  |     |                                         |     |     |        |

| R = Readable b  | bit | W = Writable     | bit | U = Unimplemented bit, read as '0'      |     |     |        |

| -n = Value at P | OR  | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |     | nown   |

bit 7-1 Unimplemented: Read as '0'

DSINT0: Interrupt-on-Change bit

1 = Interrupt-on-change was asserted during Deep Sleep

0 = Interrupt-on-change was not asserted during Deep Sleep

bit 0

| Register | Applicable Devices |             | Sleep     |           | )<br>Wake-up via WDT<br>or Interrupt |  |

|----------|--------------------|-------------|-----------|-----------|--------------------------------------|--|

| CM3CON   | PIC18F2XJ13        | PIC18F4XJ13 | 0001 1111 | 0001 1111 | นนนน นนนน                            |  |

| TMR5H    | PIC18F2XJ13        | PIC18F4XJ13 | XXXX XXXX | นนนน นนนน | սսսս սսսս                            |  |

| TMR5L    | PIC18F2XJ13        | PIC18F4XJ13 | XXXX XXXX | սսսս սսսս | սսսս սսսս                            |  |

| T5CON    | PIC18F2XJ13        | PIC18F4XJ13 | 0000 0000 | սսսս սսսս | uuuu uuuu                            |  |

| T5GCON   | PIC18F2XJ13        | PIC18F4XJ13 | 0000 0x00 | uuuu uquu | uuuu uquu                            |  |

| TMR6     | PIC18F2XJ13        | PIC18F4XJ13 | 0000 0000 | 0000 0000 | uuuu uuuu                            |  |

| PR6      | PIC18F2XJ13        | PIC18F4XJ13 | 1111 1111 | 1111 1111 | นนนน นนนน                            |  |

| T6CON    | PIC18F2XJ13        | PIC18F4XJ13 | -000 0000 | -000 0000 | -uuu uuuu                            |  |

| TMR8     | PIC18F2XJ13        | PIC18F4XJ13 | 0000 0000 | 0000 0000 | սսսս սսսս                            |  |

| PR8      | PIC18F2XJ13        | PIC18F4XJ13 | 1111 1111 | 1111 1111 | uuuu uuuu                            |  |

| T8CON    | PIC18F2XJ13        | PIC18F4XJ13 | -000 0000 | -000 0000 | -uuu uuuu                            |  |

| PSTR3CON | PIC18F2XJ13        | PIC18F4XJ13 | 00-0 0001 | 00-0 0001 | uu-u uuuu                            |  |

| ECCP3AS  | PIC18F2XJ13        | PIC18F4XJ13 | 0000 0000 | 0000 0000 | uuuu uuuu                            |  |

| ECCP3DEL | PIC18F2XJ13        | PIC18F4XJ13 | 0000 0000 | 0000 0000 | uuuu uuuu                            |  |

| CCPR3H   | PIC18F2XJ13        | PIC18F4XJ13 | XXXX XXXX | uuuu uuuu | uuuu uuuu                            |  |

| CCPR3L   | PIC18F2XJ13        | PIC18F4XJ13 | XXXX XXXX | սսսս սսսս | uuuu uuuu                            |  |

| CCP3CON  | PIC18F2XJ13        | PIC18F4XJ13 | 0000 0000 | 0000 0000 | uuuu uuuu                            |  |

| CCPR4H   | PIC18F2XJ13        | PIC18F4XJ13 | XXXX XXXX | սսսս սսսս | uuuu uuuu                            |  |

| CCPR4L   | PIC18F2XJ13        | PIC18F4XJ13 | XXXX XXXX | սսսս սսսս | uuuu uuuu                            |  |

| CCP4CON  | PIC18F2XJ13        | PIC18F4XJ13 | 00 0000   | 00 0000   | uu uuuu                              |  |

| CCPR5H   | PIC18F2XJ13        | PIC18F4XJ13 | XXXX XXXX | սսսս սսսս | uuuu uuuu                            |  |

| CCPR5L   | PIC18F2XJ13        | PIC18F4XJ13 | XXXX XXXX | սսսս սսսս | սսսս սսսս                            |  |

| CCP5CON  | PIC18F2XJ13        | PIC18F4XJ13 | 00 0000   | 00 0000   | uu uuuu                              |  |

| CCPR6H   | PIC18F2XJ13        | PIC18F4XJ13 | XXXX XXXX | սսսս սսսս | uuuu uuuu                            |  |

| CCPR6L   | PIC18F2XJ13        | PIC18F4XJ13 | XXXX XXXX | uuuu uuuu | uuuu uuuu                            |  |

| CCP6CON  | PIC18F2XJ13        | PIC18F4XJ13 | 00 0000   | 00 0000   | uu uuuu                              |  |

| CCPR7H   | PIC18F2XJ13        | PIC18F4XJ13 | XXXX XXXX | սսսս սսսս | սսսս սսսս                            |  |

| CCPR7L   | PIC18F2XJ13        | PIC18F4XJ13 | XXXX XXXX | սսսս սսսս | սսսս սսսս                            |  |

| CCP7CON  | PIC18F2XJ13        | PIC18F4XJ13 | 00 0000   | 00 0000   | 00 0000                              |  |

| CCPR8H   | PIC18F2XJ13        | PIC18F4XJ13 | XXXX XXXX | սսսս սսսս | սսսս սսսս                            |  |

| CCPR8L   | PIC18F2XJ13        | PIC18F4XJ13 | XXXX XXXX | սսսս սսսս | սսսս սսսս                            |  |

| CCP8CON  | PIC18F2XJ13        | PIC18F4XJ13 | 00 0000   | 00 0000   | uu uuuu                              |  |

## TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, – = unimplemented bit, read as '0', q = value depends on condition.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 4: See Table 5-1 for the Reset value for a specific condition.

- 5: Not implemented on PIC18F2XJ13 devices.

- 6: Not implemented on "LF" devices.

# PIC18F47J13 FAMILY

| Pin                            | Function            | TRIS<br>Setting | I/O | I/O<br>Type    | Description                                                                                                       |

|--------------------------------|---------------------|-----------------|-----|----------------|-------------------------------------------------------------------------------------------------------------------|

| RA0/AN0/C1INA/                 | RA0                 | 1               | I   | TTL            | PORTA<0> data input; disabled when analog input is enabled.                                                       |

| ULPWU/PMA6/                    |                     | 0               | 0   | DIG            | LATA<0> data output; not affected by analog input.                                                                |

| RP0                            | AN0                 | 1               | I   | ANA            | A/D Input Channel 0 and Comparator C1- input. Default input configuration on POR; does not affect digital output. |

|                                | C1INA               | 1               | Ι   | ANA            | Comparator 1 Input A.                                                                                             |

|                                | ULPWU               | 1               | Ι   | ANA            | Ultra low-power wake-up input.                                                                                    |

|                                | PMA6 <sup>(1)</sup> | х               | I/O | ST/TTL/<br>DIG | Parallel Master Port digital I/O.                                                                                 |

|                                | RP0                 | 1               | Ι   | ST             | Remappable Peripheral Pin 0 input.                                                                                |

|                                |                     | 0               | 0   | DIG            | Remappable Peripheral Pin 0 output.                                                                               |

| RA1/AN1/C2INA/                 | RA1                 | 1               | Ι   | TTL            | PORTA<1> data input; disabled when analog input is enabled.                                                       |

| VBG/CTDIN/                     |                     | 0               | 0   | DIG            | LATA<1> data output; not affected by analog input.                                                                |

| PMA7/RP1                       | AN1                 | 1               | Ι   | ANA            | A/D Input Channel 1 and Comparator C2- input. Default input configuration on POR; does not affect digital output. |

|                                | C2INA               | 1               | Ι   | ANA            | Comparator 1 Input A.                                                                                             |

|                                | Vbg                 | х               | 0   | ANA            | Band Gap Voltage Reference output. (Enabled by setting the VBGOE bit (WDTCON<4>.)                                 |

|                                | CTDIN               | 1               | Ι   | ST             | CTMU pulse delay input.                                                                                           |

|                                | PMA7 <sup>(1)</sup> | 1               | Ι   | ST/TTL         | Parallel Master Port (io_addr_in[7]).                                                                             |

|                                |                     | 0               | 0   | DIG            | Parallel Master Port address.                                                                                     |

|                                | RP1                 | 1               | Ι   | ST             | Remappable Peripheral Pin 1 input.                                                                                |

|                                |                     | 0               | 0   | DIG            | Remappable Peripheral Pin 1 output                                                                                |

| RA2/AN2/C2INB/<br>C1IND/C3INB/ | RA2                 | 0               | 0   | DIG            | LATA<2> data output; not affected by analog input. Disabled when CVREF output is enabled.                         |

| VREF-/CVREF                    |                     | 1               | I   | TTL            | PORTA<2> data input. Disabled when analog functions are enabled; disabled when CVREF output is enabled.           |

|                                | AN2                 | 1               | Ι   | ANA            | A/D Input Channel 2 and Comparator C2+ input. Default input configuration on POR; not affected by analog output.  |

|                                | C2INB               | 1               | Ι   | ANA            | Comparator 2 Input B.                                                                                             |

|                                |                     | 0               | 0   | ANA            | CTMU pulse generator charger for the C2INB comparator input.                                                      |

|                                | C1IND               | 1               | Ι   | ANA            | Comparator 1 Input D.                                                                                             |

|                                | C3INB               | 1               | Ι   | ANA            | Comparator 3 Input B.                                                                                             |

|                                | VREF-               | 1               | Ι   | ANA            | A/D and comparator voltage reference low input.                                                                   |

|                                | CVREF               | х               | 0   | ANA            | Comparator voltage reference output. Enabling this feature disables digital I/O.                                  |

| RA3/AN3/C1INB/                 | RA3                 | 0               | 0   | DIG            | LATA<3> data output; not affected by analog input.                                                                |

| VREF+                          |                     | 1               | Ι   | TTL            | PORTA<3> data input; disabled when analog input is enabled.                                                       |

|                                | AN3                 | 1               | I   | ANA            | A/D Input Channel 3 and Comparator C1+ input. Default input configuration on POR.                                 |

|                                | C1INB               | 1               | Ι   | ANA            | Comparator 1 Input B                                                                                              |

|                                | VREF+               | 1               | Ι   | ANA            | A/D and comparator voltage reference high input.                                                                  |

TABLE 10-3: PORTA I/O SUMMARY

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRISx bit does not affect port direction or is overridden for this option)

**Note 1:** This bit is only available on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

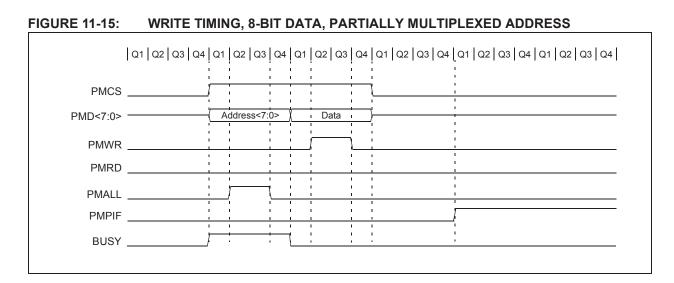

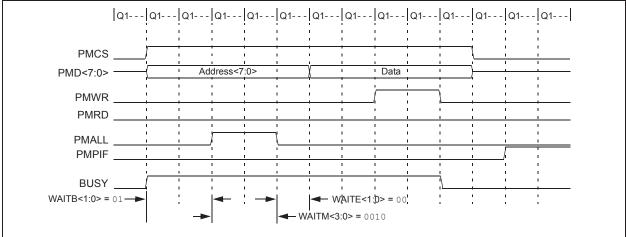

## FIGURE 11-16: WRITE TIMING, 8-BIT DATA, WAIT STATES ENABLED, PARTIALLY MULTIPLEXED ADDRESS

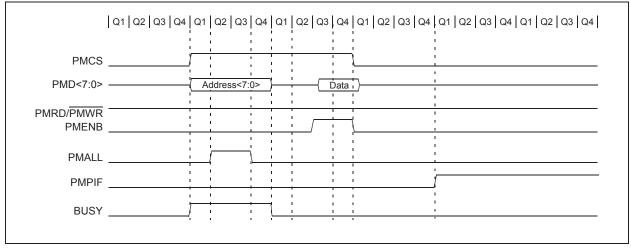

## FIGURE 11-17: READ TIMING, 8-BIT DATA, PARTIALLY MULTIPLEXED ADDRESS, ENABLE STROBE

#### 13.8.2 TIMER1 GATE SOURCE SELECTION

The Timer1 gate source can be selected from one of four different sources. Source selection is controlled by the T1GSSx bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

|  | <b>TABLE 13-4</b> : | TIMER1 GATE SOURCES | 3 |

|--|---------------------|---------------------|---|

|--|---------------------|---------------------|---|

| T1GSS<1:0> | Timer1 Gate Source  |

|------------|---------------------|

| 00         | Timer1 Gate Pin     |

| 01         | TMR2 matches PR2    |

| 10         | Comparator 1 output |

| 11         | Comparator 2 output |

13.8.2.1 T1G Pin Gate Operation

The T1G pin is one source for Timer1 gate control. It can be used to supply an external source to the Timer1 gate circuitry.

13.8.2.2 Timer2 Match Gate Operation

The TMR2 register will increment until it matches the value in the PR2 register. On the very next increment cycle, TMR2 will be reset to 00h. When this Reset

occurs, a low-to-high pulse will automatically be generated and internally supplied to the Timer1 gate circuitry. The pulse remains high for one instruction cycle and returns to low until the next match.

When T1GPOL = 1, Timer1 increments for a single instruction cycle following TMR2 matching PR2. With T1GPOL = 0, Timer1 increments except during the cycle following the match.

## 13.8.3 TIMER1 GATE TOGGLE MODE

When Timer1 Gate Toggle mode is enabled, it is possible to measure the full cycle length of a Timer1 gate signal, as opposed to the duration of a single level pulse.

The Timer1 gate source is routed through a flip-flop that changes state on every incrementing edge of the signal. See Figure 13-5 for timing details.

The T1GVAL bit will indicate when the Toggled mode is active and the timer is counting.

The Timer1 Gate Toggle mode is enabled by setting the T1GTM bit of the T1GCON register. When the T1GTM bit is cleared, the flip-flop is cleared and held clear. This is necessary in order to control which edge is measured.

##

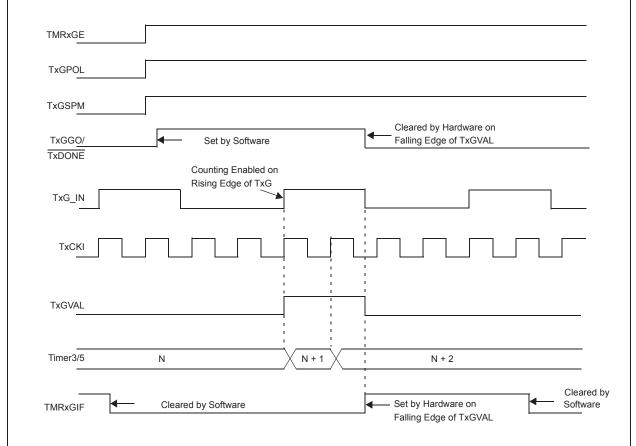

#### 15.5.4 TIMER3/5 GATE SINGLE PULSE MODE

When Timer3/5 Gate Single Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer3/5 Gate Single Pulse mode is first enabled by setting the TxGSPM bit (TxGCON<4>). Next, the TxGGO/TxDONE bit (TxGCON<3>) must be set.

The Timer3/5 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the TxGGO/TxDONE bit will automatically be cleared. No other gate events will be allowed to increment Timer3/5 until the TxGGO/TxDONE bit is once again set in software.

Clearing the TxGSPM bit will also clear the TxGGO/TxDONE bit. (For timing details, see Figure 15-4.)

Simultaneously, enabling the Toggle mode and the Single Pulse mode will permit both sections to work together. This allows the cycle times on the Timer3/5 gate source to be measured. (For timing details, see Figure 15-5.)

## FIGURE 15-4: TIMER3/5 GATE SINGLE PULSE MODE

## 17.6 Register Maps

Table 17-5, Table 17-6 and Table 17-7 summarize the registers associated with the RTCC module.

| File Name | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2     | Bit 1     | Bit 0    | All<br>Resets |

|-----------|--------|--------|---------|---------|---------|-----------|-----------|----------|---------------|

| RTCCFG    | RTCEN  | —      | RTCWREN | RTCSYNC | HALFSEC | RTCOE     | RTCPTR1   | RTCPTR0  | 0000          |

| RTCCAL    | CAL7   | CAL6   | CAL5    | CAL4    | CAL3    | CAL2      | CAL1      | CAL0     | 0000          |

| PADCFG1   | _      | —      | _       | —       | _       | RTSECSEL1 | RTSECSEL0 | PMPTTL   | 0000          |

| ALRMCFG   | ALRMEN | CHIME  | AMASK3  | AMASK2  | AMASK1  | AMASK0    | ALRMPTR1  | ALRMPTR0 | 0000          |

| ALRMRPT   | ARPT7  | ARPT6  | ARPT5   | ARPT4   | ARPT3   | ARPT2     | ARPT1     | ARPT0    | 0000          |

| PIR3      | SSP2IF | BCL2IF | RC2IF   | TX2IF   | TMR4IF  | CTMUIF    | TMR3GIF   | RTCCCIF  | 0000          |

| PIE3      | SSP2IE | BCL2IE | RC2IE   | TX2IE   | TMR4IE  | CTMUIE    | TMR3GIE   | RTCCCIE  | 0000          |

| IPR3      | SSP2IP | BCL2IP | RC2IP   | TX2IP   | TMR4IP  | CTMUIP    | TMR3GIP   | RTCCCIP  | 0000          |

### TABLE 17-5: RTCC CONTROL REGISTERS

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal for 44-pin devices.

#### TABLE 17-6: RTCC VALUE REGISTERS

| File Name | Bit 7                                                           | Bit 6       | Bit 5       | Bit 4        | Bit 3    | Bit 2  | Bit 1    | Bit 0    | All Resets |

|-----------|-----------------------------------------------------------------|-------------|-------------|--------------|----------|--------|----------|----------|------------|

| RTCVALH   | VALH RTCC Value Register Window High Byte, Based on RTCPTR<1:0> |             |             |              |          |        |          |          | XXXX       |

| RTCVALL   | RTCC Value Register Window Low Byte, Based on RTCPTR<1:0>       |             |             |              |          |        |          |          | XXXX       |

| RTCCFG    | RTCEN                                                           | _           | RTCWREN     | RTCSYNC      | HALFSEC  | RTCOE  | RTCPTR1  | RTCPTR0  | 0000       |

| ALRMCFG   | ALRMEN                                                          | CHIME       | AMASK3      | AMASK2       | AMASK1   | AMASK0 | ALRMPTR1 | ALRMPTR0 | 0000       |

| ALRMVALH  | Alarm Value Register Window High Byte, Based on ALRMPTR<1:0>    |             |             |              |          |        |          |          | XXXX       |

| ALRMVALL  | Alarm Value                                                     | Register Wi | ndow Low By | te, Based on | ALRMPTR< | :1:0>  |          |          | XXXX       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal for 44-pin devices.

## TABLE 17-7: ALARM VALUE REGISTERS

| File Name | Bit 7                                                             | Bit 6         | Bit 5         | Bit 4        | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|-------------------------------------------------------------------|---------------|---------------|--------------|------------|-------|-------|-------|---------------|

| ALRMRPT   | ARPT7                                                             | ARPT6         | ARPT5         | ARPT4        | ARPT3      | ARPT2 | ARPT1 | ARPT0 | 0000          |

| ALRMVALH  | LH Alarm Value Register Window High Byte, Based on ALRMPTR<1:0>   |               |               |              |            |       |       |       |               |

| ALRMVALL  | Alarm Value R                                                     | egister Windo | w Low Byte, E | Based on ALF | RMPTR<1:0> |       |       |       | XXXX          |

| RTCCAL    | CAL7                                                              | CAL6          | CAL5          | CAL4         | CAL3       | CAL2  | CAL1  | CAL0  | 0000          |

| RTCVALH   | TCVALH RTCC Value Register Window High Byte, Based on RTCPTR<1:0> |               |               |              |            |       |       |       |               |

| RTCVALL   | LL RTCC Value Register Window Low Byte, Based on RTCPTR<1:0>      |               |               |              |            |       |       |       |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal for 44-pin devices.

| TADLE 10-4. |             |               |          |          |          |               |          |          |  |  |

|-------------|-------------|---------------|----------|----------|----------|---------------|----------|----------|--|--|

| Name        | Bit 7       | Bit 6         | Bit 5    | Bit 4    | Bit 3    | Bit 2         | Bit 1    | Bit 0    |  |  |

| INTCON      | GIE/GIEH    | PEIE/GIEL     | TMR0IE   | INT0IE   | RBIE     | TMR0IF        | INT0IF   | RBIF     |  |  |

| RCON        | IPEN        | _             | CM       | RI       | TO       | PD            | POR      | BOR      |  |  |

| PIR4        | CCP10IF     | CCP9IF        | CCP8IF   | CCP7IF   | CCP6IF   | CCP5IF        | CCP4IF   | CCP3IF   |  |  |

| PIE4        | CCP10IE     | CCP9IE        | CCP8IE   | CCP7IE   | CCP6IE   | CCP5IE        | CCP4IE   | CCP3IE   |  |  |

| IPR4        | CCP10IP     | CCP9IP        | CCP8IP   | CCP7IP   | CCP6IP   | CCP5IP        | CCP4IP   | CCP3IP   |  |  |

| TRISB       | TRISB7      | TRISB6        | TRISB5   | TRISB4   | TRISB3   | TRISB2        | TRISB1   | TRISB0   |  |  |

| TRISC       | TRISC7      | TRISC6        | TRISC5   | TRISC4   | TRISC3   | TRISC2        | TRISC1   | TRISC0   |  |  |

| TRISE       | RDPU        | REPU          | _        | _        | _        | TRISE2        | TRISE1   | TRISE0   |  |  |

| TMR1L       | Timer1 Regi | ster Low Byte | Э        |          |          |               |          |          |  |  |

| TMR1H       | Timer1 Regi | ster High Byt | е        |          |          |               |          |          |  |  |

| TMR3L       | Timer3 Regi | ster Low Byte | Э        |          |          |               |          |          |  |  |

| TMR3H       | Timer3 Regi | ster High Byt | е        |          |          |               |          |          |  |  |

| TMR5L       | Timer5 Regi | ster Low Byte | 9        |          |          |               |          |          |  |  |

| TMR5H       | Timer5 Regi | ster High Byt | е        |          |          |               |          |          |  |  |

| T1CON       | TMR1CS1     | TMR1CS0       | T1CKPS1  | T1CKPS0  | T1OSCEN  | T1SYNC        | RD16     | TMR10N   |  |  |

| T3CON       | TMR3CS1     | TMR3CS0       | T3CKPS1  | T3CKPS0  | T3OSCEN  | <b>T3SYNC</b> | RD16     | TMR3ON   |  |  |

| T5CON       | TMR5CS1     | TMR5CS0       | T5CKPS1  | T5CKPS0  | T5OSCEN  | T5SYNC        | RD16     | TMR50N   |  |  |

| CCPR4L      | CCPR4L7     | CCPR4L6       | CCPR4L5  | CCPR4L4  | CCPR4L3  | CCPR4L2       | CCPR4L1  | CCPR4L0  |  |  |

| CCPR4H      | CCPR4H7     | CCPR4H6       | CCPR4H5  | CCPR4H4  | CCPR4H3  | CCPR4H2       | CCPR4H1  | CCPR4H0  |  |  |

| CCPR5L      | CCPR5L7     | CCPR5L6       | CCPR5L5  | CCPR5L4  | CCPR5L3  | CCPR5L2       | CCPR5L1  | CCPR5L0  |  |  |

| CCPR5H      | CCPR5H7     | CCPR5H6       | CCPR5H5  | CCPR5H4  | CCPR5H3  | CCPR5H2       | CCPR5H1  | CCPR5H0  |  |  |

| CCPR6L      | CCPR6L7     | CCPR6L6       | CCPR6L5  | CCPR6L4  | CCPR6L3  | CCPR6L2       | CCPR6L1  | CCPR6L0  |  |  |

| CCPR6H      | CCPR6H7     | CCPR6H6       | CCPR6H5  | CCPR6H4  | CCPR6H3  | CCPR6H2       | CCPR6H1  | CCPR6H0  |  |  |

| CCPR7L      | CCPR7L7     | CCPR7L6       | CCPR7L5  | CCPR7L4  | CCPR7L3  | CCPR7L2       | CCPR7L1  | CCPR7L0  |  |  |

| CCPR7H      | CCPR7H7     | CCPR7H6       | CCPR7H5  | CCPR7H4  | CCPR7H3  | CCPR7H2       | CCPR7H1  | CCPR7H0  |  |  |

| CCPR8L      | CCPR8L7     | CCPR8L6       | CCPR8L5  | CCPR8L4  | CCPR8L3  | CCPR8L2       | CCPR8L1  | CCPR8L0  |  |  |

| CCPR8H      | CCPR8H7     | CCPR8H6       | CCPR8H5  | CCPR8H4  | CCPR8H3  | CCPR8H2       | CCPR8H1  | CCPR8H0  |  |  |

| CCPR9L      | CCPR9L7     | CCPR9L6       | CCPR9L5  | CCPR9L4  | CCPR9L3  | CCPR9L2       | CCPR9L1  | CCPR9L0  |  |  |

| CCPR9H      | CCPR9H7     | CCPR9H6       | CCPR9H5  | CCPR9H4  | CCPR9H3  | CCPR9H2       | CCPR9H1  | CCPR9H0  |  |  |

| CCPR10L     | CCPR10L7    | CCPR10L6      | CCPR10L5 | CCPR10L4 | CCPR10L3 | CCPR10L2      | CCPR10L1 | CCPR10L0 |  |  |

| CCPR10H     | CCPR10H7    | CCPR10H6      | CCPR10H5 | CCPR10H4 | CCPR10H3 | CCPR10H2      | CCPR10H1 | CCPR10H0 |  |  |

| CCP4CON     | _           |               | DC4B1    | DC4B0    | CCP4M3   | CCP4M2        | CCP4M1   | CCP4M0   |  |  |

| CCP5CON     | _           |               | DC5B1    | DC5B0    | CCP5M3   | CCP5M2        | CCP5M1   | CCP5M0   |  |  |

| CCP6CON     | _           | _             | DC6B1    | DC6B0    | CCP6M3   | CCP6M2        | CCP6M1   | CCP6M0   |  |  |

| CCP7CON     | —           | _             | DC7B1    | DC7B0    | CCP7M3   | CCP7M2        | CCP7M1   | CCP7M0   |  |  |

| CCP8CON     |             | _             | DC8B1    | DC8B0    | CCP8M3   | CCP8M2        | CCP8M1   | CCP8M0   |  |  |

| CCP9CON     | _           |               | DC9B1    | DC9B0    | CCP9M3   | CCP9M2        | CCP9M1   | CCP9M0   |  |  |

| CCP10CON    | _           |               | DC10B1   | DC10B0   | CCP10M3  | CCP10M2       | CCP10M1  | CCP10M0  |  |  |

| CCPTMRS1    | C7TSEL1     | C7TSEL0       |          | C6TSEL0  |          | C5TSEL0       | C4TSEL1  | C4TSEL0  |  |  |

|             |             |               |          | C10TSEL0 |          | C9TSEL0       | C8TSEL1  | C8TSEL0  |  |  |

| <b>TABLE 18-4</b> : | REGISTERS ASSOCIATED WITH CAPTURE, COMPARE, TIMER1/3/5/7 |

|---------------------|----------------------------------------------------------|

|---------------------|----------------------------------------------------------|

Legend: — = unimplemented, read as '0'. Shaded cells are not used by capture/compare or Timer1/3/5.

## 19.1 ECCP Outputs and Configuration

The Enhanced CCP module may have up to four PWM outputs, depending on the selected operating mode. These outputs, designated PxA through PxD, are routed through the Peripheral Pin Select (PPS) module. Therefore, individual functions can be mapped to any of the remappable I/O pins (RPn).

The outputs that are active depend on the ECCP operating mode selected. The pin assignments are summarized in Table 19-3.

To configure the I/O pins as PWM outputs, the proper PWM mode must be selected by setting the PxM<1:0> and CCPxM<3:0> bits. The appropriate TRIS direction bits for the port pins must also be set as outputs.

#### 19.1.1 ECCP MODULE AND TIMER RESOURCES

The ECCP modules use Timer1, 2, 3, 4, 6 or 8, depending on the mode selected. These timers are available to CCP modules in Capture, Compare or PWM modes, as shown in Table 19-1.

## TABLE 19-1:ECCP MODE – TIMER<br/>RESOURCE

| ECCP Mode | Timer Resource                   |

|-----------|----------------------------------|

| Capture   | Timer1 or Timer3                 |

| Compare   | Timer1 or Timer3                 |

| PWM       | Timer2, Timer4, Timer6 or Timer8 |

The assignment of a particular timer to a module is determined by the Timer to ECCP enable bits in the CCPTMRS0 register (Register 19-2). The interactions between the two modules are depicted in Figure 19-1. Capture operations are designed to be used when the timer is configured for Synchronous Counter mode. Capture operations may not work as expected if the associated timer is configured for Asynchronous Counter mode.

## 19.2 Capture Mode

In Capture mode, the CCPRxH:CCPRxL register pair captures the 16-bit value of the TMR1 or TMR3 registers when an event occurs on the corresponding ECCPx pin. An event is defined as one of the following:

- · Every falling edge

- Every rising edge

- Every fourth rising edge

- Every 16<sup>th</sup> rising edge

The event is selected by the mode select bits, CCPxM<3:0> (CCPxCON register<3:0>). When a capture is made, the interrupt request flag bit, CCPxIF, is set (see Table 19-2). The flag must be cleared by software. If another capture occurs before the value in the CCPRxH/L register pair is read, the old captured value is overwritten by the new captured value.

| TABLE 19-2: | ECCP1/2/3 INTERRUPT FLAG |

|-------------|--------------------------|

|             | BITS                     |

| ECCP Module | Flag-Bit |

|-------------|----------|

| 1           | PIR1<2>  |

| 2           | PIR2<0>  |

| 3           | PIR4<0>  |

### 19.2.1 ECCP PIN CONFIGURATION

In Capture mode, the appropriate ECCPx pin should be configured as an input by setting the corresponding TRISx direction bit.

Additionally, the ECCPx input function needs to be assigned to an I/O pin through the Peripheral Pin Select module. For details on setting up the remappable pins, see Section 10.7 "Peripheral Pin Select (PPS)".

**Note:** If the ECCPx pin is configured as an output, a write to the port can cause a capture condition.

© 2010-2017 Microchip Technology Inc.

DS30009974C-page 310

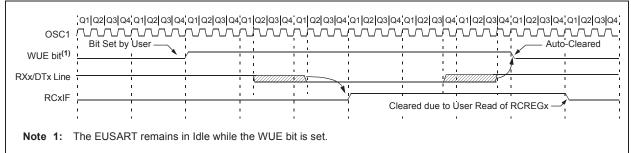

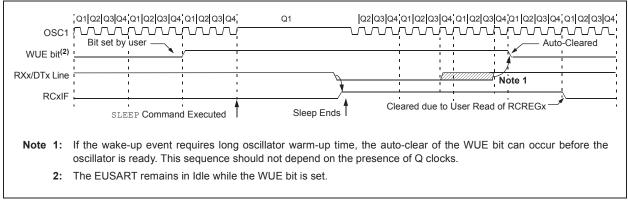

The WUE bit is automatically cleared once a low-to-high transition is observed on the RXx line following the wake-up event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

#### 21.2.4.1 Special Considerations Using Auto-Wake-up

Since auto-wake-up functions by sensing rising edge transitions on RXx/DTx, information with any state changes before the Stop bit may signal a false End-Of-Character (EOC) and cause data or framing errors. To work properly, therefore, the initial character in the transmission must be all '0's. This can be 00h (8 bits) for standard RS-232 devices or 000h (12 bits) for LIN/J2602 bus.

Oscillator start-up time must also be considered, especially in applications using oscillators with longer start-up intervals (i.e., HS or HSPLL mode). The Sync Break (or Wake-up Signal) character must be of sufficient length and be followed by a sufficient interval to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

## 21.2.4.2 Special Considerations Using the WUE Bit

The timing of WUE and RCxIF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the EUSART in an Idle mode. The wake-up event causes a receive interrupt by setting the RCxIF bit. The WUE bit is cleared after this when a rising edge is seen on RXx/DTx. The interrupt condition is then cleared by reading the RCREGx register. Ordinarily, the data in RCREGx will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set) and the RCxIF flag is set should not be used as an indicator of the integrity of the data in RCREGx. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process. If a receive operation is not occurring, the WUE bit may then be set just prior to entering Sleep mode.

## FIGURE 21-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING NORMAL OPERATION

## FIGURE 21-9: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

## 24.2 Voltage Reference Accuracy/Error

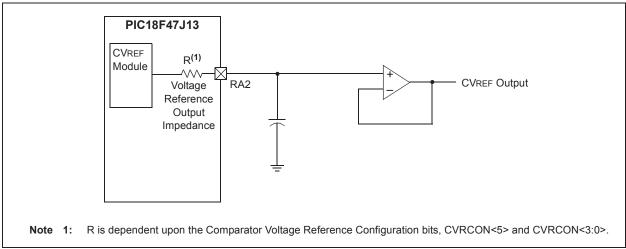

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (see Figure 24-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the CVREF output changes with fluctuations in that source. The tested absolute accuracy of the voltage reference can be found in Section 30.0 "Electrical Characteristics".

## 24.3 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the CVROE bit is set. Enabling the voltage reference output onto RA2 when it is configured as a digital input will increase current consumption. Connecting RA2 as a digital output with CVRSS enabled will also increase current consumption. The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, a buffer must be used on the voltage reference output for external connections to VREF. See Figure 24-2 for an example buffering technique.

## 24.4 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

## 24.5 Effects of a Reset

A device Reset disables the voltage reference by clearing bit, CVREN (CVRCON<7>). This Reset also disconnects the reference from the RA2 pin by clearing bit, CVROE (CVRCON<6>) and selects the high-voltage range by clearing bit, CVRR (CVRCON<5>). The CVR value select bits are also cleared.

| Name   | Bit 7                | Bit 6                | Bit 5                | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|--------|----------------------|----------------------|----------------------|--------|--------|--------|--------|--------|

| CVRCON | CVREN                | CVROE                | CVRR                 | CVRSS  | CVR3   | CVR2   | CVR1   | CVR0   |

| CM1CON | CON                  | COE                  | CPOL                 | EVPOL1 | EVPOL0 | CREF   | CCH1   | CCH0   |

| CM2CON | CON                  | COE                  | CPOL                 | EVPOL1 | EVPOL0 | CREF   | CCH1   | CCH0   |

| CM3CON | CON                  | COE                  | CPOL                 | EVPOL1 | EVPOL0 | CREF   | CCH1   | CCH0   |

| TRISA  | TRISA7               | TRISA6               | TRISA5               | —      | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| ANCON0 | PCFG7 <sup>(1)</sup> | PCFG6 <sup>(1)</sup> | PCFG5 <sup>(1)</sup> | PCFG4  | PCFG3  | PCFG2  | PCFG1  | PCFG0  |

**Legend:** — = unimplemented, read as '0', r = reserved. Shaded cells are not used with the comparator voltage reference.

Note 1: These bits are only available on 44-pin devices.

## 25.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake-up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

## 25.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Name    | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|---------|----------|-----------|--------|--------|--------|--------|--------|--------|

| HLVDCON | VDIRMAG  | BGVST     | IRVST  | HLVDEN | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   |

| PIR2    | OSCFIF   | CM2IF     | CM1IF  | —      | BCL1IF | HLVDIF | TMR3IF | CCP2IF |

| PIE2    | OSCFIE   | CM2IE     | CM1IE  | _      | BCL1IE | HLVDIE | TMR3IE | CCP2IE |

| IPR2    | OSCFIP   | CM2IP     | CM1IP  | _      | BCL1IP | HLVDIP | TMR3IP | CCP2IP |

#### TABLE 25-1: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

# PIC18F47J13 FAMILY

|                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                         | 501                                                                                           |                                                                                                                                                                                                                                       |  |  |  |  |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| BTG                                                   | Bit Toggle f                                                                                                                                                                                                                                                                                                                                                                                                            | BOV                                                                                           | Branch if Overflow                                                                                                                                                                                                                    |  |  |  |  |

| Syntax:                                               | BTG f, b {,a}                                                                                                                                                                                                                                                                                                                                                                                                           | Syntax:                                                                                       | BOV n                                                                                                                                                                                                                                 |  |  |  |  |

| Operands:                                             | $0 \leq f \leq 255$                                                                                                                                                                                                                                                                                                                                                                                                     | Operands:                                                                                     | $-128 \le n \le 127$                                                                                                                                                                                                                  |  |  |  |  |

|                                                       | 0 ≤ b < 7<br>a ∈ [0,1]                                                                                                                                                                                                                                                                                                                                                                                                  | Operation:                                                                                    | if Overflow bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                                                                                                             |  |  |  |  |

| Operation:                                            | $(\overline{f} < b >) \to f < b >$                                                                                                                                                                                                                                                                                                                                                                                      | Status Affected:                                                                              | None                                                                                                                                                                                                                                  |  |  |  |  |

| Status Affected:                                      | None                                                                                                                                                                                                                                                                                                                                                                                                                    | Encoding:                                                                                     | 1110 0100 nnnn nnnn                                                                                                                                                                                                                   |  |  |  |  |

| Encoding:<br>Description:                             | Ĵ                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                               | If the Overflow bit is '1', then the program will branch.                                                                                                                                                                             |  |  |  |  |

|                                                       | inverted.<br>If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 28.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. | Words:<br>Cycles:<br>Q Cycle Activity:<br>If Jump:                                            | The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>2-cycle instruction.<br>1<br>1(2) |  |  |  |  |

| Words:                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                       | Q1                                                                                            | Q2 Q3 Q4                                                                                                                                                                                                                              |  |  |  |  |

| Cycles:                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                       | Decode                                                                                        | Read literalProcessWrite to PC'n'Data                                                                                                                                                                                                 |  |  |  |  |

| Q Cycle Activity:                                     |                                                                                                                                                                                                                                                                                                                                                                                                                         | No                                                                                            | No No No                                                                                                                                                                                                                              |  |  |  |  |

| Q1                                                    | Q2 Q3 Q4                                                                                                                                                                                                                                                                                                                                                                                                                | operation                                                                                     | operation operation operation                                                                                                                                                                                                         |  |  |  |  |

| Decode                                                | Read Process Write                                                                                                                                                                                                                                                                                                                                                                                                      | If No Jump:                                                                                   |                                                                                                                                                                                                                                       |  |  |  |  |

|                                                       | register 'f' Data register 'f'                                                                                                                                                                                                                                                                                                                                                                                          | Q1                                                                                            | Q2 Q3 Q4                                                                                                                                                                                                                              |  |  |  |  |

| Example:                                              | BTG PORTC, 4, 0                                                                                                                                                                                                                                                                                                                                                                                                         | Decode                                                                                        | Read literalProcessNo'n'Dataoperation                                                                                                                                                                                                 |  |  |  |  |

| Before Instruct<br>PORTC<br>After Instructio<br>PORTC | = 0111 0101 <b>[75h]</b><br>n:                                                                                                                                                                                                                                                                                                                                                                                          | Example:<br>Before Instruct<br>PC<br>After Instructio<br>If Overflo<br>PC<br>If Overflo<br>PC | = address (HERE)<br>on<br>ow = 1;<br>= address (Jump)                                                                                                                                                                                 |  |  |  |  |

## PIC18F47J13 FAMILY

| XORWF                                                                                                                                                                                      |              | Exclusive                                           | OR W w                                                                                                                                                              | ith f |   |                                                |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---|------------------------------------------------|--|--|--|

| Syntax:                                                                                                                                                                                    |              | XORWF                                               | XORWF f {,d {,a}}                                                                                                                                                   |       |   |                                                |  |  |  |

| Operan                                                                                                                                                                                     | ds:          | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$ | d ∈ [0,1]                                                                                                                                                           |       |   |                                                |  |  |  |

| Operati                                                                                                                                                                                    | on:          | (W) .XOR.                                           | $(f) \rightarrow des$                                                                                                                                               | st    |   |                                                |  |  |  |

| Status /                                                                                                                                                                                   | Affected:    | N, Z                                                | N, Z                                                                                                                                                                |       |   |                                                |  |  |  |

| Encodir                                                                                                                                                                                    | ng:          | 0001                                                | 10da                                                                                                                                                                | fff   | f | ffff                                           |  |  |  |

| Descrip                                                                                                                                                                                    | tion:        | register 'f'.<br>in W. If 'd' i                     | Exclusive OR the contents of W with register 'f'. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in the register 'f' (default). |       |   |                                                |  |  |  |

|                                                                                                                                                                                            |              | lf 'a' is '1', t                                    | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).                                                  |       |   |                                                |  |  |  |

| If 'a' is '0' and the extense<br>set is enabled, this inst<br>in Indexed Literal Offse<br>mode whenever f ≤ 95<br>Section 28.2.3 "Byte<br>Bit-Oriented Instructi<br>Literal Offset Mode" f |              |                                                     |                                                                                                                                                                     |       |   | operates<br>essing<br>See<br>ed and<br>Indexed |  |  |  |

| Words:                                                                                                                                                                                     |              | 1                                                   |                                                                                                                                                                     |       |   |                                                |  |  |  |

| Cycles:                                                                                                                                                                                    |              | 1                                                   |                                                                                                                                                                     |       |   |                                                |  |  |  |

| Q Cycl                                                                                                                                                                                     | le Activity: |                                                     |                                                                                                                                                                     |       |   |                                                |  |  |  |

|                                                                                                                                                                                            | Q1           | Q2                                                  | Q3                                                                                                                                                                  | 3     |   | Q4                                             |  |  |  |

|                                                                                                                                                                                            | Decode       | Read<br>register 'f'                                | Proce<br>Data                                                                                                                                                       |       |   | /rite to<br>stination                          |  |  |  |

| Example: XORWF REG, 1, 0<br>Before Instruction                                                                                                                                             |              |                                                     |                                                                                                                                                                     |       |   |                                                |  |  |  |

| REG = AFh<br>W = B5h                                                                                                                                                                       |              |                                                     |                                                                                                                                                                     |       |   |                                                |  |  |  |

| After Instruction<br>REG = 1Ah<br>W = B5h                                                                                                                                                  |              |                                                     |                                                                                                                                                                     |       |   |                                                |  |  |  |

|              |        | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                 |          |       |                                       |

|--------------|--------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------|-------|---------------------------------------|

| Param<br>No. | Symbol | Characteristic                                                                                                                         | Min             | Мах      | Units | Conditions                            |

|              | VIL    | Input Low Voltage                                                                                                                      |                 |          |       |                                       |

|              |        | All I/O Ports:                                                                                                                         |                 |          |       |                                       |

| D030         |        | with TTL Buffer                                                                                                                        | Vss             | 0.15 Vdd | V     | VDD < 3.3V                            |

| D030A        |        | with TTL Buffer                                                                                                                        | Vss             | 0.8      | V     | 3.3V <u>≤</u> VDD <u>≤</u> 3.6V       |

| D031         |        | with Schmitt Trigger Buffer                                                                                                            | Vss             | 0.2 Vdd  | V     |                                       |

| D031A        |        | SCLx/SDAx                                                                                                                              | —               | 0.3 Vdd  | V     | I <sup>2</sup> C enabled              |

| D031B        |        | SCLx/SDAx                                                                                                                              | —               | 0.8      | V     | SMBus enabled                         |

| D032         |        | MCLR                                                                                                                                   | Vss             | 0.2 Vdd  | V     |                                       |

| D033         |        | OSC1                                                                                                                                   | Vss             | 0.3 Vdd  | V     | HS, HSPLL modes                       |

| D033A        |        | OSC1                                                                                                                                   | Vss             | 0.2 Vdd  | V     | EC, ECPLL modes                       |

| D034         |        | T1OSI                                                                                                                                  | Vss             | 0.3      | V     | T1OSCEN = 1                           |

|              | Vih    | Input High Voltage<br>I/O Ports without 5.5V<br>Tolerance:                                                                             |                 |          |       |                                       |

| D040         |        | with TTL Buffer                                                                                                                        | 0.25 VDD + 0.8V | Vdd      | V     | VDD < 3.3V                            |

| D040A        |        | with TTL Buffer                                                                                                                        | 2.0             | Vdd      | V     | 3.3V <u>&lt;</u> Vdd <u>&lt;</u> 3.6V |

| D041         |        | with Schmitt Trigger Buffer<br>I/O Ports with 5.5V Tolerance: <sup>(4)</sup>                                                           | 0.8 Vdd         | Vdd      | V     |                                       |

| Dxxx         |        | with TTL Buffer                                                                                                                        | 0.25 VDD + 0.8V | 5.5      | V     | VDD < 3.3V                            |

| DxxxA        |        |                                                                                                                                        | 2.0             | 5.5      | V     | $3.3V \le V\text{DD} \le 3.6V$        |

| Dxxx         |        | with Schmitt Trigger Buffer                                                                                                            | 0.8 Vdd         | 5.5      | V     |                                       |

| D041A        |        | SCLx/SDAx                                                                                                                              | 0.7 Vdd         | _        | V     | I <sup>2</sup> C enabled              |

| D041B        |        | SCLx/SDAx                                                                                                                              | 2.1             | _        | V     | SMBus enabled; VDD <u>&gt;</u> 3V     |

| D042         |        | MCLR                                                                                                                                   | 0.8 Vdd         | 5.5      | V     |                                       |

| D043         |        | OSC1                                                                                                                                   | 0.7 Vdd         | Vdd      | V     | HS, HSPLL modes                       |

| D043A        |        | OSC1                                                                                                                                   | 0.8 VDD         | Vdd      | V     | EC, ECPLL modes                       |

| D044         |        | T1OSI                                                                                                                                  | 1.6             | Vdd      | V     | T1OSCEN = 1                           |

|              | IPU    | Weak Pull-up Current                                                                                                                   |                 |          |       |                                       |

| D070         | IPURB  | PORTB, PORTD <sup>(3)</sup> and<br>PORTE <sup>(3)</sup> Weak Pull-up Current                                                           | 80              | 400      | μA    | VDD = 3.3V, VPIN = VSS                |

## 30.3 DC Characteristics: PIC18F47J13 Family (Industrial)

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**2:** Negative current is defined as current sourced by the pin.

**3:** Only available in 44-pin devices.

4: Refer to Table 10-2 for pin tolerance levels.

| Param<br>No. | Sym             | Characteristic                | Min | Тур† | Max | Units | Conditions |  |