#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                  |

| Data Converters            | A/D 10x10b/12b                                                              |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 28-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf27j13-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 6.1.1 HARD MEMORY VECTORS

All PIC18 devices have a total of three hard-coded return vectors in their program memory space. The Reset vector address is the default value to which the program counter returns on all device Resets; it is located at 0000h.

PIC18 devices also have two interrupt vector addresses for handling high-priority and low-priority interrupts. The high-priority interrupt vector is located at 0008h and the low-priority interrupt vector at 0018h. Figure 6-2 provides their locations in relation to the program memory map.

#### FIGURE 6-2: HARD VECTOR AND CONFIGURATION WORD LOCATIONS FOR PIC18F47J13 FAMILY DEVICES

|         | Reset Vector                                                                                                        | 0000h                                    |

|---------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| High-P  | riority Interrupt Vector                                                                                            | 0008h                                    |

| Low-P   | riority Interrupt Vector                                                                                            | 0018h                                    |

| F       | On-Chip<br>Program Memory                                                                                           |                                          |

| Flash   | Configuration Words                                                                                                 | (Top of Memory-7)<br>(Top of Memory)     |

|         | Read as '0'                                                                                                         |                                          |

|         |                                                                                                                     | 1FFFFh                                   |

| Legend: | (Top of Memory) repr<br>of on-chip program m<br>Figure 6-1 for device<br>Shaded area represe<br>memory. Areas are n | -specific values).<br>ents unimplemented |

# 6.1.2 FLASH CONFIGURATION WORDS

Because PIC18F47J13 Family devices do not have persistent configuration memory, the top four words of on-chip program memory are reserved for configuration information. On Reset, the configuration information is copied into the Configuration registers.

The Configuration Words are stored in their program memory location in numerical order, starting with the lower byte of CONFIG1 at the lowest address and ending with the upper byte of CONFIG4.

Table 6-1 provides the actual addresses of the Flash Configuration Word for devices in the PIC18F47J13 Family. Figure 6-2 displays their location in the memory map with other memory vectors.

Additional details on the device Configuration Words are provided in **Section 27.1 "Configuration Bits"**.

# TABLE 6-1: FLASH CONFIGURATION WORD FOR PIC18F47J13 FAMILY DEVICES

| Device      | Program<br>Memory<br>(Kbytes) | Configuration<br>Word Addresses |  |

|-------------|-------------------------------|---------------------------------|--|

| PIC18F26J13 | 64                            | FFF8h to FFFFh                  |  |

| PIC18F46J13 | 04                            |                                 |  |

| PIC18F27J13 | 128                           | 1FFF8h to 1FFFFh                |  |

| PIC18F47J13 | 120                           |                                 |  |

# 6.3 Data Memory Organization

| Note: | The operation of some aspects of data    |

|-------|------------------------------------------|

|       | memory are changed when the PIC18        |

|       | extended instruction set is enabled. See |

|       | Section 6.6 "Data Memory and the         |

|       | Extended Instruction Set" for more       |

|       | information.                             |

The data memory in PIC18 devices is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. The memory space is divided into as many as 16 banks that contain 256 bytes each. The PIC18F47J13 Family implements all available banks and provides 3.8 Kbytes of data memory available to the user. Figure 6-6 provides the data memory organization for the devices.

The data memory contains Special Function Registers (SFRs) and General Purpose Registers (GPRs). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratchpad operations in the user's application. Any read of an unimplemented location will read as '0's.

The instruction set and architecture allow operations across all banks. The entire data memory may be accessed by Direct, Indirect or Indexed Addressing modes. Addressing modes are discussed later in this section.

To ensure that commonly used registers (select SFRs and select GPRs) can be accessed in a single cycle, PIC18 devices implement an Access Bank. This is a 256-byte memory space that provides fast access to select SFRs and the lower portion of GPR Bank 0 without using the BSR. **Section 6.3.2 "Access Bank**" provides a detailed description of the Access RAM.

#### 6.3.1 BANK SELECT REGISTER

Large areas of data memory require an efficient addressing scheme to make rapid access to any address possible. Ideally, this means that an entire address does not need to be provided for each read or write operation. For PIC18 devices, this is accomplished with a RAM banking scheme. This divides the memory space into 16 contiguous banks of 256 bytes. Depending on the instruction, each location can be addressed directly by its full 12-bit address, or an 8-bit low-order address and a 4-bit Bank Pointer.

Most instructions in the PIC18 instruction set make use of the Bank Pointer, known as the Bank Select Register (BSR). This SFR holds the 4 MSbs of a location's address; the instruction itself includes the 8 LSbs. Only the four lower bits of the BSR are implemented (BSR<3:0>). The upper four bits are unused; they will always read '0' and cannot be written to. The BSR can be loaded directly by using the MOVLB instruction.

The value of the BSR indicates the bank in data memory. The 8 bits in the instruction show the location in the bank and can be thought of as an offset from the bank's lower boundary. The relationship between the BSR's value and the bank division in data memory is illustrated in Figure 6-7.

Because up to 16 registers can share the same low-order address, the user must always be careful to ensure that the proper bank is selected before performing a data read or write. For example, writing what should be program data to an 8-bit address of F9h, while the BSR is 0Fh, will end up resetting the PC.

While any bank can be selected, only those banks that are actually implemented can be read or written to. Writes to unimplemented banks are ignored, while reads from unimplemented banks will return '0's. Even so, the STATUS register will still be affected as if the operation was successful. The data memory map in Figure 6-6 indicates which banks are implemented.

In the core PIC18 instruction set, only the MOVFF instruction fully specifies the 12-bit address of the source and target registers. This instruction ignores the BSR completely when it executes. All other instructions include only the low-order address as an operand and must use either the BSR or the Access Bank to locate their target registers.

| Function | TRIS                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I/O                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Setting                                                                                                                                                                      | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Туре                                                                                                                                                 | Description                                                                                                                                                                                                                                                                                                                      |

| RC0      | 1                                                                                                                                                                            | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ST                                                                                                                                                   | PORTC<0> data input.                                                                                                                                                                                                                                                                                                             |

|          | 0                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIG                                                                                                                                                  | LATC<0> data output.                                                                                                                                                                                                                                                                                                             |

| T1OSO    | Х                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ANA                                                                                                                                                  | Timer1 oscillator output; enabled when Timer1 oscillator is enabled. Disables digital I/O.                                                                                                                                                                                                                                       |

| T1CKI    | 1                                                                                                                                                                            | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ST                                                                                                                                                   | Timer1 digital clock input.                                                                                                                                                                                                                                                                                                      |

| RP11     | 1                                                                                                                                                                            | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ST                                                                                                                                                   | Remappable Peripheral Pin 11 input.                                                                                                                                                                                                                                                                                              |

|          | 0                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIG                                                                                                                                                  | Remappable Peripheral Pin 11 output.                                                                                                                                                                                                                                                                                             |

| RC1      | 1                                                                                                                                                                            | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ST                                                                                                                                                   | PORTC<1> data input.                                                                                                                                                                                                                                                                                                             |

|          | 0                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIG                                                                                                                                                  | LATC<1> data output.                                                                                                                                                                                                                                                                                                             |

| CCP8     | 1                                                                                                                                                                            | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ST                                                                                                                                                   | Capture input.                                                                                                                                                                                                                                                                                                                   |

|          | 0                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIG                                                                                                                                                  | Compare/PWM output.                                                                                                                                                                                                                                                                                                              |

| T1OSI    | Х                                                                                                                                                                            | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ANA                                                                                                                                                  | Timer1 oscillator input; enabled when Timer1 oscillator is enabled. Disables digital I/O.                                                                                                                                                                                                                                        |

| RP12     | 1                                                                                                                                                                            | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ST                                                                                                                                                   | Remappable Peripheral Pin 12 input.                                                                                                                                                                                                                                                                                              |

|          | 0                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIG                                                                                                                                                  | Remappable Peripheral Pin 12 output.                                                                                                                                                                                                                                                                                             |

| RC2      | 1                                                                                                                                                                            | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ST                                                                                                                                                   | PORTC<2> data input.                                                                                                                                                                                                                                                                                                             |

|          | 0                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIG                                                                                                                                                  | PORTC<2> data output.                                                                                                                                                                                                                                                                                                            |

| AN11     | 1                                                                                                                                                                            | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ANA                                                                                                                                                  | A/D Input Channel 11.                                                                                                                                                                                                                                                                                                            |

| C2IND    | 1                                                                                                                                                                            | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ANA                                                                                                                                                  | Comparator 2 Input D.                                                                                                                                                                                                                                                                                                            |

| CTPLS    | 0                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIG                                                                                                                                                  | CTMU pulse generator output.                                                                                                                                                                                                                                                                                                     |

| RP13     | 1                                                                                                                                                                            | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ST                                                                                                                                                   | Remappable Peripheral Pin 13 input.                                                                                                                                                                                                                                                                                              |

|          | 0                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIG                                                                                                                                                  | Remappable Peripheral Pin 13 output.                                                                                                                                                                                                                                                                                             |

| RC3      | 1                                                                                                                                                                            | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ST                                                                                                                                                   | PORTC<3> data input.                                                                                                                                                                                                                                                                                                             |

|          | 0                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIG                                                                                                                                                  | PORTC<3> data output.                                                                                                                                                                                                                                                                                                            |

| SCK1     | 1                                                                                                                                                                            | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ST                                                                                                                                                   | SPI clock input (MSSP1 module).                                                                                                                                                                                                                                                                                                  |

|          | 0                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIG                                                                                                                                                  | SPI clock output (MSSP1 module).                                                                                                                                                                                                                                                                                                 |

| SCL1     | 1                                                                                                                                                                            | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | l <sup>2</sup> C/<br>SMBus                                                                                                                           | I <sup>2</sup> C clock input (MSSP1 module).                                                                                                                                                                                                                                                                                     |

|          | 0                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIG                                                                                                                                                  | I <sup>2</sup> C clock output (MSSP1 module).                                                                                                                                                                                                                                                                                    |

| RP14     | 1                                                                                                                                                                            | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ST                                                                                                                                                   | Remappable Peripheral Pin 14 input.                                                                                                                                                                                                                                                                                              |

|          | 0                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIG                                                                                                                                                  | Remappable Peripheral Pin 14 output.                                                                                                                                                                                                                                                                                             |

| RC4      | 0                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIG                                                                                                                                                  | PORTC<4> data output.                                                                                                                                                                                                                                                                                                            |

| SDI1     | 1                                                                                                                                                                            | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ST                                                                                                                                                   | SPI data input (MSSP1 module).                                                                                                                                                                                                                                                                                                   |

| SDA1     | 1                                                                                                                                                                            | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | l <sup>2</sup> C/<br>SMBus                                                                                                                           | I <sup>2</sup> C data input (MSSP1 module).                                                                                                                                                                                                                                                                                      |

|          | 0                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIG                                                                                                                                                  | I <sup>2</sup> C data output (MSSP1 module).                                                                                                                                                                                                                                                                                     |

| RP15     | 1                                                                                                                                                                            | Ι                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ST                                                                                                                                                   | Remappable Peripheral Pin 15 input.                                                                                                                                                                                                                                                                                              |

|          | 0                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DIG                                                                                                                                                  | Remappable Peripheral Pin 15 output.                                                                                                                                                                                                                                                                                             |

|          | T1CKI<br>RP11<br>RC1<br>CCP8<br>T10SI<br>RP12<br>RC2<br>AN11<br>C2IND<br>CTPLS<br>RP13<br>RC3<br>RP13<br>SCK1<br>SCL1<br>SCL1<br>RP14<br>RP14<br>RC4<br>SD11<br>SDA1<br>SDA1 | T1OSO       x         T1CKI       1         RP11       1         RP11       1         RC1       1         RC2       1         RP12       1         RP12       1         RC2       1         RC1       1         RC2       1         RC3       1         RC4       0         SCL1       1         RC4       0         RC4       0         SDA1       1         Q       0         RP15       0         RP14       1         0       0         RC4       0         SDA1       1         0       0         RP15       0 | T10SOxOT1CKI1IRP111IRP111I0OORC11I0OOT1OSIXIRP121IRP121I0OORC21I0OORC11ICTPLSOORP131ICTPLSOORC31I0OOSCL11I0OORC4OOSDA11IOOORP151I0OORP151I0ORP151I0O | T10SOxOANAT1CKI1ISTRP111ISTRP111IST00DIGRC11IST00DIGCCP81IST1000DIGT1OSIXIANARP121IST00DIGRC21IST00DIGRC21IST00DIGRC11ANAC2IND1IANAC1PLS0ODIGRP131IST00DIGSCK111STSMBus00DIGSCL11IST00DIGRP141IST00DIGSDA11IST00DIGSDA11IST00DIGSMBus00DIGSMBus00DIGSMBus00DIGSMBus00DIGSMBus00DIGSMBus00DIGSMBus00DIGSMBus00DIGSMBus00DIGSMBus0 |

TABLE 10-7: PORTC I/O SUMMARY

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; I<sup>2</sup>C/SMB = I<sup>2</sup>C/SMBus input buffer; x = Don't care (TRISx bit does not affect port direction or is overridden for this option)

**Note 1:** This bit is only available on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

# 10.6 PORTE, TRISE and LATE Registers

| Note: | PORTE    | is | available | only | in | 44-pin |

|-------|----------|----|-----------|------|----|--------|

|       | devices. |    |           |      |    |        |

Depending on the particular PIC18F47J13 Family device selected, PORTE is implemented in two different ways.

For 44-pin devices, PORTE is a 3-bit wide port. Three pins (RE0/AN5/PMRD, RE1/AN6/PMWR and RE2/AN7/PMCS) are individually configurable as inputs or outputs. These pins have Schmitt Trigger input buffers. When selected as analog inputs, these pins will read as '0's.

The corresponding Data Direction register is TRISE. Setting a TRISE bit (= 1) will make the corresponding PORTE pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISE bit (= 0) will make the corresponding PORTE pin an output (i.e., put the contents of the output latch on the selected pin).

TRISE controls the direction of the RE pins, even when they are being used as analog inputs. The user must make sure to keep the pins configured as inputs when using them as analog inputs.

**Note:** On a POR, RE<2:0> are configured as analog inputs.

The Data Latch register (LATE) is also memory mapped. Read-modify-write operations on the LATE register read and write the latched output value for PORTE.

#### EXAMPLE 10-6: INITIALIZING PORTE

| CLRF  | PORTE  | ; Initialize PORTE by |  |

|-------|--------|-----------------------|--|

|       |        | ; clearing output     |  |

|       |        | ; data latches        |  |

| CLRF  | LATE   | ; Alternate method    |  |

|       |        | ; to clear output     |  |

|       |        | ; data latches        |  |

| MOVLW | 0xE0   | ; Configure REx       |  |

| MOVWF | ANCON0 | ; for digital inputs  |  |

| MOVLW | 0x03   | ; Value used to       |  |

|       |        | ; initialize data     |  |

|       |        | ; direction           |  |

| MOVWF | TRISE  | ; Set RE<0> as inputs |  |

|       |        | ; RE<1> as outputs    |  |

|       |        | ; RE<2> as inputs     |  |

|       |        |                       |  |

Each of the PORTE pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is performed by clearing bit, REPU (TRISE<6>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a POR. The integrated weak pull-ups consist of a semiconductor structure similar to, but somewhat different, from a discrete resistor. On an unloaded I/O pin, the weak pull-ups are intended to provide logic high indication, but will not necessarily pull the pin all the way to VDD levels.

Note that the pull-ups can be used for any set of features, similar to the pull-ups found on PORTB.

# 10.7 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices similar to the PIC18F47J13 Family. In an application that needs to use more than one peripheral, multiplexed on a single pin, inconvenient work arounds in application code or a complete redesign may be the only option.

The Peripheral Pin Select (PPS) feature provides an alternative to these choices by enabling the user's peripheral set selection and its placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the microcontroller to their entire application, rather than trimming the application to fit the device.

The PPS feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/ or output of any one of the many digital peripherals to any one of these I/O pins. PPS is performed in software, and generally, does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 10.7.1 AVAILABLE PINS

The PPS feature is used with a range of up to 22 pins. The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number. See Table 1-3 and Table 1-4 for pinout options in each package offering.

# 10.7.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and external interrupt inputs. Also included are the outputs of the comparator module, since these are discrete digital signals.

The PPS module is not applied to I<sup>2</sup>C, change notification inputs, RTCC alarm outputs or peripherals with analog inputs. Additionally, the MSSP1 and EUSART1 modules are not routed through the PPS module.

A key difference between pin select and non-pin select peripherals is that pin select peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-pin select peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

#### 10.7.2.1 Peripheral Pin Select Function Priority

When a pin selectable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Pin select peripherals never take priority over any analog functions associated with the pin.

#### 10.7.3 CONTROLLING PERIPHERAL PIN SELECT

PPS features are controlled through two sets of Special Function Registers (SFRs): one to map peripheral inputs and the other to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or an output is being mapped.

# REGISTER 10-33: RPOR9: PERIPHERAL PIN SELECT OUTPUT REGISTER 9 (BANKED EC9h)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | RP9R4 | RP9R3 | RP9R2 | RP9R1 | RP9R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |                    |  |  |

|-------------------|-------------------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                            | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP9R<4:0>:** Peripheral Output Function is Assigned to RP9 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-34: RPOR10: PERIPHERAL PIN SELECT OUTPUT REGISTER 10 (BANKED ECAh)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP10R4 | RP10R3 | RP10R2 | RP10R1 | RP10R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | R/W = Readable bit, | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |  |  |  |

|-------------------|---------------------|-------------------------------------------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit                                       | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared                                        | x = Bit is unknown                 |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP10R<4:0>:** Peripheral Output Function is Assigned to RP10 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-35: RPOR11: PERIPHERAL PIN SELECT OUTPUT REGISTER 11 (BANKED ECBh)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

|       | —   | —   | RP11R4 | RP11R3 | RP11R2 | RP11R1 | RP11R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable bit, Writa | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                    |  |  |  |

|-------------------|----------------------------------------|-------------------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                       | U = Unimplemented bit, rea                                  | d as '0'           |  |  |  |

| -n = Value at POR | '1' = Bit is set                       | '0' = Bit is cleared                                        | x = Bit is unknown |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP11R<4:0>:** Peripheral Output Function is Assigned to RP11 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-42: RPOR18: PERIPHERAL PIN SELECT OUTPUT REGISTER 18 (BANKED ED2h)

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP18R4 | RP18R3 | RP18R2 | RP18R1 | RP18R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | R/W = Readable bit, Writa | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                    |  |  |

|-------------------|---------------------------|-------------------------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read as '0'                          |                    |  |  |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared                                        | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP18R<4:0>:** Peripheral Output Function is Assigned to RP18 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-43: RPOR19: PERIPHERAL PIN SELECT OUTPUT REGISTER 19 (BANKED ED3h)<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP19R4 | RP19R3 | RP19R2 | RP19R1 | RP19R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | R/W = Readable bit, \ | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |  |  |  |

|-------------------|-----------------------|-------------------------------------------------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit                                       | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared                                        | x = Bit is unknown                 |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP19R<4:0>:** Peripheral Output Function is Assigned to RP19 Output Pin bits (see Table 10-14 for peripheral function numbers)

Note 1: RP19 pins are not available on 28-pin devices.

# REGISTER 10-44: RPOR20: PERIPHERAL PIN SELECT OUTPUT REGISTER 20 (BANKED ED4h)<sup>(1)</sup>

| U-0   | U-0 | U-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-----|--------|--------|--------|--------|--------|

| —     | —   | —   | RP20R4 | RP20R3 | RP20R2 | RP20R1 | RP20R0 |

| bit 7 |     |     |        |        |        |        | bit 0  |

| Legend:           | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |                    |  |  |

|-------------------|-------------------------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                                            | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                            | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP20R<4:0>:** Peripheral Output Function is Assigned to RP20 Output Pin bits (see Table 10-14 for peripheral function numbers)

Note 1: RP20 pins are not available on 28-pin devices.

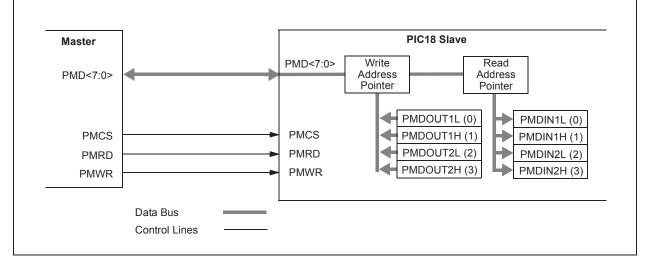

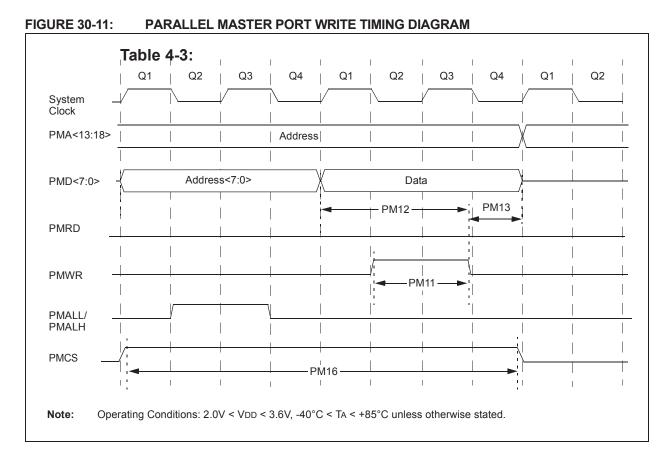

#### 11.2.4 BUFFERED PARALLEL SLAVE PORT MODE

Buffered Parallel Slave Port mode is functionally identical to the Legacy PSP mode with one exception, the implementation of 4-level read and write buffers. Buffered PSP mode is enabled by setting the INCM bits in the PMMODEH register. If the INCM<1:0> bits are set to '11', the PMP module will act as the buffered PSP.

When the Buffered PSP mode is active, the PMDIN1L, PMDIN1H, PMDIN2L and PMDIN2H registers become the write buffers and the PMDOUT1L, PMDOUT1H, PMDOUT2L and PMDOUT2H registers become the read buffers. Buffers are numbered, 0 through 3, starting with the lower byte of PMDIN1L to PMDIN2H as the read buffers and PMDOUT1L to PMDOUT2H as the write buffers.

# 11.2.4.1 READ FROM SLAVE PORT

For read operations, the bytes will be sent out sequentially, starting with Buffer 0 (PMDOUT1L<7:0>) and ending with Buffer 3 (PMDOUT2H<7:0>) for every read strobe. The module maintains an internal pointer to keep track of which buffer is to be read. Each buffer has a corresponding read status bit, OBxE, in the PMSTATL register. This bit is cleared when a buffer contains data that has not been written to the bus and is set when data is written to the bus. If the current buffer location being read from is empty, a buffer underflow is generated and the Buffer Overflow Flag bit, OBUF, is set. If all four OBxE status bits are set, then the Output Buffer Empty flag (OBE) will also be set.

# 11.2.4.2 WRITE TO SLAVE PORT

For write operations, the data has to be stored sequentially, starting with Buffer 0 (PMDIN1L<7:0>) and ending with Buffer 3 (PMDIN2H<7:0>). As with read operations, the module maintains an internal pointer to the buffer that is to be written next.

The input buffers have their own write status bits: IBxF in the PMSTATH register. The bit is set when the buffer contains unread incoming data and cleared when the data has been read. The flag bit is set on the write strobe. If a write occurs on a buffer when its associated IBxF bit is set, the Buffer Overflow flag, IBOV, is set; any incoming data in the buffer will be lost. If all four IBxF flags are set, the Input Buffer Full Flag (IBF) is set.

In Buffered Slave mode, the module can be configured to generate an interrupt on every read or write strobe (IRQM<1:0> = 01). It can be configured to generate an interrupt on a read from Read Buffer 3 or a write to Write Buffer 3, which is essentially an interrupt every fourth read or write strobe (RQM<1:0> = 11). When interrupting every fourth byte for input data, all Input Buffer registers should be read to clear the IBxF flags. If these flags are not cleared, then there is a risk of hitting an overflow condition.

#### FIGURE 11-5: PARALLEL MASTER/SLAVE CONNECTION BUFFERED EXAMPLE

# 15.6 Timer3/5 Interrupt

The TMRx register pair (TMRxH:TMRxL) increments from 0000h to FFFFh and overflows to 0000h. The Timerx interrupt, if enabled, is generated on overflow and is latched in the interrupt flag bit, TMRxIF. Table 15-3 gives each module's flag bit.

TABLE 15-3: TIMER3/5 INTERRUPT FLAG BITS

| Timer Module | Flag Bit |

|--------------|----------|

| 3            | PIR2<1>  |

| 5            | PIR5<1>  |

This interrupt can be enabled or disabled by setting or clearing the TMRxIE bit, respectively. Table 15-4 gives each module's enable bit.

#### TABLE 15-4: TIMER3/5 INTERRUPT ENABLE BITS

| Timer Module | Flag Bit |

|--------------|----------|

| 3            | PIE2<1>  |

| 5            | PIE5<2>  |

# 15.7 Resetting Timer3/5 Using the ECCP Special Event Trigger

If the ECCP modules are configured to use Timerx and to generate a Special Event Trigger in Compare mode (CCPxM<3:0> = 1011), this signal will reset Timerx. The trigger from ECCP2 will also start an A/D conversion if the A/D module is enabled. (For more information, see Section 19.3.4 "Special Event Trigger".)

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPRxH:CCPRxL register pair effectively becomes a Period register for TimerX.

If Timerx is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timerx coincides with a Special Event Trigger from an ECCP module, the write will take precedence.

| Note: | The Special Event Triggers from the        |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|

|       | ECCPx module will only clear the TMR3      |  |  |  |  |  |

|       | register's content, but not set the TMR3IF |  |  |  |  |  |

|       | interrupt flag bit (PIR1<0>).              |  |  |  |  |  |

Note: The CCP and ECCP modules use Timers, 1 through 8, for some modes. The assignment of a particular timer to a CCP/ECCP module is determined by the Timer to CCP enable bits in the CCPTMRSx registers. For more details, see Register 18-3 and Register 19-2.

# 17.1.4 RTCEN BIT WRITE

An attempt to write to the RTCEN bit while RTCWREN = 0 will be ignored. RTCWREN must be set before a write to RTCEN can take place.

Like the RTCEN bit, the RTCVALH and RTCVALL registers can only be written to when RTCWREN = 1. A write to these registers, while RTCWREN = 0, will be ignored.

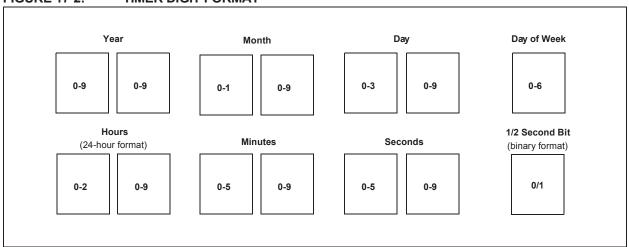

FIGURE 17-2: TIMER DIGIT FORMAT

# 17.2 Operation

#### 17.2.1 REGISTER INTERFACE

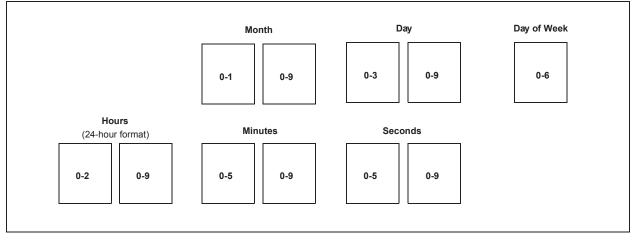

The register interface for the RTCC and alarm values is implemented using the Binary Coded Decimal (BCD) format. This simplifies the firmware when using the module, as each of the digits is contained within its own 4-bit value (see Figure 17-2 and Figure 17-3).

### FIGURE 17-3: ALARM DIGIT FORMAT

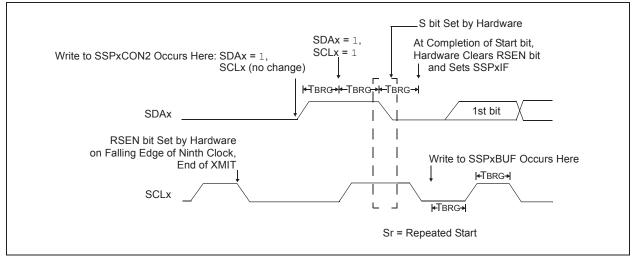

# 20.5.9 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition occurs when the RSEN bit (SSPxCON2<1>) is programmed high and the I<sup>2</sup>C logic module is in the Idle state. When the RSEN bit is set, the SCLx pin is asserted low. When the SCLx pin is sampled low, the BRG is loaded with the contents of SSPxADD<5:0> and begins counting. The SDAx pin is released (brought high) for one BRG count (TBRG). When the BRG times out, and if SDAx is sampled high, the SCLx pin will be deasserted (brought high). When SCLx is sampled high, the BRG is reloaded with the contents of SSPxADD<6:0> and begins counting. SDAx and SCLx must be sampled high for one TBRG. This action is then followed by assertion of the SDAx pin (SDAx = 0) for one TBRG while SCLx is high. Following this, the RSEN bit (SSPxCON2<1>) will be automatically cleared and the BRG will not be reloaded, leaving the SDAx pin held low. As soon as a Start condition is detected on the SDAx and SCLx pins, the Start bit (SSPxSTAT<3>) will be set. The SSPxIF bit will not be set until the BRG has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDAx is sampled low when SCLx goes from low-to-high.

- SCLx goes low before SDAx is asserted low. This may indicate that another master is attempting to transmit a data '1'.

Immediately following the SSPxIF bit getting set, the user may write the SSPxBUF with the 7-bit address in 7-bit mode, or the default first address in 10-bit mode. After the first eight bits are transmitted and an ACK is received, the user may then transmit an additional 8 bits of address (10-bit mode) or 8 bits of data (7-bit mode).

# 20.5.9.1 WCOL Status Flag

If the user writes the SSPxBUF when a Repeated Start sequence is in progress, the WCOL is set and the contents of the buffer are unchanged (the write does not occur).

Note: Because queueing of events is not allowed, writing of the lower five bits of SSPxCON2 is disabled until the Repeated Start condition is complete.

# FIGURE 20-22: REPEATED START CONDITION WAVEFORM

# 21.1 Baud Rate Generator (BRG)

The BRG is a dedicated, 8-bit or 16-bit generator that supports both the Asynchronous and Synchronous modes of the EUSART. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit (BAUDCONx<3>) selects 16-bit mode.

The SPBRGHx:SPBRGx register pair controls the period of a free-running timer. In Asynchronous mode, the BRGH (TXSTAx<2>) and BRG16 (BAUDCONx<3>) bits also control the baud rate. In Synchronous mode, BRGH is ignored.

Table 21-1 provides the formula for computation of the baud rate for different EUSART modes, which only apply in Master mode (internally generated clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRGHx:SPBRGx registers can be calculated using the formulas in Table 21-1. From this, the error in baud rate can be determined. An example calculation is provided in Example 21-1. Typical baud rates and error values for the various Asynchronous modes are provided in Table 21-2. It may be advantageous to use the high baud rate (BRGH = 1) or the 16-bit BRG to reduce the baud rate error, or achieve a slow baud rate for a fast oscillator frequency.

Writing a new value to the SPBRGHx:SPBRGx registers causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

When operated in the Synchronous mode, SPBRGH:SPBRG values of 0000h and 0001h are not supported. In the Asynchronous mode, all BRG values may be used.

#### 21.1.1 OPERATION IN POWER-MANAGED MODES

The device clock is used to generate the desired baud rate. When one of the power-managed modes is entered, the new clock source may be operating at a different frequency. This may require an adjustment to the value in the SPBRGx register pair.

#### 21.1.2 SAMPLING

The data on the RXx pin (either RC7/CCP10/PMA4/ RX1/DT1/RP18 or RPn/RX2/DT2) is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RXx pin.

| <b>TABLE 21-1</b> : | BAUD RATE FORMULAS |

|---------------------|--------------------|