#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 22                                                                          |

| Program Memory Size        | 128KB (64K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                  |

| Data Converters            | A/D 10x10b/12b                                                              |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

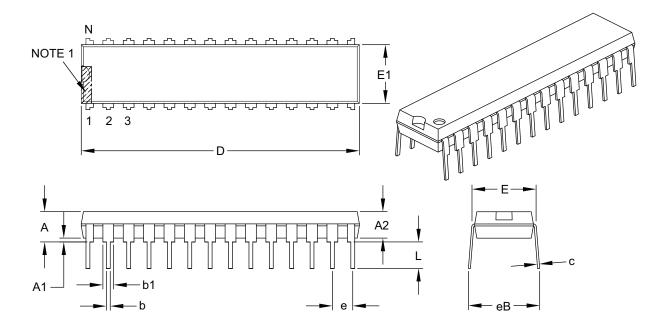

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 28-SPDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf27j13-i-sp |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.1.3 EXPANDED MEMORY

The PIC18F47J13 Family provides ample room for application code, from 64 Kbytes to 128 Kbytes of code space. The Flash cells for program memory are rated to last in excess of 10000 erase/write cycles. Data retention without refresh is conservatively estimated to be greater than 20 years.

The Flash program memory is readable and writable during normal operation. The PIC18F47J13 Family also provides plenty of room for dynamic application data with up to 3.8 Kbytes of data RAM.

#### 1.1.4 EXTENDED INSTRUCTION SET

The PIC18F47J13 Family implements the optional extension to the PIC18 instruction set, adding eight new instructions and an Indexed Addressing mode. Enabled as a device configuration option, the extension has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as C.

#### 1.1.5 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also aids in migrating to the next larger device.

The PIC18F47J13 Family is also pin compatible with other PIC18 families, such as the PIC18F4550, PIC18F2450 and PIC18F46J50. This allows a new dimension to the evolution of applications, allowing developers to select different price points within Microchip's PIC18 portfolio, while maintaining the same feature set.

### 1.2 Other Special Features

- **Communications:** The PIC18F47J13 Family incorporates a range of serial and parallel communication peripherals. This device includes two independent Enhanced USARTs and two Master Synchronous Serial Port (MSSP) modules, capable of both Serial Peripheral Interface (SPI) and I<sup>2</sup>C (Master and Slave) modes of operation. The device also has a parallel port and can be configured to serve as either a Parallel Master Port (PMP) or as a Parallel Slave Port (PSP).

- CCP/ECCP Modules: All devices in the family incorporate seven Capture/Compare/PWM (CCP) modules and three Enhanced Capture/Compare/PWM (ECCP) modules to maximize flexibility in control applications. ECCPs offer up to four PWM output signals each. The ECCPs also offer many beneficial features, including polarity selection, programmable dead time, auto-shutdown and restart and Half-Bridge and Full-Bridge Output modes.

- 10/12-Bit A/D Converter: This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period, and thus, reducing code overhead.

- Extended Watchdog Timer (WDT): This enhanced version incorporates a 16-bit prescaler, allowing an extended time-out range that is stable across operating voltage and temperature. See Section 30.0 "Electrical Characteristics" for time-out periods.

#### 1.3 Details on Individual Family Devices

Devices in the PIC18F47J13 Family are available in 28-pin and 44-pin packages. Block diagrams for the two groups are shown in Figure 1-1 and Figure 1-2. The devices are differentiated from each other in two ways:

- Flash program memory (two sizes: 64 Kbytes for the PIC18FX6J13 and 128 Kbytes for PIC18FX-7J13)

- I/O ports (three bidirectional ports on 28-pin devices, five bidirectional ports on 44-pin devices)

All other features for devices in this family are identical. These are summarized in Table 1-1 and Table 1-2.

The pinouts for the PIC18F2XJ13 devices are listed in Table 1-3. The pinouts for the PIC18F4XJ13 devices are shown in Table 1-4.

The PIC18F47J13 Family of devices provides an on-chip voltage regulator to supply the correct voltage levels to the core. Parts designated with an "F" part number (such as PIC18F47J13) have the voltage regulator enabled.

These parts can run from 2.15V-3.6V on VDD, but should have the VDDCORE pin connected to VSs through a low-ESR capacitor. Parts designated with an "LF" part number (such as PIC18**LF**47J13) do not enable the voltage regulator nor support Deep Sleep mode. For "LF" parts, an external supply of 2.0V-2.7V has to be supplied to the VDDCORE pin while 2.0V-3.6V can be supplied to VDD (VDDCORE should never exceed VDD).

For more details about the internal voltage regulator, see Section 27.3 "On-Chip Voltage Regulator".

| TABLE 1-1: | DEVICE FEATURES FOR THE PIC18F2XJ13 (28-PIN DEVICES) |

|------------|------------------------------------------------------|

|            |                                                      |

| Features                             | PIC18F26J13                                                                       | PIC18F27J13 |  |

|--------------------------------------|-----------------------------------------------------------------------------------|-------------|--|

| Operating Frequency                  | DC – 48 MHz                                                                       | DC – 48 MHz |  |

| Program Memory (Kbytes)              | 64                                                                                | 128         |  |

| Program Memory (Instructions)        | 32,768                                                                            | 65,536      |  |

| Data Memory (Kbytes)                 | 3.8                                                                               | 3.8         |  |

| Interrupt Sources                    | 3                                                                                 | 0           |  |

| I/O Ports                            | Ports A, B, C                                                                     |             |  |

| Timers                               | 8                                                                                 |             |  |

| Enhanced Capture/Compare/PWM Modules | 3 ECCP and 7 CCP                                                                  |             |  |

| Serial Communications                | MSSP (2), Enhanced USART (2)                                                      |             |  |

| Parallel Communications (PMP/PSP)    | No                                                                                |             |  |

| 10/12-Bit Analog-to-Digital Module   | 10 Input Channels                                                                 |             |  |

| Resets (and Delays)                  | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLR, WD<br>(PWRT, OST) |             |  |

| Instruction Set                      | 75 Instructions, 83 with Extended Instruction Set Enabled                         |             |  |

| Packages                             | 28-Pin QFN, SOIC, SSOP and SPDIP (300 mil)                                        |             |  |

#### TABLE 1-2: DEVICE FEATURES FOR THE PIC18F4XJ13 (44-PIN DEVICES)

| Features                             | PIC18F46J13                                                                    | PIC18F47J13 |  |

|--------------------------------------|--------------------------------------------------------------------------------|-------------|--|

| Operating Frequency                  | DC – 48 MHz                                                                    | DC – 48 MHz |  |

| Program Memory (Kbytes)              | 64                                                                             | 128         |  |

| Program Memory (Instructions)        | 32,768                                                                         | 65,536      |  |

| Data Memory (Kbytes)                 | 3.8                                                                            | 3.8         |  |

| Interrupt Sources                    | 3                                                                              | 0           |  |

| I/O Ports                            | Ports A, B, C, D, E                                                            |             |  |

| Timers                               | 8                                                                              |             |  |

| Enhanced Capture/Compare/PWM Modules | 3 ECCP and 7 CCP                                                               |             |  |

| Serial Communications                | MSSP (2), Enhanced USART (2)                                                   |             |  |

| Parallel Communications (PMP/PSP)    | Yes                                                                            |             |  |

| 10/12-Bit Analog-to-Digital Module   | 13 Input Channels                                                              |             |  |

| Resets (and Delays)                  | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLR, WD (PWRT, OST) |             |  |

| Instruction Set                      | 75 Instructions, 83 with Extended Instruction Set Enabled                      |             |  |

| Packages                             | 44-Pin QFN and TQFP                                                            |             |  |

|                                        | Pin Number |             | - Pin Buffer |                   |                                                                                                 |  |  |

|----------------------------------------|------------|-------------|--------------|-------------------|-------------------------------------------------------------------------------------------------|--|--|

| Pin Name                               | 44-<br>QFN | 44-<br>TQFP | Type Type    |                   | Description                                                                                     |  |  |

|                                        |            |             |              |                   | PORTA is a bidirectional I/O port.                                                              |  |  |

| RA0/AN0/C1INA/ULPWU/PMA6/<br>RP0       | 19         | 19          |              |                   |                                                                                                 |  |  |

| RA0                                    |            |             | I/O          | TTL/DIG           | Digital I/O.                                                                                    |  |  |

| AN0                                    |            |             | I            | Analog            | Analog Input 0.                                                                                 |  |  |

| C1INA                                  |            |             | I            | Analog            | Comparator 1 Input A.                                                                           |  |  |

| ULPWU                                  |            |             | I            | Analog            | Ultra low-power wake-up input.                                                                  |  |  |

| PMA6                                   |            |             | I/O          | ST/TTL/           | Parallel Master Port digital I/O.                                                               |  |  |

| RP0                                    |            |             | I/O          | DIG<br>ST/DIG     | Remappable Peripheral Pin 0 input/output.                                                       |  |  |

|                                        |            |             | 1/0          | 51/010            |                                                                                                 |  |  |

| RA1/AN1/C2INA/VBG/CTDIN/               | 20         | 20          |              |                   |                                                                                                 |  |  |

| PMA7/RP1                               |            |             | 1/0          |                   | Digital I/O                                                                                     |  |  |

| RA1<br>AN1                             |            |             | 1/O<br>0     | TTL/DIG<br>Analog | Digital I/O.<br>Analog Input 1.                                                                 |  |  |

| C2INA                                  |            |             |              | Analog            | Comparator 2 Input A.                                                                           |  |  |

| VBG                                    |            |             | 0            | Analog            | Band Gap Reference Voltage (VBG) output.                                                        |  |  |

| CTDIN                                  |            |             | I            | ST                | CTMU pulse delay input.                                                                         |  |  |

| PMA7                                   |            |             | I/O          | ST/TTL/           | Parallel Master Port digital I/O.                                                               |  |  |

|                                        |            |             | _            | DIG               |                                                                                                 |  |  |

| RP1                                    |            |             | I/O          | ST/DIG            | Remappable Peripheral Pin 1 input/output.                                                       |  |  |

| RA2/AN2/C2INB/C1IND/C3INB/             | 21         | 21          |              |                   |                                                                                                 |  |  |

| /REF-/CVREF                            |            |             |              |                   |                                                                                                 |  |  |

| RA2                                    |            |             | I/O          | TTL/DIG           | Digital I/O.                                                                                    |  |  |

| AN2                                    |            |             | I            | Analog            | Analog Input 2.                                                                                 |  |  |

| C2INB                                  |            |             | I            | Analog            | Comparator 2 Input B.                                                                           |  |  |

| C1IND                                  |            |             | I            | Analog            | Comparator 1 Input D.                                                                           |  |  |

| C3INB                                  |            |             | I            | Analog            | Comparator 3 Input B.                                                                           |  |  |

| VREF-                                  |            |             |              | Analog            | A/D reference voltage (low) input.                                                              |  |  |

| CVREF                                  |            |             |              | Analog            | Comparator reference voltage output.                                                            |  |  |

| RA3/AN3/C1INB/VREF+                    | 22         | 22          |              |                   |                                                                                                 |  |  |

| RA3                                    |            |             | I/O          | TTL/DIG           | 0                                                                                               |  |  |

| AN3                                    |            |             |              | Analog            | Analog Input 3.                                                                                 |  |  |

| C1INB                                  |            |             |              | Analog            | Comparator 1 Input B.                                                                           |  |  |

| VREF+                                  |            |             |              | Analog            | A/D reference voltage (high) input.                                                             |  |  |

| RA5/AN4/C1INC/SS1/HLVDIN/RP2           | 24         | 24          |              |                   |                                                                                                 |  |  |

| RA5                                    |            |             | I/O          | TTL/DIG           | 0                                                                                               |  |  |

| AN4                                    |            |             |              | Analog            | Analog Input 4.                                                                                 |  |  |

| C1INC<br>SS1                           |            |             |              | Analog            | SPI slave select input.                                                                         |  |  |

| HLVDIN                                 |            |             |              | TTL<br>Analog     | Comparator 1 Input C.<br>High/Low-Voltage Detect input.                                         |  |  |

| RP2                                    |            |             | 1/O          | ST/DIG            |                                                                                                 |  |  |

| RA6 <sup>(1)</sup>                     |            |             |              |                   |                                                                                                 |  |  |

| RA7 <sup>(1)</sup>                     |            |             |              |                   | See the OSC2/CLKO/RA6 pin.<br>See the OSC1/CLKI/RA7 pin.                                        |  |  |

| <b>_egend:</b> TTL = TTL compatible in |            |             |              |                   | CMOS = CMOS compatible input or output                                                          |  |  |

| ST = Schmitt Trigger in                | iput wit   | n CMO       | is level     |                   | Analog = Analog input                                                                           |  |  |

| I = Input<br>P = Power                 |            |             |              |                   | O = Output<br>OD = Open-Drain (no P diode to VDD)                                               |  |  |

| P = Power<br>DIG = Digital output      |            |             |              |                   | OD = Open-Drain (no P diode to VDD)<br>I <sup>2</sup> C = Open-Drain, I <sup>2</sup> C specific |  |  |

|                                        | abled if   | 10004       | and O        |                   | used for the clock function.                                                                    |  |  |

|                                        |            |             |              |                   | 3F47J13, PIC18LF46J13 and PIC18LF47J13).                                                        |  |  |

|                                        |            | ່າເມ        |              | 10,11010          | $j_1 + j_0 + j_0$ , $j_1 + j_0 + j_0 + j_0$ and $f_1 + f_0 + f_0 + f_0$ .                       |  |  |

#### TABLE 1-4: PIC18F4XJ13 PINOUT I/O DESCRIPTIONS (CONTINUED)

2: Available only on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

3: 5.5V tolerant.

#### 3.3 Clock Sources and Oscillator Switching

Like previous PIC18 enhanced devices, the PIC18F47J13 Family includes a feature that allows the device clock source to be switched from the main oscillator to an alternate, low-frequency clock source. PIC18F47J13 Family devices offer two alternate clock sources. When an alternate clock source is enabled, the various power-managed operating modes are available.

Essentially, there are three clock sources for these devices:

- Primary Oscillators

- Secondary Oscillators

- Internal Oscillator Block

The **Primary Oscillators** include the External Crystal and Resonator modes, the External Clock modes and the internal oscillator block. The particular mode is defined by the FOSC<2:0> Configuration bits. The details of these modes are covered earlier in this chapter.

The **Secondary Oscillators** are external sources that are not connected to the OSC1 or OSC2 pins. These sources may continue to operate even after the controller is placed in a power-managed mode.

PIC18F47J13 Family devices offer the Timer1 oscillator as a secondary oscillator. This oscillator, in all power-managed modes, is often the time base for functions such as a Real-Time Clock (RTC). Most often, a 32.768 kHz watch crystal is connected between the RC0/T1OSO/T1CKI/RP11 and RC1/CCP8/T1OSI/RP12 pins. Like the HS Oscillator mode circuits, loading capacitors are also connected from each pin to ground. The Timer1 oscillator is discussed in larger detail in Section 13.5 "Timer1 Oscillator".

In addition to being a primary clock source, the **postscaled internal clock** is available as a power-managed mode clock source. The INTRC source is also used as the clock source for several special features, such as the WDT and Fail-Safe Clock Monitor (FSCM).

#### 3.3.1 OSCILLATOR CONTROL REGISTER

The OSCCON register (Register 3-2) controls several aspects of the device clock's operation, both in full-power operation and in power-managed modes.

The System Clock Select bits, SCS<1:0>, select the clock source. The available clock sources are the primary clock (defined by the FOSC<2:0> Configuration bits), the secondary clock (Timer1 oscillator) and the postscaled internal clock. The clock source changes immediately, after one or more of the bits is written to, following a brief clock transition interval. The SCS bits are cleared on all forms of Reset.

The Internal Oscillator Frequency Select bits, IRCF<2:0>, select the frequency output provided on the postscaled internal clock line. The choices are the INTRC source, the INTOSC source (8 MHz) or one of the frequencies derived from the INTOSC postscaler (31 kHz to 4 MHz). If the postscaled internal clock is supplying the device clock, changing the states of these bits will have an immediate change on the internal oscillator's output. On device Resets, the default output frequency of the INTOSC postscaler is set at 4 MHz.

When an output frequency of 31 kHz is selected (IRCF<2:0> = 000), users may choose the internal oscillator, which acts as the source. This is done with the INTSRC bit in the OSCTUNE register (OSCTUNE<7>). Setting this bit selects INTOSC as a 31.25 kHz clock source by enabling the divide-by-256 output of the INTOSC postscaler. Clearing INTSRC selects INTRC (nominally 31 kHz) as the clock source.

This option allows users to select the tunable and more precise INTOSC as a clock source, while maintaining power savings with a very low clock speed. Regardless of the setting of INTSRC, INTRC always remains the clock source for features such as the WDT and the FSCM.

The OSTS and SOSCRUN bits indicate which clock source is currently providing the device clock. The OSTS bit indicates that the Oscillator Start-up Timer (OST) has timed out and the primary clock is providing the device clock in primary clock modes. The SOSCRUN bit (OSC-CON2<6>) indicates when the Timer1 oscillator is providing the device clock in secondary clock modes. In power-managed modes, only one of these bits will be set at any time. If none of these bits are set, the INTRC is providing the clock or the internal oscillator block has just started and is not yet stable.

The IDLEN bit determines if the device goes into Sleep mode, or one of the Idle modes, when the SLEEP instruction is executed.

## REGISTER 7-1: EECON1: EEPROM CONTROL REGISTER 1 (ACCESS FA6h)

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-x | R/W-0 | R/S-0 | U-0   |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | WPROG | FREE  | WRERR | WREN  | WR    | —     |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           | S = Settable bit (cannot b | S = Settable bit (cannot be cleared in software) |                                    |  |  |  |  |

|-------------------|----------------------------|--------------------------------------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bi                             | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared                             | x = Bit is unknown                 |  |  |  |  |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                    |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5   | WPROG: One Word-Wide Program bit                                                                                                                                                                                                                                              |

|         | <ul> <li>1 = Program 2 bytes on the next WR command</li> <li>0 = Program 64 bytes on the next WR command</li> </ul>                                                                                                                                                           |

| bit 4   | FREE: Flash Erase Enable bit                                                                                                                                                                                                                                                  |

|         | <ul><li>1 = Perform an erase operation on the next WR command (cleared by hardware after completion of erase)</li><li>0 = Perform write-only</li></ul>                                                                                                                        |

| bit 3   | WRERR: Flash Program Error Flag bit                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = A write operation is prematurely terminated (any Reset during self-timed programming in normal operation or an improper write attempt)</li> <li>0 = The write operation completed</li> </ul>                                                                     |

| bit 2   | WREN: Flash Program Write Enable bit                                                                                                                                                                                                                                          |

|         | <ul><li>1 = Allows write cycles to Flash program memory</li><li>0 = Inhibits write cycles to Flash program memory</li></ul>                                                                                                                                                   |

| bit 1   | WR: Write-Control bit                                                                                                                                                                                                                                                         |

|         | <ul> <li>1 = Initiates a program memory erase cycle or write cycle<br/>(The operation is self-timed and the bit is cleared by hardware once the write is complete. The WR<br/>bit can only be set (not cleared) in software.)</li> <li>0 = Write cycle is complete</li> </ul> |

| bit 0   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                    |

| EXAMPLE 7-3:      | WRITING TO FLASH PROGRAM MEMORY                    |                           |                                                                       |  |  |  |  |  |  |  |

|-------------------|----------------------------------------------------|---------------------------|-----------------------------------------------------------------------|--|--|--|--|--|--|--|

| ERASE BLOCK       | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | TBLPTRU                   | ; Load TBLPTR with the base address<br>; of the memory block, minus 1 |  |  |  |  |  |  |  |

| LINASE_BLOCK      | BSF                                                | EECON1. WREN              | ; enable write to memory                                              |  |  |  |  |  |  |  |

|                   | BSF                                                |                           | ; enable Erase operation                                              |  |  |  |  |  |  |  |

|                   | BCF                                                | INTCON, GIE               | ; disable interrupts                                                  |  |  |  |  |  |  |  |

|                   | MOVLW                                              |                           | , disable interrupts                                                  |  |  |  |  |  |  |  |

|                   | MOVWF                                              |                           | ; write 55h                                                           |  |  |  |  |  |  |  |

|                   | MOVLW                                              |                           | , write John                                                          |  |  |  |  |  |  |  |

|                   | MOVWF                                              |                           | ; write OAAh                                                          |  |  |  |  |  |  |  |

|                   |                                                    | EECON1, WR                | ; start erase (CPU stall)                                             |  |  |  |  |  |  |  |

|                   | BSF                                                |                           | ; re-enable interrupts                                                |  |  |  |  |  |  |  |

|                   | MOVLW                                              |                           | , 10 0.0010 1.00110,000                                               |  |  |  |  |  |  |  |

|                   | MOVWF                                              |                           | ; Need to write 16 blocks of 64 to write                              |  |  |  |  |  |  |  |

|                   |                                                    | _                         | ; one erase block of 1024                                             |  |  |  |  |  |  |  |

| RESTART BUFFER    |                                                    |                           |                                                                       |  |  |  |  |  |  |  |

| _                 | MOVLW                                              | D'64'                     |                                                                       |  |  |  |  |  |  |  |

|                   | MOVWF                                              | COUNTER                   |                                                                       |  |  |  |  |  |  |  |

|                   | MOVLW                                              | BUFFER ADDR HIGH          | ; point to buffer                                                     |  |  |  |  |  |  |  |

|                   | MOVWF                                              | FSROH — —                 |                                                                       |  |  |  |  |  |  |  |

|                   | MOVLW                                              | BUFFER ADDR LOW           |                                                                       |  |  |  |  |  |  |  |

|                   | MOVWF                                              |                           |                                                                       |  |  |  |  |  |  |  |

| FILL BUFFER       |                                                    |                           |                                                                       |  |  |  |  |  |  |  |

|                   |                                                    |                           | ; read the new data from I2C, SPI,                                    |  |  |  |  |  |  |  |

|                   |                                                    |                           | ; PSP, USART, etc.                                                    |  |  |  |  |  |  |  |

| WRITE_BUFFER      |                                                    |                           |                                                                       |  |  |  |  |  |  |  |

|                   | MOVLW                                              | D'64'                     | ; number of bytes in holding register                                 |  |  |  |  |  |  |  |

|                   | MOVWF                                              | COUNTER                   |                                                                       |  |  |  |  |  |  |  |

| WRITE_BYTE_TO_HRE |                                                    |                           |                                                                       |  |  |  |  |  |  |  |

|                   | MOVFF                                              | POSTINCO, WREG            | ; get low byte of buffer data                                         |  |  |  |  |  |  |  |

|                   | MOVWF                                              | TABLAT                    | ; present data to table latch                                         |  |  |  |  |  |  |  |

|                   | TBLWT+'                                            | r -                       | ; write data, perform a short write                                   |  |  |  |  |  |  |  |

|                   |                                                    |                           | ; to internal TBLWT holding register.                                 |  |  |  |  |  |  |  |

|                   |                                                    | COUNTER                   | ; loop until buffers are full                                         |  |  |  |  |  |  |  |

|                   | BRA                                                | WRITE_BYTE_TO_HREGS       |                                                                       |  |  |  |  |  |  |  |

| PROGRAM_MEMORY    | DOP                                                | DECOM1 MEEN               |                                                                       |  |  |  |  |  |  |  |

|                   | BSF                                                |                           | ; enable write to memory                                              |  |  |  |  |  |  |  |

|                   | BCF                                                | INTCON, GIE               | ; disable interrupts                                                  |  |  |  |  |  |  |  |

| Poquined          | MOVLW                                              | 0x55                      | . write 55b                                                           |  |  |  |  |  |  |  |

| Required          | MOVWF                                              | EECON2                    | ; write 55h                                                           |  |  |  |  |  |  |  |

| Sequence          | MOVLW                                              | 0xAA<br>EECON2            | · ····································                                |  |  |  |  |  |  |  |

|                   | MOVWF<br>BSF                                       | EECON2<br>FECON1 WP       | ; write OAAh<br>; start program (CPU stall)                           |  |  |  |  |  |  |  |

|                   | BSF                                                | EECON1, WR<br>INTCON, GIE | ; start program (CPO starr)<br>; re-enable interrupts                 |  |  |  |  |  |  |  |

|                   | BCF                                                | EECON1, WREN              | ; re-enable interrupts<br>; disable write to memory                   |  |  |  |  |  |  |  |

|                   | DUĽ                                                | DDCONI, WKEN              | , areable write to memory                                             |  |  |  |  |  |  |  |

|                   | DECESZ                                             | WRITE COUNTER             | ; done with one write cycle                                           |  |  |  |  |  |  |  |

|                   | BRA                                                | RESTART BUFFER            | ; if not done replacing the erase block                               |  |  |  |  |  |  |  |

|                   | 2141                                               |                           | , II had adno repracing the trade prock                               |  |  |  |  |  |  |  |

#### REGISTER 9-3: INTCON3: INTERRUPT CONTROL REGISTER 3 (ACCESS FF0h)

| R/W-1                | R/W-1                                 | R/W-0                                  | R/W-0            | R/W-0            | R/W-0           | R/W-0            | R/W-0        |

|----------------------|---------------------------------------|----------------------------------------|------------------|------------------|-----------------|------------------|--------------|

| INT2IP               | INT1IP                                | INT3IE                                 | INT2IE           | INT1IE           | INT3IF          | INT2IF           | INT1IF       |

| bit 7                |                                       |                                        |                  |                  |                 |                  | bit (        |

| Locondu              |                                       |                                        |                  |                  |                 |                  |              |

| Legend:<br>R = Reada | ahla hit                              | W = Writable                           | hit              | II = I Inimplen  | nented bit, rea | nd as 'O'        |              |

| -n = Value           |                                       | '1' = Bit is set                       |                  | '0' = Bit is cle |                 | x = Bit is unkr  | nown         |

|                      |                                       | 1 Bit io oot                           |                  |                  |                 |                  |              |

| bit 7                | INT2IP: INT2                          | External Interr                        | upt Priority bit |                  |                 |                  |              |

|                      | 1 = High pric                         |                                        |                  |                  |                 |                  |              |

|                      | 0 = Low prio                          | rity                                   |                  |                  |                 |                  |              |

| bit 6                |                                       | External Interr                        | upt Priority bit |                  |                 |                  |              |

|                      | 1 = High pric<br>0 = Low prio         |                                        |                  |                  |                 |                  |              |

| bit 5                | •                                     | External Interr                        | unt Enable hit   |                  |                 |                  |              |

|                      |                                       | the INT3 exteri                        | •                |                  |                 |                  |              |

|                      |                                       | the INT3 exter                         |                  |                  |                 |                  |              |

| bit 4                | INT2IE: INT2                          | External Interr                        | upt Enable bit   |                  |                 |                  |              |

|                      |                                       | the INT2 extern                        | •                |                  |                 |                  |              |

| 1.1.0                |                                       | the INT2 exter                         |                  |                  |                 |                  |              |

| bit 3                |                                       | External Interr                        | -                |                  |                 |                  |              |

|                      |                                       | the INT1 extern<br>the INT1 extern     |                  |                  |                 |                  |              |

| bit 2                |                                       | External Interr                        |                  |                  |                 |                  |              |

|                      |                                       |                                        |                  | must be cleared  | d in software)  |                  |              |

|                      |                                       | 3 external inter                       |                  | cur              |                 |                  |              |

| bit 1                |                                       | External Interr                        |                  |                  |                 |                  |              |

|                      |                                       | 2 external interi<br>2 external interi |                  | must be cleared  | d in software)  |                  |              |

| bit 0                |                                       | External Interr                        | •                | Sui              |                 |                  |              |

|                      |                                       |                                        |                  | must be cleared  | d in software)  |                  |              |

|                      |                                       | 1 external interi                      |                  |                  |                 |                  |              |

| Note                 | Interrupt floor bits                  | oro oot when                           | on interrunt     | ndition accura   | rogardiaca of   | the state of its | oorroopandin |

| Note:                | Interrupt flag bits enable bit or the |                                        |                  |                  |                 |                  |              |

|                      | are clear prior to                    | •                                      |                  |                  |                 |                  | . 3          |

# PIC18F47J13 FAMILY

| Pin                            | Function            | TRIS<br>Setting                                    | I/O                                                  | I/O<br>Type | Description                                                                                                       |  |  |

|--------------------------------|---------------------|----------------------------------------------------|------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| RA0/AN0/C1INA/                 | RA0                 | 1                                                  | I                                                    | TTL         | PORTA<0> data input; disabled when analog input is enabled.                                                       |  |  |

| ULPWU/PMA6/                    |                     | 0                                                  | 0                                                    | DIG         | LATA<0> data output; not affected by analog input.                                                                |  |  |

| RP0                            | AN0                 | 1                                                  | I                                                    | ANA         | A/D Input Channel 0 and Comparator C1- input. Default input configuration on POR; does not affect digital output. |  |  |

|                                | C1INA               | 1                                                  | Ι                                                    | ANA         | Comparator 1 Input A.                                                                                             |  |  |

|                                | ULPWU               | 1                                                  | Ι                                                    | ANA         | Ultra low-power wake-up input.                                                                                    |  |  |

|                                | PMA6 <sup>(1)</sup> | х                                                  | I/O ST/TTL/ Parallel Master Port digital I/O.<br>DIG |             |                                                                                                                   |  |  |

|                                | RP0                 | 1                                                  | Ι                                                    | ST          | Remappable Peripheral Pin 0 input.                                                                                |  |  |

|                                |                     | 0                                                  | 0                                                    | DIG         | Remappable Peripheral Pin 0 output.                                                                               |  |  |

| RA1/AN1/C2INA/                 | RA1                 | 1                                                  | Ι                                                    | TTL         | PORTA<1> data input; disabled when analog input is enabled.                                                       |  |  |

| VBG/CTDIN/                     |                     | LATA<1> data output; not affected by analog input. |                                                      |             |                                                                                                                   |  |  |

| PMA7/RP1                       | AN1                 | 1                                                  | Ι                                                    | ANA         | A/D Input Channel 1 and Comparator C2- input. Default input configuration on POR; does not affect digital output. |  |  |

|                                | C2INA               | 1                                                  | Ι                                                    | ANA         | Comparator 1 Input A.                                                                                             |  |  |

|                                | Vbg                 | х                                                  | 0                                                    | ANA         | Band Gap Voltage Reference output. (Enabled by settin<br>the VBGOE bit (WDTCON<4>.)                               |  |  |

|                                | CTDIN               | 1                                                  | Ι                                                    | ST          | CTMU pulse delay input.                                                                                           |  |  |

|                                | PMA7 <sup>(1)</sup> | 1                                                  | Ι                                                    | ST/TTL      | Parallel Master Port (io_addr_in[7]).                                                                             |  |  |

|                                |                     | 0                                                  | 0                                                    | DIG         | Parallel Master Port address.                                                                                     |  |  |

|                                | RP1                 | 1                                                  | Ι                                                    | ST          | Remappable Peripheral Pin 1 input.                                                                                |  |  |

|                                |                     | 0                                                  | 0                                                    | DIG         | Remappable Peripheral Pin 1 output                                                                                |  |  |

| RA2/AN2/C2INB/<br>C1IND/C3INB/ | RA2                 | 0                                                  | 0                                                    | DIG         | LATA<2> data output; not affected by analog input. Disabled when CVREF output is enabled.                         |  |  |

| VREF-/CVREF                    |                     | 1                                                  | I                                                    | TTL         | PORTA<2> data input. Disabled when analog functions are enabled; disabled when CVREF output is enabled.           |  |  |

|                                | AN2                 | 1                                                  | Ι                                                    | ANA         | A/D Input Channel 2 and Comparator C2+ input. Default input configuration on POR; not affected by analog output.  |  |  |

|                                | C2INB               | 1                                                  | Ι                                                    | ANA         | Comparator 2 Input B.                                                                                             |  |  |

|                                |                     | 0                                                  | 0                                                    | ANA         | CTMU pulse generator charger for the C2INB comparator input.                                                      |  |  |

|                                | C1IND               | 1                                                  | Ι                                                    | ANA         | Comparator 1 Input D.                                                                                             |  |  |

|                                | C3INB               | 1                                                  | Ι                                                    | ANA         | Comparator 3 Input B.                                                                                             |  |  |

|                                | VREF-               | 1                                                  | Ι                                                    | ANA         | A/D and comparator voltage reference low input.                                                                   |  |  |

|                                | CVREF               | х                                                  | 0                                                    | ANA         | Comparator voltage reference output. Enabling this feature disables digital I/O.                                  |  |  |

| RA3/AN3/C1INB/                 | RA3                 | 0                                                  | 0                                                    | DIG         | LATA<3> data output; not affected by analog input.                                                                |  |  |

| VREF+                          |                     | 1                                                  | Ι                                                    | TTL         | PORTA<3> data input; disabled when analog input is enabled.                                                       |  |  |

|                                | AN3                 | 1                                                  | I                                                    | ANA         | A/D Input Channel 3 and Comparator C1+ input. Default input configuration on POR.                                 |  |  |

|                                | C1INB               | 1                                                  | Ι                                                    | ANA         | Comparator 1 Input B                                                                                              |  |  |

|                                | VREF+               | 1                                                  | Ι                                                    | ANA         | A/D and comparator voltage reference high input.                                                                  |  |  |

TABLE 10-3: PORTA I/O SUMMARY

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRISx bit does not affect port direction or is overridden for this option)

**Note 1:** This bit is only available on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

## 12.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software selectable operation as a timer or counter in both 8-bit or 16-bit modes

- · Readable and writable registers

- Dedicated 8-bit, software programmable

prescaler

- Selectable clock source (internal or external)

- · Edge select for external clock

- Interrupt-on-overflow

The T0CON register (Register 12-1) controls all aspects of the module's operation, including the prescale selection. It is both readable and writable.

Figure 12-1 provides a simplified block diagram of the Timer0 module in 8-bit mode. Figure 12-2 provides a simplified block diagram of the Timer0 module in 16-bit mode.

#### REGISTER 12-1: T0CON: TIMER0 CONTROL REGISTER (ACCESS FD5h)

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR00N | T08BIT | TOCS  | T0SE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

| Legend:    |                                                                                       |                                                            |                       |                    |  |  |  |  |

|------------|---------------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------|--------------------|--|--|--|--|

| R = Reada  | ble bit                                                                               | W = Writable bit                                           | U = Unimplemented bit | , read as '0'      |  |  |  |  |

| -n = Value | at POR                                                                                | '1' = Bit is set                                           | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |  |

|            |                                                                                       |                                                            |                       |                    |  |  |  |  |

| bit 7      |                                                                                       | : Timer0 On/Off Control bit                                |                       |                    |  |  |  |  |

|            |                                                                                       | les Timer0                                                 |                       |                    |  |  |  |  |

|            | 0 = Stops                                                                             | 5 Timer0                                                   |                       |                    |  |  |  |  |

| bit 6      | T08BIT: 1                                                                             | Timer0 8-Bit/16-Bit Control bit                            | t                     |                    |  |  |  |  |

|            |                                                                                       | 0 is configured as an 8-bit tir                            |                       |                    |  |  |  |  |

|            | 0 = Timei                                                                             | 0 is configured as a 16-bit tir                            | mer/counter           |                    |  |  |  |  |

| bit 5      | TOCS: Tir                                                                             | mer0 Clock Source Select bit                               |                       |                    |  |  |  |  |

|            | 1 = Trans                                                                             | 1 = Transition on T0CKI pin input edge                     |                       |                    |  |  |  |  |

|            | 0 = Intern                                                                            | al clock (Fosc/4)                                          |                       |                    |  |  |  |  |

| bit 4      | T0SE: Timer0 Source Edge Select bit                                                   |                                                            |                       |                    |  |  |  |  |

|            | 1 = Increment on high-to-low transition on T0CKI pin                                  |                                                            |                       |                    |  |  |  |  |

|            | 0 = Increi                                                                            | ment on low-to-high transitior                             | n on T0CKI pin        |                    |  |  |  |  |

| bit 3      | PSA: Timer0 Prescaler Assignment bit                                                  |                                                            |                       |                    |  |  |  |  |

|            | 1 = Timer0 prescaler is not assigned. Timer0 clock input bypasses prescaler.          |                                                            |                       |                    |  |  |  |  |

|            | 0 = Timer0 prescaler is assigned. Timer0 clock input comes from the prescaler output. |                                                            |                       |                    |  |  |  |  |

| bit 2-0    | T0PS<2:                                                                               | 0>: Timer0 Prescaler Select I                              | oits                  |                    |  |  |  |  |

|            | 111 = 1:256 Prescale value                                                            |                                                            |                       |                    |  |  |  |  |

|            | 110 = 1:128 Prescale value                                                            |                                                            |                       |                    |  |  |  |  |

|            |                                                                                       | A Prescale value                                           |                       |                    |  |  |  |  |

|            |                                                                                       | 32 Prescale value                                          |                       |                    |  |  |  |  |

|            |                                                                                       | 6 Prescale value                                           |                       |                    |  |  |  |  |

|            |                                                                                       | <ul> <li>Prescale value</li> <li>Prescale value</li> </ul> |                       |                    |  |  |  |  |

|            | 001 = 1.4<br>000 = 1.2                                                                |                                                            |                       |                    |  |  |  |  |

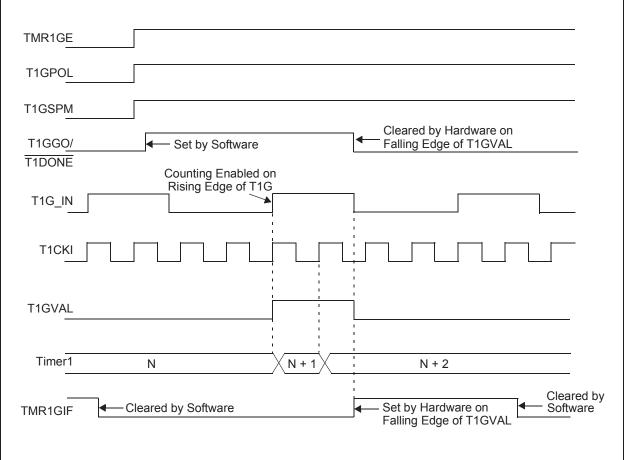

#### 13.8.4 TIMER1 GATE SINGLE PULSE MODE

When Timer1 Gate Single Pulse mode is enabled, it is possible to capture a single pulse gate event. Timer1 Gate Single Pulse mode is first enabled by setting the T1GSPM bit in the T1GCON register. Next, the T1GGO/T1DONE bit in the T1GCON register must be set. The Timer1 will be fully enabled on the next incrementing edge. On the next trailing edge of the pulse, the T1GGO/T1DONE bit will automatically be cleared. No other gate events will be allowed to increment Timer1 until the T1GGO/T1DONE bit is once again set in software.

Clearing the T1GSPM <u>bit of the T1GCON</u> register will also clear the T1GGO/T1DONE bit. See Figure 13-6 for timing details.

Enabling the Toggle mode and the Single Pulse mode, simultaneously, will permit both sections to work together. This allows the cycle times on the Timer1 gate source to be measured. See Figure 13-7 for timing details.

#### 13.8.5 TIMER1 GATE VALUE STATUS

When the Timer1 gate value status is utilized, it is possible to read the most current level of the gate control value. The value is stored in the T1GVAL bit in the T1GCON register. The T1GVAL bit is valid even when the Timer1 gate is not enabled (TMR1GE bit is cleared).

#### FIGURE 13-6: TIMER1 GATE SINGLE PULSE MODE

NOTES:

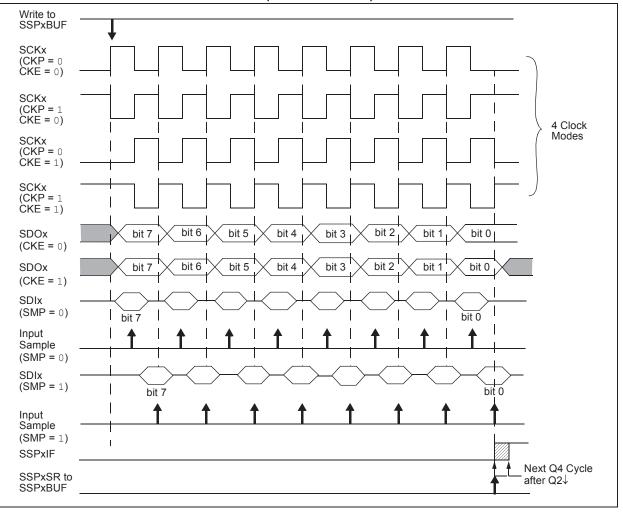

#### 20.3.6 MASTER MODE

The master can initiate the data transfer at any time because it controls the SCKx. The master determines when the slave (Processor 2, Figure 20-2) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSPxBUF register is written to. If the SPI is only going to receive, the SDOx output could be disabled (programmed as an input). The SSPxSR register will continue to shift in the signal present on the SDIx pin at the programmed clock rate. As each byte is received, it will be loaded into the SSPxBUF register as if it is a normal received byte (interrupts and status bits are appropriately set). This could be useful in receiver applications as a "Line Activity Monitor" mode.

To avoid lost data in Master mode, a read of Note: the SSPxBUF must be performed to clear the Buffer Full (BF) detect bit (SSPxSTAT<0>) between each transmission.

The CKP is selected by appropriately programming the CKP bit (SSPxCON1<4>). This then, would give waveforms for SPI communication, as illustrated in

Figure 20-3, Figure 20-5 and Figure 20-6, where the Most Significant Byte (MSB) is transmitted first. In Master mode, the SPI clock rate (bit rate) is user-programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/8 (or 2 Tcy)

- Fosc/16 (or 4 Tcy)

- Fosc/64 (or 16 Tcy)

- Timer2 output/2

When using the Timer2 output/2 option, the Period Register 2 (PR2) can be used to determine the SPI bit rate. However, only PR2 values of 0x01 to 0xFF are valid in this mode.

Figure 20-3 illustrates the waveforms for Master mode. When the CKE bit is set, the SDOx data is valid before there is a clock edge on SCKx. The change of the input sample is shown based on the state of the SMP bit. The time when the SSPxBUF is loaded with the received data is shown.

#### FIGURE 20-3: SPI MODE WAVEFORM (MASTER MODE)

© 2010-2017 Microchip Technology Inc.

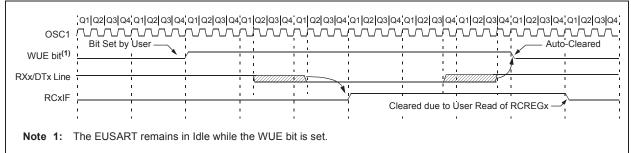

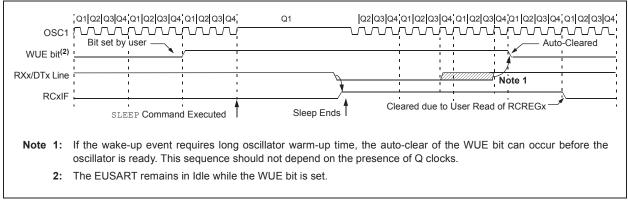

The WUE bit is automatically cleared once a low-to-high transition is observed on the RXx line following the wake-up event. At this point, the EUSART module is in Idle mode and returns to normal operation. This signals to the user that the Sync Break event is over.

#### 21.2.4.1 Special Considerations Using Auto-Wake-up

Since auto-wake-up functions by sensing rising edge transitions on RXx/DTx, information with any state changes before the Stop bit may signal a false End-Of-Character (EOC) and cause data or framing errors. To work properly, therefore, the initial character in the transmission must be all '0's. This can be 00h (8 bits) for standard RS-232 devices or 000h (12 bits) for LIN/J2602 bus.

Oscillator start-up time must also be considered, especially in applications using oscillators with longer start-up intervals (i.e., HS or HSPLL mode). The Sync Break (or Wake-up Signal) character must be of sufficient length and be followed by a sufficient interval to allow enough time for the selected oscillator to start and provide proper initialization of the EUSART.

## 21.2.4.2 Special Considerations Using the WUE Bit

The timing of WUE and RCxIF events may cause some confusion when it comes to determining the validity of received data. As noted, setting the WUE bit places the EUSART in an Idle mode. The wake-up event causes a receive interrupt by setting the RCxIF bit. The WUE bit is cleared after this when a rising edge is seen on RXx/DTx. The interrupt condition is then cleared by reading the RCREGx register. Ordinarily, the data in RCREGx will be dummy data and should be discarded.

The fact that the WUE bit has been cleared (or is still set) and the RCxIF flag is set should not be used as an indicator of the integrity of the data in RCREGx. Users should consider implementing a parallel method in firmware to verify received data integrity.

To assure that no actual data is lost, check the RCIDL bit to verify that a receive operation is not in process. If a receive operation is not occurring, the WUE bit may then be set just prior to entering Sleep mode.

#### FIGURE 21-8: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING NORMAL OPERATION

#### FIGURE 21-9: AUTO-WAKE-UP BIT (WUE) TIMINGS DURING SLEEP

The analog reference voltage is software selectable to either the device's positive and negative supply voltage (AVDD and AVSS), or the voltage level on the RA3/AN3/C1INB/VREF+ and RA2/AN2/C2INB/C1IND/C3INB/VREF-/CVREF pins.

The A/D Converter has a unique feature of being able to operate while the device is in Sleep mode. To operate in Sleep, the A/D conversion clock must be derived from the A/D's internal RC oscillator.

The output of the sample and hold is the input into the converter, which generates the result via successive approximation.

Each port pin associated with the A/D Converter can be configured as an analog input or as a digital I/O. The ADRESH and ADRESL registers contain the result of the A/D conversion. When the A/D conversion is complete, the result is loaded into the ADRESH:ADRESL register pair, the GO/DONE bit (ADCON0<1>) is cleared and the A/D Interrupt Flag bit, ADIF, is set.

A device Reset forces all registers to their Reset state. This forces the A/D module to be turned off and any conversion in progress is aborted. The value in the ADRESH:ADRESL register pair is not modified for a Power-on Reset (POR). These registers will contain unknown data after a POR.

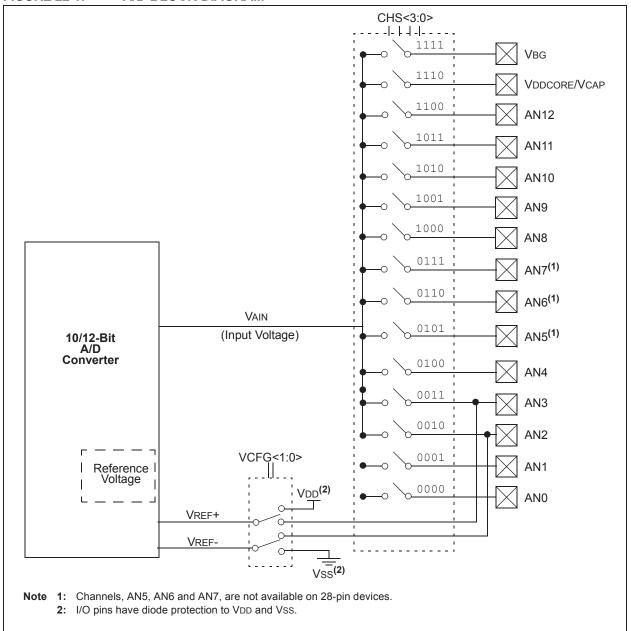

Figure 22-1 provides the block diagram of the A/D module.

FIGURE 22-1: A/D BLOCK DIAGRAM

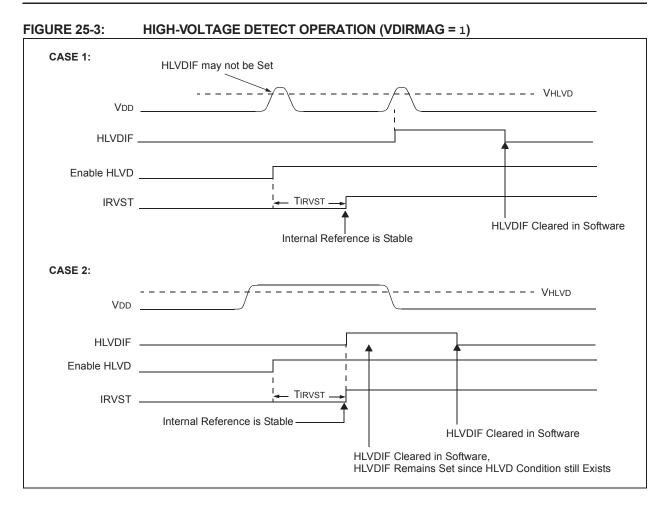

#### 25.5 Applications

In many applications, it is desirable to have the ability to detect a drop below, or rise above, a particular threshold.

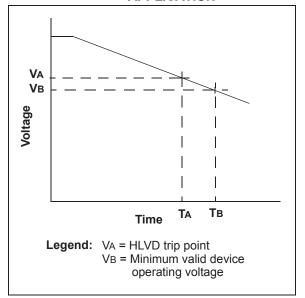

For general battery applications, Figure 25-4 provides a possible voltage curve.

Over time, the device voltage decreases. When the device voltage reaches voltage, VA, the HLVD logic generates an interrupt at time, TA. The interrupt could cause the execution of an ISR, which would allow the application to perform "housekeeping tasks" and perform a controlled shutdown before the device voltage exits the valid operating range at TB.

The HLVD, thus, would give the application a time window, represented by the difference between TA and TB, to safely exit.

TYPICAL HIGH/ LOW-VOLTAGE DETECT APPLICATION

#### REGISTER 27-4: CONFIG2H: CONFIGURATION REGISTER 2 HIGH (BYTE ADDRESS 300003h)

| U-1   | U-1 | U-1 | U-1 | R/WO-1 | R/WO-1 | R/WO-1 | R/WO-1 |

|-------|-----|-----|-----|--------|--------|--------|--------|

| —     | —   | —   | —   | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 |

| bit 7 |     |     |     |        |        |        | bit 0  |

| Legend:           |                     |                        |                    |

|-------------------|---------------------|------------------------|--------------------|

| R = Readable bit  | WO = Write-Once bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-4 | <b>Unimplemented:</b> Program the corresponding Flash Configuration bit to '1' |  |

|---------|--------------------------------------------------------------------------------|--|

|         |                                                                                |  |

| bit 3-0 | WDTPS<3:0>: Watchdog Timer Postscale Select bits |

|---------|--------------------------------------------------|

|         | 1111 <b>= 1:32,768</b>                           |

|      | ,          |

|------|------------|

| 1110 | = 1:16,384 |

| 1101 | = 1:8,192  |

| 1100 | = 1:4,096  |

| 1011 | = 1:2,048  |

| 1010 | = 1:1,024  |

| 1001 | = 1:512    |

| 1000 | = 1:256    |

| 0111 | = 1:128    |

| 0110 | = 1:64     |

| 0101 | = 1:32     |

| 0100 | = 1:16     |

| 0011 | = 1:8      |

| 0010 | = 1:4      |

| 0001 | = 1:2      |

| 0000 | = 1:1      |

|      |            |

#### 30.4 DC Characteristics: PIC18F47J13 Family (Industrial)

|              |        |                                        | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |       |                                                    |  |

|--------------|--------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------------------------|--|

| Param<br>No. | Symbol | Characteristic                         | Тур                                                                                                                                    | Мах  | Units | Conditions                                         |  |

|              | lı∟    | Input Leakage Current <sup>(1,2)</sup> |                                                                                                                                        |      |       |                                                    |  |

| D060         |        | I/O Ports without 5.5V Tolerance       | ±5                                                                                                                                     | ±200 |       | $Vss \le VPIN \le VDD,$ Pin at high-impedance      |  |

|              |        | I/O Ports with 5.5V Tolerance          | ±5                                                                                                                                     | ±200 |       | Vss $\leq$ VPIN $\leq$ 5.5V, Pin at high-impedance |  |

| D061         |        | MCLR                                   | ±5                                                                                                                                     | ±200 | nA    | $Vss \leq V PIN \leq V DD$                         |  |

| D063         |        | OSC1                                   | ±5                                                                                                                                     | ±200 | nA    | $Vss \leq V \text{PIN} \leq V \text{DD}$           |  |

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

2: Negative current is defined as current sourced by the pin.

#### TABLE 30-1: MEMORY PROGRAMMING REQUIREMENTS

| IDC CHARACTERISTICS |       |                                       | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |      |       |                                               |  |