Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 48MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 22                                                                           |

| Program Memory Size        | 128KB (64K x 16)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 3.8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                   |

| Data Converters            | A/D 10x10b/12b                                                               |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 28-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf27j13t-i-so |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| U-0            | R-0 <sup>(2)</sup> | U-0                                                                                                      | R/W-1     | R/W-0 <sup>(2)</sup>     | R/W-1            | U-0           | U-0   |  |  |  |

|----------------|--------------------|----------------------------------------------------------------------------------------------------------|-----------|--------------------------|------------------|---------------|-------|--|--|--|

| _              | SOSCRUN            | _                                                                                                        | SOSCDRV   | SOSCGO <sup>(3)</sup>    | _                |               |       |  |  |  |

| bit 7          |                    | l                                                                                                        | •         |                          |                  | •             | bit ( |  |  |  |

| Legend:        |                    |                                                                                                          |           |                          |                  |               |       |  |  |  |

| R = Readab     | le bit             | W = Writable                                                                                             | bit       | U = Unimplen             | nented bit. read | <b>as</b> '0' |       |  |  |  |

| -n = Value a   | t POR              | W = Writable bitU = Unimplemented bit, read as '0''1' = Bit is set'0' = Bit is clearedx = Bit is unknown |           |                          |                  |               |       |  |  |  |

|                |                    |                                                                                                          |           |                          |                  |               |       |  |  |  |

| bit 7          | Unimplemen         | ted: Read as '                                                                                           | 0'        |                          |                  |               |       |  |  |  |

| bit 6          | SOSCRUN: S         | SOSC Run Stat                                                                                            | us bit    |                          |                  |               |       |  |  |  |

|                |                    | lock comes fro<br>lock comes fro                                                                         |           | SOSC<br>or other than SC | DSC              |               |       |  |  |  |

| bit 5          | Unimplemen         | ted: Read as '                                                                                           | 0'        |                          |                  |               |       |  |  |  |

| bit 4          | SOSCDRV: S         | OSC Drive Co                                                                                             | ntrol bit |                          |                  |               |       |  |  |  |

|                |                    | OSC oscillato<br>er T1OSC/SO                                                                             |           |                          | Configuration bi | ts, CONFIG2L  | <4:3> |  |  |  |

|                | -                  | cillator Start C                                                                                         |           |                          |                  |               |       |  |  |  |

| bit 3          |                    |                                                                                                          |           | pherals are rec          | uesting it       |               |       |  |  |  |

| bit 3          |                    |                                                                                                          |           | s are requestin          | ig it            |               |       |  |  |  |

| bit 3<br>bit 2 |                    | is shut off unl                                                                                          |           | s are requestin          | ig it            |               |       |  |  |  |

- 2: Default output frequency of INTOSC on Reset (4 MHz).

- 3: When the SOSC is selected to run from a digital clock input, rather than an external crystal, this bit has no effect.

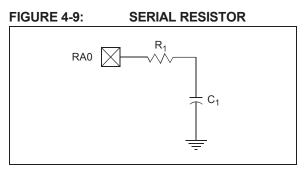

A series resistor between RA0 and the external capacitor provides overcurrent protection for the RA0/AN0/C1INA/ULPWU/RP0 pin and can allow for software calibration of the time-out (see Figure 4-9).

A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired interrupt delay. This technique will compensate for the affects of temperature, voltage and component accuracy. The ULPWU peripheral can also be configured as a simple Programmable Low-Voltage Detect (LVD) or temperature sensor.

| Note: | For more information, refer to AN879, |

|-------|---------------------------------------|

|       | Using the Microchip Ultra Low-Power   |

|       | Wake-up Module application note       |

|       | (DS00879).                            |

## 4.8 Peripheral Module Disable

All peripheral modules (except for I/O ports) also have a second control bit that can disable their functionality. These bits, known as the Peripheral Module Disable (PMD) bits, are generically named "xxxMD" (using "xxx" as the mnemonic version of the module's name).

These bits are located in the PMDISx special function registers. In contrast to the module enable bits (generically named "xxxEN" and located in bit position seven of the control registers), the PMD bits must be set (= 1) to disable the modules.

While the PMD and module enable bits both disable a peripheral's functionality, the PMD bit completely shuts down the peripheral, effectively powering down all circuits and removing all clock sources. This has the additional effect of making any of the module's control and buffer registers, mapped in the SFR space, unavailable for operations. Essentially, the peripheral ceases to exist until the PMD bit is cleared.

This differs from using the module enable bit, which allows the peripheral to be reconfigured and buffer registers preloaded, even when the peripheral's operations are disabled.

The PMD bits are most useful in highly power-sensitive applications. In these cases, the bits can be set before the main body of the application to remove peripherals that will not be needed at all.

| Register | Bit 7                | Bit 6   | Bit 5                 | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on POR, BOR |

|----------|----------------------|---------|-----------------------|---------|---------|--------|--------|--------|-------------------|

| PMDIS3   | CCP10MD              | CCP9MD  | CCP8MD                | CCP7MD  | CCP6MD  | CCP5MD | CCP4MD | _      | 0000 000-         |

| PMDIS2   | —                    | TMR8MD  | —                     | TMR6MD  | TMR5MD  | CMP3MD | CMP2MD | CMP1MD | -0-0 0000         |

| PMDIS1   | PSPMD <sup>(1)</sup> | CTMUMD  | RTCCMD <sup>(2)</sup> | TMR4MD  | TMR3MD  | TMR2MD | TMR1MD | _      | 0000 000-         |

| PMDIS0   | ECCP3MD              | ECCP2MD | ECCP1MD               | UART2MD | UART1MD | SPI2MD | SP11MD | ADCMD  | 0000 0000         |

## TABLE 4-2:LOW-POWER MODE REGISTERS

Note 1: Not implemented on 28-pin devices (PIC18F26J13, PIC18F27J13, PIC18LF26J13 and PIC18LF27J13).

2: To prevent accidental RTCC changes, the RTCCMD bit is normally locked. Use the following unlock sequence (with interrupts disabled) to successfully modify the RTCCMD bit:

1. Write 55h to EECON2.

2. Write 0AAh to EECON2.

3. Immediately write the modified RTCCMD setting to PMDIS1.

| Register |             | e Devices   | Power-on Reset,<br>Brown-out Reset,<br>Wake From Deep<br>Sleep | MCLR Resets<br>WDT Reset<br>RESET Instruction<br>Stack Resets<br>CM Resets | Wake-up via WDT<br>or Interrupt |  |

|----------|-------------|-------------|----------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------|--|

| CM3CON   | PIC18F2XJ13 | PIC18F4XJ13 | 0001 1111                                                      | 0001 1111                                                                  | นนนน นนนน                       |  |

| TMR5H    | PIC18F2XJ13 | PIC18F4XJ13 | XXXX XXXX                                                      | นนนน นนนน                                                                  | սսսս սսսս                       |  |

| TMR5L    | PIC18F2XJ13 | PIC18F4XJ13 | XXXX XXXX                                                      | սսսս սսսս                                                                  | սսսս սսսս                       |  |

| T5CON    | PIC18F2XJ13 | PIC18F4XJ13 | 0000 0000                                                      | սսսս սսսս                                                                  | uuuu uuuu                       |  |

| T5GCON   | PIC18F2XJ13 | PIC18F4XJ13 | 0000 0x00                                                      | uuuu uquu                                                                  | uuuu uquu                       |  |

| TMR6     | PIC18F2XJ13 | PIC18F4XJ13 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |

| PR6      | PIC18F2XJ13 | PIC18F4XJ13 | 1111 1111                                                      | 1111 1111                                                                  | սսսս սսսս                       |  |

| T6CON    | PIC18F2XJ13 | PIC18F4XJ13 | -000 0000                                                      | -000 0000                                                                  | -uuu uuuu                       |  |

| TMR8     | PIC18F2XJ13 | PIC18F4XJ13 | 0000 0000                                                      | 0000 0000                                                                  | սսսս սսսս                       |  |

| PR8      | PIC18F2XJ13 | PIC18F4XJ13 | 1111 1111                                                      | 1111 1111                                                                  | uuuu uuuu                       |  |

| T8CON    | PIC18F2XJ13 | PIC18F4XJ13 | -000 0000                                                      | -000 0000                                                                  | -uuu uuuu                       |  |

| PSTR3CON | PIC18F2XJ13 | PIC18F4XJ13 | 00-0 0001                                                      | 00-0 0001                                                                  | uu-u uuuu                       |  |

| ECCP3AS  | PIC18F2XJ13 | PIC18F4XJ13 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |

| ECCP3DEL | PIC18F2XJ13 | PIC18F4XJ13 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |

| CCPR3H   | PIC18F2XJ13 | PIC18F4XJ13 | XXXX XXXX                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |

| CCPR3L   | PIC18F2XJ13 | PIC18F4XJ13 | XXXX XXXX                                                      | սսսս սսսս                                                                  | uuuu uuuu                       |  |

| CCP3CON  | PIC18F2XJ13 | PIC18F4XJ13 | 0000 0000                                                      | 0000 0000                                                                  | uuuu uuuu                       |  |

| CCPR4H   | PIC18F2XJ13 | PIC18F4XJ13 | XXXX XXXX                                                      | սսսս սսսս                                                                  | uuuu uuuu                       |  |

| CCPR4L   | PIC18F2XJ13 | PIC18F4XJ13 | XXXX XXXX                                                      | սսսս սսսս                                                                  | uuuu uuuu                       |  |

| CCP4CON  | PIC18F2XJ13 | PIC18F4XJ13 | 00 0000                                                        | 00 0000                                                                    | uu uuuu                         |  |

| CCPR5H   | PIC18F2XJ13 | PIC18F4XJ13 | XXXX XXXX                                                      | սսսս սսսս                                                                  | uuuu uuuu                       |  |

| CCPR5L   | PIC18F2XJ13 | PIC18F4XJ13 | XXXX XXXX                                                      | սսսս սսսս                                                                  | սսսս սսսս                       |  |

| CCP5CON  | PIC18F2XJ13 | PIC18F4XJ13 | 00 0000                                                        | 00 0000                                                                    | uu uuuu                         |  |

| CCPR6H   | PIC18F2XJ13 | PIC18F4XJ13 | XXXX XXXX                                                      | սսսս սսսս                                                                  | uuuu uuuu                       |  |

| CCPR6L   | PIC18F2XJ13 | PIC18F4XJ13 | XXXX XXXX                                                      | uuuu uuuu                                                                  | uuuu uuuu                       |  |

| CCP6CON  | PIC18F2XJ13 | PIC18F4XJ13 | 00 0000                                                        | 00 0000                                                                    | uu uuuu                         |  |

| CCPR7H   | PIC18F2XJ13 | PIC18F4XJ13 | XXXX XXXX                                                      | սսսս սսսս                                                                  | սսսս սսսս                       |  |

| CCPR7L   | PIC18F2XJ13 | PIC18F4XJ13 | XXXX XXXX                                                      | սսսս սսսս                                                                  | սսսս սսսս                       |  |

| CCP7CON  | PIC18F2XJ13 | PIC18F4XJ13 | 00 0000                                                        | 00 0000                                                                    | 00 0000                         |  |

| CCPR8H   | PIC18F2XJ13 | PIC18F4XJ13 | XXXX XXXX                                                      | սսսս սսսս                                                                  | սսսս սսսս                       |  |

| CCPR8L   | PIC18F2XJ13 | PIC18F4XJ13 | XXXX XXXX                                                      | սսսս սսսս                                                                  | սսսս սսսս                       |  |

| CCP8CON  | PIC18F2XJ13 | PIC18F4XJ13 | 00 0000                                                        | 00 0000                                                                    | uu uuuu                         |  |

## TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

**Legend:** u = unchanged, x = unknown, – = unimplemented bit, read as '0', q = value depends on condition.

**Note 1:** When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- 3: One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 4: See Table 5-1 for the Reset value for a specific condition.

- 5: Not implemented on PIC18F2XJ13 devices.

- 6: Not implemented on "LF" devices.

## 6.3.4 SPECIAL FUNCTION REGISTERS

The SFRs are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy more than the top half of Bank 15 (F40h to FFFh). Table 6-2, Table 6-3 and Table 6-4 provide a list of these registers.

The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the peripheral functions. The Reset and Interrupt registers are described in their corresponding chapters, while the

ALU's STATUS register is described later in this section. Registers related to the operation of the peripheral features are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's

Note: The SFRs located between EB0h and F5Fh are not part of the Access Bank. Either BANKED instructions (using BSR) or the MOVFF instruction should be used to access these locations. When programming in MPLAB<sup>®</sup> C18, the compiler will automatically use the appropriate addressing mode.

## TABLE 6-2: ACCESS BANK SPECIAL FUNCTION REGISTER MAP

| Address | Name                    | Address | Name                    | Address | Name     | Address | Name                   | Address | Name                     |

|---------|-------------------------|---------|-------------------------|---------|----------|---------|------------------------|---------|--------------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(1)</sup>    | FBFh    | PSTR1CON | F9Fh    | IPR1                   | F7Fh    | SPBRGH1                  |

| FFEh    | TOSH                    | FDEh    | POSTINC2 <sup>(1)</sup> | FBEh    | ECCP1AS  | F9Eh    | PIR1                   | F7Eh    | BAUDCON1                 |

| FFDh    | TOSL                    | FDDh    | POSTDEC2 <sup>(1)</sup> | FBDh    | ECCP1DEL | F9Dh    | PIE1                   | F7Dh    | SPBRGH2                  |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(1)</sup>  | FBCh    | CCPR1H   | F9Ch    | RCSTA2                 | F7Ch    | BAUDCON2                 |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(1)</sup>   | FBBh    | CCPR1L   | F9Bh    | OSCTUNE                | F7Bh    | TMR3H                    |

| FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | CCP1CON  | F9Ah    | T1GCON                 | F7Ah    | TMR3L                    |

| FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    | PSTR2CON | F99h    | IPR5                   | F79h    | T3CON                    |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    | ECCP2AS  | F98h    | PIR5                   | F78h    | TMR4                     |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | ECCP2DEL | F97h    | T3GCON                 | F77h    | PR4                      |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | CCPR2H   | F96h    | TRISE                  | F76h    | T4CON                    |

| FF5h    | TABLAT                  | FD5h    | TOCON                   | FB5h    | CCPR2L   | F95h    | TRISD                  | F75h    | SSP2BUF                  |

| FF4h    | PRODH                   | FD4h    | (5)                     | FB4h    | CCP2CON  | F94h    | TRISC                  | F74h    | SSP2ADD <sup>(3)</sup>   |

| FF3h    | PRODL                   | FD3h    | OSCCON                  | FB3h    | CTMUCONH | F93h    | TRISB                  | F73h    | SSP2STAT                 |

| FF2h    | INTCON                  | FD2h    | CM1CON                  | FB2h    | CTMUCONL | F92h    | TRISA                  | F72h    | SSP2CON1                 |

| FF1h    | INTCON2                 | FD1h    | CM2CON                  | FB1h    | CTMUICON | F91h    | PIE5                   | F71h    | SSP2CON2                 |

| FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | SPBRG1   | F90h    | IPR4                   | F70h    | CMSTAT                   |

| FEFh    | INDF0 <sup>(1)</sup>    | FCFh    | TMR1H                   | FAFh    | RCREG1   | F8Fh    | PIR4                   | F6Fh    | PMADDRH <sup>(2,4)</sup> |

| FEEh    | POSTINC0 <sup>(1)</sup> | FCEh    | TMR1L                   | FAEh    | TXREG1   | F8Eh    | PIE4                   | F6Eh    | PMADDRL <sup>(2,4)</sup> |

| FEDh    | POSTDEC0 <sup>(1)</sup> | FCDh    | T1CON                   | FADh    | TXSTA1   | F8Dh    | LATE <sup>(2)</sup>    | F6Dh    | PMDIN1H <sup>(2)</sup>   |

| FECh    | PREINC0 <sup>(1)</sup>  | FCCh    | TMR2                    | FACh    | RCSTA1   | F8Ch    | LATD <sup>(2)</sup>    | F6Ch    | PMDIN1L <sup>(2)</sup>   |

| FEBh    | PLUSW0 <sup>(1)</sup>   | FCBh    | PR2                     | FABh    | SPBRG2   | F8Bh    | LATC                   | F6Bh    | TXADDRL                  |

| FEAh    | FSR0H                   | FCAh    | T2CON                   | FAAh    | RCREG2   | F8Ah    | LATB                   | F6Ah    | TXADDRH                  |

| FE9h    | FSR0L                   | FC9h    | SSP1BUF                 | FA9h    | TXREG2   | F89h    | LATA                   | F69h    | RXADDRL                  |

| FE8h    | WREG                    | FC8h    | SSP1ADD <sup>(3)</sup>  | FA8h    | TXSTA2   | F88h    | DMACON1                | F68h    | RXADDRH                  |

| FE7h    | INDF1 <sup>(1)</sup>    | FC7h    | SSP1STAT                | FA7h    | EECON2   | F87h    | OSCCON2 <sup>(5)</sup> | F67h    | DMABCL                   |

| FE6h    | POSTINC1 <sup>(1)</sup> | FC6h    | SSP1CON1                | FA6h    | EECON1   | F86h    | DMACON2                | F66h    | DMABCH                   |

| FE5h    | POSTDEC1 <sup>(1)</sup> | FC5h    | SSP1CON2                | FA5h    | IPR3     | F85h    | HLVDCON                | F65h    | _                        |

| FE4h    | PREINC1 <sup>(1)</sup>  | FC4h    | ADRESH                  | FA4h    | PIR3     | F84h    | PORTE <sup>(2)</sup>   | F64h    | _                        |

| FE3h    | PLUSW1 <sup>(1)</sup>   | FC3h    | ADRESL                  | FA3h    | PIE3     | F83h    | PORTD <sup>(2)</sup>   | F63h    | _                        |

| FE2h    | FSR1H                   | FC2h    | ADCON0                  | FA2h    | IPR2     | F82h    | PORTC                  | F62h    | —                        |

| FE1h    | FSR1L                   | FC1h    | ADCON1                  | FA1h    | PIR2     | F81h    | PORTB                  | F61h    | —                        |

| FE0h    | BSR                     | FC0h    | WDTCON                  | FA0h    | PIE2     | F80h    | PORTA                  | F60h    | _                        |

Note 1: This is not a physical register.

2: This register is not available on 28-pin devices.

3: SSPxADD and SSPxMSK share the same address.

**4:** PMADDRH and PMDOUTH share the same address, and PMADDRL and PMDOUTL share the same address. PMADDRx is used in Master modes and PMDOUTx is used in Slave modes.

5: Reserved; do not write to this location.

## 6.6.3 MAPPING THE ACCESS BANK IN INDEXED LITERAL OFFSET MODE

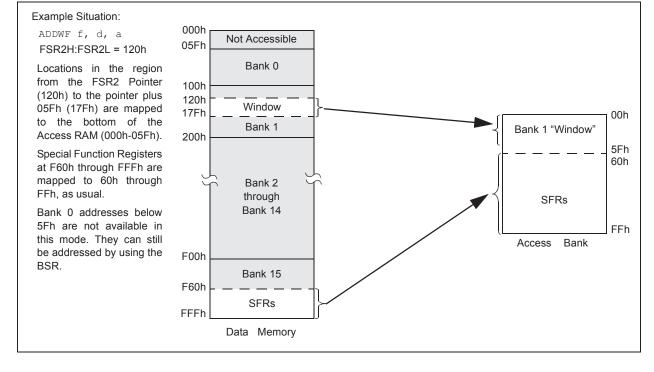

The use of Indexed Literal Offset Addressing mode effectively changes how the lower part of Access RAM (00h to 5Fh) is mapped. Rather than containing just the contents of the bottom part of Bank 0, this mode maps the contents from Bank 0 and a user-defined "window" that can be located anywhere in the data memory space. The value of FSR2 establishes the lower boundary of the addresses mapped to the window, while the upper boundary is defined by FSR2 plus 95 (5Fh). Addresses in the Access RAM above 5Fh are mapped as previously described (see Section 6.3.2 "Access Bank"). Figure 6-10 provides an example of Access Bank remapping in this addressing mode.

Remapping of the Access Bank applies only to operations using the Indexed Literal Offset mode. Operations that use the BSR (Access RAM bit is '1') will continue to use Direct Addressing as before. Any Indirect or Indexed Addressing operation that explicitly uses any of the indirect file operands (including FSR2) will continue to operate as standard Indirect Addressing. Any instruction that uses the Access Bank, but includes a register address of greater than 05Fh, will use Direct Addressing and the normal Access Bank map.

## 6.6.4 BSR IN INDEXED LITERAL OFFSET MODE

Although the Access Bank is remapped when the extended instruction set is enabled, the operation of the BSR remains unchanged. Direct Addressing, using the BSR to select the data memory bank, operates in the same manner as previously described.

## FIGURE 6-10: REMAPPING THE ACCESS BANK WITH INDEXED LITERAL OFFSET ADDRESSING

## 7.5.3 WRITE VERIFY

Depending on the application, good programming practice may dictate that the value written to the memory should be verified against the original value. This should be used in applications where excessive writes can stress bits near the specification limit.

## 7.5.4 UNEXPECTED TERMINATION OF WRITE OPERATION

If a write is terminated by an unplanned event, such as loss of power or an unexpected Reset, the memory location just programmed should be verified and reprogrammed <u>if needed</u>. If the write operation is interrupted by a MCLR Reset, or a WDT time-out Reset during normal operation, the user can check the WRERR bit and rewrite the location(s) as needed.

## 7.6 Flash Program Operation During Code Protection

See Section 27.6 "Program Verification and Code Protection" for details on code protection of Flash program memory.

## TABLE 7-2: REGISTERS ASSOCIATED WITH PROGRAM FLASH MEMORY

| Name    | Bit 7                                                         | Bit 6        | Bit 5  | Bit 4                                                   | Bit 3 | Bit 2  | Bit 1  | Bit 0 |  |  |

|---------|---------------------------------------------------------------|--------------|--------|---------------------------------------------------------|-------|--------|--------|-------|--|--|

| TBLPTRU | —                                                             | —            | bit 21 | Program Memory Table Pointer Upper Byte (TBLPTR<20:16>) |       |        |        |       |  |  |

| TBPLTRH | TBPLTRH Program Memory Table Pointer High Byte (TBLPTR<15:8>) |              |        |                                                         |       |        |        |       |  |  |

| TBLPTRL | Program Memory Table Pointer Low Byte (TBLPTR<7:0>)           |              |        |                                                         |       |        |        |       |  |  |

| TABLAT  | Program Me                                                    | mory Table L | atch   |                                                         |       |        |        |       |  |  |

| INTCON  | GIE/GIEH                                                      | PEIE/GIEL    | TMR0IE | INT0IE                                                  | RBIE  | TMR0IF | INT0IF | RBIF  |  |  |

| EECON2  | Program Memory Control Register 2 (not a physical register)   |              |        |                                                         |       |        |        |       |  |  |

| EECON1  | —                                                             | _            | WPROG  | FREE                                                    | WRERR | WREN   | WR     |       |  |  |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used during Flash program memory access.

## 9.2 PIR Registers

The PIR registers contain the individual flag bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Request (Flag) registers (PIR1, PIR2, PIR3).

- Note 1: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Interrupt Enable bit, GIE (INT-CON<7>).

- 2: User software should ensure the appropriate interrupt flag bits are cleared prior to enabling an interrupt and after servicing that interrupt.

## REGISTER 9-4: PIR1: PERIPHERAL INTERRUPT REQUEST (FLAG) REGISTER 1 (ACCESS F9Eh)

| R/W-0                | R/W-0 | R-0   | R-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|----------------------|-------|-------|-------|--------|--------|--------|--------|

| PMPIF <sup>(1)</sup> | ADIF  | RC1IF | TX1IF | SSP1IF | CCP1IF | TMR2IF | TMR1IF |

| bit 7                |       |       |       |        |        |        | bit 0  |

| Legend:      |                           |                                                                |                                                  |                       |

|--------------|---------------------------|----------------------------------------------------------------|--------------------------------------------------|-----------------------|

| R = Readab   | ole bit                   | W = Writable bit                                               | U = Unimplemented bit                            | , read as '0'         |

| -n = Value a | at POR                    | '1' = Bit is set                                               | '0' = Bit is cleared                             | x = Bit is unknown    |

| bit 7        | PMPIF: F                  | Parallel Master Port Read/Wr                                   | ite Interrupt Flag bit <sup>(1)</sup>            |                       |

|              |                           | ad or a write operation has tal<br>ead or write has occurred   | ken place (must be cleared in                    | software)             |

| bit 6        | ADIF: A/                  | D Converter Interrupt Flag bi                                  | t                                                |                       |

|              |                           | A/D conversion completed (m<br>A/D conversion is not comple    |                                                  |                       |

| bit 5        | RC1IF: E                  | EUSART1 Receive Interrupt F                                    | Flag bit                                         |                       |

|              |                           | EUSART1 receive buffer, RC<br>EUSART1 receive buffer is e      | CREG1, is full (cleared when F<br>empty          | RCREG1 is read)       |

| bit 4        | TX1IF: E                  | USART1 Transmit Interrupt F                                    | Flag bit                                         |                       |

|              |                           | EUSART1 transmit buffer, TX<br>EUSART1 transmit buffer is t    | KREG1, is empty (cleared whe<br>full             | en TXREG1 is written) |

| bit 3        | SSP1IF:                   | Master Synchronous Serial F                                    | Port 1 Interrupt Flag bit                        |                       |

|              |                           | transmission/reception is cor<br>ting to transmit/receive      | nplete (must be cleared in sof                   | tware)                |

| bit 2        | CCP1IF:                   | ECCP1 Interrupt Flag bit                                       |                                                  |                       |

|              |                           |                                                                | ccurred (must be cleared in so                   | oftware)              |

|              |                           |                                                                | match occurred (must be clea<br>e match occurred | ared in software)     |

|              | <u>PWM mo</u><br>Unused i | <u>ode:</u><br>in this mode.                                   |                                                  |                       |

| bit 1        | TMR2IF:                   | TMR2 to PR2 Match Interrup                                     | ot Flag bit                                      |                       |

|              |                           | R2 to PR2 match occurred (m<br>FMR2 to PR2 match occurred      | ,                                                |                       |

| bit 0        | TMR1IF:                   | TMR1 Overflow Interrupt Fla                                    | ag bit                                           |                       |

|              |                           | R1 register overflowed (must l<br>R1 register did not overflow | be cleared in software)                          |                       |

| Note 1: T    | These bits a              | re unimplemented on 28-pin o                                   | devices.                                         |                       |

## REGISTER 10-30: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTER 6 (BANKED EC6h)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | RP6R4 | RP6R3 | RP6R2 | RP6R1 | RP6R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | R/W = Readable bit, Writa | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |  |  |  |  |  |

|-------------------|---------------------------|-------------------------------------------------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read as '0'                          |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared x = Bit is unknown                     |  |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP6R<4:0>:** Peripheral Output Function is Assigned to RP6 Output Pin bits (see Table 10-14 for peripheral function numbers)

## REGISTER 10-31: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTER 7 (BANKED EC7h)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | RP7R4 | RP7R3 | RP7R2 | RP7R1 | RP7R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | R/W = Readable bit, | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                    |  |

|-------------------|---------------------|-------------------------------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit                                       | , read as '0'      |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared                                        | x = Bit is unknown |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP7R<4:0>:** Peripheral Output Function is Assigned to RP7 Output Pin bits (see Table 10-14 for peripheral function numbers)

## REGISTER 10-32: RPOR8: PERIPHERAL PIN SELECT OUTPUT REGISTER 8 (BANKED EC8h)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

|       | —   | —   | RP8R4 | RP8R3 | RP8R2 | RP8R1 | RP8R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable bit, W | Vritable bit if IOLOCK = 0 |                    |

|-------------------|------------------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit                   | U = Unimplemented bit,     | , read as '0'      |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP8R<4:0>:** Peripheral Output Function is Assigned to RP8 Output Pin bits (see Table 10-14 for peripheral function numbers)

## 11.3 MASTER PORT MODES

In its Master modes, the PMP module provides an 8-bit data bus, up to 16 bits of address, and all the necessary control signals to operate a variety of external parallel devices, such as memory devices, peripherals and slave microcontrollers. To use the PMP as a master, the module must be enabled (PMPEN = 1) and the mode must be set to one of the two possible Master modes (PMMODEH<1:0> = 10 or 11).

Because there are a number of parallel devices with a variety of control methods, the PMP module is designed to be extremely flexible to accommodate a range of configurations. Some of these features include:

- · 8-Bit and 16-Bit Data modes on an 8-bit data bus

- · Configurable address/data multiplexing

- · Up to two chip select lines

- Up to 16 selectable address lines

- · Address auto-increment and auto-decrement

- · Selectable polarity on all control lines

- Configurable Wait states at different stages of the read/write cycle

## 11.3.1 PMP AND I/O PIN CONTROL

Multiple control bits are used to configure the presence or absence of control and address signals in the module. These bits are PTBEEN, PTWREN, PTRDEN and PTEN<15:0>. They give the user the ability to conserve pins for other functions and allow flexibility to control the external address. When any one of these bits is set, the associated function is present on its associated pin; when clear, the associated pin reverts to its defined I/O port function.

Setting a PTENx bit will enable the associated pin as an address pin and drive the corresponding data contained in the PMADDR register. Clearing a PTENx bit will force the pin to revert to its original I/O function.

For the pins configured as chip select (PMCS) with the corresponding PTENx bit set, the PTEN0 and PTEN1 bits will also control the PMALL and PMALH signals. When multiplexing is used, the associated address latch signals should be enabled.

## 11.3.2 READ/WRITE-CONTROL

The PMP module supports two distinct read/write signaling methods. In Master Mode 1, read and write strobes are combined into a single control line, PMRD/PMWR. A second control line, PMENB, determines when a read or write action is to be taken. In Master Mode 2, separate read and write strobes (PMRD and PMWR) are supplied on separate pins.

All control signals (PMRD, PMWR, PMBE, PMENB, PMAL and PMCS) can be individually configured as either positive or negative polarity. Configuration is controlled by separate bits in the PMCONL register. Note that the polarity of control signals that share the same output pin (for example, PMWR and PMENB) are controlled by the same bit; the configuration depends on which Master Port mode is being used.

## 11.3.3 DATA WIDTH

The PMP supports data widths of both 8 bits and 16 bits. The data width is selected by the MODE16 bit (PMMODEH<2>). Because the data path into and out of the module is only 8 bits wide, 16-bit operations are always handled in a multiplexed fashion, with the Least Significant Byte (LSB) of data being presented first. To differentiate data bytes, the byte enable control strobe, PMBE, is used to signal when the Most Significant Byte (MSB) of data is being presented on the data lines.

## 11.3.4 ADDRESS MULTIPLEXING

In either of the Master modes (PMMODEH<1:0> = 1x), the user can configure the address bus to be multiplexed together with the data bus. This is accomplished by using the ADRMUX<1:0> bits (PMCONH<4:3>). There are three address multiplexing modes available. Typical pinout configurations for these modes are displayed in Figure 11-9, Figure 11-10 and Figure 11-11.

In Demultiplexed mode (PMCONH<4:3> = 00), data and address information are completely separated. Data bits are presented on PMD<7:0>, and address bits are presented on PMADDRH<6:0> and PMADDRL<7:0>.

In Partially Multiplexed mode (PMCONH<4:3> = 01), the lower eight bits of the address are multiplexed with the data pins on PMD<7:0>. The upper eight bits of the address are unaffected and are presented on PMADDRH<6:0>. The PMA0 pin is used as an address latch and presents the Address Latch Low (PMALL) enable strobe. The read and write sequences are extended by a complete CPU cycle during which the address is presented on the PMD<7:0> pins.

In Fully Multiplexed mode (PMCONH<4:3> = 10), the entire 16 bits of the address are multiplexed with the data pins on PMD<7:0>. The PMA0 and PMA1 pins are used to present Address Latch Low (PMALL) enable and Address Latch High (PMALH) enable strobes, respectively. The read and write sequences are extended by two complete CPU cycles. During the first cycle, the lower eight bits of the address are presented on the PMD<7:0> pins with the PMALL strobe active. During the second cycle, the upper eight bits of the address are presented on the PMD<7:0> pins with the PMALH strobe active. In the event the upper address bits are configured as chip select pins, the corresponding address bits are automatically forced to '0'.

### 13.5.1 USING TIMER1 AS A CLOCK SOURCE

The Timer1 oscillator is also available as a clock source in power-managed modes. By setting the clock select bits, SCS<1:0> (OSCCON<1:0>), to '01', the device switches to SEC\_RUN mode. Both the CPU and peripherals are clocked from the Timer1 oscillator. If the IDLEN bit (OSCCON<7>) is cleared and a SLEEP instruction is executed, the device enters SEC\_IDLE mode. Additional details are available in Section 4.0 "Low-Power Modes".

Whenever the Timer1 oscillator is providing the clock source, the Timer1 system clock status flag, SOSCRUN (OSCCON2<6>), is set. This can be used to determine the controller's current clocking mode. It can also indicate the clock source currently being used by the Fail-Safe Clock Monitor. If the Clock Monitor is enabled and the Timer1 oscillator fails while providing the clock, polling the SOSCRUN bit will indicate whether the clock is being provided by the Timer1 oscillator or another source.

## 13.5.2 TIMER1 OSCILLATOR LAYOUT CONSIDERATIONS

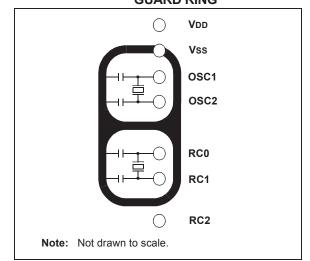

The Timer1 oscillator circuit draws very little power during operation. Due to the low-power nature of the oscillator, it may also be sensitive to rapidly changing signals in close proximity. This is especially true when the oscillator is configured for extremely Low-Power mode (SOSCSEL = 0b01).

The oscillator circuit, displayed in Figure 13-2, should be located as close as possible to the microcontroller. There should be no circuits passing within the oscillator circuit boundaries other than Vss or VDD.

If a high-speed circuit must be located near the oscillator (such as the ECCP1 pin in Output Compare or PWM mode, or the primary oscillator using the OSC2 pin), a grounded guard ring around the oscillator circuit, as displayed in Figure 13-3, may be helpful when used on a single-sided PCB or in addition to a ground plane.

#### FIGURE 13-3:

OSCILLATOR CIRCUIT WITH GROUNDED GUARD RING

In the Low Drive Level mode, SOSCSEL = 0b01, it is critical that the RC2 I/O pin signals be kept away from the oscillator circuit. Configuring RC2 as a digital output, and toggling it, can potentially disturb the oscillator circuit, even with relatively good PCB layout. If possible, it is recommended to either leave RC2 unused, or use it as an input pin with a slew rate limited signal source. If RC2 must be used as a digital output, it may be necessary to use the Higher Drive Level Oscillator mode (SOSCSEL = 0b11) with many PCB layouts. Even in the High Drive Level mode, careful layout procedures should still be followed when designing the oscillator circuit.

In addition to dV/dt induced noise considerations, it is also important to ensure that the circuit board is clean. Even a very small amount of conductive soldering flux residue can cause PCB leakage currents which can overwhelm the oscillator circuit.

## 13.6 Timer1 Interrupt

The TMR1 register pair (TMR1H:TMR1L) increments from 0000h to FFFFh and rolls over to 0000h. The Timer1 interrupt, if enabled, is generated on overflow which is latched in interrupt flag bit, TMR1IF (PIR1<0>). This interrupt can be enabled or disabled by setting or clearing the Timer1 Interrupt Enable bit, TMR1IE (PIE1<0>).

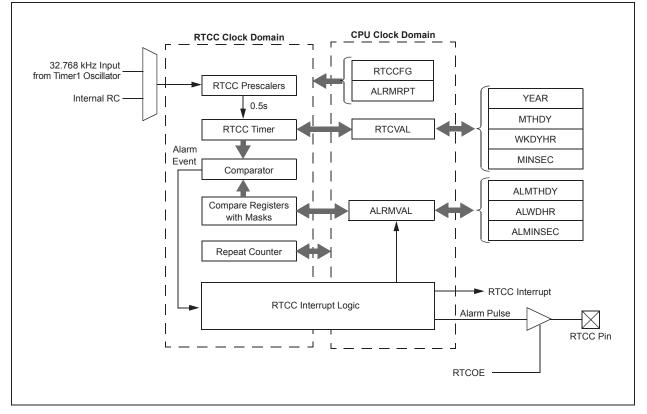

## 17.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

The key features of the Real-Time Clock and Calendar (RTCC) module are:

- · Time: hours, minutes and seconds

- 24-hour format (military time)

- Calendar: weekday, date, month and year

- · Alarm configurable

- Year range: 2000 to 2099

- · Leap year correction

- BCD format for compact firmware

- · Optimized for low-power operation

- · User calibration with auto-adjust

- Calibration range: ±2.64 seconds error per month

- Requirements: external 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

The RTCC module is intended for applications where accurate time must be maintained for an extended period with minimum to no intervention from the CPU. The module is optimized for low-power usage in order to provide extended battery life while keeping track of time.

The module is a 100-year clock and calendar with automatic leap year detection. The range of the clock is from 00:00:00 (midnight) on January 1, 2000 to 23:59:59 on December 31, 2099. Hours are measured in 24-hour (military time) format. The clock provides a granularity of one second with half second visibility to the user.

#### FIGURE 17-1: RTCC BLOCK DIAGRAM

# PIC18F47J13 FAMILY

#### REGISTER 17-2: RTCCAL: RTCC CALIBRATION REGISTER (BANKED F3Eh)

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CAL7  | CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-0 | CAL<7:0>: RTCC Drift Calibration bits<br>01111111 = Maximum positive adjustment; adds 508 RTC clock pulses every minute |

|---------|-------------------------------------------------------------------------------------------------------------------------|

|         |                                                                                                                         |

|         |                                                                                                                         |

|         | 00000001 = Minimum positive adjustment; adds four RTCC clock pulses every minute<br>00000000 = No adjustment            |

|         | 11111111 = Minimum negative adjustment; subtracts four RTCC clock pulses every minute                                   |

|         |                                                                                                                         |

|         |                                                                                                                         |

|         | 10000000 = Maximum negative adjustment; subtracts 512 RTCC clock pulses every minute                                    |

## REGISTER 17-3: PADCFG1: PAD CONFIGURATION REGISTER 1 (BANKED F3Ch)

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0                    | R/W-0                    | R/W-0                 |

|-------|-----|-----|-----|-----|--------------------------|--------------------------|-----------------------|

|       | _   | _   | _   | _   | RTSECSEL1 <sup>(1)</sup> | RTSECSEL0 <sup>(1)</sup> | PMPTTL <sup>(2)</sup> |

| bit 7 |     |     |     |     |                          |                          | bit 0                 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7-3 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2-1 | RTSECSEL<1:0>: RTCC Seconds Clock Output Select bits <sup>(1)</sup>                                                                                                                                                                                                                                                   |

|         | <ul> <li>11 = Reserved; do not use</li> <li>10 = RTCC source clock is selected for the RTCC pin (pin can be INTRC or T1OSC, depending on the RTCOSC (CONFIG3L&lt;1&gt;) setting)</li> <li>01 = RTCC seconds clock is selected for the RTCC pin</li> <li>00 = RTCC alarm pulse is selected for the RTCC pin</li> </ul> |

| bit 0   | <b>PMPTTL:</b> PMP Module TTL Input Buffer Select bit <sup>(2)</sup> <ol> <li>PMP module uses TTL input buffers</li> <li>PMP module uses Schmitt input buffers</li> </ol>                                                                                                                                             |

- **Note 1:** To enable the actual RTCC output, the RTCOE (RTCCFG<2>) bit must be set.

- 2: Available only on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13). For 28-pin devices, the bit is U-0.

## 19.0 ENHANCED CAPTURE/COMPARE/PWM (ECCP) MODULE

PIC18F47J13 Family devices have three Enhanced Capture/Compare/PWM (ECCP) modules: ECCP1, ECCP2 and ECCP3. These modules contain a 16-bit register, which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. These ECCP modules are upwardly compatible with CCP.

Note: Throughout this section, generic references are used for register and bit names that are the same – except for an 'x' variable that indicates the item's association with the ECCP1, ECCP2 or ECCP3 module. For example, the control register is named CCPxCON and refers to CCP1CON, CCP2CON and CCP3CON. The ECCP modules are implemented as standard CCP modules with enhanced PWM capabilities. These include:

- Provision for two or four output channels

- · Output Steering modes

- · Programmable polarity

- Programmable dead-band control

- Automatic shutdown and restart

The enhanced features are discussed in detail in Section 19.4 "PWM (Enhanced Mode)".

When a shutdown event occurs, two things happen:

- The ECCPxASE bit is set to '1'. The ECCPxASE will remain set until cleared in firmware or an auto-restart occurs. (See Section 19.4.5 "Auto-Restart Mode".)

- The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs (PxA/PxC and

PxB/PxD). The state of each pin pair is determined by the PSSxAC and PSSxBD bits (ECCPxAS<3:0>).

Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

## REGISTER 19-4: ECCPxAS: ECCP1/2/3 AUTO-SHUTDOWN CONTROL REGISTER (1, ACCESS FBEh; 2, FB8h; 3, BANKED F19h)

| R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0   | R/W-0   | R/W-0   | R/W-0   |

|----------|----------|----------|----------|---------|---------|---------|---------|

| ECCPxASE | ECCPxAS2 | ECCPxAS1 | ECCPxAS0 | PSSxAC1 | PSSxAC0 | PSSxBD1 | PSSxBD0 |

| bit 7    |          |          |          |         |         |         | bit 0   |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7   | ECCPxASE: ECCP Auto-Shutdown Event Status bit                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = A shutdown event has occurred; ECCP outputs are in a shutdown state</li> <li>0 = ECCP outputs are operating</li> </ul>                                                                                                                                                                                                                                                                                                                                       |

| bit 6-4 | ECCPxAS<2:0>: ECCP Auto-Shutdown Source Select bits                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         | <ul> <li>000 = Auto-shutdown is disabled</li> <li>001 = Comparator, C1OUT, output is high</li> <li>010 = Comparator, C2OUT, output is high</li> <li>011 = Either comparator, C1OUT or C2OUT, is high</li> <li>100 = VIL on FLT0 pin</li> <li>101 = VIL on FLT0 pin or comparator, C1OUT, output is high</li> <li>110 = VIL on FLT0 pin or comparator, C2OUT, output is high</li> <li>111 = VIL on FLT0 pin or comparator, C1OUT, or comparator, C2OUT, is high</li> </ul> |

| bit 3-2 | PSSxAC<1:0>: PxA and PxC Pins Shutdown State Control bits                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | 00 = Drive pins, PxA and PxC, to '0'<br>01 = Drive pins, PxA and PxC, to '1'<br>1x = PxA and PxC pins tri-state                                                                                                                                                                                                                                                                                                                                                           |

| bit 1-0 | PSSxBD<1:0>: PxB and PxD Pins Shutdown State Control bits<br>00 = Drive pins, PxB and PxD, to '0'<br>01 = Drive pins, PxB and PxD, to '1'<br>1x = PxB and PxD pins tri-state                                                                                                                                                                                                                                                                                              |

| Note 1: | The auto-shutdown condition is a level-based signal, not an edge-based signal. As long as the level is                                                                                                                                                                                                                                                                                                                                                                    |

|         | present, the auto-shutdown will persist.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2:      | Writing to the ECCPxASE bit is disabled while an auto-shutdown condition persists.                                                                                                                                                                                                                                                                                                                                                                                        |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

3: Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart), the PWM signal will always restart at the beginning of the next PWM period.

#### **REGISTER 21-1: TXSTAX: TRANSMIT STATUS AND CONTROL REGISTER** (1, ACCESS FADh; 2, FA8h) R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R-1 TXEN<sup>(1)</sup> CSRC TX9 SYNC SENDB BRGH TRMT TX9D bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' x = Bit is unknown -n = Value at POR '1' = Bit is set '0' = Bit is cleared bit 7 CSRC: Clock Source Select bit Asynchronous mode: Don't care. Synchronous mode: 1 = Master mode (clock generated internally from BRG) 0 = Slave mode (clock from external source) TX9: 9-Bit Transmit Enable bit bit 6 1 = Selects 9-bit transmission 0 = Selects 8-bit transmission TXEN: Transmit Enable bit<sup>(1)</sup> bit 5 1 = Transmit is enabled and the TXx/CKx pin is configured as an output 0 = Transmit is disabled bit 4 SYNC: EUSART Mode Select bit 1 = Synchronous mode 0 = Asynchronous mode bit 3 SENDB: Send Break Character bit Asynchronous mode: 1 = Send Sync Break on next transmission (cleared by hardware upon completion) 0 = Sync Break transmission completed Synchronous mode: Don't care. bit 2 BRGH: High Baud Rate Select bit Asynchronous mode: 1 = High speed 0 = Low speed Synchronous mode: Unused in this mode. bit 1 TRMT: Transmit Shift Register Status bit 1 = TSR is empty 0 = TSR is full TX9D: 9<sup>th</sup> bit of Transmit Data bit 0 Can be address/data bit or a parity bit.

#### Note 1: SREN/CREN overrides TXEN in Sync mode.

| Name     | Bit 7                                 | Bit 6          | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1   | Bit 0  |

|----------|---------------------------------------|----------------|--------|--------|---------|--------|---------|--------|

| INTCON   | GIE/GIEH                              | PEIE/GIEL      | TMR0IE | INT0IE | RBIE    | TMR0IF | INT0IF  | RBIF   |

| PIR1     | PMPIF <sup>(1)</sup>                  | ADIF           | RC1IF  | TX1IF  | SSP1IF  | CCP1IF | TMR2IF  | TMR1IF |

| PIE1     | PMPIE <sup>(1)</sup>                  | ADIE           | RC1IE  | TX1IE  | SSP1IE  | CCP1IE | TMR2IE  | TMR1IE |

| IPR1     | PMPIP <sup>(1)</sup>                  | ADIP           | RC1IP  | TX1IP  | SSP1IP  | CCP1IP | TMR2IP  | TMR1IP |

| PIR3     | SSP2IF                                | BCL2IF         | RC2IF  | TX2IF  | TMR4IF  | CTMUIF | TMR3GIF | RTCCIF |

| PIE3     | SSP2IE                                | BCL2IE         | RC2IE  | TX2IE  | TMR4IE  | CTMUIE | TMR3GIE | RTCCIE |

| IPR3     | SSP2IP                                | BCL2IP         | RC2IP  | TX2IP  | TMR4IP  | CTMUIP | TMR3GIP | RTCCIP |

| RCSTAx   | SPEN                                  | RX9            | SREN   | CREN   | ADDEN   | FERR   | OERR    | RX9D   |

| RCREGx   | EUSARTx Re                            | eceive Registe | er     |        |         |        |         |        |

| TXSTAx   | CSRC                                  | TX9            | TXEN   | SYNC   | SENDB   | BRGH   | TRMT    | TX9D   |

| BAUDCONx | ABDOVF                                | RCIDL          | RXDTP  | TXCKP  | BRG16   | _      | WUE     | ABDEN  |

| SPBRGHx  | EUSARTx Baud Rate Generator High Byte |                |        |        |         |        |         |        |

| SPBRGx   | EUSARTx Baud Rate Generator Low Byte  |                |        |        |         |        |         |        |

| ODCON2   | —                                     |                |        | _      | CCP10OD | CCP9OD | U2OD    | U10D   |

## TABLE 21-8: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER RECEPTION

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous master reception.

Note 1: These pins are only available on 44-pin devices.

## 22.1 A/D Acquisition Requirements

For the A/D Converter to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The analog input model is illustrated in Figure 22-2. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor, CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD). The source impedance affects the offset voltage at the analog input (due to pin leakage current). The maximum recommended impedance for analog sources is 2.5 k $\Omega$  for 10-bit conversions and 1 k $\Omega$ for 12-bit conversions. After the analog input channel is selected (changed), the channel must be sampled for at least the minimum acquisition time before starting a conversion.

| Note: | When    | the    | conversion      | is  | started,   | the   |

|-------|---------|--------|-----------------|-----|------------|-------|

|       | holding | g capa | acitor is disco | nne | ected from | n the |

|       | input p | in.    |                 |     |            |       |

## EQUATION 22-1: ACQUISITION TIME

| TACQ | = | Amplifier Settling Time + Holding Capacitor Charging Time + Temperature Coefficient |

|------|---|-------------------------------------------------------------------------------------|

|      | = | TAMP + TC + TCOFF                                                                   |

## EQUATION 22-2: A/D MINIMUM CHARGING TIME

| VHOLD | = | $(\text{VREF} - (\text{VREF}/2048)) \cdot (1 - e^{(-\text{TC/CHOLD}(\text{Ric} + \text{Rss} + \text{Rs}))})$ |

|-------|---|--------------------------------------------------------------------------------------------------------------|

| or    |   |                                                                                                              |

| TC    | = | -(CHOLD)(RIC + RSS + RS) ln(1/2048)                                                                          |

#### EQUATION 22-3: CALCULATING THE MINIMUM REQUIRED ACQUISITION TIME

| TACQ    | =       | TAMP + TC + TCOFF                                                                                                                                |

|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| TAMP    | =       | 0.2 μs                                                                                                                                           |

| TCOFF   | =       | (Temp – 25°C)(0.02 μs/°C)<br>(85°C – 25°C)(0.02 μs/°C)<br>1.2 μs                                                                                 |

| Tempera | ature c | oefficient is only required for temperatures > 25°C. Below 25°C, TCOFF = 0 $\mu$ s.                                                              |

| Тс      | =       | -(Chold)(Ric + Rss + Rs) $\ln(1/2048) \ \mu s$<br>-(25 pF) (1 k $\Omega$ + 2 k $\Omega$ + 2.5 k $\Omega$ ) ln(0.0004883) $\mu s$<br>1.05 $\mu s$ |

| TACQ    | =       | 0.2 μs + 1.05 μs + 1.2 μs<br>2.45 μs                                                                                                             |

To calculate the minimum acquisition time, Equation 22-1 may be used. This equation assumes that 1/2 LSb error is used (1,024 steps for the 10-bit A/D). The 1/2 LSb error is the maximum error allowed for the A/D to meet its specified resolution.

Equation 22-3 provides the calculation of the minimum required acquisition time, TACQ. This calculation is based on the following application system assumptions:

| CHOLD            | =      | 25 pF                            |

|------------------|--------|----------------------------------|

| Rs               | =      | 2.5 kΩ                           |

| Conversion Error | $\leq$ | 1/2 LSb                          |

| Vdd              | =      | $3V \rightarrow Rss = 2 k\Omega$ |

| Temperature      | =      | 85°C (system max.)               |

## PIC18F47J13 FAMILY

| RCA     | LL              | Relative Ca                                                                                                                         | all                                                                                       |                                                          |                                               |                                                                |  |

|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------|--|

| Syntax: |                 | RCALL n                                                                                                                             | RCALL n                                                                                   |                                                          |                                               |                                                                |  |

| Oper    | ands:           | -1024 ≤ n ≤                                                                                                                         | 1023                                                                                      |                                                          |                                               |                                                                |  |

| Oper    | ation:          | $(PC) + 2 \rightarrow (PC) + 2 + 2$                                                                                                 | ,                                                                                         |                                                          |                                               |                                                                |  |

| Statu   | s Affected:     | None                                                                                                                                |                                                                                           |                                                          |                                               |                                                                |  |

| Enco    | ding:           | 1101                                                                                                                                | lnnn                                                                                      | nnn                                                      | ın                                            | nnnn                                                           |  |

|         | .ription:       | Subroutine<br>from the cu<br>address (PC<br>stack. Then<br>number '2n<br>have incren<br>instruction,<br>PC + 2 + 2r<br>2-cycle inst | rrent loca<br>C + 2) is<br>and the<br>to the Penented to<br>the new<br>the new<br>the new | ation. I<br>pushe<br>2's c<br>C. Sin<br>o fetch<br>addre | First<br>ed or<br>omp<br>ce th<br>the<br>ss w | , return<br>hto the<br>lement<br>he PC will<br>next<br>/ill be |  |

| Word    | ls:             | 1                                                                                                                                   |                                                                                           |                                                          |                                               |                                                                |  |

| Cycle   | es:             | 2                                                                                                                                   |                                                                                           |                                                          |                                               |                                                                |  |

| QC      | ycle Activity:  |                                                                                                                                     |                                                                                           |                                                          |                                               |                                                                |  |

|         | Q1              | Q2                                                                                                                                  | Q3                                                                                        |                                                          |                                               | Q4                                                             |  |

|         | Decode          | Read literal<br>'n'<br>PUSH PC<br>to stack                                                                                          | Proce<br>Data                                                                             |                                                          | Wri                                           | te to PC                                                       |  |

|         | No<br>operation | No<br>operation                                                                                                                     | No<br>operat                                                                              | ion                                                      | ор                                            | No<br>eration                                                  |  |