Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 48MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 34                                                                          |

| Program Memory Size        | 64KB (32K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 3.8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                  |

| Data Converters            | A/D 13x10b/12b                                                              |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-VQFN Exposed Pad                                                         |

| Supplier Device Package    | 44-QFN (8x8)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf46j13-i-ml |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                                           | 9     |

|-------|---------------------------------------------------------------------------|-------|

| 2.0   | Guidelines for Getting Started with PIC18FJ Microcontrollers              | 28    |

| 3.0   | Oscillator Configurations                                                 | 32    |

| 4.0   | Low-Power Modes                                                           | 43    |

| 5.0   | Reset                                                                     | 60    |

| 6.0   | Memory Organization                                                       | 75    |

| 7.0   | Flash Program Memory                                                      | . 101 |

| 8.0   | 8 x 8 Hardware Multiplier                                                 | . 111 |

| 9.0   | Interrupts                                                                | . 113 |

| 10.0  | I/O Ports                                                                 | . 133 |

| 11.0  | Parallel Master Port (PMP)                                                | . 173 |

| 12.0  | Timer0 Module                                                             | . 198 |

| 13.0  | Timer1 Module                                                             | . 202 |

| 14.0  | Timer2 Module                                                             | . 212 |

| 15.0  | Timer3/5 Module                                                           | . 214 |

| 16.0  | Timer4/6/8 Module                                                         | . 226 |

| 17.0  | Real-Time Clock and Calendar (RTCC)                                       | . 229 |

| 18.0  | Capture/Compare/PWM (CCP) Modules                                         | . 248 |

| 19.0  | Enhanced Capture/Compare/PWM (ECCP) Module                                | . 260 |

| 20.0  | Master Synchronous Serial Port (MSSP) Module                              |       |

| 21.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | . 336 |

| 22.0  | 10/12-Bit Analog-to-Digital Converter (A/D) Module                        | . 358 |

| 23.0  | Comparator Module                                                         |       |

| 24.0  | Comparator Voltage Reference Module                                       |       |

| 25.0  | High/Low Voltage Detect (HLVD)                                            | . 380 |

| 26.0  | Charge Time Measurement Unit (CTMU)                                       |       |

| 27.0  | Special Features of the CPU                                               | . 403 |

| 28.0  | Instruction Set Summary                                                   | . 420 |

| 29.0  | Development Support                                                       | . 470 |

| 30.0  | Electrical Characteristics                                                |       |

| 31.0  | Packaging Information                                                     | . 516 |

|       | ndix A: Revision History                                                  |       |

| Appe  | ndix B: Migration From PIC18F46J11 to PIC18F47J13                         | . 534 |

|       | /icrochip Website                                                         |       |

|       | mer Change Notification Service                                           |       |

|       | mer Support                                                               |       |

| Produ | uct Identification System                                                 | . 536 |

## 3.2.2 CRYSTAL OSCILLATOR/CERAMIC RESONATORS

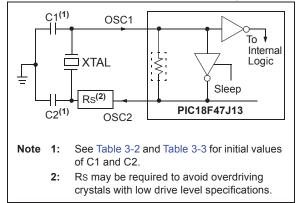

In HS and HSPLL Oscillator modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation. Figure 3-2 displays the pin connections.

The oscillator design requires the use of a parallel resonant crystal.

| Note: | Us | e of a series | resona  | ant cr | ystal r | nay give |

|-------|----|---------------|---------|--------|---------|----------|

|       | а  | frequency     | out     | of     | the     | crystal  |

|       | ma | anufacturer's | specifi | catio  | ns.     |          |

#### FIGURE 3-2: CRYSTAL/CERAMIC RESONATOR OPERATION (HS OR HSPLL CONFIGURATION)

## TABLE 3-2:CAPACITOR SELECTION FOR<br/>CERAMIC RESONATORS

| Typical Capacitor Values Used: |                     |                |                |  |

|--------------------------------|---------------------|----------------|----------------|--|

| Mode                           | Freq                | OSC1           | OSC2           |  |

| HS                             | 8.0 MHz<br>16.0 MHz | 27 pF<br>22 pF | 27 pF<br>22 pF |  |

Capacitor values are for design guidance only.

These capacitors were tested with the resonators listed below for basic start-up and operation. **These values are not optimized**.

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following Table 3-3 for additional information.

| Resonators Used: |

|------------------|

| 4.0 MHz          |

| 8.0 MHz          |

| 16.0 MHz         |

## TABLE 3-3:CAPACITOR SELECTION FOR<br/>CRYSTAL OSCILLATOR

| Osc Type | Crystal<br>Freq | Typical Capacitor Values<br>Tested: |       |  |

|----------|-----------------|-------------------------------------|-------|--|

|          | Freq            | C1                                  | C2    |  |

| HS       | 4 MHz           | 27 pF                               | 27 pF |  |

|          | 8 MHz           | 22 pF                               | 22 pF |  |

|          | 16 MHz          | 18 pF                               | 18 pF |  |

Capacitor values are for design guidance only.

These capacitors were tested with the crystals listed below for basic start-up and operation. **These values are not optimized.**

Different capacitor values may be required to produce acceptable oscillator operation. The user should test the performance of the oscillator over the expected VDD and temperature range for the application.

See the notes following this table for additional information.

| Crystals Used: |

|----------------|

| 4 MHz          |

| 8 MHz          |

| 16 MHz         |

- Note 1: Higher capacitance not only increases the stability of oscillator, but also increases the start-up time.

- 2: Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- **3:** Rs may be required to avoid overdriving crystals with low drive level specification.

- **4:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

An internal postscaler allows users to select a clock frequency other than that of the crystal or resonator. Frequency division is determined by the CPDIV Configuration bits. Users may select a clock frequency of the oscillator frequency, or 1/2, 1/3 or 1/6 of the frequency.

### 6.4.3.2 FSR Registers and POSTINC, POSTDEC, PREINC and PLUSW

In addition to the INDF operand, each FSR register pair also has four additional indirect operands. Like INDF, these are "virtual" registers that cannot be indirectly read or written to. Accessing these registers actually accesses the associated FSR register pair, but also performs a specific action on its stored value. They are:

- POSTDEC: accesses the FSR value, then automatically decrements it by one thereafter

- POSTINC: accesses the FSR value, then automatically increments it by one thereafter

- PREINC: increments the FSR value by one, then uses it in the operation

- PLUSW: adds the signed value of the W register (range of -128 to +127) to that of the FSR and uses the new value in the operation

In this context, accessing an INDF register uses the value in the FSR registers without changing them. Similarly, accessing a PLUSW register gives the FSR value offset by the value in the W register; neither value is actually changed in the operation. Accessing the other virtual registers changes the value of the FSR registers.

Operations on the FSRs with POSTDEC, POSTINC and PREINC affect the entire register pair; that is, rollovers of the FSRnL register from FFh to 00h carry over to the FSRnH register. On the other hand, results of these operations do not change the value of any flags in the STATUS register (e.g., Z, N, OV, etc.).

The PLUSW register can be used to implement a form of Indexed Addressing in the data memory space. By manipulating the value in the W register, users can reach addresses that are fixed offsets from pointer addresses. In some applications, this can be used to implement some powerful program control structure, such as software stacks, inside of data memory.

## 6.4.3.3 Operations by FSRs on FSRs

Indirect Addressing operations that target other FSRs or virtual registers represent special cases. For example, using an FSR to point to one of the virtual registers will not result in successful operations. As a specific case, assume that FSR0H:FSR0L contains FE7h, the address of INDF1. Attempts to read the value of the INDF1, using INDF0 as an operand, will return 00h. Attempts to write to INDF1, using INDF0 as the operand, will result in a NOP.

On the other hand, using the virtual registers to write to an FSR pair may not occur as planned. In these cases, the value will be written to the FSR pair but without any incrementing or decrementing. Thus, writing to INDF2 or POSTDEC2 will write the same value to the FSR2H:FSR2L.

Since the FSRs are physical registers mapped in the SFR space, they can be manipulated through all direct operations. Users should proceed cautiously when working on these registers, particularly if their code uses Indirect Addressing.

Similarly, operations by Indirect Addressing are generally permitted on all other SFRs. Users should exercise appropriate caution that they do not inadvertently change settings that might affect the operation of the device.

## 6.5 Program Memory and the Extended Instruction Set

The operation of program memory is unaffected by the use of the extended instruction set.

Enabling the extended instruction set adds five additional two-word commands to the existing PIC18 instruction set: ADDFSR, CALLW, MOVSF, MOVSS and SUBFSR. These instructions are executed as described in Section 6.2.4 "Two-Word Instructions".

## 7.0 FLASH PROGRAM MEMORY

The Flash program memory is readable, writable and erasable during normal operation over the entire  $\mathsf{V}\mathsf{D}\mathsf{D}$  range.

A read from program memory is executed on 1 byte at a time. A write to program memory is executed on blocks of 64 bytes at a time or 2 bytes at a time. Program memory is erased in blocks of 1024 bytes at a time. A bulk erase operation may not be issued from user code.

Writing or erasing program memory will cease instruction fetches until the operation is complete. The program memory cannot be accessed during the write or erase, therefore, code cannot execute. An internal programming timer terminates program memory writes and erases.

A value written to program memory does not need to be a valid instruction. Executing a program memory location that forms an invalid instruction results in a NOP.

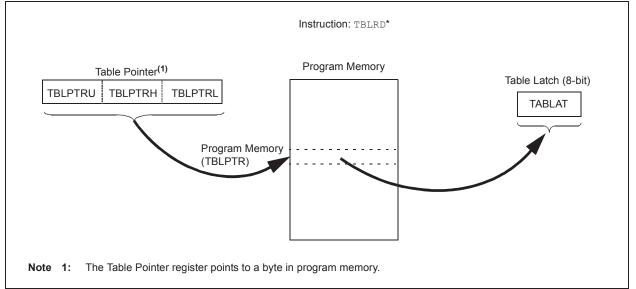

## 7.1 Table Reads and Table Writes

In order to read and write program memory, there are two operations that allow the processor to move bytes between the program memory space and the data RAM:

- Table Read (TBLRD)

- Table Write (TBLWT)

The program memory space is 16 bits wide, while the data RAM space is 8 bits wide. Table reads and table writes move data between these two memory spaces through an 8-bit register (TABLAT).

Table read operations retrieve data from program memory and place it into the data RAM space. Figure 7-1 illustrates the operation of a table read with program memory and data RAM.

Table write operations store data from the data memory space into holding registers in program memory. The procedure to write the contents of the holding registers into program memory is detailed in **Section 7.5** "Writing **to Flash Program Memory**". Figure 7-2 illustrates the operation of a table write with program memory and data RAM.

Table operations work with byte entities. A table block containing data, rather than program instructions, is not required to be word-aligned. Therefore, a table block can start and end at any byte address. If a table write is being used to write executable code into program memory, program instructions will need to be word-aligned.

FIGURE 7-1:

#### TABLE READ OPERATION

#### REGISTER 9-12: PIE4: PERIPHERAL INTERRUPT ENABLE REGISTER 4 (ACCESS F8Eh)

| R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|---------|--------|--------|--------|--------|--------|--------|--------|

| CCP10IE | CCP9IE | CCP8IE | CCP7IE | CCP6IE | CCP5IE | CCP4IE | CCP3IE |

| bit 7   |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 7-1 CCP10IE:CCP4IE: CCP<10:4> Interrupt Enable bits

- 1 = Enabled

- 0 = Disabled

#### bit 0 CCP3IE: ECCP3 Interrupt Enable bit

- 1 = Enabled

- 0 = Disabled

## REGISTER 9-13: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5 (ACCESS F91h)

| U-0   | U-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0   | R/W-0   |

|-------|-----|-------|--------|--------|--------|---------|---------|

| —     | —   | CM3IE | TMR8IE | TMR6IE | TMR5IE | TMR5GIE | TMR1GIE |

| bit 7 |     |       |        |        |        |         | bit 0   |

| Legend:           |                  |                             |                    |  |

|-------------------|------------------|-----------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |  |

| bit 7-6 | Unimplemented: Read as '0'                                                             |

|---------|----------------------------------------------------------------------------------------|

| bit 5   | <b>CM3IE:</b> Comparator 3 Receive Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled |

| bit 4   | <b>TMR8IE:</b> TMR8 to PR8 Match Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled   |

| bit 3   | <b>TMR6IE:</b> TMR6 to PR6 Match Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled   |

| bit 2   | <b>TMR5IE:</b> TMR5 Overflow Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled       |

| bit 1   | TMR5GIE: TMR5 Gate Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled                 |

| bit 0   | <b>TMR1GIE:</b> TMR1 Gate Interrupt Enable bit<br>1 = Enabled<br>0 = Disabled          |

| Pin               | Function | TRIS<br>Setting | I/O | l/O<br>Type | Description                                                                         |

|-------------------|----------|-----------------|-----|-------------|-------------------------------------------------------------------------------------|

| RB7/CCP7/         | RB7      | 0               | 0   | DIG         | LATB<7> data output.                                                                |

| KBI3/PGD/<br>RP10 |          | 1               | Ι   | TTL         | PORTB<7> data input; weak pull-up when the $\overline{\text{RBPU}}$ bit is cleared. |

|                   | CCP7     | 1               | Ι   | ST          | Capture input.                                                                      |

|                   |          | 0               | 0   | DIG         | Compare/PWM output.                                                                 |

|                   | KBI3     | 1               | 0   | TTL         | Interrupt-on-change pin.                                                            |

|                   | PGD      | х               | 0   | DIG         | Serial execution data output for ICSP and ICD operation. <sup>(2)</sup>             |

|                   |          | х               | Ι   | ST          | Serial execution data input for ICSP and ICD operation. <sup>(2)</sup>              |

|                   | RP10     | 1               | Ι   | ST          | Remappable Peripheral Pin 10 input.                                                 |

|                   |          | 0               | 0   | DIG         | Remappable Peripheral Pin 10 output.                                                |

TABLE 10-5: PORTB I/O SUMMARY (CONTINUED)

**Legend:** DIG = Digital level output; TTL = TTL input buffer; ST = Schmitt Trigger input buffer; ANA = Analog level input/output; x = Don't care (TRISx bit does not affect port direction or is overridden for this option)

**Note 1:** Pins are configured as analog inputs by default on POR. Using these pins for digital inputs requires setting the appropriate bits in the ANCON1 register.

- **2:** All other pin functions are disabled when ICSP<sup>™</sup> or ICD is enabled.

- 3: Only on 44-pin devices (PIC18F46J13, PIC18F47J13, PIC18LF46J13 and PIC18LF47J13).

- 4: Only on 28-pin devices (PIC18F26J13, PIC18F27J13, PIC18LF26J13 and PIC18LF27J13).

| Name    | Bit 7    | Bit 6     | Bit 5   | Bit 4         | Bit 3   | Bit 2     | Bit 1     | Bit 0   |

|---------|----------|-----------|---------|---------------|---------|-----------|-----------|---------|

| PORTB   | RB7      | RB6       | RB5     | RB4           | RB3     | RB2       | RB1       | RB0     |

| LATB    | LATB7    | LATB6     | LATB5   | LATB4         | LATB3   | LATB2     | LATB1     | LATB0   |

| TRISB   | TRISB7   | TRISB6    | TRISB5  | TRISB4        | TRISB3  | TRISB2    | TRISB1    | TRISB0  |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE  | <b>INTOIE</b> | RBIE    | TMR0IF    | INT0IF    | RBIF    |

| INTCON2 | RBPU     | INTEDG0   | INTEDG1 | INTEDG2       | INTEDG3 | TMR0IP    | INT3IP    | RBIP    |

| INTCON3 | INT2IP   | INT1IP    | INT3IE  | INT2IE        | INT1IE  | INT3IF    | INT2IF    | INT1IF  |

| ANCON1  | VBGEN    | —         | —       | PCFG12        | PCFG11  | PCFG10    | PCFG9     | PCFG8   |

| REFOCON | ROON     | —         | ROSSLP  | ROSEL         | RODIV3  | RODIV2    | RODIV1    | RODIV0  |

| CM3CON  | CON      | COE       | CPOL    | EVPOL1        | EVPOL0  | CREF      | CCH1      | CCH0    |

| PADCFG1 | _        | —         | —       | —             | _       | RTSECSEL1 | RTSECSEL0 | PMPTTL  |

| RTCCFG  | RTCEN    | _         | RTCWREN | RTCSYNC       | HALFSEC | RTCOE     | RTCPTR1   | RTCPTR0 |

#### TABLE 10-6: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by PORTB.

#### 10.7.3.1 Input Mapping

The inputs of the PPS options are mapped on the basis of the peripheral; that is, a control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-6 through Register 10-23). Each register contains a 5-bit field which is associated with one of the pin selectable peripherals. Programming a given peripheral's bit field with an appropriate 5-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any of the bit fields corresponds to the maximum number of Peripheral Pin Selections supported by the device.

| TABLE 10-13: SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION) | TABLE 10-13: |

|----------------------------------------------------------------|--------------|

|----------------------------------------------------------------|--------------|

| Input Name                                          | Function Name | Register | Configuration<br>Bits |

|-----------------------------------------------------|---------------|----------|-----------------------|

| External Interrupt 1                                | INT1          | RPINR1   | INTR1R<4:0>           |

| External Interrupt 2                                | INT2          | RPINR2   | INTR2R<4:0>           |

| External Interrupt 3                                | INT3          | RPINR3   | INTR3R<4:0>           |

| Timer0 External Clock Input                         | T0CKI         | RPINR4   | T0CKR<4:0>            |

| Timer3 External Clock Input                         | T3CKI         | RPINR6   | T3CKR<4:0>            |

| Timer5 External Clock Input                         | T5CKI         | RPINR15  | T5CKR<4:0>            |

| Input Capture 1                                     | CCP1          | RPINR7   | IC1R<4:0>             |

| Input Capture 2                                     | CCP2          | RPINR8   | IC2R<4:0>             |

| Input Capture 3                                     | CCP3          | RPINR9   | IC3R<4:0>             |

| Timer1 Gate Input                                   | T1G           | RPINR12  | T1GR<4:0>             |

| Timer3 Gate Input                                   | T3G           | RPINR13  | T3GR<4:0>             |

| Timer5 Gate Input                                   | T5G           | RPINR14  | T5GR<4:0>             |

| EUSART2 Asynchronous Receive/Synchronous<br>Receive | RX2/DT2       | RPINR16  | RX2DT2R<4:0>          |

| EUSART2 Asynchronous Clock Input                    | CK2           | RPINR17  | CK2R<4:0>             |

| SPI2 Data Input                                     | SDI2          | RPINR21  | SDI2R<4:0>            |

| SPI2 Clock Input                                    | SCK2IN        | RPINR22  | SCK2R<4:0>            |

| SPI2 Slave Select Input                             | SS2IN         | RPINR23  | SS2R<4:0>             |

| PWM Fault Input                                     | FLT0          | RPINR24  | OCFAR<4:0>            |

**Note 1:** Unless otherwise noted, all inputs use the Schmitt Trigger input buffers.

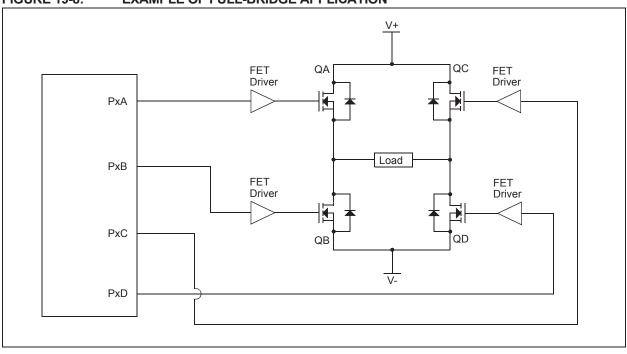

### 19.4.2 FULL-BRIDGE MODE

In Full-Bridge mode, all four pins are used as outputs. An example of a full-bridge application is provided in Figure 19-8.

In the Forward mode, the PxA pin is driven to its active state and the PxD pin is modulated, while the PxB and PxC pins are driven to their inactive state, as shown in Figure 19-9.

FIGURE 19-8: EXAMPLE OF FULL-BRIDGE APPLICATION

In the Reverse mode, the PxC pin is driven to its active state and the PxB pin is modulated, while the PxA and PxD pins are driven to their inactive state, as shown in Figure 19-9.

The PxA, PxB, PxC and PxD outputs are multiplexed with the port data latches. The associated TRIS bits must be cleared to configure the PxA, PxB, PxC and PxD pins as outputs.

#### 20.3.1 REGISTERS

Each MSSP module has four registers for SPI mode operation. These are:

- MSSPx Control Register 1 (SSPxCON1)

- MSSPx Status Register (SSPxSTAT)

- Serial Receive/Transmit Buffer Register (SSPxBUF)

- MSSPx Shift Register (SSPxSR) Not directly accessible

SSPxCON1 and SSPxSTAT are the control and status registers in SPI mode operation. The SSPxCON1 register is readable and writable. The lower six bits of the SSPxSTAT are read-only. The upper two bits of the SSPxSTAT are read/write.

SSPxSR is the shift register used for shifting data in or out. SSPxBUF is the buffer register to which data bytes are written to or read from. In receive operations, SSPxSR and SSPxBUF together, create a double-buffered receiver. When SSPxSR receives a complete byte, it is transferred to SSPxBUF and the SSPxIF interrupt is set.

During transmission, the SSPxBUF is not double-buffered. A write to SSPxBUF will write to both SSPxBUF and SSPxSR.

Note: Because the SSPxBUF register is double-buffered, using read-modify-write instructions such as BCF, COMF, etc., will not work.

Similarly, when debugging under an in-circuit debugger, performing actions that cause reads of SSPxBUF (mouse hovering, watch, etc.) can consume data that the application code was expecting to receive.

#### REGISTER 20-1: SSPxSTAT: MSSPx STATUS REGISTER (SPI MODE) (ACCESS 1, FC7h; 2, F73h)

| R/W-1 | R/W-1              | R-1 | R-1 | R-1 | R-1 | R-1 | R-1   |

|-------|--------------------|-----|-----|-----|-----|-----|-------|

| SMP   | CKE <sup>(1)</sup> | D/Ā | Р   | S   | R/W | UA  | BF    |

| bit 7 |                    |     |     |     |     |     | bit 0 |

Legend:

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | SMP: Sample bit                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------|

|       | SPI Master mode:                                                                                            |

|       | 1 = Input data sampled at the end of data output time                                                       |

|       | 0 = Input data sampled at the middle of data output time                                                    |

|       | SPI Slave mode:                                                                                             |

|       | SMP must be cleared when SPI is used in Slave mode.                                                         |

| bit 6 | CKE: SPI Clock Select bit <sup>(1)</sup>                                                                    |

|       | 1 = Transmit occurs on transition from active to Idle clock state                                           |

|       | 0 = Transmit occurs on transition from Idle to active clock state                                           |

| bit 5 | D/A: Data/Address bit                                                                                       |

|       | Used in I <sup>2</sup> C mode only.                                                                         |

| bit 4 | P: Stop bit                                                                                                 |

|       | Used in I <sup>2</sup> C mode only; this bit is cleared when the MSSP module is disabled, SSPEN is cleared. |

| bit 3 | S: Start bit                                                                                                |

|       | Used in I <sup>2</sup> C mode only.                                                                         |

| bit 2 | R/W: Read/Write Information bit                                                                             |

|       | Used in I <sup>2</sup> C mode only.                                                                         |

| bit 1 | UA: Update Address bit                                                                                      |

|       | Used in I <sup>2</sup> C mode only.                                                                         |

| bit 0 | BF: Buffer Full Status bit                                                                                  |

|       | 1 = Receive complete, SSPxBUF is full                                                                       |

|       | 0 = Receive not complete, SSPxBUF is empty                                                                  |

|       |                                                                                                             |

Note 1: Polarity of the clock state is set by the CKP bit (SSPxCON1<4>).

## REGISTER 20-2: SSPxCON1: MSSPx CONTROL REGISTER 1 (SPI MODE) (1, ACCESS FC6h; 2, F72h)

|            |                                                                                              |                                        | -                                                                                                |                                                                                  |                       |                      |                      |

|------------|----------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------|----------------------|----------------------|

| R/W-0      | R/C-0                                                                                        | R/W-0                                  | R/W-0                                                                                            | R/W-0                                                                            | R/W-0                 | R/W-0                | R/W-0                |

| WCOL       | SSPOV <sup>(1)</sup>                                                                         | SSPEN <sup>(2)</sup>                   | CKP                                                                                              | SSPM3 <sup>(3)</sup>                                                             | SSPM2 <sup>(3)</sup>  | SSPM1 <sup>(3)</sup> | SSPM0 <sup>(3)</sup> |

| bit 7      |                                                                                              |                                        |                                                                                                  |                                                                                  |                       |                      | bit 0                |

|            |                                                                                              | 0 01 11                                | 1.14                                                                                             |                                                                                  |                       |                      |                      |

| Legend:    |                                                                                              | C = Clearable                          |                                                                                                  |                                                                                  |                       |                      |                      |

| R = Reada  |                                                                                              | W = Writable                           |                                                                                                  | -                                                                                | nented bit, read      |                      |                      |

| -n = Value | at POR                                                                                       | '1' = Bit is set                       |                                                                                                  | '0' = Bit is clea                                                                | ared                  | x = Bit is unkr      | nown                 |

| bit 7      | 1 = The SSP                                                                                  | •                                      |                                                                                                  | e it is still transm                                                             | nitting the previ     | ous word (mus        | t be cleared in      |

|            | software)<br>0 = No collisi                                                                  | /                                      |                                                                                                  |                                                                                  |                       |                      |                      |

| bit 6      |                                                                                              | eive Overflow I                        | ndicator hit(1)                                                                                  |                                                                                  |                       |                      |                      |

| bit 0      | SPI Slave mo                                                                                 |                                        |                                                                                                  |                                                                                  |                       |                      |                      |

|            | flow, the                                                                                    | data in SSPxS<br>F, even if only tr    | R is lost. Over                                                                                  | BUF register is s<br>flow can only or<br>a, to avoid settir                      | ccur in Slave n       | node. The user       | must read the        |

| bit 5      |                                                                                              | ter Synchronou                         | s Serial Port F                                                                                  | nable bit <sup>(2)</sup>                                                         |                       |                      |                      |

|            | 1 = Enables s                                                                                | serial port and o                      | onfigures SCI                                                                                    | <pre><x, as="" i="" o="" p<="" pins="" pre="" sdix="" sdox,="" se=""></x,></pre> |                       | erial port pins      |                      |

| bit 4      |                                                                                              | Polarity Select b                      |                                                                                                  |                                                                                  | -                     |                      |                      |

|            | 1 = Idle state                                                                               | for clock is a hi<br>for clock is a lo | igh level                                                                                        |                                                                                  |                       |                      |                      |

| bit 3-0    | SSPM<3:0>:                                                                                   | Master Synchr                          | onous Serial F                                                                                   | Port Mode Selec                                                                  | t bits <sup>(3)</sup> |                      |                      |

|            | 0101 = SPI S<br>0100 = SPI S<br>0011 = SPI N<br>0010 = SPI N<br>0001 = SPI N<br>1010 = SPI N | Slave mode, clo                        | ck = SCKx pin<br>ck = SCKx pin<br>ock = TMR2 o<br>ock = Fosc/64<br>ock = Fosc/16<br>ock = Fosc/8 | ; <u>SSx</u> pin contro<br>; SSx pin contro<br>utput/2                           | ol disabled, SS       | x can be used        | as I/O pin           |

|            | In Master mode, t<br>writing to the SSF                                                      |                                        |                                                                                                  | e each new rec                                                                   | eption (and tra       | insmission) is ir    | nitiated by          |

- 2: When enabled, this pin must be properly configured as input or output.

- 3: Bit combinations not specifically listed here are either reserved or implemented in I<sup>2</sup>C mode only.

## 20.4 SPI DMA MODULE

The SPI DMA module contains control logic to allow the MSSP2 module to perform SPI direct memory access transfers. This enables the module to quickly transmit or receive large amounts of data with relatively little CPU intervention. When the SPI DMA module is used, MSSP2 can directly read and write to general purpose SRAM. When the SPI DMA module is not enabled, MSSP2 functions normally, but without DMA capability.

The SPI DMA module is composed of control logic, a Destination Receive Address Pointer, a Transmit Source Address Pointer, an interrupt manager and a Byte Count register for setting the size of each DMA transfer. The DMA module may be used with all SPI Master and Slave modes, and supports both half-duplex and full-duplex transfers.

## 20.4.1 I/O PIN CONSIDERATIONS

When enabled, the SPI DMA module uses the MSSP2 module. All SPI input and output signals, related to MSSP2, are routed through the Peripheral Pin Select module. The appropriate initialization procedure, as described in **Section 20.4.6** "**Using the SPI DMA Module**", will need to be followed prior to using the SPI DMA module. The output pins assigned to the SDO2 and SCK2 functions can optionally be configured as open-drain outputs, such as for level shifting operations mentioned in the same section.

## 20.4.2 RAM TO RAM COPY OPERATIONS

Although the SPI DMA module is primarily intended to be used for SPI communication purposes, the module can also be used to perform RAM to RAM copy operations. To do this, configure the module for Full-Duplex Master mode operation, but assign the SDO2 output and SDI2 input functions onto the same RPn pin in the PPS module. Also assign SCK2 out and SCK2 in onto the same RPn pin (a different pin than used for SDO2 and SDI2). This will allow the module to operate in Loopback mode, providing RAM copy capability.

## 20.4.3 IDLE AND SLEEP CONSIDERATIONS

The SPI DMA module remains fully functional when the microcontroller is in Idle mode.

During normal Sleep, the SPI DMA module is not functional and should not be used. To avoid corrupting a transfer, user firmware should be careful to make certain that pending DMA operations are complete by polling the DMAEN bit in the DMACON1 register prior to putting the microcontroller into Sleep.

In SPI Slave modes, the MSSP2 module is capable of transmitting and/or receiving one byte of data while in Sleep mode. This allows the SSP2IF flag in the PIR3 register to be used as a wake-up source. When the DMAEN bit is cleared, the SPI DMA module is effectively disabled, and the MSSP2 module functions normally, but without DMA capabilities. If the DMAEN bit is clear prior to entering Sleep, it is still possible to use the SSP2IF as a wake-up source without any data loss.

Neither MSSP2 nor the SPI DMA module will provide any functionality in Deep Sleep. Upon exiting from Deep Sleep, all of the I/O pins, MSSP2 and SPI DMA related registers will need to be fully re-initialized before the SPI DMA module can be used again.

## 20.4.4 REGISTERS

The SPI DMA engine is enabled and controlled by the following Special Function Registers:

- DMACON1

DMACON2

- TXADDRH TXADDRL

- RXADDRH

RXADDRL

- DMABCH DMABCL

© 2010-2017 Microchip Technology Inc.

## 20.5.4 CLOCK STRETCHING

Both 7-Bit and 10-Bit Slave modes implement automatic clock stretching during a transmit sequence.

The SEN bit (SSPxCON2<0>) allows clock stretching to be enabled during receives. Setting SEN will cause the SCLx pin to be held low at the end of each data receive sequence.

#### 20.5.4.1 Clock Stretching for 7-Bit Slave Receive Mode (SEN = 1)

In 7-Bit Slave Receive mode, <u>on the falling edge of the</u> ninth clock at the end of the ACK sequence, if the BF bit is set, the CKP bit in the SSPxCON1 register is automatically cleared, forcing the SCLx output to be held low. The CKP bit being cleared to '0' will assert the SCLx line low. The CKP bit must be set in the user's ISR before reception is allowed to continue. By holding the SCLx line low, the user has time to service the ISR and read the contents of the SSPxBUF before the master device can initiate another receive sequence. This will prevent buffer overruns from occurring (see Figure 20-15).

- Note 1: If the user reads the contents of the SSPxBUF before the falling edge of the ninth clock, thus clearing the BF bit, the CKP bit will not be cleared and clock stretching will not occur.

- 2: The CKP bit can be set in software regardless of the state of the BF bit. The user should be careful to clear the BF bit in the ISR before the next receive sequence in order to prevent an overflow condition.

## 20.5.4.2 Clock Stretching for 10-Bit Slave Receive Mode (SEN = 1)

In 10-Bit Slave Receive mode, during the address sequence, clock stretching automatically takes place but CKP is not cleared. During this time, if the UA bit is set after the ninth clock, clock stretching is initiated. The UA bit is set after receiving the upper byte of the 10-bit address and following the receive of the second byte of the 10-bit address with the R/W bit cleared to '0'. The release of the clock line occurs upon updating SSPxADD. Clock stretching will occur on each data receive sequence, as described in 7-bit mode.

**Note:** If the user polls the UA bit and clears it by updating the SSPxADD register before the falling edge of the ninth clock occurs, and if the user has not cleared the BF bit by reading the SSPxBUF register before that time, then the CKP bit will still NOT be asserted low. Clock stretching on the basis of the state of the BF bit only occurs during a data sequence, not an address sequence.

### 20.5.4.3 Clock Stretching for 7-Bit Slave Transmit Mode

The 7-Bit Slave Transmit mode implements clock stretching by clearing the CKP bit, after the falling edge of the ninth clock, if the BF bit is clear. This occurs regardless of the state of the SEN bit.

The user's Interrupt Service Routine (ISR) must set the CKP bit before transmission is allowed to continue. By holding the SCLx line low, the user has time to service the ISR and load the contents of the SSPxBUF before the master device can initiate another transmit sequence (see Figure 20-10).

- Note 1: If the user loads the contents of SSPxBUF, setting the BF bit before the falling edge of the ninth clock, the CKP bit will not be cleared and clock stretching will not occur.

- **2:** The CKP bit can be set in software regardless of the state of the BF bit.

#### 20.5.4.4 Clock Stretching for 10-Bit Slave Transmit Mode

In 10-Bit Slave Transmit mode, clock stretching is controlled during the first two address sequences by the state of the UA bit, just as it is in 10-Bit Slave Receive mode. The first two addresses are followed by a third address sequence, which contains the high-order bits of the 10-bit address and the R/W bit set to '1'. After the third address sequence is performed, the UA bit is not set, the module is now configured in Transmit mode and clock stretching is controlled by the BF flag as in 7-Bit Slave Transmit mode (see Figure 20-13).

## 21.1 Baud Rate Generator (BRG)

The BRG is a dedicated, 8-bit or 16-bit generator that supports both the Asynchronous and Synchronous modes of the EUSART. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit (BAUDCONx<3>) selects 16-bit mode.

The SPBRGHx:SPBRGx register pair controls the period of a free-running timer. In Asynchronous mode, the BRGH (TXSTAx<2>) and BRG16 (BAUDCONx<3>) bits also control the baud rate. In Synchronous mode, BRGH is ignored.

Table 21-1 provides the formula for computation of the baud rate for different EUSART modes, which only apply in Master mode (internally generated clock).

Given the desired baud rate and Fosc, the nearest integer value for the SPBRGHx:SPBRGx registers can be calculated using the formulas in Table 21-1. From this, the error in baud rate can be determined. An example calculation is provided in Example 21-1. Typical baud rates and error values for the various Asynchronous modes are provided in Table 21-2. It may be advantageous to use the high baud rate (BRGH = 1) or the 16-bit BRG to reduce the baud rate error, or achieve a slow baud rate for a fast oscillator frequency.

Writing a new value to the SPBRGHx:SPBRGx registers causes the BRG timer to be reset (or cleared). This ensures the BRG does not wait for a timer overflow before outputting the new baud rate.

When operated in the Synchronous mode, SPBRGH:SPBRG values of 0000h and 0001h are not supported. In the Asynchronous mode, all BRG values may be used.

#### 21.1.1 OPERATION IN POWER-MANAGED MODES

The device clock is used to generate the desired baud rate. When one of the power-managed modes is entered, the new clock source may be operating at a different frequency. This may require an adjustment to the value in the SPBRGx register pair.

#### 21.1.2 SAMPLING

The data on the RXx pin (either RC7/CCP10/PMA4/ RX1/DT1/RP18 or RPn/RX2/DT2) is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RXx pin.

| <b>TABLE 21-1</b> : | BAUD RATE FORMULAS |

|---------------------|--------------------|

| TABLE 21-4:         |                    |

| Configuration Bits |       |      | BRG/EUSART Mode     | Baud Rate Formula  |  |  |

|--------------------|-------|------|---------------------|--------------------|--|--|

| SYNC               | BRG16 | BRGH | BRG/EUSART MODE     | Dauu Kale Formula  |  |  |

| 0                  | 0     | 0    | 8-bit/Asynchronous  | Fosc/[64 (n + 1)]  |  |  |

| 0                  | 0     | 1    | 8-bit/Asynchronous  | Fosc/[16 (n + 1)]  |  |  |

| 0                  | 1     | 0    | 16-bit/Asynchronous | POSC/[10 (II + 1)] |  |  |

| 0                  | 1     | 1    | 16-bit/Asynchronous |                    |  |  |

| 1                  | 0     | Х    | 8-bit/Synchronous   | Fosc/[4 (n + 1)]   |  |  |

| 1                  | 1     | Х    | 16-bit/Synchronous  |                    |  |  |

**Legend:** x = Don't care, n = value of SPBRGHx:SPBRGx register pair

## 26.4 Measuring Capacitance with the CTMU

There are two separate methods of measuring capacitance with the CTMU. The first is the absolute method, in which the actual capacitance value is desired. The second is the relative method, in which the actual capacitance is not needed, rather an indication of a change in capacitance is required.

#### 26.4.1 ABSOLUTE CAPACITANCE MEASUREMENT

For absolute capacitance measurements, both the current and capacitance calibration steps found in **Section 26.3 "Calibrating the CTMU Module"** should be followed. Capacitance measurements are then performed using the following steps:

- 1. Initialize the A/D Converter.

- 2. Initialize the CTMU.

- 3. Set EDG1STAT.

- 4. Wait for a fixed delay, *T*.

- 5. Clear EDG1STAT.

- 6. Perform an A/D conversion.

- 7. Calculate the total capacitance, CTOTAL = (I \* T)/V, where *I* is known from the current source measurement step (see **Section 26.3.1 "Current Source Calibration"**), *T* is a fixed delay and *V* is measured by performing an A/D conversion.

- 8. Subtract the stray and A/D capacitance (*C*OFFSET from **Section 26.3.2** "**Capacitance Calibration**") from *CTOTAL* to determine the measured capacitance.

#### 26.4.2 CAPACITIVE TOUCH SENSE USING RELATIVE CHARGE MEASUREMENT

An application may not require precise capacitance measurements. For example, when detecting a valid press of a capacitance-based touch sense button, detecting a relative change of capacitance is of interest. In this type of application, when the touch sense pad is not being pressed, the total capacitance is the capacitance of the combination of the board traces, the A/D Converter, etc. A larger voltage will be measured by the A/D Converter. When the touch sense pad is pressed, the total capacitance is larger due to the addition of the capacitance of the human body, therefore, a smaller voltage will be measured by the A/D Converter.

Detecting capacitance changes is easily accomplished with the CTMU using these steps:

- 1. Initialize the A/D Converter and the CTMU.

- 2. Set EDG1STAT.

- 3. Wait for a fixed delay.

- 4. Clear EDG1STAT.

- 5. Perform an A/D conversion.

The voltage measured by performing the A/D conversion is an indication of the relative capacitance. Note that in this case, no calibration of the current source or circuit capacitance measurement is needed. See Example 26-4 for a sample software routine for a capacitive touch switch.

#### REGISTER 27-4: CONFIG2H: CONFIGURATION REGISTER 2 HIGH (BYTE ADDRESS 300003h)

| U-1   | U-1 | U-1 | U-1 | R/WO-1 | R/WO-1 | R/WO-1 | R/WO-1 |

|-------|-----|-----|-----|--------|--------|--------|--------|

| —     | —   | —   | —   | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 |

| bit 7 |     |     |     |        |        |        | bit 0  |

| Legend:                              |                  |                                    |                    |  |

|--------------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit WO = Write-Once bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                    | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 7-4 | <b>Unimplemented:</b> Program the corresponding Flash Configuration bit to '1' |  |

|---------|--------------------------------------------------------------------------------|--|

|         |                                                                                |  |

| bit 3-0 | WDTPS<3:0>: Watchdog Timer Postscale Select bits |

|---------|--------------------------------------------------|

|         | 1111 <b>= 1:32,768</b>                           |

|      | ,          |

|------|------------|

| 1110 | = 1:16,384 |

| 1101 | = 1:8,192  |

| 1100 | = 1:4,096  |

| 1011 | = 1:2,048  |

| 1010 | = 1:1,024  |

| 1001 | = 1:512    |

| 1000 | = 1:256    |

| 0111 | = 1:128    |

| 0110 | = 1:64     |

| 0101 | = 1:32     |

| 0100 | = 1:16     |

| 0011 | = 1:8      |

| 0010 | = 1:4      |

| 0001 | = 1:2      |

| 0000 | = 1:1      |

|      |            |

# PIC18F47J13 FAMILY

| BCF               | Bit Clear f                                                                                                                     | BN                                                                                                                                                       | Branch if Negative                                                                                                                                    |  |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:           | BCF f, b {,a}                                                                                                                   | Syntax:                                                                                                                                                  | BN n                                                                                                                                                  |  |  |  |  |  |  |

| Operands:         | $0 \leq f \leq 255$                                                                                                             | Operands:                                                                                                                                                | $-128 \le n \le 127$                                                                                                                                  |  |  |  |  |  |  |

|                   | $\begin{array}{l} 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$                                                                   | Operation:                                                                                                                                               | if Negative bit is '1',<br>(PC) + 2 + 2n $\rightarrow$ PC                                                                                             |  |  |  |  |  |  |

| Operation:        | $0 \rightarrow f \le b >$                                                                                                       | Status Affected:                                                                                                                                         | None                                                                                                                                                  |  |  |  |  |  |  |

| Status Affected:  | None                                                                                                                            | Encoding:                                                                                                                                                | 1110 0110 nnnn nnnn                                                                                                                                   |  |  |  |  |  |  |

| Encoding:         | 1001 bbba ffff ffff                                                                                                             | Description:                                                                                                                                             | If the Negative bit is '1', then the                                                                                                                  |  |  |  |  |  |  |

| Description:      | Bit 'b' in register 'f' is cleared.                                                                                             | ·                                                                                                                                                        | program will branch.                                                                                                                                  |  |  |  |  |  |  |

|                   | If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank (default).              |                                                                                                                                                          | The 2's complement number '2n' is<br>added to the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be |  |  |  |  |  |  |

|                   | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing |                                                                                                                                                          | PC + 2 + 2n. This instruction is then a $2$ -cycle instruction.                                                                                       |  |  |  |  |  |  |

|                   | mode whenever $f \le 95$ (5Fh). See                                                                                             | Words:                                                                                                                                                   | 1                                                                                                                                                     |  |  |  |  |  |  |

|                   | Section 28.2.3 "Byte-Oriented and                                                                                               | Cycles:                                                                                                                                                  | 1(2)                                                                                                                                                  |  |  |  |  |  |  |

|                   | Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details.                                                       | Q Cycle Activity:<br>If Jump:                                                                                                                            | .,                                                                                                                                                    |  |  |  |  |  |  |

| Words:            | 1                                                                                                                               | Q1                                                                                                                                                       | Q2 Q3 Q4                                                                                                                                              |  |  |  |  |  |  |

| Cycles:           | 1                                                                                                                               | Decode                                                                                                                                                   | Read literal Process Write to                                                                                                                         |  |  |  |  |  |  |

| Q Cycle Activity: |                                                                                                                                 |                                                                                                                                                          | 'n' Data PC                                                                                                                                           |  |  |  |  |  |  |

| Q1                | Q2 Q3 Q4                                                                                                                        | No<br>operation                                                                                                                                          | No No No operation operation                                                                                                                          |  |  |  |  |  |  |

| Decode            | ReadProcessWriteregister 'f'Dataregister 'f'                                                                                    | If No Jump:                                                                                                                                              |                                                                                                                                                       |  |  |  |  |  |  |

|                   |                                                                                                                                 | Q1                                                                                                                                                       | Q2 Q3 Q4                                                                                                                                              |  |  |  |  |  |  |

| Example:          | BCF FLAG REG, 7, 0                                                                                                              | Decode                                                                                                                                                   | Read literal Process No                                                                                                                               |  |  |  |  |  |  |

| Before Instruc    | tion                                                                                                                            |                                                                                                                                                          | 'n' Data operation                                                                                                                                    |  |  |  |  |  |  |

| FLAG_RI           | EG = C7h                                                                                                                        |                                                                                                                                                          |                                                                                                                                                       |  |  |  |  |  |  |

| After Instructio  |                                                                                                                                 | Example:                                                                                                                                                 | HERE BN Jump                                                                                                                                          |  |  |  |  |  |  |

| FLAG_RI           | EG = 47h                                                                                                                        | Before Instruction<br>PC = address (HERE)<br>After Instruction<br>If Negative = 1;<br>PC = address (Jump)<br>If Negative = 0;<br>PC = address (HERE + 2) |                                                                                                                                                       |  |  |  |  |  |  |

|                   |                                                                                                                                 |                                                                                                                                                          |                                                                                                                                                       |  |  |  |  |  |  |

# PIC18F47J13 FAMILY

| POP                                     | ,               | Рор Тор о                                                               | Pop Top of Return Stack                                                                                                                                                                                                                                                                    |                 |     |               |  |  |

|-----------------------------------------|-----------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|---------------|--|--|

| Syntax:                                 |                 | POP                                                                     | POP                                                                                                                                                                                                                                                                                        |                 |     |               |  |  |

| Oper                                    | rands:          | None                                                                    |                                                                                                                                                                                                                                                                                            |                 |     |               |  |  |

| Oper                                    | ration:         | $(TOS) \rightarrow b$                                                   | it bucke                                                                                                                                                                                                                                                                                   | et              |     |               |  |  |

| Statu                                   | us Affected:    | None                                                                    |                                                                                                                                                                                                                                                                                            |                 |     |               |  |  |

| Enco                                    | oding:          | 0000                                                                    | 0000                                                                                                                                                                                                                                                                                       | 000             | 0 ( | 0110          |  |  |

| Desc                                    | cription:       | stack and is<br>then becon<br>was pushed<br>This instruc<br>the user to | The TOS value is pulled off the return<br>stack and is discarded. The TOS value<br>then becomes the previous value that<br>was pushed onto the return stack.<br>This instruction is provided to enable<br>the user to properly manage the return<br>stack to incorporate a software stack. |                 |     |               |  |  |

| Word                                    | ds:             | 1                                                                       |                                                                                                                                                                                                                                                                                            |                 |     |               |  |  |

| Cycle                                   | es:             | 1                                                                       |                                                                                                                                                                                                                                                                                            |                 |     |               |  |  |

| QC                                      | cycle Activity: |                                                                         |                                                                                                                                                                                                                                                                                            |                 |     |               |  |  |

|                                         | Q1              | Q2                                                                      | (                                                                                                                                                                                                                                                                                          | 23              | -   | Q4            |  |  |

|                                         | Decode          | No<br>operation                                                         |                                                                                                                                                                                                                                                                                            | TOS<br>lue      | ор  | No<br>eration |  |  |

| <u>Exar</u>                             | <u>nple:</u>    | POP<br>GOTO                                                             | NEW                                                                                                                                                                                                                                                                                        |                 |     |               |  |  |

| Before Instructio<br>TOS<br>Stack (1 le |                 | tion<br>level down)                                                     | =<br>=                                                                                                                                                                                                                                                                                     | 0031A<br>014332 |     |               |  |  |

| After Instruction<br>TOS<br>PC          |                 | n                                                                       | =<br>=                                                                                                                                                                                                                                                                                     | 014332<br>NEW   | 2h  |               |  |  |

| PUS     | н                                         | Push Top o                                                                                | Push Top of Return Stack               |                                            |                               |                                     |  |  |  |

|---------|-------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------------|-------------------------------|-------------------------------------|--|--|--|

| Syntax: |                                           | PUSH                                                                                      | PUSH                                   |                                            |                               |                                     |  |  |  |

| Oper    | ands:                                     | None                                                                                      | None                                   |                                            |                               |                                     |  |  |  |

| Oper    | ation:                                    | $(PC + 2) \rightarrow$                                                                    | TOS                                    |                                            |                               |                                     |  |  |  |

| Statu   | s Affected:                               | None                                                                                      | None                                   |                                            |                               |                                     |  |  |  |

| Enco    | ding:                                     | 0000                                                                                      | 0000                                   | 000                                        | 0                             | 0101                                |  |  |  |

| Desc    | ription:                                  | The PC + 2<br>the return s<br>value is pus<br>This instruc<br>software sta<br>then pushin | tack. ⊺<br>shed d<br>tion al<br>ack by | The prev<br>own on<br>lows imp<br>modifyir | ious<br>the s<br>blem<br>ng T | TOS<br>stack.<br>enting a<br>OS and |  |  |  |

| Word    | ls:                                       | 1                                                                                         | 1                                      |                                            |                               |                                     |  |  |  |

| Cycle   | es:                                       | 1                                                                                         | 1                                      |                                            |                               |                                     |  |  |  |