Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

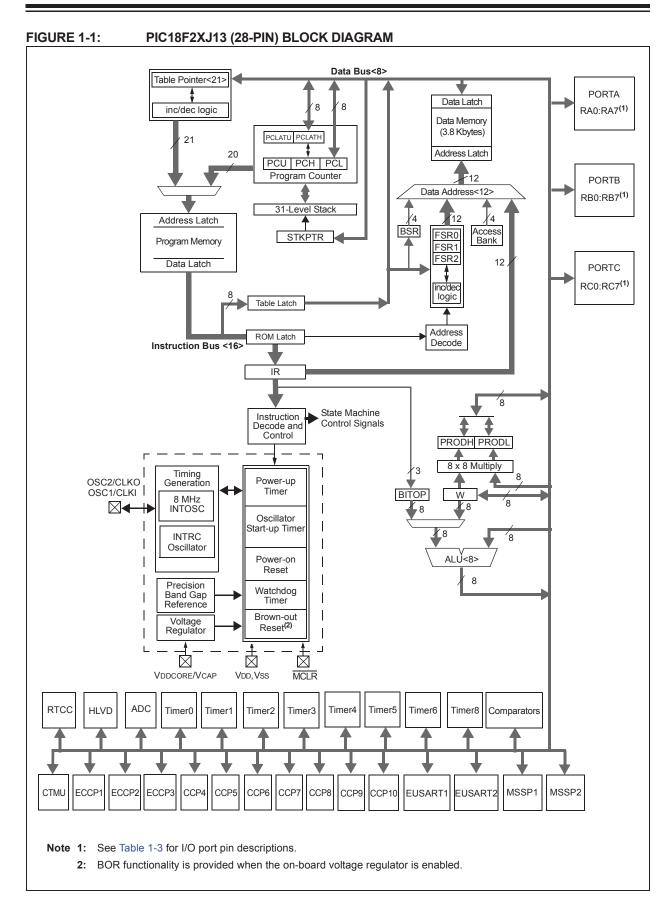

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 014110                   |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 48MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 34                                                                           |

| Program Memory Size        | 128KB (64K x 16)                                                             |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 3.8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 2.75V                                                                   |

| Data Converters            | A/D 13x10b/12b                                                               |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

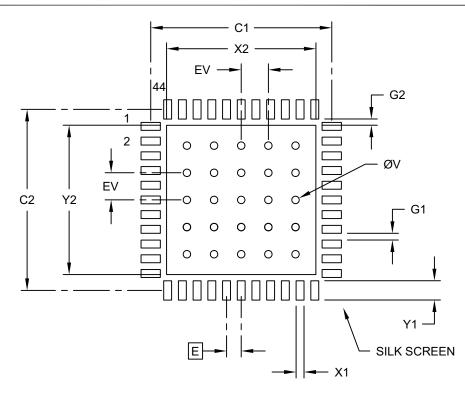

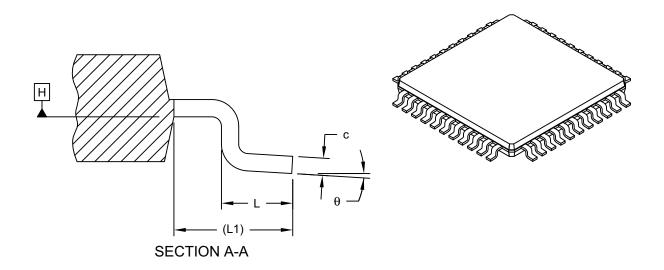

| Package / Case             | 44-TQFP                                                                      |

| Supplier Device Package    | 44-TQFP (10x10)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf47j13t-i-pt |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 1.0   | Device Overview                                                           | 9     |

|-------|---------------------------------------------------------------------------|-------|

| 2.0   | Guidelines for Getting Started with PIC18FJ Microcontrollers              | 28    |

| 3.0   | Oscillator Configurations                                                 | 32    |

| 4.0   | Low-Power Modes                                                           | 43    |

| 5.0   | Reset                                                                     | 60    |

| 6.0   | Memory Organization                                                       | 75    |

| 7.0   | Flash Program Memory                                                      | . 101 |

| 8.0   | 8 x 8 Hardware Multiplier                                                 | . 111 |

| 9.0   | Interrupts                                                                | . 113 |

| 10.0  | I/O Ports                                                                 | . 133 |

| 11.0  | Parallel Master Port (PMP)                                                | . 173 |

| 12.0  | Timer0 Module                                                             | . 198 |

| 13.0  | Timer1 Module                                                             | . 202 |

| 14.0  | Timer2 Module                                                             | . 212 |

| 15.0  | Timer3/5 Module                                                           | . 214 |

| 16.0  | Timer4/6/8 Module                                                         | . 226 |

| 17.0  | Real-Time Clock and Calendar (RTCC)                                       | . 229 |

| 18.0  | Capture/Compare/PWM (CCP) Modules                                         | . 248 |

| 19.0  | Enhanced Capture/Compare/PWM (ECCP) Module                                | . 260 |

| 20.0  | Master Synchronous Serial Port (MSSP) Module                              |       |

| 21.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) | . 336 |

| 22.0  | 10/12-Bit Analog-to-Digital Converter (A/D) Module                        | . 358 |

| 23.0  | Comparator Module                                                         |       |

| 24.0  | Comparator Voltage Reference Module                                       |       |

| 25.0  | High/Low Voltage Detect (HLVD)                                            | . 380 |

| 26.0  | Charge Time Measurement Unit (CTMU)                                       |       |

| 27.0  | Special Features of the CPU                                               | . 403 |

| 28.0  | Instruction Set Summary                                                   | . 420 |

| 29.0  | Development Support                                                       | . 470 |

| 30.0  | Electrical Characteristics                                                |       |

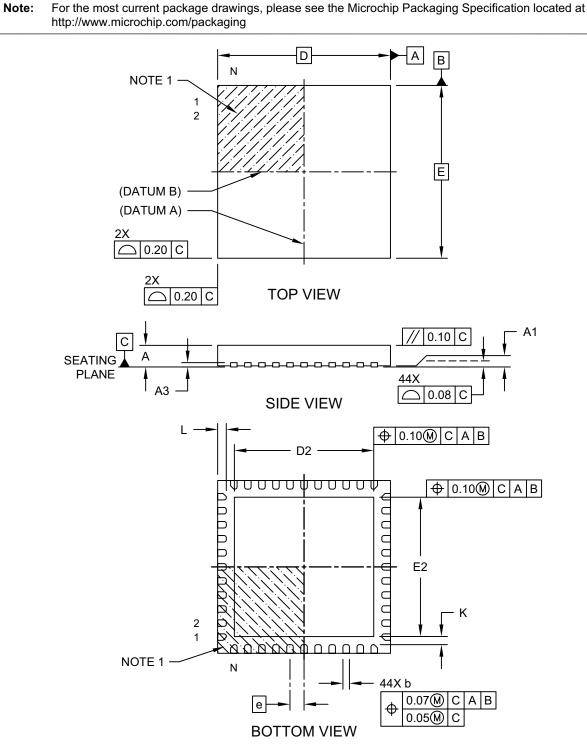

| 31.0  | Packaging Information                                                     | . 516 |

|       | ndix A: Revision History                                                  |       |

| Appe  | ndix B: Migration From PIC18F46J11 to PIC18F47J13                         | . 534 |

|       | /icrochip Website                                                         |       |

|       | mer Change Notification Service                                           |       |

|       | mer Support                                                               |       |

| Produ | uct Identification System                                                 | . 536 |

| <b>TABLE 1-3</b> : | PIC18F2XJ | PIC18F2XJ13 PINOUT I/O DESCRIPTIONS (CONTINUED) |  |  |  |  |  |  |  |  |

|--------------------|-----------|-------------------------------------------------|--|--|--|--|--|--|--|--|

|                    |           | Pin Number                                      |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Pin Nu                     | ımber             |                           |                                                |                                                                                                                                                                                          |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------|---------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28-SPDIP/<br>SSOP/<br>SOIC | 28-QFN            | Pin<br>Type               | Buffer<br>Type                                 | Description                                                                                                                                                                              |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |                   |                           |                                                | PORTC is a bidirectional I/O port.                                                                                                                                                       |  |  |

| RC0/T1OSO/T1CKI/RP11<br>RC0<br>T1OSO<br>T1CKI<br>RP11                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11                         | 8                 | I/O<br>O<br>I<br>I/O      | ST/DIG<br>Analog<br>ST<br>ST/DIG               | Digital I/O.<br>Timer1 oscillator output.<br>Timer1 external digital clock input.<br>Remappable Peripheral Pin 11 input/output.                                                          |  |  |

| RC1/CCP8/T1OSI/RP12<br>RC1<br>CCP8<br>T1OSI<br>RP12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12                         | 9                 | I/O<br>I/O<br>I<br>I/O    | ST/DIG<br>ST/DIG<br>Analog<br>ST/DIG           | Digital I/O.<br>Capture/Compare/PWM input/output.<br>Timer1 oscillator input.<br>Remappable Peripheral Pin 12 input/output.                                                              |  |  |

| RC2/AN11/C2IND/CTPLS/RP13<br>RC2<br>AN11<br>C2IND<br>CTPLS<br>RP13                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 13                         | 10                | I/O<br>I<br>I<br>O<br>I/O | ST/DIG<br>Analog<br>Analog<br>DIG<br>ST/DIG    | Digital I/O.<br>Analog Input 11.<br>Comparator 2 Input D.<br>CTMU pulse generator output.<br>Remappable Peripheral Pin 13 input/output.                                                  |  |  |

| RC3/SCK1/SCL1/RP14<br>RC3<br>SCK1<br>SCL1<br>RP14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 14                         | 11                | I/O<br>I/O<br>I/O<br>I/O  | ST/DIG<br>ST/DIG<br>I <sup>2</sup> C<br>ST/DIG | Digital I/O.<br>SPI clock input/output.<br>I <sup>2</sup> C clock input/output.<br>Remappable Peripheral Pin 14 input/output.                                                            |  |  |

| RC4/SDI1/SDA1/RP15<br>RC4<br>SDI1<br>SDA1<br>RP15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                         | 12                | I/O<br>I<br>I/O<br>I/O    | ST/DIG<br>ST<br>I <sup>2</sup> C<br>ST/DIG     | Digital I/O.<br>SPI data input.<br>I <sup>2</sup> C data input/output.<br>Remappable Peripheral Pin 15 input/output.                                                                     |  |  |

| RC5/SDO1/RP16<br>RC5<br>SDO1<br>RP16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 16                         | 13                | I/O<br>O<br>I/O           | ST/DIG<br>DIG<br>ST/DIG                        | Digital I/O.<br>SPI data output.<br>Remappable Peripheral Pin 16 input/output.                                                                                                           |  |  |

| RC6/CCP9/TX1/CK1/RP17<br>RC6<br>CCP9<br>TX1<br>CK1<br>RP17                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17 <sup>(2)</sup>          | 14(2)             | I/O<br>I/O<br>I/O<br>I/O  | ST/DIG<br>ST/DIG<br>DIG<br>ST/DIG<br>ST/DIG    | Digital I/O.<br>Capture/Compare/PWM input/output.<br>EUSART1 asynchronous transmit.<br>EUSART1 synchronous clock (see related<br>RX1/DT1).<br>Remappable Peripheral Pin 17 input/output. |  |  |

| RC7/CCP10/RX1/DT1/RP18<br>RC7<br>CCP10<br>RX1<br>DT1<br>RP18                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18 <sup>(2)</sup>          | 15 <sup>(2)</sup> | I/O<br>I/O<br>I<br>I/O    | ST/DIG<br>ST/DIG<br>ST<br>ST/DIG<br>ST/DIG     | Digital I/O.<br>Capture/Compare/PWM input/output.<br>Asynchronous serial receive data input.<br>Synchronous serial data output/input.<br>Remannable Perinberal Pin 18 input/output       |  |  |

| RP18   I/O   ST/DIG   Remappable Peripheral Pin 18 input/output.     Legend:   TTL = TTL compatible input<br>ST = Schmitt Trigger input with CMOS levels<br>I = Input<br>P = Power<br>DIG = Digital output   CMOS   = CMOS compatible input or output     0   = Output<br>OD   = Output<br>OD   = Output<br>OD   = Open-Drain (no P diode to VDD)<br>I <sup>2</sup> C   = Open-Drain, I <sup>2</sup> C specific     Note 1:   RA7 and RA6 will be disabled if OSC1 and OSC2 are used for the clock function.   2:   5.5V tolerant. |                            |                   |                           |                                                |                                                                                                                                                                                          |  |  |

2: 5.5V tolerant.

## 4.2.3 RC\_RUN MODE

In RC\_RUN mode, the CPU and peripherals are clocked from the internal oscillator; the primary clock is shut down. This mode provides the best power conservation of all the Run modes while still executing code. It works well for user applications, which are not highly timing-sensitive or do not require high-speed clocks at all times.

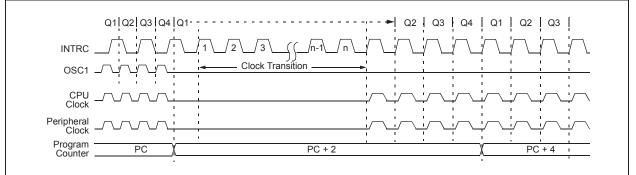

This mode is entered by setting the SCS<1:0> bits (OSCCON<1:0>) to '11'. When the clock source is switched to the internal oscillator block (see Figure 4-3), the primary oscillator is shut down and the OSTS bit is cleared.

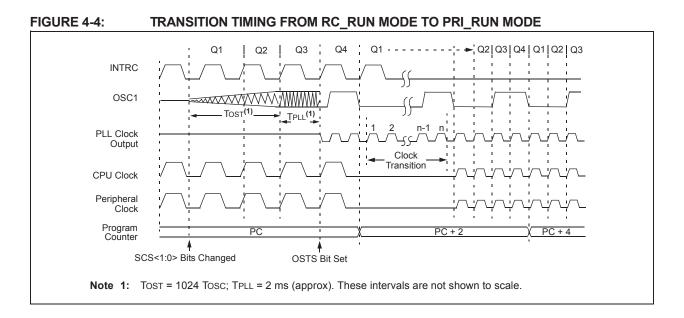

On transitions from RC\_RUN mode to PRI\_RUN mode, the device continues to be clocked from the INTOSC block while the primary clock is started. When the primary clock becomes ready, a clock switch to the primary clock occurs (see Figure 4-4). When the clock switch is complete, the OSTS bit is set and the primary clock is providing the device clock. The IDLEN and SCS bits are not affected by the switch. The INTRC clock source will continue to run if either the WDT or the FSCM is enabled.

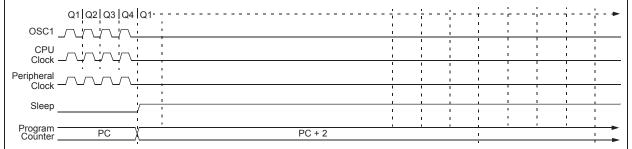

## FIGURE 4-3: TRANSITION TIMING TO RC\_RUN MODE

# 4.3 Sleep Mode

The power-managed Sleep mode is identical to the legacy Sleep mode offered in all other PIC devices. It is entered by clearing the IDLEN bit (the default state on device Reset) and executing the SLEEP instruction. This shuts down the selected oscillator (Figure 4-5). All clock source status bits are cleared.

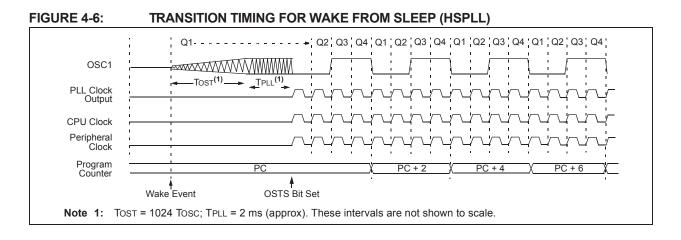

Entering the Sleep mode from any other mode does not require a clock switch. This is because no clocks are needed once the controller has entered Sleep mode. If the WDT is selected, the INTRC source will continue to operate. If the Timer1 oscillator is enabled, it will also continue to run. When a wake event occurs in Sleep mode (by interrupt, Reset or WDT time-out), the device will not be clocked until the clock source selected by the SCS<1:0> bits becomes ready (see Figure 4-6), or it will be clocked from the internal oscillator if either the Two-Speed Start-up or the FSCM is enabled (see Section 27.0 "Special Features of the CPU"). In either case, the OSTS bit is set when the primary clock is providing the device clocks. The IDLEN and SCS bits are not affected by the wake-up.

## 6.3.4 SPECIAL FUNCTION REGISTERS

The SFRs are registers used by the CPU and peripheral modules for controlling the desired operation of the device. These registers are implemented as static RAM. SFRs start at the top of data memory (FFFh) and extend downward to occupy more than the top half of Bank 15 (F40h to FFFh). Table 6-2, Table 6-3 and Table 6-4 provide a list of these registers.

The SFRs can be classified into two sets: those associated with the "core" device functionality (ALU, Resets and interrupts) and those related to the peripheral functions. The Reset and Interrupt registers are described in their corresponding chapters, while the

ALU's STATUS register is described later in this section. Registers related to the operation of the peripheral features are described in the chapter for that peripheral.

The SFRs are typically distributed among the peripherals whose functions they control. Unused SFR locations are unimplemented and read as '0's

Note: The SFRs located between EB0h and F5Fh are not part of the Access Bank. Either BANKED instructions (using BSR) or the MOVFF instruction should be used to access these locations. When programming in MPLAB<sup>®</sup> C18, the compiler will automatically use the appropriate addressing mode.

## TABLE 6-2: ACCESS BANK SPECIAL FUNCTION REGISTER MAP

| Address | Name                    | Address | Name                    | Address | Name     | Address | Name                   | Address | Name                     |

|---------|-------------------------|---------|-------------------------|---------|----------|---------|------------------------|---------|--------------------------|

| FFFh    | TOSU                    | FDFh    | INDF2 <sup>(1)</sup>    | FBFh    | PSTR1CON | F9Fh    | IPR1                   | F7Fh    | SPBRGH1                  |

| FFEh    | TOSH                    | FDEh    | POSTINC2 <sup>(1)</sup> | FBEh    | ECCP1AS  | F9Eh    | PIR1                   | F7Eh    | BAUDCON1                 |

| FFDh    | TOSL                    | FDDh    | POSTDEC2 <sup>(1)</sup> | FBDh    | ECCP1DEL | F9Dh    | PIE1                   | F7Dh    | SPBRGH2                  |

| FFCh    | STKPTR                  | FDCh    | PREINC2 <sup>(1)</sup>  | FBCh    | CCPR1H   | F9Ch    | RCSTA2                 | F7Ch    | BAUDCON2                 |

| FFBh    | PCLATU                  | FDBh    | PLUSW2 <sup>(1)</sup>   | FBBh    | CCPR1L   | F9Bh    | OSCTUNE                | F7Bh    | TMR3H                    |

| FFAh    | PCLATH                  | FDAh    | FSR2H                   | FBAh    | CCP1CON  | F9Ah    | T1GCON                 | F7Ah    | TMR3L                    |

| FF9h    | PCL                     | FD9h    | FSR2L                   | FB9h    | PSTR2CON | F99h    | IPR5                   | F79h    | T3CON                    |

| FF8h    | TBLPTRU                 | FD8h    | STATUS                  | FB8h    | ECCP2AS  | F98h    | PIR5                   | F78h    | TMR4                     |

| FF7h    | TBLPTRH                 | FD7h    | TMR0H                   | FB7h    | ECCP2DEL | F97h    | T3GCON                 | F77h    | PR4                      |

| FF6h    | TBLPTRL                 | FD6h    | TMR0L                   | FB6h    | CCPR2H   | F96h    | TRISE                  | F76h    | T4CON                    |

| FF5h    | TABLAT                  | FD5h    | TOCON                   | FB5h    | CCPR2L   | F95h    | TRISD                  | F75h    | SSP2BUF                  |

| FF4h    | PRODH                   | FD4h    | (5)                     | FB4h    | CCP2CON  | F94h    | TRISC                  | F74h    | SSP2ADD <sup>(3)</sup>   |

| FF3h    | PRODL                   | FD3h    | OSCCON                  | FB3h    | CTMUCONH | F93h    | TRISB                  | F73h    | SSP2STAT                 |

| FF2h    | INTCON                  | FD2h    | CM1CON                  | FB2h    | CTMUCONL | F92h    | TRISA                  | F72h    | SSP2CON1                 |

| FF1h    | INTCON2                 | FD1h    | CM2CON                  | FB1h    | CTMUICON | F91h    | PIE5                   | F71h    | SSP2CON2                 |

| FF0h    | INTCON3                 | FD0h    | RCON                    | FB0h    | SPBRG1   | F90h    | IPR4                   | F70h    | CMSTAT                   |

| FEFh    | INDF0 <sup>(1)</sup>    | FCFh    | TMR1H                   | FAFh    | RCREG1   | F8Fh    | PIR4                   | F6Fh    | PMADDRH <sup>(2,4)</sup> |

| FEEh    | POSTINC0 <sup>(1)</sup> | FCEh    | TMR1L                   | FAEh    | TXREG1   | F8Eh    | PIE4                   | F6Eh    | PMADDRL <sup>(2,4)</sup> |

| FEDh    | POSTDEC0 <sup>(1)</sup> | FCDh    | T1CON                   | FADh    | TXSTA1   | F8Dh    | LATE <sup>(2)</sup>    | F6Dh    | PMDIN1H <sup>(2)</sup>   |

| FECh    | PREINC0 <sup>(1)</sup>  | FCCh    | TMR2                    | FACh    | RCSTA1   | F8Ch    | LATD <sup>(2)</sup>    | F6Ch    | PMDIN1L <sup>(2)</sup>   |

| FEBh    | PLUSW0 <sup>(1)</sup>   | FCBh    | PR2                     | FABh    | SPBRG2   | F8Bh    | LATC                   | F6Bh    | TXADDRL                  |

| FEAh    | FSR0H                   | FCAh    | T2CON                   | FAAh    | RCREG2   | F8Ah    | LATB                   | F6Ah    | TXADDRH                  |

| FE9h    | FSR0L                   | FC9h    | SSP1BUF                 | FA9h    | TXREG2   | F89h    | LATA                   | F69h    | RXADDRL                  |

| FE8h    | WREG                    | FC8h    | SSP1ADD <sup>(3)</sup>  | FA8h    | TXSTA2   | F88h    | DMACON1                | F68h    | RXADDRH                  |

| FE7h    | INDF1 <sup>(1)</sup>    | FC7h    | SSP1STAT                | FA7h    | EECON2   | F87h    | OSCCON2 <sup>(5)</sup> | F67h    | DMABCL                   |

| FE6h    | POSTINC1 <sup>(1)</sup> | FC6h    | SSP1CON1                | FA6h    | EECON1   | F86h    | DMACON2                | F66h    | DMABCH                   |

| FE5h    | POSTDEC1 <sup>(1)</sup> | FC5h    | SSP1CON2                | FA5h    | IPR3     | F85h    | HLVDCON                | F65h    | _                        |

| FE4h    | PREINC1 <sup>(1)</sup>  | FC4h    | ADRESH                  | FA4h    | PIR3     | F84h    | PORTE <sup>(2)</sup>   | F64h    | _                        |

| FE3h    | PLUSW1 <sup>(1)</sup>   | FC3h    | ADRESL                  | FA3h    | PIE3     | F83h    | PORTD <sup>(2)</sup>   | F63h    | _                        |

| FE2h    | FSR1H                   | FC2h    | ADCON0                  | FA2h    | IPR2     | F82h    | PORTC                  | F62h    | —                        |

| FE1h    | FSR1L                   | FC1h    | ADCON1                  | FA1h    | PIR2     | F81h    | PORTB                  | F61h    | —                        |

| FE0h    | BSR                     | FC0h    | WDTCON                  | FA0h    | PIE2     | F80h    | PORTA                  | F60h    | _                        |

Note 1: This is not a physical register.

2: This register is not available on 28-pin devices.

3: SSPxADD and SSPxMSK share the same address.

**4:** PMADDRH and PMDOUTH share the same address, and PMADDRL and PMDOUTL share the same address. PMADDRx is used in Master modes and PMDOUTx is used in Slave modes.

5: Reserved; do not write to this location.

| REGISTER 10-1: ODCON1: PERIPHERAL OPEN-DRAIN CONTROL REGISTER 1 (BANKED F42h) |              |                                        |                |                   |                  |                 |         |  |  |

|-------------------------------------------------------------------------------|--------------|----------------------------------------|----------------|-------------------|------------------|-----------------|---------|--|--|

| R/W-0                                                                         | R/W-0        | R/W-0                                  | R/W-0          | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |  |

| CCP8OD                                                                        | CCP7OD       | CCP6OD                                 | CCP5OD         | CCP4OD            | ECCP3OD          | ECCP2OD         | ECCP10D |  |  |

| bit 7                                                                         |              | •                                      |                |                   |                  |                 | bit 0   |  |  |

|                                                                               |              |                                        |                |                   |                  |                 |         |  |  |

| Legend:                                                                       |              |                                        |                |                   |                  |                 |         |  |  |

| R = Readable                                                                  |              | W = Writable                           |                | •                 | nented bit, read |                 |         |  |  |

| -n = Value at                                                                 | POR          | '1' = Bit is set                       |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |  |  |

| hit 7                                                                         |              | CD9 Onen Drei                          | - Output Ench  | a hit             |                  |                 |         |  |  |

| bit 7                                                                         |              | CP8 Open-Drai<br>ain capability is     |                | e bit             |                  |                 |         |  |  |

|                                                                               |              | ain capability is                      |                |                   |                  |                 |         |  |  |

| bit 6                                                                         |              | CP7 Open-Drai                          |                | e bit             |                  |                 |         |  |  |

|                                                                               |              | ain capability is                      | •              |                   |                  |                 |         |  |  |

|                                                                               |              | ain capability is                      |                |                   |                  |                 |         |  |  |

| bit 5                                                                         | CCP6OD: CO   | CP6 Open-Drai                          | n Output Enabl | e bit             |                  |                 |         |  |  |

|                                                                               |              | ain capability is                      |                |                   |                  |                 |         |  |  |

|                                                                               | •            | ain capability is                      |                |                   |                  |                 |         |  |  |

| bit 4                                                                         |              | CP5 Open-Drai                          | •              | e bit             |                  |                 |         |  |  |

|                                                                               |              | ain capability is<br>ain capability is |                |                   |                  |                 |         |  |  |

| bit 3                                                                         | •            | CP4 Open-Drai                          |                | a bit             |                  |                 |         |  |  |

| DIL 3                                                                         |              | ain capability is                      |                | e bit             |                  |                 |         |  |  |

|                                                                               |              | ain capability is                      |                |                   |                  |                 |         |  |  |

| bit 2                                                                         | •            | ECCP3 Open-D                           |                | able bit          |                  |                 |         |  |  |

|                                                                               |              | ain capability is                      | •              |                   |                  |                 |         |  |  |

|                                                                               | 0 = Open-dra | ain capability is                      | disabled       |                   |                  |                 |         |  |  |

| bit 1                                                                         | ECCP2OD: E   | ECCP2 Open-D                           | rain Output En | able bit          |                  |                 |         |  |  |

|                                                                               |              | ain capability is                      |                |                   |                  |                 |         |  |  |

|                                                                               |              | ain capability is                      |                |                   |                  |                 |         |  |  |

| bit 0                                                                         |              | ECCP1 Open-D                           |                | able bit          |                  |                 |         |  |  |

|                                                                               |              | ain capability is<br>ain capability is |                |                   |                  |                 |         |  |  |

|                                                                               |              | an capability is                       | นเรสมเย่น      |                   |                  |                 |         |  |  |

## 10.4 PORTC, TRISC and LATC Registers

PORTC is an 8-bit wide, bidirectional port. The corresponding Data Direction register is TRISC. Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., put the corresponding output driver in a high-impedance mode). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., put the contents of the output latch on the selected pin).

The Data Latch register (LATC) is also memory mapped. Read-modify-write operations on the LATC register read and write the latched output value for PORTC.

PORTC is multiplexed with several peripheral functions (see Table 10-7). The pins have Schmitt Trigger input buffers.

When enabling peripheral functions, care should be taken in defining TRISx bits for each PORTC pin. Some peripherals override the TRISx bit to make a pin an output, while other peripherals override the TRISx bit to make a pin an input. The user should refer to the corresponding peripheral section for additional information.

#### Note: On a Power-on Reset, PORTC pins (except RC2) are configured as digital inputs. RC2 will default as an analog input (controlled by the ANCON1 register).

The contents of the TRISC register are affected by peripheral overrides. Reading TRISC always returns the current contents, even though a peripheral device may be overriding one or more of the pins.

## EXAMPLE 10-4: INITIALIZING PORTC

| CLRF  | PORTC     | ; Initialize PORTC by      |

|-------|-----------|----------------------------|

|       |           | ; clearing output          |

|       |           | ; data latches             |

| CLRF  | LATC      | ; Alternate method         |

|       |           | ; to clear output          |

|       |           | ; data latches             |

| MOVLW | 0x3F      | ; Value used to            |

|       |           | ; initialize data          |

|       |           | ; direction                |

| MOVWF | TRISC     | ; Set RC<5:0> as inputs    |

|       |           | ; RC<7:6> as outputs       |

| MOVLB | 0x0F      | ; ANCON register is not in |

|       |           | Access Bank                |

| BSF   | ANCON1, P | CFG11                      |

|       |           | ;Configure RC2/AN11 as     |

|       |           | digital input              |

|       |           |                            |

## REGISTER 10-24: RPOR0: PERIPHERAL PIN SELECT OUTPUT REGISTER 0 (BANKED EC1h)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | RP0R4 | RP0R3 | RP0R2 | RP0R1 | RP0R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | R/W = Readable bit, V | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |  |  |  |  |

|-------------------|-----------------------|-------------------------------------------------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit                                       | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared                                        | x = Bit is unknown                 |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP0R<4:0>:** Peripheral Output Function is Assigned to RP0 Output Pin bits (see Table 10-14 for peripheral function numbers)

#### REGISTER 10-25: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTER 1 (BANKED EC7h)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | RP1R4 | RP1R3 | RP1R2 | RP1R1 | RP1R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | R/W = Readable bit, | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                                    |  |  |  |  |

|-------------------|---------------------|-------------------------------------------------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit                                       | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared                                        | x = Bit is unknown                 |  |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP1R<4:0>:** Peripheral Output Function is Assigned to RP1 Output Pin bits (see Table 10-14 for peripheral function numbers)

## REGISTER 10-26: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTER 2 (BANKED EC3h)

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

|       | —   | —   | RP2R4 | RP2R3 | RP2R2 | RP2R1 | RP2R0 |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           | $R/\overline{W}$ = Readable bit, W | $R/\overline{W}$ = Readable bit, Writable bit if IOLOCK = 0 |                    |  |  |  |

|-------------------|------------------------------------|-------------------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                   | U = Unimplemented bit, read as '0'                          |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                   | '0' = Bit is cleared                                        | x = Bit is unknown |  |  |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP2R<4:0>:** Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 10-14 for peripheral function numbers)

# REGISTER 11-4: PMMODEL: PARALLEL PORT MODE REGISTER LOW BYTE (BANKED F5Ch)<sup>(1)</sup>

| R/W-0                 | R/W-0                 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0                 | R/W-0                 |

|-----------------------|-----------------------|--------|--------|--------|--------|-----------------------|-----------------------|

| WAITB1 <sup>(2)</sup> | WAITB0 <sup>(2)</sup> | WAITM3 | WAITM2 | WAITM1 | WAITM0 | WAITE1 <sup>(2)</sup> | WAITE0 <sup>(2)</sup> |

| bit 7                 |                       |        |        |        |        |                       | bit 0                 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-6 | WAITB<1:0>: Data Setup to Read/Write Wait State Configuration bits <sup>(2)</sup><br>11 = Data Wait of 4 Tcy; multiplexed address phase of 4 Tcy<br>10 = Data Wait of 3 Tcy; multiplexed address phase of 3 Tcy<br>01 = Data Wait of 2 Tcy; multiplexed address phase of 2 Tcy<br>00 = Data Wait of 1 Tcy; multiplexed address phase of 1 Tcy |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-2 | WAITM<3:0>: Read to Byte Enable Strobe Wait State Configuration bits<br>1111 = Wait of additional 15 Tcy                                                                                                                                                                                                                                      |

|         | 0001 = Wait of additional 1 Tcy<br>0000 = No additional Wait cycles (operation forced into one Tcy)                                                                                                                                                                                                                                           |

| bit 1-0 | WAITE<1:0>: Data Hold After Strobe Wait State Configuration bits <sup>(2)</sup><br>11 = Wait of 4 Tcy<br>10 = Wait of 3 Tcy<br>01 = Wait of 2 Tcy<br>00 = Wait of 1 Tcy                                                                                                                                                                       |

| Note 1  | This register is only systemed on 44 nin devises                                                                                                                                                                                                                                                                                              |

Note 1: This register is only available on 44-pin devices.

2: WAITBx and WAITEx bits are ignored whenever WAITM<3:0> = 0000.

## 15.6 Timer3/5 Interrupt

The TMRx register pair (TMRxH:TMRxL) increments from 0000h to FFFFh and overflows to 0000h. The Timerx interrupt, if enabled, is generated on overflow and is latched in the interrupt flag bit, TMRxIF. Table 15-3 gives each module's flag bit.

TABLE 15-3: TIMER3/5 INTERRUPT FLAG BITS

| Timer Module | Flag Bit |

|--------------|----------|

| 3            | PIR2<1>  |

| 5            | PIR5<1>  |

This interrupt can be enabled or disabled by setting or clearing the TMRxIE bit, respectively. Table 15-4 gives each module's enable bit.

#### TABLE 15-4: TIMER3/5 INTERRUPT ENABLE BITS

| Timer Module | Flag Bit |

|--------------|----------|

| 3            | PIE2<1>  |

| 5            | PIE5<2>  |

## 15.7 Resetting Timer3/5 Using the ECCP Special Event Trigger

If the ECCP modules are configured to use Timerx and to generate a Special Event Trigger in Compare mode (CCPxM<3:0> = 1011), this signal will reset Timerx. The trigger from ECCP2 will also start an A/D conversion if the A/D module is enabled. (For more information, see Section 19.3.4 "Special Event Trigger".)

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPRxH:CCPRxL register pair effectively becomes a Period register for TimerX.

If Timerx is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timerx coincides with a Special Event Trigger from an ECCP module, the write will take precedence.

| Note: | The Special Event Triggers from the        |

|-------|--------------------------------------------|

|       | ECCPx module will only clear the TMR3      |

|       | register's content, but not set the TMR3IF |

|       | interrupt flag bit (PIR1<0>).              |

Note: The CCP and ECCP modules use Timers, 1 through 8, for some modes. The assignment of a particular timer to a CCP/ECCP module is determined by the Timer to CCP enable bits in the CCPTMRSx registers. For more details, see Register 18-3 and Register 19-2.

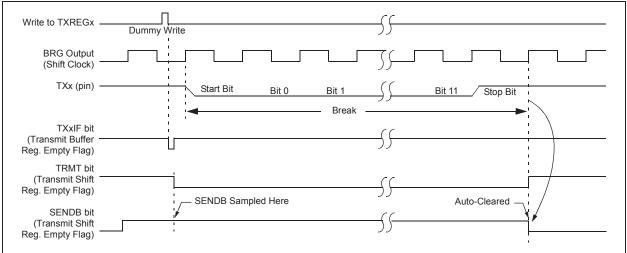

## 21.2.5 BREAK CHARACTER SEQUENCE

The EUSART module has the capability of sending the special Break character sequences that are required by the LIN/J2602 bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTAx<3> and TXSTAx<5>) are set while the Transmit Shift Register is loaded with data.

Note that the value of data written to TXREGx will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN/J2602 specification).

Note that the data value written to the TXREGx for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 21-10 for the timing of the Break character sequence.

#### 21.2.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN/J2602 bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREGx with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREGx to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREGx becomes empty, as indicated by the TXxIF, the next data byte can be written to TXREGx.

#### 21.2.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.

The first method forces configuration of the baud rate at a frequency of 9/13 of the typical speed. This allows for the Stop bit transition to be at the correct sampling location (13 bits for Break versus Start bit and 8 data bits for typical data).

The second method uses the auto-wake-up feature described in Section 21.2.4 "Auto-Wake-up on Sync Break Character". By enabling this feature, the EUSART will sample the next two transitions on RXx/DTx, cause an RCxIF interrupt and receive the next data byte followed by another interrupt.

Note that following a Break character, the user will typically want to enable the Auto-Baud Rate Detect feature. For both methods, the user can set the ABDEN bit once the TXxIF interrupt is observed.

## FIGURE 21-10: SEND BREAK CHARACTER SEQUENCE

# 25.6 Operation During Sleep

When enabled, the HLVD circuitry continues to operate during Sleep. If the device voltage crosses the trip point, the HLVDIF bit will be set and the device will wake-up from Sleep. Device execution will continue from the interrupt vector address if interrupts have been globally enabled.

## 25.7 Effects of a Reset

A device Reset forces all registers to their Reset state. This forces the HLVD module to be turned off.

| Name    | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

|---------|----------|-----------|--------|--------|--------|--------|--------|--------|

| HLVDCON | VDIRMAG  | BGVST     | IRVST  | HLVDEN | HLVDL3 | HLVDL2 | HLVDL1 | HLVDL0 |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF   |

| PIR2    | OSCFIF   | CM2IF     | CM1IF  | —      | BCL1IF | HLVDIF | TMR3IF | CCP2IF |

| PIE2    | OSCFIE   | CM2IE     | CM1IE  | _      | BCL1IE | HLVDIE | TMR3IE | CCP2IE |

| IPR2    | OSCFIP   | CM2IP     | CM1IP  | _      | BCL1IP | HLVDIP | TMR3IP | CCP2IP |

#### TABLE 25-1: REGISTERS ASSOCIATED WITH HIGH/LOW-VOLTAGE DETECT MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the HLVD module.

# PIC18F47J13 FAMILY

| RET                                                                                                                                                                                                                                                                                                                                                     | RETURN Return from Subroutine    |                                                                                                                                                               |               |      |                                                         |                  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|---------------------------------------------------------|------------------|--|--|

| Synta                                                                                                                                                                                                                                                                                                                                                   | ax:                              | RETURN                                                                                                                                                        | {s}           |      |                                                         |                  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                    | ands:                            | $s \in [0,1]$                                                                                                                                                 |               |      |                                                         |                  |  |  |

| Oper                                                                                                                                                                                                                                                                                                                                                    | ation:                           | $(TOS) \rightarrow PC;$<br>if s = 1,<br>$(WS) \rightarrow W,$<br>$(STATUSS) \rightarrow STATUS,$<br>$(BSRS) \rightarrow BSR,$<br>PCLATU, PCLATH are unchanged |               |      |                                                         |                  |  |  |

| Statu                                                                                                                                                                                                                                                                                                                                                   | s Affected:                      | None                                                                                                                                                          |               |      |                                                         |                  |  |  |

| Enco                                                                                                                                                                                                                                                                                                                                                    | ding:                            | 0000                                                                                                                                                          | 0000          | 000  | 1                                                       | 001s             |  |  |

| Description: Return from subroutine. The stack is<br>popped and the top of the stack (TOS)<br>is loaded into the program counter. If<br>'s'= 1, the contents of the shadow<br>registers, WS, STATUSS and BSRS,<br>are loaded into their corresponding<br>registers, W, STATUS and BSR. If<br>'s' = 0, no update of these registers<br>occurs (default). |                                  |                                                                                                                                                               |               |      | ck (TOS)<br>unter. If<br>dow<br>BSRS,<br>nding<br>R. If |                  |  |  |

| Word                                                                                                                                                                                                                                                                                                                                                    | ls:                              | 1                                                                                                                                                             |               |      |                                                         |                  |  |  |

| Cycle                                                                                                                                                                                                                                                                                                                                                   | es:                              | 2                                                                                                                                                             | 2             |      |                                                         |                  |  |  |

| QC                                                                                                                                                                                                                                                                                                                                                      | ycle Activity:                   |                                                                                                                                                               |               |      |                                                         |                  |  |  |

|                                                                                                                                                                                                                                                                                                                                                         | Q1                               | Q2                                                                                                                                                            | Q             | 3    |                                                         | Q4               |  |  |

|                                                                                                                                                                                                                                                                                                                                                         | Decode                           | No<br>operation                                                                                                                                               | Proce<br>Data |      | •                                                       | OP PC<br>m stack |  |  |

|                                                                                                                                                                                                                                                                                                                                                         | No                               | No                                                                                                                                                            | No            |      |                                                         | No               |  |  |

|                                                                                                                                                                                                                                                                                                                                                         | operation                        | operation                                                                                                                                                     | operat        | tion | ор                                                      | eration          |  |  |

| <u>Exan</u>                                                                                                                                                                                                                                                                                                                                             | <u>nple:</u><br>After Instructic | RETURN                                                                                                                                                        |               |      |                                                         |                  |  |  |

After Instruction: PC = TOS

| RLCF                               | Rotate Lef                                                                                                                                                                                                                                                                               |                                          | in Carry                                       | /                                                                |  |  |  |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------|------------------------------------------------------------------|--|--|--|

| Syntax:                            | RLCF f                                                                                                                                                                                                                                                                                   | {,d {,a}}                                |                                                |                                                                  |  |  |  |

| Operands:                          | $0 \le f \le 255$                                                                                                                                                                                                                                                                        |                                          |                                                |                                                                  |  |  |  |

|                                    | d ∈ [0,1]<br>a ∈ [0,1]                                                                                                                                                                                                                                                                   |                                          |                                                |                                                                  |  |  |  |

| Operation:                         | $(f < n >) \rightarrow de$                                                                                                                                                                                                                                                               | <b>⊳st<n +<="" b=""> 1</n></b>           | >                                              |                                                                  |  |  |  |

| operation.                         | $(f<7>) \rightarrow C$                                                                                                                                                                                                                                                                   |                                          | -,                                             |                                                                  |  |  |  |

|                                    | $(C) \rightarrow dest$                                                                                                                                                                                                                                                                   | <0>                                      |                                                |                                                                  |  |  |  |

| Status Affected:                   | C, N, Z                                                                                                                                                                                                                                                                                  |                                          |                                                |                                                                  |  |  |  |

| Encoding:                          | 0011                                                                                                                                                                                                                                                                                     | 0011 01da ffff                           |                                                |                                                                  |  |  |  |

| Description:                       | lf 'd' is '0', t                                                                                                                                                                                                                                                                         | ne left thr<br>he result<br>esult is sto | ough the<br>is place                           | re rotated<br>e Carry flag.<br>ed in W. If 'd'<br>ck in register |  |  |  |

|                                    |                                                                                                                                                                                                                                                                                          | he BSR i                                 |                                                | is selected.<br>to select the                                    |  |  |  |

|                                    | If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever $f \le 95$ (5Fh). See<br>Section 28.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed<br>Literal Offset Mode" for details. |                                          |                                                |                                                                  |  |  |  |

|                                    |                                                                                                                                                                                                                                                                                          |                                          | ctions i                                       | n Indexed                                                        |  |  |  |

|                                    |                                                                                                                                                                                                                                                                                          | set Mode                                 | ctions i                                       | n Indexed<br>tails.                                              |  |  |  |

|                                    | Literal Off                                                                                                                                                                                                                                                                              | set Mode                                 | ctions i<br>" for de                           | n Indexed<br>tails.                                              |  |  |  |

| Words:                             | Literal Off                                                                                                                                                                                                                                                                              | set Mode                                 | ctions i<br>" for de                           | n Indexed<br>tails.                                              |  |  |  |

| Cycles:                            | Literal Off                                                                                                                                                                                                                                                                              | set Mode                                 | ctions i<br>" for de                           | n Indexed<br>tails.                                              |  |  |  |

| Cycles:<br>Q Cycle Activity:       | Literal Offs<br>C<br>1<br>1                                                                                                                                                                                                                                                              | set Mode                                 | ctions i<br>" for de<br>egister f              | n Indexed<br>tails.                                              |  |  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1 | Literal Offs<br>C<br>1<br>1<br>Q2                                                                                                                                                                                                                                                        | set Mode                                 | ctions i<br>" for de<br>egister f              | n Indexed<br>tails.                                              |  |  |  |

| Cycles:<br>Q Cycle Activity:       | Literal Offs<br>C<br>1<br>1                                                                                                                                                                                                                                                              | set Mode                                 | ctions i<br>"" for de<br>egister f<br>3<br>ess | n Indexed<br>tails.                                              |  |  |  |

## 30.4 DC Characteristics: PIC18F47J13 Family (Industrial)

| DC CHA       |        |                                        |     | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |       |                                                    |  |  |

|--------------|--------|----------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------|--|--|

| Param<br>No. | Symbol | Characteristic                         | Тур | Мах                                                                                                                                    | Units | Conditions                                         |  |  |

|              | lı∟    | Input Leakage Current <sup>(1,2)</sup> |     |                                                                                                                                        |       |                                                    |  |  |

| D060         |        | I/O Ports without 5.5V Tolerance       | ±5  | ±200                                                                                                                                   |       | $Vss \le VPIN \le VDD,$ Pin at high-impedance      |  |  |

|              |        | I/O Ports with 5.5V Tolerance          | ±5  | ±200                                                                                                                                   |       | Vss $\leq$ VPIN $\leq$ 5.5V, Pin at high-impedance |  |  |

| D061         |        | MCLR                                   | ±5  | ±200                                                                                                                                   | nA    | $Vss \leq V PIN \leq V DD$                         |  |  |

| D063         |        | OSC1                                   | ±5  | ±200                                                                                                                                   | nA    | $Vss \leq V \text{PIN} \leq V \text{DD}$           |  |  |

**Note 1:** The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

2: Negative current is defined as current sourced by the pin.

#### TABLE 30-1: MEMORY PROGRAMMING REQUIREMENTS

| DC CH/       | ARACTI | ERISTICS                              | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature -40°C $\leq$ TA $\leq$ +85°C for industrial |          |      |       |                                               |

|--------------|--------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------|------|-------|-----------------------------------------------|

| Param<br>No. | Sym    | Characteristic                        |                                                                                                                              | Min Typ† |      | Units | Conditions                                    |

|              |        | Program Flash Memory                  |                                                                                                                              |          |      |       |                                               |

| D130         | Eр     | Cell Endurance                        | 10K                                                                                                                          | —        | _    | E/W   | -40°C to +85°C                                |

| D131         | Vpr    | VDDcore for Read                      | VMIN                                                                                                                         | —        | 2.75 | V     | Vміn = Minimum operating<br>voltage           |

| D132B        | VPEW   | VDDCORE for Self-Timed Erase or Write | 2.25                                                                                                                         | —        | 2.75 | V     |                                               |

| D133A        | Tiw    | Self-Timed Write Cycle Time           | _                                                                                                                            | 2.8      | _    | ms    | 64 bytes                                      |

| D133B        | TIE    | Self-Timed Block Erase Cycle<br>Time  | _                                                                                                                            | 33.0     | _    | ms    |                                               |

| D134         | Tretd  | Characteristic Retention              | 20                                                                                                                           | _        | _    | Year  | Provided no other specifications are violated |

| D135         | IDDP   | Supply Current during<br>Programming  | _                                                                                                                            | 3        | _    | mA    |                                               |

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

| <b>Operating Conditions:</b> 3.0V < VDD < 3.6V, -40°C < TA < +85°C (unless otherwise stated) |        |                                           |      |            |             |       |          |  |  |

|----------------------------------------------------------------------------------------------|--------|-------------------------------------------|------|------------|-------------|-------|----------|--|--|

| Param<br>No.                                                                                 | Sym    | Characteristics                           | Min  | Тур        | Мах         | Units | Comments |  |  |

| D300                                                                                         | VIOFF  | Input Offset Voltage                      |      | <u>+</u> 5 | <u>+</u> 25 | mV    |          |  |  |

| D301                                                                                         | VICM   | Input Common Mode Voltage                 | 0    | _          | Vdd         | V     |          |  |  |

|                                                                                              | Virv   | Internal Reference Voltage                | 0.57 | 0.60       | 0.63        | V     |          |  |  |

| D302                                                                                         | CMRR   | Common Mode Rejection Ratio               | 55   | _          | _           | dB    |          |  |  |