Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are analyzared to

### Details

| Details                 |                                                                         |

|-------------------------|-------------------------------------------------------------------------|

| Product Status          | Active                                                                  |

| Applications            | I/O Controller                                                          |

| Core Processor          | 8024 Keyboard Controller                                                |

| Program Memory Type     | -                                                                       |

| Controller Series       | -                                                                       |

| RAM Size                | -                                                                       |

| Interface               | LPC, Serial, UART                                                       |

| Number of I/O           | 19                                                                      |

| Voltage - Supply        | -                                                                       |

| Operating Temperature   | 0°C ~ 70°C (TA)                                                         |

| Mounting Type           | Surface Mount                                                           |

| Package / Case          | 64-WFBGA                                                                |

| Supplier Device Package | 64-WFBGA (6x6)                                                          |

| Purchase URL            | https://www.e-xfl.com/product-detail/microchip-technology/sch3223-7u-tr |

|                         |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Note        | Name                     | Description                                                                                                                                                                             | VCC<br>Power<br>Plane | VTR<br>Power<br>Plane    | VCC=0<br>Operation<br>(Note 2-10) | Buffer<br>Modes<br>(Note 2-1)                |

|-------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------------|-----------------------------------|----------------------------------------------|

|             |                          | MISCELLA                                                                                                                                                                                | ANEOUS PINS           |                          |                                   |                                              |

|             | GP42/<br>nIO_PME         | General Purpose I/O.<br>Power Management Event<br>Output. This active low<br>Power Management Event<br>signal allows this device to<br>request wake-up in either<br>S3 or S5 and below. |                       | GP42/<br>nIO_PME         | NO GATE                           | (I/O12/OD12)<br>/(O12/OD12)                  |

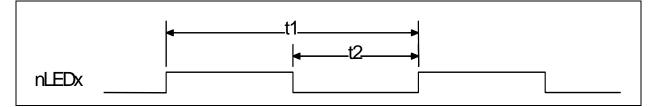

| 2-6,<br>2-7 | GP60<br>/nLED1<br>/WDT   | General Purpose I/O<br>/nLED1<br>Watchdog Timer Output                                                                                                                                  |                       | GP60<br>/nLED1<br>/WDT   | NO GATE                           | (I/O12/OD12)<br>/(O12/OD12)<br>/(O12/OD12)   |

|             | nFPRST /<br>GP30         | Front Panel Reset /<br>General Purpose IO                                                                                                                                               |                       | nFPRST /<br>GP30         | NO GATE                           | ISPU_400 /<br>(I/O4/OD4)                     |

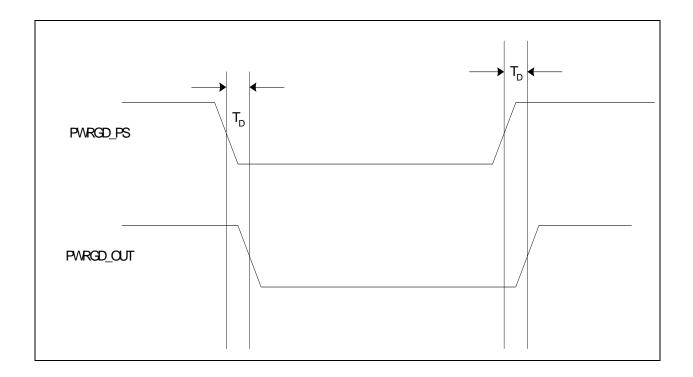

|             | PWRGD_PS                 | Power Good Input from<br>Power Supply                                                                                                                                                   |                       | PWRGD_P<br>S             | NO GATE                           | ISPU_400                                     |

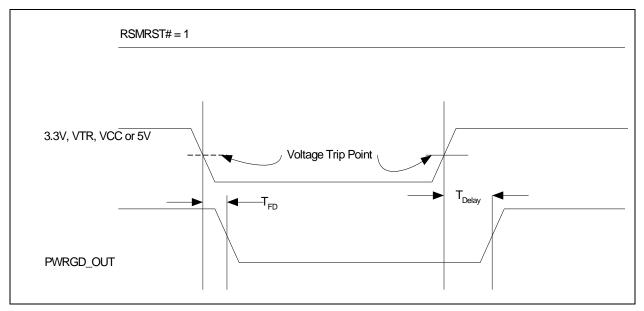

|             | PWRGD_OUT                | Power Good Output –<br>Open Drain                                                                                                                                                       |                       | PWRGD_<br>OUT            | NO GATE                           | OD8                                          |

|             | nRSMRST                  | Resume Reset Output                                                                                                                                                                     |                       | nRSMRST                  | NO GATE                           | OD24                                         |

| 2-6,<br>2-7 | GP61<br>/nLED2 /<br>CLKO | General Purpose I/O<br>/nLED2<br>/ Programmable Clock<br>Output                                                                                                                         |                       | GP61<br>/nLED2 /<br>CLKO | NO GATE                           | (I/O12/OD12)<br>/ (O12/OD12)<br>/ (O12/OD12) |

| 2-7         | GP27 /nIO_SMI            | General Purpose I/O<br>/System Mgt. Interrupt                                                                                                                                           | GP27<br>/nIO_SMI      | GP27                     | /<br>HI-Z                         | (I/O12/OD12)<br>/(O12/OD12)                  |

|             | TEST                     | Test purposes. Customer should tie this pin to VSS at all times.                                                                                                                        | TEST                  | TEST                     |                                   |                                              |

|             |                          | HARDWARE MO                                                                                                                                                                             | ONITORING BL          | OCK                      |                                   |                                              |

| 2-8         | +5V_IN                   | Analog input for +5V                                                                                                                                                                    | HVTR                  |                          |                                   | I <sub>AN</sub>                              |

| 2-8         | +2.5_IN                  | Analog input for +2.5V                                                                                                                                                                  | HVTR                  |                          |                                   | I <sub>AN</sub>                              |

| 2-8         | VCCP_IN                  | Analog input for +Vccp<br>(processor voltage: 1.5 V<br>nominal).                                                                                                                        | HVTR                  |                          |                                   | I <sub>AN</sub>                              |

| 2-8         | +12V_IN                  | Analog input for +12V                                                                                                                                                                   | HVTR                  |                          |                                   | I <sub>AN</sub>                              |

|             | REMOTE1-                 | This is the negative input<br>(current sink) from the<br>remote thermal diode 1.                                                                                                        | HVTR                  |                          |                                   | I <sub>AND-</sub>                            |

|             | REMOTE1+                 | This is the positive input<br>(current source) from the<br>remote thermal diode 1.                                                                                                      | HVTR                  |                          |                                   | I <sub>AND+</sub>                            |

|             | PWM1                     | Fan Speed Control 1<br>Output.                                                                                                                                                          |                       | PWM1                     |                                   | OD8                                          |

|             | FANTACH1                 | Tachometer Input 1 for monitoring a fan.                                                                                                                                                |                       | FANTACH<br>1             |                                   | ١ <sub>M</sub>                               |

|             |                          | RESET                                                                                                                                                                                   | OUTPUTS               |                          |                                   |                                              |

|             | nPCIRST3 /<br>GP47       | PCI Reset output 3<br>GPIO with Schmitt trigger<br>input                                                                                                                                | nPCIRST3              | GP47                     | NO GATE                           | (O4/OD4) /<br>(IS/O4/OD4)                    |

|             | nPCIRST2 /<br>GP46       | PCI Reset output 2<br>GPIO with Schmitt trigger<br>input                                                                                                                                | nPCIRST2              | GP46                     | NO GATE                           | (O8/OD8) /<br>(IS/O8/OD8)                    |

## TABLE 2-2: SCH3223 PIN FUNCTIONS DESCRIPTION (CONTINUED)

# 4.0 POWER FUNCTIONALITY

The SCH3223 has five power planes: VCC, HVTR, VREF, VTR, and Vbat.

### 4.1 VCC Power

The SCH3223 is a 3.3 Volt part. The VCC supply is 3.3 Volts (nominal). VCC is the main power supply for the Super I/O Block. See Section 25.2, "DC Electrical Characteristics," on page 170.

### 4.2 HVTR Power

The HVTR supply is 3.3 Volts (nominal). HVTR is a dedicated power supply for the Hardware Monitoring Block. HVTR is connected to the VTR suspend well. See Section 25.2, "DC Electrical Characteristics," on page 170.

**Note:** The hardware monitoring logic is powered by HVTR, but only operational when VCC is on. The hardware monitoring block is connected to the suspend well to retain the programmed configuration through a sleep cycle.

### 4.3 VTR Support

The SCH3223 requires a trickle supply (VTR) to provide sleep current for the programmable wake-up events in the PME interface when VCC is removed. The VTR supply is 3.3 Volts (nominal). See Section 25.0, "Operational Description," on page 170. The maximum VTR current that is required depends on the functions that are used in the part. See Section 25.0.

If the SCH3223 is not intended to provide wake-up capabilities on standby current, VTR can be connected to VCC. VTR powers the IR interface, the PME configuration registers, and the PME interface. The VTR pin generates a VTR Poweron-Reset signal to initialize these components. If VTR is to be used for programmable wake-up events when VCC is removed, VTR must be at its full minimum potential at least 10 ms before Vcc begins a power-on cycle. Note that under all circumstances, the hardware monitoring HVTR must be driven as the same source as VTR.

### 4.3.1 TRICKLE POWER FUNCTIONALITY

When the SCH3223 is running under VTR only (VCC removed), PME wakeup events are active and (if enabled) able to assert the nIO\_PME pin active low.

The following requirements apply to all I/O pins that are specified to be 5 volt tolerant.

- I/O buffers that are wake-up event compatible are powered by VCC. Under VTR power (VCC=0), these pins may only be configured as inputs. These pins have input buffers into the wakeup logic that are powered by VTR.

- I/O buffers that may be configured as either push-pull or open drain under VTR power (VCC=0), are powered by VTR. This means, at a minimum, they will source their specified current from VTR even when VCC is present.

The GPIOs that are used for PME wakeup as input are GP27, GP50-GP57, GP60, GP61. These GPIOs function as follows (with the exception of GP60 and GP61 - see below):

• Buffers are powered by VCC, but in the absence of VCC they are backdrive protected (they do not impose a load on any external VTR powered circuitry). They are wakeup compatible as inputs under VTR power. These pins have input buffers into the wakeup logic that are powered by VTR.

All GPIOs listed above are PME wakeup as a GPIO (or alternate function).

The other GPIOs function as follows:

### GP42, GP60 and GP61:

• Buffers powered by VTR. GP42 is the nIO\_PME pin which is active under VTR. GP60 and GP61 have LED as the alternate function and the logic is able to control the pin under VTR.

The following list summarizes the blocks, registers and pins that are powered by VTR.

- PME interface block

- PME runtime register block (includes all PME, SMI, GPIO, Fan and other miscellaneous registers)

- Digital logic in the Hardware Monitoring block

- LED control logic

- Watchdog Timer

### Bit 7

This bit is permanently set to logic "0" in the 450 mode. In the FIFO mode, this bit is set to a logic "1" when there is at least one parity error, framing error or break indication in the FIFO. This bit is cleared when the LSR is read if there are no subsequent errors in the FIFO.

### 7.1.9 MODEM STATUS REGISTER (MSR)

### Address Offset = 6H, DLAB = X, READ/WRITE

This 8 bit register provides the current state of the control lines from the MODEM (or peripheral device). In addition to this current state information, four bits of the MODEM Status Register (MSR) provide change information. These bits are set to logic "1" whenever a control input from the MODEM changes state. They are reset to logic "0" whenever the MODEM Status Register is read.

### Bit 0

Delta Clear To Send (DCTS). Bit 0 indicates that the nCTS input to the chip has changed state since the last time the MSR was read.

### Bit 1

Delta Data Set Ready (DDSR). Bit 1 indicates that the nDSR input has changed state since the last time the MSR was read.

### Bit 2

Trailing Edge of Ring Indicator (TERI). Bit 2 indicates that the nRI input has changed from logic "0" to logic "1".

### Bit 3

Delta Data Carrier Detect (DDCD). Bit 3 indicates that the nDCD input to the chip has changed state.

**Note:** Whenever bit 0, 1, 2, or 3 is set to a logic "1", a MODEM Status Interrupt is generated.

### Bit 4

This bit is the complement of the Clear To Send (nCTS) input. If bit 4 of the MCR is set to logic "1", this bit is equivalent to nRTS in the MCR.

### Bit 5

This bit is the complement of the Data Set Ready (nDSR) input. If bit 4 of the MCR is set to logic "1", this bit is equivalent to DTR in the MCR.

### Bit 6

This bit is the complement of the Ring Indicator (nRI) input. If bit 4 of the MCR is set to logic "1", this bit is equivalent to OUT1 in the MCR.

### Bit 7

This bit is the complement of the Data Carrier Detect (nDCD) input. If bit 4 of the MCR is set to logic "1", this bit is equivalent to OUT2 in the MCR.

### 7.1.10 SCRATCHPAD REGISTER (SCR)

### Address Offset =7H, DLAB =X, READ/WRITE

This 8 bit read/write register has no effect on the operation of the Serial Port. It is intended as a scratchpad register to be used by the programmer to hold data temporarily.

### 7.1.11 PROGRAMMABLE BAUD RATE GENERATOR (AND DIVISOR LATCHES DLH, DLL)

The Serial Port contains a programmable Baud Rate Generator that is capable of dividing the internal PLL clock by any divisor from 1 to 65535. The internal PLL clock is divided down to generate a 1.8462MHz frequency for Baud Rates less than 38.4k, a 1.8432MHz frequency for 115.2k, a 3.6864MHz frequency for 230.4k and a 7.3728MHz frequency for 460.8k. This output frequency of the Baud Rate Generator is 16x the Baud rate. Two 8 bit latches store the divisor in 16 bit binary format. These Divisor Latches must be loaded during initialization in order to insure desired operation of the Baud Rate Generator. Upon loading either of the Divisor Latches, a 16 bit Baud counter is immediately loaded. This prevents long counts on initial load. If a 0 is loaded into the BRG registers the output divides the clock by the number 3.

| Register<br>Address<br>(Note 7-4)                  | Register Name                                     | Register<br>Symbol | Bit 7                                 | Bit 6                                        | Bit 5                                       | Bit 4                       | Bit 3                                           | Bit 2                                                   | Bit 1                                                                         | Bit 0                                                         |

|----------------------------------------------------|---------------------------------------------------|--------------------|---------------------------------------|----------------------------------------------|---------------------------------------------|-----------------------------|-------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------|

| $\begin{array}{l} ADDR = 0\\ DLAB = 0 \end{array}$ | Receive Buffer Register<br>(Read Only)            | RBR                | Data Bit 7                            | Data Bit 6                                   | Data Bit 5                                  | Data Bit 4                  | Data Bit 3                                      | Data Bit 2                                              | Data Bit 1                                                                    | Data Bit 0<br>(Note 7-5)                                      |

| ADDR = 0<br>DLAB = 0                               | Transmitter Holding Reg-<br>ister<br>(Write Only) | THR                | Data Bit 7                            | Data Bit 6                                   | Data Bit 5                                  | Data Bit 4                  | Data Bit 3                                      | Data Bit 2                                              | Data Bit 1                                                                    | Data Bit 0                                                    |

| ADDR = 1<br>DLAB = 0                               | Interrupt Enable Register                         | IER                | 0                                     | 0                                            | 0                                           | 0                           | Enable<br>MODEM Sta-<br>tus Interrupt<br>(EMSI) | Enable<br>Receiver Line<br>Status Inter-<br>rupt (ELSI) | Enable<br>Transmitter<br>Holding Reg-<br>ister Empty<br>Interrupt<br>(ETHREI) | Enable<br>Received<br>Data Avail-<br>able Interrup<br>(ERDAI) |

| ADDR = 2                                           | Interrupt Ident. Register<br>(Read Only)          | lir                | FIFOs<br>Enabled<br>(Note 7-9)        | FIFOs<br>Enabled<br>(Note 6)                 | 0                                           | 0                           | Interrupt ID<br>Bit (Note 7-9)                  | Interrupt ID<br>Bit                                     | Interrupt ID<br>Bit                                                           | "0" if Inter-<br>rupt Pending                                 |

| ADDR = 2                                           | FIFO Control Register<br>(Write Only)             | FCR<br>(Note 7-11) | RCVR Trig-<br>ger MSB                 | RCVR Trig-<br>ger LSB                        | Reserved                                    | Reserved                    | DMA Mode<br>Select<br>(Note 7-10)               | XMIT FIFO<br>Reset                                      | RCVR FIFO<br>Reset                                                            | FIFO Enable                                                   |

| ADDR = 3                                           | Line Control Register                             | LCR                | Divisor Latch<br>Access Bit<br>(DLAB) | Set Break                                    | Stick Parity                                | Even Parity<br>Select (EPS) | Parity Enable<br>(PEN)                          | Number of<br>Stop Bits<br>(STB)                         | Word Length<br>Select Bit 1<br>(WLS1)                                         | Word Length<br>Select Bit 0<br>(WLS0)                         |

| ADDR = 4                                           | MODEM Control Register                            | MCR                | 0                                     | 0                                            | 0                                           | Loop                        | OUT2<br>(Note 7-7)                              | OUT1<br>(Note 7-7)                                      | Request to<br>Send (RTS)                                                      | Data Termina<br>Ready (DTR                                    |

| ADDR = 5                                           | Line Status Register                              | LSR                | Error in<br>RCVR FIFO<br>(Note 7-9)   | Transmitter<br>Empty<br>(TEMT)<br>(Note 7-6) | Transmitter<br>Holding Reg-<br>ister (THRE) | Break Inter-<br>rupt (BI)   | Framing Error<br>(FE)                           | Parity Error<br>(PE)                                    | Overrun Error<br>(OE)                                                         | Data Ready<br>(DR)                                            |

| ADDR = 6                                           | MODEM Status Register                             | MSR                | Data Carrier<br>Detect (DCD)          | Ring Indicator<br>(RI)                       | Data Set<br>Ready (DSR)                     | Clear to Send<br>(CTS)      | Delta Data<br>Carrier<br>Detect<br>(DDCD)       | Trailing Edge<br>Ring Indicator<br>(TERI)               | Delta Data<br>Set Ready<br>(DDSR)                                             | Delta Clear to<br>Send (DCTS                                  |

| ADDR = 7                                           | Scratch Register (Note 7-<br>8)                   | SCR                | Bit 7                                 | Bit 6                                        | Bit 5                                       | Bit 4                       | Bit 3                                           | Bit 2                                                   | Bit 1                                                                         | Bit 0                                                         |

#### DECISTED SUMMARY FOR AN INDIVIDUAL UART CHANNEL

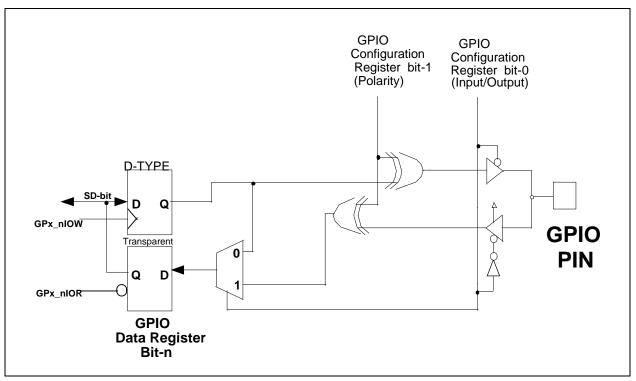

**Note:** Figure 10-1 is for illustration purposes only and is not intended to suggest specific implementation details.

### TABLE 10-4:GPIO READ/WRITE BEHAVIOR

| Host Operation | GPIO Input Port           | GPIO Output Port                 |

|----------------|---------------------------|----------------------------------|

| READ           | LATCHED VALUE OF GPIO PIN | LAST WRITE TO GPIO DATA REGISTER |

| WRITE          | NO EFFECT                 | BIT PLACED IN GPIO DATA REGISTER |

### **10.5 GPIO PME and SMI Functionality**

The SCH3223 provides GPIOs that can directly generate a PME. The polarity bit in the GPIO control registers select the edge on these GPIO pins that will set the associated status bit in a PME Status. For additional description of PME behavior see Section 12.0, "PME Support," on page 46. The default is the low-to-high transition. In addition, the SCH3223 provides GPIOs that can directly generate an SMI.

The following GPIOs are dedicated wakeup GPIOs with a status and enable bit in the PME status and enable registers:

GP27 is controlled by PME\_STS3, PME\_EN3 registers.

GP50-GP57 are controlled by PME\_STS5, PME\_EN5 registers.

GP60, GP61 are controlled by PME\_STS6, and PME\_EN6 registers.

The following GPIOs can directly generate an SMI and have a status and enable bit in the SMI status and enable registers.

GP54, GP55, GP56, GP57, GP60 are controlled by SMI\_STS3, and SMI\_EN3 registers.

GP42, GP61 are controlled by SMI\_STS4, and SMI\_EN4 registers.

The following GPIOs have "either edge triggered interrupt" (EETI) input capability: GP60, GP61. These GPIOs can generate a PME and an SMI on both a high-to-low and a low-to-high edge on the GPIO pin. These GPIOs have a status bit in the PME\_STS6 status register that is set on both edges. The corresponding bits in the PME and SMI status registers are also set on both edges.

© 2015 Microchip Technology Inc.

# 14.0 PROGRAMMABLE CLOCK OUTPUT

A CLK\_OUT pin is available on the SCH3223. This will output a programmable frequency between 0.5 Hz to 16 Hz, and have the following characteristics:

- Must run when Vcc if off could use 32Khz clock

- Accuracy is not an issue

- CLOCK\_OUT register at offset 3Ch in runtime registers with the following programming:

- Options for 0.25, 0.5, 1, 2, 4, 8, or 16 Hz

**APPLICATION NOTE:** No attempt has been made to synchronize the clock. As a result, glitches will occur on the clock output when different frequencies are selected.

| CLOCK Output<br>Control Register<br>VTR POR = 0x00 | Bit[0] Enable<br>1= Output Enabled<br>0= Disable Clock output<br>Bit[3:1] Frequency Select<br>000= 0.25 Hz<br>001= 0.50 Hz<br>010= 1.00 Hz<br>011= 2.00 Hz<br>100= 4.00 Hz<br>101= 8.00 Hz<br>110= 16 hz<br>111 = reserved<br>Bit[7:4] Reserved |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

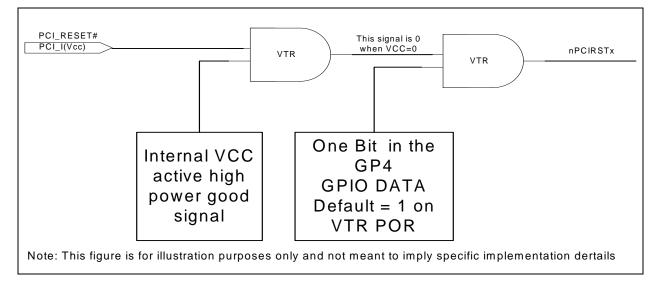

When the VTR power is applied, VCC is powered down, and the GPIO control register's contents are default, the nPCIRSTx pin output is low.

The Figure 16-1 illustrates the nPCIRSTx function. The figure is for illustration purposes only and in not intended to suggest specific implementation details.

### FIGURE 16-1: NPCIRSTX LOGIC

# 17.0 POWER CONTROL FEATURES

The SCH3223 device is able to turn on the power supply when the power button located on the PC chassis is pressed, or when recovering from a power failure. The signals used to support these features are:

- PB\_IN#

- PB\_OUT#

- SLP\_Sx#

- PS\_ON#

Table 17-1 and Figure 17-1 describe the interface and connectivity of the following Power Control Features:

- 1. Front Panel Reset with Input Debounce, Power Supply Gate, and Powergood Output Signal Generation

- 2. AC Recovery Circuit

- 3. SLP\_Sx# PME wakeup

# TABLE 17-1: POWER CONTROL INTERFACE

| Name      | Direction | Description                                                                |

|-----------|-----------|----------------------------------------------------------------------------|

| PB_IN#    | Input     | Power Button Input                                                         |

| PB_OUT#   | Output    | Power Good Output                                                          |

| PS_ON#    | Output    | Power Supply On output                                                     |

| SLP_SX#   | Input     | From south bridge                                                          |

| PWRGD_PS  | Input     | Power Good Input from Power Supply                                         |

| nFPRST    | Input     | Reset Input from Front Panel                                               |

| PWRGD_OUT | Output    | Power Good Output – Open Drain                                             |

| nIO_PME   | Output    | Power Management Event Output signal allows this device to request wakeup. |

# **19.0 BATTERY BACKED SECURITY KEY REGISTER**

Located at the Secondary Base I/O Address of Logical Device A is a 32 byte CMOS memory register dedicated to security key storage. This security key register is battery powered and has the option to be read protected, write protected, and lockable. The Secondary Base I/O Address is programmable at offsets 0x62 and 0x63. Table 19-1, "Security Key Register Summary" is a complete list of the Security Key registers.

| Register Offset<br>(HEX) | Vbat POR                     | Register             |  |  |  |

|--------------------------|------------------------------|----------------------|--|--|--|

| 00                       | 0x00                         | Security Key Byte 0  |  |  |  |

| 01                       | 0x00                         | Security Key Byte 1  |  |  |  |

| 02                       | 0x00                         | Security Key Byte 2  |  |  |  |

| 03                       | 0x00                         | Security Key Byte 3  |  |  |  |

| 04                       | 0x00                         | Security Key Byte 4  |  |  |  |

| 05                       | 0x00 Security Key Byte 5     |                      |  |  |  |

| 06                       | 0x00                         | Security Key Byte 6  |  |  |  |

| 07                       | 0x00                         | Security Key Byte 7  |  |  |  |

| 08                       | 0x00                         | Security Key Byte 8  |  |  |  |

| 09                       | 0x00                         | Security Key Byte 9  |  |  |  |

| 0A                       | 0x00                         | Security Key Byte 10 |  |  |  |

| 0B                       | 0x00                         | Security Key Byte 11 |  |  |  |

| 0C                       | 0x00                         | Security Key Byte 12 |  |  |  |

| 0D                       | 0x00                         | Security Key Byte 13 |  |  |  |

| 0E                       | 0x00                         | Security Key Byte 14 |  |  |  |

| 0F                       | 0x00                         | Security Key Byte 15 |  |  |  |

| 10                       | 0x00                         | Security Key Byte 16 |  |  |  |

| 11                       | 0x00                         | Security Key Byte 17 |  |  |  |

| 12                       | 0x00                         | Security Key Byte 18 |  |  |  |

| 13                       | 0x00                         | Security Key Byte 19 |  |  |  |

| 14                       | 0x00                         | Security Key Byte 20 |  |  |  |

| 15                       | 0x00                         | Security Key Byte 21 |  |  |  |

| 16                       | 0x00                         | Security Key Byte 22 |  |  |  |

| 17                       | 0x00                         | Security Key Byte 23 |  |  |  |

| 18                       | 0x00                         | Security Key Byte 24 |  |  |  |

| 19                       | 0x00                         | Security Key Byte 25 |  |  |  |

| 1A                       | 0x00                         | Security Key Byte 26 |  |  |  |

| 1B                       | 1B 0x00 Security Key Byte 27 |                      |  |  |  |

| 1C                       | 1C 0x00 Security Key Byte 28 |                      |  |  |  |

| 1D                       | 0x00                         | Security Key Byte 29 |  |  |  |

| 1E                       | 0x00                         | Security Key Byte 30 |  |  |  |

| 1F                       | 0x00                         | Security Key Byte 31 |  |  |  |

### TABLE 19-1: SECURITY KEY REGISTER SUMMARY

Access to the Security Key register block is controlled by bits [2:1] of the Security Key Control (SKC) Register located in the Configuration Register block, Logical Device A, at offset 0xF2. The following table summarizes the function of these bits.

occurred and the Tach Reading register will be set to either FFFEh or FFFFh depending on the state of the Slow Tach bits located in the TACHx Options registers at offsets 90h - 93h. Software can easily compute the RPM value using the tachometer reading value if it knows the number of edges per revolution.

- **Note 1:** If the PWM output associated with a tach input is configured for the high frequency option then the tach input must be configured for Mode 1.

- **2:** Some enhanced features added to support Mode 2, are available to Mode 1 also. They are: programmable number of tach edges and force tach reading register to FFFEh to indicate a SLOW fan.

- 3: Five edges or two tach pulses are generated per revolution.

- **4:** If a tach input is left unconnected it must be configured for Mode 1.

### 20.14.2.4 Mode 2 - Monitor Tach input When PWM is 'ON'

In this mode, the PWM is used to pulse the Fan motor of a 3-wire fan. 3-wire fans use the same power supply to drive the fan motor and to drive the tachometer output logic. When the PWM is 'ON' the fan generates valid tach pulses. When the PWM is not driving the Fan, the tachometer signal is not generated and the tach signal becomes indeterminate or tristate. Therefore, Mode 2 only makes tachometer measurements when the associated PWM is driving high during an update cycle. As a result, the Fan tachometer measurement is "synchronized" to the PWM output, such that it only looks for tach pulses when the PWM is 'ON'.

**Note:** Any fan tachometer input may be associated with any PWM output (see Linking Fan Tachometers to PWMs on page 98.)

During an update cycle, if an insufficient number of tachometer pulses are detected during this time period, the following applies: If at least one edge but less than the programmed number of edges is detected, the fan is considered slow. If no edge is detected, the fan is considered stopped.

- **Note 1:** The interrupt status bits are set, if enabled, to indicate that a slow or stopped fan event has occurred when the tach reading registers are greater than the tach limit registers.

- 2: At some duty cycles, the programmed number of edges will appear during some PWM High times, but not all. If opportunistic mode is enabled, the tach logic will latch the count value any time it detects the programmed number of edges and reset the update counter. An interrupt will only be generated if no valid readings were made during the programmed update time.

### 20.14.2.5 Assumptions (refer to Figure 4 - PWM and Tachometer Concept):

The Tachometer pulse generates 5 transitions per fan revolution (i.e., two fan tachometer periods per revolution, edges  $2\rightarrow 6$ ). One half of a revolution (one tachometer period) is equivalent to three edges ( $2\rightarrow 4$  or  $3\rightarrow 5$ ). One quarter of a revolution (one-half tachometer period) is equivalent to two edges. To obtain the fan speed, count the number of 90Khz pulses that occurs between 2 edges i.e.,  $2\rightarrow 3$ , between 3 edges i.e.,  $2\rightarrow 4$ , or between 5 edges, i.e.  $2\rightarrow 6$  (the case of 9 edges is not shown). The time from 1-2 occurs through the guard time and is not to be used. For the discussion below, an edge is a high-to-low or low-to-high transition (edges are numbered – refer to Figure 4 - PWM and Tachometer Concept.

The Tachometer circuit begins monitoring the tach when the associated PWM output transitions high and the guard time has expired. Each tach circuit will continue monitoring until either the "ON" time ends or the programmed number of edges has been detected, whichever comes first.

The Fan Tachometer value may be updated every 300ms, 500ms, or 1000ms.

### 21.2.7 REGISTER 3EH: COMPANY ID

| Register<br>Address | Read/<br>Write | Register Name | Bit 7<br>(MSb) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>(LSb) | Default<br>Value |

|---------------------|----------------|---------------|----------------|-------|-------|-------|-------|-------|-------|----------------|------------------|

| 3Eh                 | R              | Company ID    | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 5Ch              |

The company ID register contains a unique value to allow software to identify Microchip devices that been implemented in a given system.

### 21.2.8 REGISTER 3FH: REVISION

| Register<br>Address | Read/<br>Write | Register Name | Bit 7<br>(MSb) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>(LSb) | Default<br>Value |

|---------------------|----------------|---------------|----------------|-------|-------|-------|-------|-------|-------|----------------|------------------|

| 3Fh                 | R              | Revision      | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | 01h              |

The Revision register contains the current version of this device.

The register is used by application software to identify which version of the device has been implemented in the given system. Based on this information, software can determine which registers to read from and write to. Further, application software may use the current stepping to implement work-arounds for bugs found in a specific silicon stepping.

This register is read only – a write to this register has no effect.

### 21.2.9 REGISTER 40H: READY/LOCK/START MONITORING

| Register<br>Address | Read/<br>Write | Register Name    | Bit 7<br>(MSb) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1                  | Bit 0<br>(LSb) | Default<br>Value |

|---------------------|----------------|------------------|----------------|-------|-------|-------|-------|-------|------------------------|----------------|------------------|

| 40h                 | R/W            | Ready/Lock/Start | RES            | RES   | RES   | RES   | OVRID | READY | LOCK<br>Note 21<br>-15 | START          | 04h              |

Note 21-15 This LOCK bit is cleared when PWRGD\_PS is asserted.

Setting the Lock bit makes the Lock and Start bits read-only.

| Bit | Name  | R/W               | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-------|-------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | START | R/W               | 0       | When software writes a 1 to this bit, the SCH3223 enables<br>monitoring and PWM output control functions based on the<br>limit and parameter registers. Before this bit is set, the part<br>does not update register values. Whenever this bit is set to<br>0, the monitoring and PWM output control functions are<br>based on the default limits and parameters, regardless of the<br>current values in the limit and parameter registers. The<br>SCH3223 preserves the values currently stored in the limit<br>and parameter registers when this bit is set or cleared. This<br>bit becomes read only when the Lock bit is set. |

|     |       |                   |         | Note 1: When this bit is 0, all fans are on full 100% duty cycle, i.e., PWM pins are high for 255 clocks, low for 1 clock. When this bit is 0, the part is not monitoring.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |       |                   |         | 2: It is suggested that software clear the START bit<br>and exit auto fan control mode before modifying<br>any fan configuration registers. After clearing the<br>START bit, software should wait for a period of one<br>90kHz-10% clock (~12.5usec) before setting the<br>START bit back to '1' to ensure the fan logic exited<br>auto mode when START was cleared.                                                                                                                                                                                                                                                              |

| 1   | LOCK  | R/W<br>Note 21-16 | 0       | Setting this bit to 1 locks specified limit and parameter registers. Once this bit is set, limit and parameter registers become read only and will remain locked until the device is powered off. This register bit becomes read only once it is set.                                                                                                                                                                                                                                                                                                                                                                             |

The Fan Tachometer Low Limit registers indicate the tachometer reading under which the corresponding bit will be set in the Interrupt Status Register 2 register. In Auto Fan Control mode, the fan can run at high speeds (100% duty cycle), so care should be taken in software to ensure that the limit is low enough not to cause sporadic alerts. Note that an interrupt status event will be generated when the tachometer reading is greater than the minimum tachometer limit.

The fan tachometer will not cause a bit to be set in the interrupt status register if the current value in the associated Current PWM Duty registers is 00h or if the PWM is disabled via the PWM Configuration Register.

Interrupts will never be generated for a fan if its tachometer minimum is set to FFFFh.

### 21.2.15 REGISTERS 5C-5EH: PWM CONFIGURATION

| Register<br>Address | Read/Write | Register Name       | Bit 7<br>(MSb) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>(LSb) | Default<br>Value |

|---------------------|------------|---------------------|----------------|-------|-------|-------|-------|-------|-------|----------------|------------------|

| 5Ch                 | R/W        | PWM 1 Configuration | ZON2           | ZON1  | ZON0  | INV   | SUEN1 | SPIN2 | SPIN1 | SPIN0          | 62h              |

| 5Dh                 | R/W        | PWM 2 Configuration | ZON2           | ZON1  | ZON0  | INV   | SUEN2 | SPIN2 | SPIN1 | SPIN0          | 62h              |

| 5Eh                 | R/W        | PWM 3 Configuration | ZON2           | ZON1  | ZON0  | INV   | SUEN3 | SPIN2 | SPIN1 | SPIN0          | 62h              |

These registers become read only when the Lock bit is set. Any further attempts to write to these registers shall have no effect.

### Bits [7:5] Zone/Mode

Bits [7:5] of the PWM Configuration registers associate each PWM with a temperature zone.

- When in Auto Fan Mode, the PWM will be assigned to a zone, and its PWM duty cycle will be adjusted according to the temperature of that zone. If 'Hottest' option is selected (101 or 110), the PWM will be controlled by the hottest of zones 2 and 3, or of zones 1, 2, and 3. If one of these options is selected, the PWM is controlled by the limits and parameters for the zone that requires the highest PWM duty cycle, as computed by the auto fan algorithm.

- When in manual control mode, the PWMx Current Duty Cycle Registers (30h-32h) become Read/Write. It is then

possible to control the PWM outputs with software by writing to these registers. See PWMx Current Duty Cycle

Registers description.

- When the fan is disabled (100) the corresponding PWM output is driven low (or high, if inverted).

- When the fan is Full On (011) the corresponding PWM output is driven high (or low, if inverted).

Note 1: Zone 1 is controlled by Remote Diode 1 Temp Reading register

- 2: Zone 2 is controlled by the Ambient Reading Register.

- 3: Zone 3 is controlled by Remote Diode 2 Temp Reading register

| ZON[7:5] | PWM Configuration                        |

|----------|------------------------------------------|

| 000      | Fan on zone 1 auto                       |

| 001      | Fan on zone 2 auto                       |

| 010      | Fan on zone 3 auto                       |

| 011      | Fan always on full                       |

| 100      | Fan disabled                             |

| 101      | Fan controlled by hottest of zones 2,3   |

| 110      | Fan controlled by hottest of zones 1,2,3 |

| 111      | Fan manually controlled                  |

### TABLE 21-7: FAN ZONE SETTING

### Bit [4] PWM Invert

Bit [4] inverts the PWM output. If set to 1, 100% duty cycle will yield an output that is low for 255 clocks and high for 1 clock. If set to 0, 100% duty cycle will yield an output that is high for 255 clocks and low for 1 clock.

### Bit [3] Forced Spin-up Enable

Bit [3] enables the forced spin up option for a particular PWM. If set to 1, the forced spin-up feature is enabled for the associated PWM. If set to 0, the forced spin-up feature is disabled for the associated PWM.

**APPLICATION NOTE:** This bit should always be enabled (set) to prevent fan tachometer interrupts during spinup.

This register holds a bit set until the bit is written to 1 by software. The contents of this register are cleared (set to 0) automatically by the device after it is written by software, if the nTHERMTRIP pin is no longer active. Once set, the Status bits remain set until written to 1, even if the nTHERMTRIP pin is no longer active.

Bits[2:0] THERMTRIP zone status bits (one bit per zone). A status bit is set to '1' if the associated zone temp exceeds the associated THERMTRIP Temp Limit register value.

### 21.2.66 REGISTER CBH: THERMTRIP OUTPUT ENABLE REGISTER

| Register<br>Address | Read/<br>Write | Register Name              | Bit 7<br>(MSb) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>(LSb) | Default<br>Value |

|---------------------|----------------|----------------------------|----------------|-------|-------|-------|-------|-------|-------|----------------|------------------|

| CBh                 | R/W            | THERMTRIP<br>Output Enable | RES            | RES   | RES   | RES   | RES   | RD2   | RD1   | AMB            | 00h              |

These registers become read only when the Lock bit is set. Any further attempts to write to these registers shall have no effect.

Bits[2:0] in THERMTRIP Output Enable register, THERMTRIP output enable bits (one bit per zone). Each zone may be individually enabled to assert the nTHERMTRIP pin if the zone temperature reading exceeds the associated THERM-TRIP Temp Limit register value. 1=enable, 0=disable (default)

### 21.2.67 REGISTER CEH: MCHP RESERVED REGISTER

| Register<br>Address | Read/<br>Write | Register Name | Bit 7<br>(MSb) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2              | Bit 1              | Bit 0<br>(LSb)     | Default<br>Value |

|---------------------|----------------|---------------|----------------|-------|-------|-------|-------|--------------------|--------------------|--------------------|------------------|

| CEh                 | R/W            |               | RES            | RES   | RES   | RES   | RES   | RD2<br>_INT_<br>EN | RD1<br>_INT_<br>EN | AMB_<br>INT_<br>EN | 00h              |

### 21.2.68 REGISTERS D1,D6,DBH: PWM MAX SEGMENT REGISTERS

| Register<br>Address | Read/<br>Write | Register Name | Bit 7<br>(MSb) | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0<br>(LSb) | Default<br>Value |

|---------------------|----------------|---------------|----------------|-------|-------|-------|-------|-------|-------|----------------|------------------|

| 0D1h                | R/W            | PWM1 Max      | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FFh              |

| 0D6h                | R/W            | PWM2 Max      | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FFh              |

| 0DBh                | R/W            | PWM3 Max      | 7              | 6     | 5     | 4     | 3     | 2     | 1     | 0              | FFh              |

These registers become read only when the Lock bit is set. Any further attempts to write to these registers shall have no effect.

Registers 0D1h, 0D6h and 0DBh are used to program the Max PWM duty cycle for the fan function for each PWM.

### 21.2.69 REGISTER E0H: ENABLE LSBS FOR AUTO FAN

| Register<br>Address | Read/<br>Write | Register Name           | Bit 7<br>(MSb) | Bit 6 | Bit 5       | Bit 4       | Bit 3       | Bit 2       | Bit 1       | Bit 0<br>(LSb) | Default<br>Value |

|---------------------|----------------|-------------------------|----------------|-------|-------------|-------------|-------------|-------------|-------------|----------------|------------------|

| E0h                 | R/W            | Enable LSbs for AutoFan | RES            | RES   | PWM3_<br>n1 | PWM3_<br>n0 | PWM2_<br>n1 | PWM2_<br>n0 | PWM1_<br>n1 | PWM1_<br>n0    | 00h              |

### Bits[7:6] Reserved

Bits[5:4] PWM3\_n[1:0]

Bits[3:2] PWM2\_n[1:0]

Bits[1:0] PWM1\_n[1:0]

The PWMx\_n[1:0] configuration bits allow the autofan control logic to utilize the extended resolution bits in the temperature reading. Increasing the precision reduces the programmable temperature range that can be used to control the PWM outputs. For a description of the programmable temperature ranges see Registers 5F-61h: Zone Temperature Range, PWM Frequency on page 116.

### TABLE 22-6: LOGICAL DEVICE REGISTERS (CONTINUED)

| Logical Device Register              | Address     | Description                                                                                             |

|--------------------------------------|-------------|---------------------------------------------------------------------------------------------------------|

| DMA Selection                        | (0x74,0x75) | Reserved - not supported in the SCH3223. Do not attempt to alter these registers in any Logical Device. |

| 32-Bit Memory Space<br>Configuration | (0x76-0xA8) | Reserved - not implemented. These register locations ignore writes and return zero when read.           |

| Logical Device                       | (0xA9-0xDF) | Reserved - not implemented. These register locations ignore writes and return zero when read.           |

| Logical Device Configuration         | (0xE0-0xFE) | Reserved – Vendor Defined (see MCHP defined Logical Device Configuration Registers).                    |

| Reserved                             | 0xFF        | Reserved                                                                                                |

|                                      |             |                                                                                                         |

**Note 22-4** A logical device will be active and powered up according to the following equation unless otherwise specified:

DEVICE ON (ACTIVE) = (Activate Bit SET or Pwr/Control Bit SET).

The Logical Device's Activate Bit and its Pwr/Control Bit are linked such that setting or clearing one sets or clears the other.

**Note 22-5** If the I/O Base Addr of the logical device is not within the Base I/O range as shown in the Logical Device I/O map, then read or write is not valid and is ignored.

| Logical<br>Device<br>Number | Logical Device               | Register<br>Index | Base I/O Range<br>(Note 22-6)             | Fixed Base Offsets                                                                                                 |

|-----------------------------|------------------------------|-------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 0x00                        | Reserved                     | n/a               | n/a                                       | n/a                                                                                                                |

| 0x01                        | Reserved                     | n/a               | n/a                                       | n/a                                                                                                                |

| 0x02                        | Reserved                     | n/a               | n/a                                       | n/a                                                                                                                |

| 0x03                        | Reserved                     | n/a               | n/a                                       | n/a                                                                                                                |

| 0x04                        | Serial Port 1                | 0x60,0x61         | [0x0100:0x0FF8]<br>ON 8 BYTE BOUNDARIES   | +0 : RB/TB/LSB div<br>+1 : IER/MSB div<br>+2 : IIR/FCR<br>+3 : LCR<br>+4 : MSR<br>+5 : LSR<br>+6 : MSR<br>+7 : SCR |

| 0x05                        | Serial Port 2                | 0x60,0x61         | [0x0100:0x0FF8]<br>ON 8 BYTE BOUNDARIES   | +0 : RB/TB/LSB div<br>+1 : IER/MSB div<br>+2 : IIR/FCR<br>+3 : LCR<br>+4 : MSR<br>+5 : LSR<br>+6 : MSR<br>+7 : SCR |

| 0x06                        | Reserved                     | n/a               | n/a                                       | n/a                                                                                                                |

| 0x07                        | Reserved                     | n/a               | n/a                                       | n/a                                                                                                                |

| 0x08                        | Reserved                     | n/a               | n/a                                       | n/a                                                                                                                |

| 0x09                        | Reserved                     | n/a               | n/a                                       | n/a                                                                                                                |

| 0x0A                        | Runtime<br>Register<br>Block | 0x60,0x61         | [0x0000:0x0F7F]<br>on 128-byte boundaries | See Table 23-1, "Runtime Register<br>Summary," on page 150                                                         |

|                             | Security Key<br>Register     | 0x62, 0x63        | [0x0000:0x0FDF<br>on 32-byte boundaries   | +00 : Security Key Byte 0<br>+1F: Security Key Byte 31                                                             |

| 0x0B                        | Reserved                     | n/a               | n/a                                       | n/a                                                                                                                |

TABLE 22-7: BASE I/O RANGE FOR LOGICAL DEVICES

| CLOCKI32<br>Default = 0x00 on VTR<br>POR                                                     | 0xF0<br>(R/W)                                               | Bit[0] (CLK32_PRSN)<br>0 = 32kHz clock is connected to the CLKI32 pin (default)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                              |                                                             | <ul> <li>a) a significant of the control of the con</li></ul> |

| Reserved Register<br>Default = 0x00<br>on VCC POR,<br>/TR POR and<br>PCI RESET               | 0xF1 R/W                                                    | Reserved. Do not alter from default value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Security Key Control<br>SKC) Register<br>Default=0x04 on a VTR<br>POR, VCC POR, PCI<br>Reset | 0xF2<br>R/W when<br>bit[0]= 0<br>Read-Only when<br>bit[0]=1 | Bit[0] SKC Register Lock<br>This bit blocks write access to the Security Key Control Register.<br>0 = Security Key Control Register is a Read/Write register (default)<br>1 = Security Key Control Register is a Read-Only register<br>Bit[1] Read-Lock<br>This bit prevents reads from the Security Key registers located at an<br>offset from the Secondary Base I/O address in Logical Device A<br>0 = Permits read operations in the Security Key block (default)<br>1 = Prevents read operations in the Security Key block (default)<br>1 = Prevents read operations in the Security Key block (Reads return<br>00h.)<br>Bit[2] Write-Lock<br>This bit prevents writes to the Security Key registers located at an<br>offset from the Secondary Base I/O address in Logical Device A<br>0 = Permits write operations in the Security Key block<br>1 = Prevents write operations in the Security Key block<br>1 = Prevents write operations in the Security Key block<br>1 = Prevents write operations in the Security Key block<br>1 = Reserved<br>Bit[3] Reserved<br>Bit[4] Reserved<br>Bit[6] Reserved<br>Bit[6] Reserved<br>Bit[7] Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# TABLE 22-11: LOGICAL DEVICE A [LOGICAL DEVICE NUMBER = 0X0A]

### TABLE 23-2: DETAILED RUNTIME REGISTER DESCRIPTION (CONTINUED)

| Name                                                                                                                                                                                                                                                                                                                                                                                                                          | REG Offset<br>(HEX)                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMI_STS1<br>Default = 0x02, or<br>0x03 on VTR POR.<br>The default will be<br>0x03 if there is a<br>LOW_BAT event<br>under VBAT power<br>only, or 0x02 if this<br>event does not occur.<br>Bit 0 will be set to '1'<br>on a VCC POR if the<br>battery voltage drops<br>below 2.4V under<br>VTR power (VCC=0)<br>or under battery<br>power only.<br>Bit 1 is set to '1' on<br>VCC POR, VTR<br>POR, PCI Reset and<br>soft reset. | 14<br>Bits[0] are<br>R/WC.<br>Bits[1:4,7] are<br>RO.            | SMI Status Register 1<br>This register is used to read the status of the SMI inputs.<br>The following bits must be cleared at their source except as shown.<br>Bit[0] LOW_BAT. Cleared by a write of '1'. When the battery is removed and<br>replaced or if the battery voltage drops below 1.2V (nominal) under battery<br>power only (VBAT POR), then the LOW_BAT SMI status bit is set on VTR<br>POR. When the battery voltage drops below 2.4 volts (nominal) under VTR<br>power (VCC=0) or under battery power only, the LOW_BAT SMI status bit is<br>set on VCC POR.<br>Bit[1] Reserved<br>Bit[2] U2INT<br>Bit[4] Reserved<br>Bit[5] Reserved<br>Bit[6] Reserved<br>Bit[7] WDT |

| SMI_STS2                                                                                                                                                                                                                                                                                                                                                                                                                      | 15                                                              | Bit[7:0] Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Default = 0x00<br>on VTR POR<br>SMI_STS3                                                                                                                                                                                                                                                                                                                                                                                      | (R/W)<br>Bits[0,1] are<br>RO<br>Bits[2] is<br>Read-Clear.<br>16 | SMI Status Register 3<br>This register is used to read the status of the SMI inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Default = 0x00<br>on VTR POR                                                                                                                                                                                                                                                                                                                                                                                                  | (R/WC)                                                          | The following bits are cleared on a write of '1'.<br>Bit[0] Reserved<br>Bit[1] Reserved<br>Bit[2] Reserved<br>Bit[3] GP54<br>Bit[4] GP55<br>Bit[5] GP56<br>Bit[6] GP57<br>Bit[7] GP60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SMI_STS4<br>Default = 0x00<br>on VTR POR<br>(Note 23-14)                                                                                                                                                                                                                                                                                                                                                                      | 17<br>(R/WC)                                                    | SMI Status Register 4<br>This register is used to read the status of the SMI inputs.<br>The following bits are cleared on a write of '1'.<br>Bit[0] Reserved<br>Bit[1] Reserved<br>Bit[2] Reserved<br>Bit[3] Reserved<br>Bit[4] Reserved<br>Bit[5] GP42<br>Bit[6] Reserved<br>Bit[7] GP61                                                                                                                                                                                                                                                                                                                                                                                            |

| SMI_EN1<br>Default = 0x00<br>on VTR POR                                                                                                                                                                                                                                                                                                                                                                                       | 18<br>(R/W)                                                     | SMI Enable Register 1<br>This register is used to enable the different interrupt sources onto the group<br>nIO_SMI output.<br>1=Enable<br>0=Disable<br>Bit[0] EN_LOW_BAT<br>Bit[1] Reserved<br>Bit[2] EN_U2INT<br>Bit[3] EN_U1INT<br>Bit[4] Reserved<br>Bit[5] Reserved<br>Bit[6] Reserved<br>Bit[7] EN_WDT                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                            |                                    |                            | -                                                           | -                                                                  |                    |                                      |

|--------------------------------------------------------------------------------------------|------------------------------------|----------------------------|-------------------------------------------------------------|--------------------------------------------------------------------|--------------------|--------------------------------------|

| SUPER I/O BLO<br>(T <sub>A</sub>                                                           | OCK (T <sub>A</sub> IND<br>COMMERC | IAL = 0 <sup>0</sup> C - + | 10 <sup>0</sup> C – +1<br>70 <sup>0</sup> C, V <sub>0</sub> | 85 <sup>0</sup> C, V <sub>CC</sub> = -<br><sub>CC</sub> = +3.3 V ± | +3.3 V ± 1<br>10%) | 10%) OR                              |

| Parameter                                                                                  | Symbol                             | MIN                        | ТҮР                                                         | MAX                                                                | Units              | Comments                             |

| IO12 Type Buffer                                                                           |                                    |                            |                                                             |                                                                    |                    |                                      |