Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                 |

| Number of I/O              | 30                                                                            |

| Program Memory Size        | 24KB (8K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3011-20e-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, UniWinDriver, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U S A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2010, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

#### ISBN: 978-1-60932-659-3

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL00® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

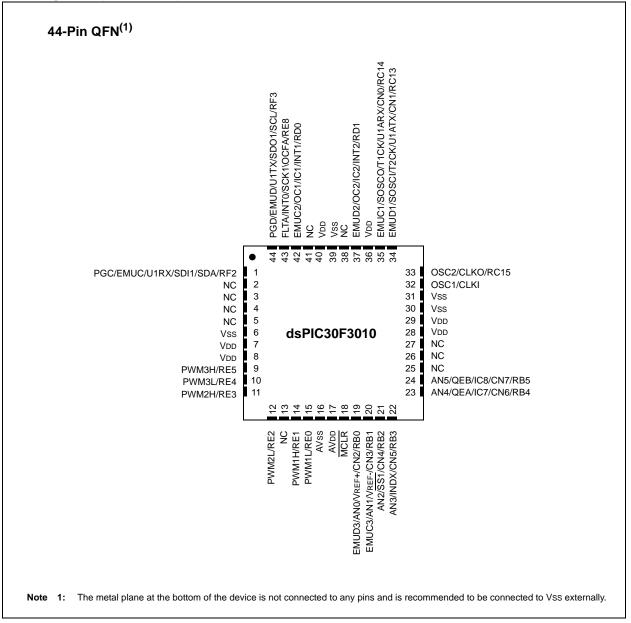

## **Pin Diagrams (Continued)**

# dsPIC30F3010/3011

NOTES:

| Pin Name              | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                        |  |  |  |  |  |  |

|-----------------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| OSC1                  | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                    |  |  |  |  |  |  |

| OSC2                  | I/O         | —              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.           |  |  |  |  |  |  |

| PGD                   | I/O         | ST             | In-Circuit Serial Programming data input/output pin.                                                                                               |  |  |  |  |  |  |

| PGC                   | I           | ST             | In-Circuit Serial Programming clock input pin.                                                                                                     |  |  |  |  |  |  |

| RB0-RB5               | I/O         | ST             | PORTB is a bidirectional I/O port.                                                                                                                 |  |  |  |  |  |  |

| RC13-RC15             | I/O         | ST             | PORTC is a bidirectional I/O port.                                                                                                                 |  |  |  |  |  |  |

| RD0-RD1               | I/O         | ST             | PORTD is a bidirectional I/O port.                                                                                                                 |  |  |  |  |  |  |

| RE0-RE5,<br>RE8       | I/O         | ST             | PORTE is a bidirectional I/O port.                                                                                                                 |  |  |  |  |  |  |

| RF2-RF3               | I/O         | ST             | PORTF is a bidirectional I/O port.                                                                                                                 |  |  |  |  |  |  |

| SCK1                  | I/O         | ST             | Synchronous serial clock input/output for SPI1.                                                                                                    |  |  |  |  |  |  |

| SDI1                  | I           | ST             | SPI1 Data In.                                                                                                                                      |  |  |  |  |  |  |

| SDO1                  | 0           | —              | SPI1 Data Out.                                                                                                                                     |  |  |  |  |  |  |

| SCL                   | I/O         | ST             | Synchronous serial clock input/output for I <sup>2</sup> C.                                                                                        |  |  |  |  |  |  |

| SDA                   | I/O         | ST             | Synchronous serial data input/output for I <sup>2</sup> C.                                                                                         |  |  |  |  |  |  |

| SOSCO<br>SOSCI        | 0           | ST/CMOS        | 32 kHz low-power oscillator crystal output.<br>32 kHz low-power oscillator crystal input. ST buffer when configured in RC<br>mode; CMOS otherwise. |  |  |  |  |  |  |

| T1CK                  | I           | ST             | Timer1 external clock input.                                                                                                                       |  |  |  |  |  |  |

| T2CK                  | I           | ST             | Timer2 external clock input.                                                                                                                       |  |  |  |  |  |  |

| U1RX                  | I           | ST             | UART1 Receive.                                                                                                                                     |  |  |  |  |  |  |

| U1TX                  | 0           | —              | UART1 Transmit.                                                                                                                                    |  |  |  |  |  |  |

| U1ARX                 |             | ST             | UART1 Alternate Receive.                                                                                                                           |  |  |  |  |  |  |

| U1ATX                 | 0           |                | UART1 Alternate Transmit.                                                                                                                          |  |  |  |  |  |  |

| VDD                   | P           | —              | Positive supply for logic and I/O pins.                                                                                                            |  |  |  |  |  |  |

| Vss                   | P           |                | Ground reference for logic and I/O pins.                                                                                                           |  |  |  |  |  |  |

| VREF+                 | I           | Analog         | Analog Voltage Reference (High) input.                                                                                                             |  |  |  |  |  |  |

| Vref-                 | I           | Analog         | Analog Voltage Reference (Low) input.                                                                                                              |  |  |  |  |  |  |

| Legend: CM<br>ST<br>I | = Sc        |                | ible input or outputAnalog =Analog inputr input with CMOS levelsO=OutputP=Power                                                                    |  |  |  |  |  |  |

TABLE 1-2: dsPIC30F3010 I/O PIN DESCRIPTIONS (CONTINUED)

# dsPIC30F3010/3011

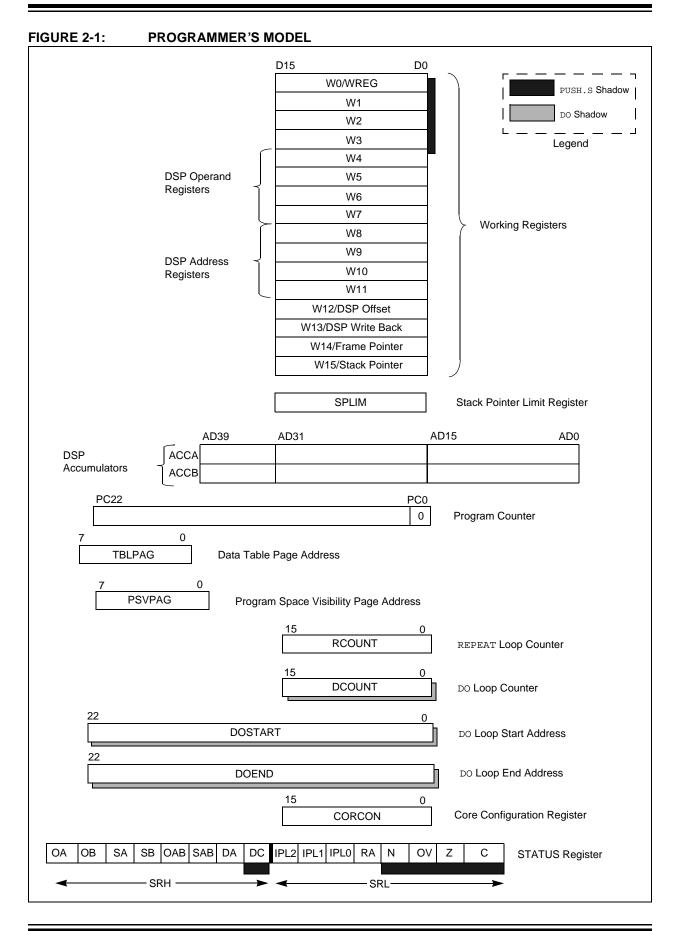

### TABLE 3-1: PROGRAM SPACE ADDRESS CONSTRUCTION

|                          | Access                           | Program Space Address |                            |  |        |     |  |  |  |  |

|--------------------------|----------------------------------|-----------------------|----------------------------|--|--------|-----|--|--|--|--|

| Access Type              | Space                            | <23>                  | <23> <22:16> <15>          |  | <14:1> | <0> |  |  |  |  |

| Instruction Access       | User                             | 0                     | 0 PC<22:1> 0               |  |        |     |  |  |  |  |

| TBLRD/TBLWT              | User<br>(TBLPAG<7> = 0)          | TBL                   | BLPAG<7:0> Data EA <15:0>  |  |        |     |  |  |  |  |

| TBLRD/TBLWT              | Configuration<br>(TBLPAG<7> = 1) | TBL                   | TBLPAG<7:0> Data EA <15:0> |  |        |     |  |  |  |  |

| Program Space Visibility | User                             | 0                     | PSVPAG<7:0> Data EA <14:0: |  |        |     |  |  |  |  |

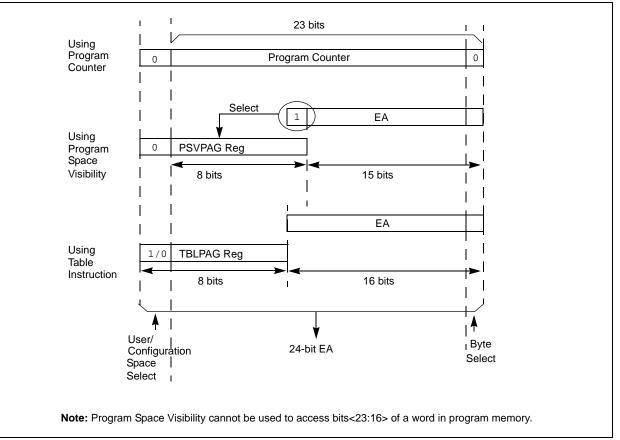

#### FIGURE 3-2: DATA ACCESS FROM PROGRAM SPACE ADDRESS GENERATION

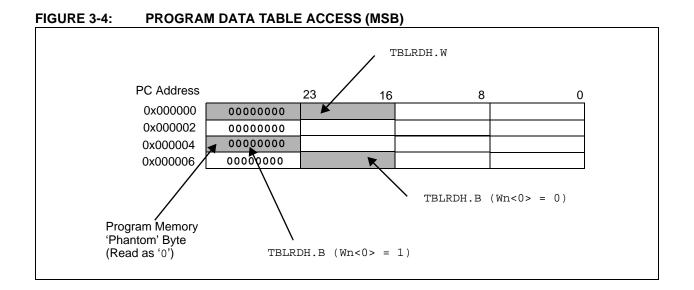

#### 3.1.1 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

This architecture fetches 24-bit wide program memory. Consequently, instructions are always aligned. However, as the architecture is modified Harvard, data can also be present in program space.

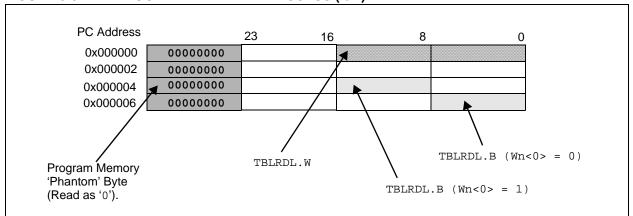

There are two methods by which program space can be accessed: via special table instructions, or through the remapping of a 16K word program space page into the upper half of data space (see Section 3.1.2 "Data Access From Program Memory Using Program Space Visibility"). The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the Isw of any address within program space, without going through data space. The TBLRDH and TBLWTH instructions are the only method whereby the upper 8 bits of a program space word can be accessed as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the lsw, and TBLRDH and TBLWTH access the space which contains the MSB.

Figure 3-2 illustrates how the EA is created for table operations and data space accesses (PSV = 1). Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a data space word.

A set of table instructions are provided to move byte or word-sized data to and from program space.

- TBLRDL: Table Read Low Word: Read the lsw of the program address; P<15:0> maps to D<15:0>. Byte: Read one of the LSBs of the program address; P<7:0> maps to the destination byte when byte select = 0; P<15:8> maps to the destination byte when byte select = 1.

- TBLWTL: Table Write Low (refer to Section 6.0 "Flash Program Memory" for details on Flash programming).

- TBLRDH: Table Read High Word: Read the msw of the program address; P<23:16> maps to D<7:0>; D<15:8> will always

be = 0.Bute: Bead one of the MSBs of the program

*Byte:* Read one of the MSBs of the program address;

P<23:16> maps to the destination byte when byte select = 0;

The destination byte will always be = 0 when byte select = 1.

TBLWTH: Table Write High (refer to Section 6.0 "Flash Program Memory" for details on Flash programming).

#### FIGURE 3-3: PROGRAM DATA TABLE ACCESS (Isw)

# dsPIC30F3010/3011

#### 3.1.2 DATA ACCESS FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word program space page. This provides transparent access of stored constant data from X data space, without the need to use special instructions (i.e., TBLRDL/H, TBLWTL/H instructions).

Program space access through the data space occurs if the MSb of the data space, EA, is set and program space visibility is enabled, by setting the PSV bit in the Core Control register (CORCON). The functions of CORCON are discussed in Section 2.4 "DSP Engine".

Data accesses to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Note that the upper half of addressable data space is always part of the X data space. Therefore, when a DSP operation uses program space mapping to access this memory region, Y data space should typically contain state (variable) data for DSP operations, whereas X data space should typically contain coefficient (constant) data.

Although each data space address, 0x8000 and higher, maps directly into a corresponding program memory address, as shown in Figure 3-5, only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits should be programmed to force an illegal instruction to maintain machine robustness. Refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157) for details on instruction encoding. Note that by incrementing the PC by 2 for each program memory word, the 15 LSbs of data space addresses directly map to the 15 LSbs in the corresponding program space addresses. The remaining bits are provided by the Program Space Visibility Page register, PSVPAG<7:0>, as shown in Figure 3-5.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | table reads/writes.                       |

For instructions that use PSV which are executed outside a REPEAT loop:

- The following instructions will require one instruction cycle in addition to the specified execution time:

- MAC class of instructions with data operand prefetch

- MOV instructions

- MOV.D instructions

- All other instructions will require two instruction cycles in addition to the specified execution time of the instruction.

For instructions that use PSV which are executed inside a REPEAT loop:

- The following instances will require two instruction cycles in addition to the specified execution time of the instruction:

- Execution in the first iteration

- Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

- Any other iteration of the REPEAT loop will allow the instruction, accessing data using PSV, to execute in a single cycle.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A sign-extend (SE) instruction is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions, including the DSP instructions, operate only on words.

#### 3.2.5 NEAR DATA SPACE

An 8 Kbyte 'near' data space is reserved in X address memory space between 0x0000 and 0x1FFF, which is directly addressable via a 13-bit absolute address field within all memory direct instructions. The remaining X address space and all of the Y address space is addressable indirectly. Additionally, the whole of X data space is addressable using MOV instructions, which support memory direct addressing with a 16-bit address field.

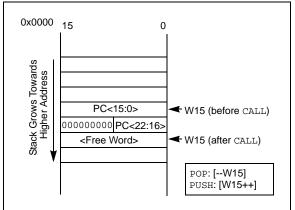

#### 3.2.6 SOFTWARE STACK

The dsPIC DSC device contains a software stack. W15 is used as the Stack Pointer.

The Stack Pointer always points to the first available free word and grows from lower addresses towards higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 3-9. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

Note: A PC push during exception processing will concatenate the SRL register to the MSB of the PC prior to the push. There is a Stack Pointer Limit register (SPLIM) associated with the Stack Pointer. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0', because all stack operations must be word-aligned. Whenever an Effective Address (EA) is generated using W15 as a source or destination pointer, the address thus generated is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value, 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800, thus preventing the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

### FIGURE 3-9: CALL STACK FRAME

## 4.0 ADDRESS GENERATOR UNITS

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

The dsPIC DSC core contains two independent address generator units: the X AGU and Y AGU. The Y AGU supports word-sized data reads for the DSP MAC class of instructions only. The dsPIC DSC AGUs support three types of data addressing:

- Linear Addressing

- Modulo (Circular) Addressing

- Bit-Reversed Addressing

Linear and Modulo Data Addressing modes can be applied to data space or program space. Bit-Reversed Addressing is only applicable to data space addresses.

## 4.1 Instruction Addressing Modes

The addressing modes in Table 4-1 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions are somewhat different from those in the other instruction types.

### 4.1.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (near data space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register, or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space during file register operation.

#### 4.1.2 MCU INSTRUCTIONS

The three-operand MCU instructions are of the form:

Operand 3 = Operand 1 < function> Operand 2

where Operand 1 is always a working register (i.e., the addressing mode can only be Register Direct), which is referred to as Wb. Operand 2 can be a W register, fetched from data memory, or a 5-bit literal. The result location can be either a W register or an address location. The following addressing modes are supported by MCU instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-Modified

- Register Indirect Pre-Modified

- 5-bit or 10-bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### TABLE 4-1:FUNDAMENTAL ADDRESSING MODES SUPPORTED

| Addressing Mode                        | Description                                                                                            |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                   | The address of the file register is specified explicitly.                                              |

| Register Direct                        | The contents of a register are accessed directly.                                                      |

| Register Indirect                      | The contents of Wn forms the EA.                                                                       |

| Register Indirect Post-Modified        | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified         | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset  | The sum of Wn and a literal forms the EA.                                                              |

## 6.4 RTSP Operation

The dsPIC30F Flash program memory is organized into rows and panels. Each row consists of 32 instructions or 96 bytes. Each panel consists of 128 rows or  $4K \times 24$  instructions. RTSP allows the user to erase one row (32 instructions) at a time and to program 32 instructions at one time.

Each panel of program memory contains write latches that hold 32 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the panel write latches. The data to be programmed into the panel is loaded in sequential order into the write latches; instruction 0, instruction 1, etc. The addresses loaded must always be from an even group of 32 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the write latches. Programming is performed by setting the special bits in the NVMCON register. 32 TBLWTL and four TBLWTH instructions are required to load the 32 instructions.

All of the table write operations are single-word writes (2 instruction cycles), because only the table latches are written.

After the latches are written, a programming operation needs to be initiated to program the data.

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

### 6.5 RTSP Control Registers

The four SFRs used to read and write the program Flash memory are:

- NVMCON

- NVMADR

- NVMADRU

- NVMKEY

#### 6.5.1 NVMCON REGISTER

The NVMCON register controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

#### 6.5.2 NVMADR REGISTER

The NVMADR register is used to hold the lower two bytes of the effective address. The NVMADR register captures the EA<15:0> of the last table instruction that has been executed and selects the row to write.

#### 6.5.3 NVMADRU REGISTER

The NVMADRU register is used to hold the upper byte of the effective address. The NVMADRU register captures the EA<23:16> of the last table instruction that has been executed.

#### 6.5.4 NVMKEY REGISTER

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 6.6 "Programming Operations"** for further details.

**Note:** The user can also directly write to the NVMADR and NVMADRU registers to specify a program memory address for erasing or programming.

### 14.3 Position Measurement Mode

There are two measurement modes which are supported and are termed x2 and x4. These modes are selected by the QEIM<2:0> mode select bits located in SFR, QEICON<10:8>.

When control bits, QEIM<2:0> = 100 or 101, the x2 Measurement mode is selected and the QEI logic only looks at the Phase A input for the position counter increment rate. Every rising and falling edge of the Phase A signal causes the position counter to be incremented or decremented. The Phase B signal is still utilized for the determination of the counter direction, just as in the x4 Measurement mode.

Within the x2 Measurement mode, there are two variations of how the position counter is reset:

- Position counter reset by detection of index pulse, QEIM<2:0> = 100.

- Position counter reset by match with MAXCNT, QEIM<2:0> = 101.

When control bits, QEIM<2:0> = 110 or 111, the x4 Measurement mode is selected and the QEI logic looks at both edges of the Phase A and Phase B input signals. Every edge of both signals causes the position counter to increment or decrement.

Within the x4 Measurement mode, there are two variations of how the position counter is reset:

- 1. Position counter reset by detection of index pulse, QEIM<2:0> = 110.

- Position counter reset by match with MAXCNT, QEIM<2:0> = 111.

The x4 Measurement mode provides for finer resolution data (more position counts) for determining motor position.

#### 14.4 Programmable Digital Noise Filters

The digital noise filter section is responsible for rejecting noise on the incoming quadrature signals. Schmitt Trigger inputs and a three-clock cycle delay filter combine to reject low level noise and large, short duration noise spikes that typically occur in noise prone applications, such as a motor system.

The filter ensures that the filtered output signal is not permitted to change until a stable value has been registered for three consecutive clock cycles.

For the QEA, QEB and INDX pins, the clock divide frequency for the digital filter is programmed by bits, QECK<2:0> (DFLTCON<6:4>), and are derived from the base instruction cycle, Tcy.

To enable the filter output for channels, QEA, QEB and INDX, the QEOUT bit must be '1'. The filter network for all channels is disabled on POR and BOR.

### 14.5 Alternate 16-Bit Timer/Counter

When the QEI module is not configured for the QEI mode, QEIM<2:0> = 001, the module can be configured as a simple 16-bit timer/counter. The setup and control of the auxiliary timer is accomplished through the QEICON SFR register. This timer functions identically to Timer1. The QEA pin is used as the timer clock input.

When configured as a timer, the POSCNT register serves as the Timer Count register and the MAXCNT register serves as the Period register. When a Timer/ Period register match occurs, the QEI interrupt flag will be asserted.

The only exception between the general purpose timers and this timer is the added feature of external up/down input select. When the UPDN pin is asserted high, the timer will increment up. When the UPDN pin is asserted low, the timer will be decremented.

| Note: | Changing the operational mode (i.e., from    |

|-------|----------------------------------------------|

|       | QEI to timer or vice versa), will not affect |

|       | the Timer/Position Count register contents.  |

The UPDN control/status bit (QEICON<11>) can be used to select the count direction state of the Timer register. When UPDN = 1, the timer will count up. When UPDN = 0, the timer will count down.

In addition, control bit, UPDN\_SRC (QEICON<0>), determines whether the timer count direction state is based on the logic state written into the UPDN control/ status bit (QEICON<11>), or the QEB pin state. When UPDN\_SRC = 1, the timer count direction is controlled from the QEB pin. Likewise, when UPDN\_SRC = 0, the timer count direction is controlled by the UPDN bit.

**Note:** This timer does not support the External Asynchronous Counter mode of operation. If using an external clock source, the clock will automatically be synchronized to the internal instruction cycle.

#### 14.6 QEI Module Operation During CPU Sleep Mode

#### 14.6.1 QEI OPERATION DURING CPU SLEEP MODE

The QEI module will be halted during the CPU Sleep mode.

#### 14.6.2 TIMER OPERATION DURING CPU SLEEP MODE

During CPU Sleep mode, the timer will not operate, because the internal clocks are disabled.

### 15.1.4 DOUBLE-UPDATE MODE

In the Double-Update mode (PTMOD<1:0> = 11), an interrupt event is generated each time the PTMR register is equal to zero, as well as each time a period match occurs. The postscaler selection bits have no effect in this mode of the timer.

The Double-Update mode provides two additional functions to the user. First, the control loop bandwidth is doubled because the PWM duty cycles can be updated, twice per period. Second, asymmetrical center-aligned PWM waveforms can be generated, which are useful for minimizing output waveform distortion in certain motor control applications.

**Note:** Programming a value of 0x0001 in the Period register could generate a continuous interrupt pulse, and hence, must be avoided.

#### 15.1.5 PWM TIME BASE PRESCALER

The input clock to PTMR (Fosc/4), has prescaler options of 1:1, 1:4, 1:16, or 1:64, selected by control bits, PTCKPS<1:0> in the PTCON SFR. The prescaler counter is cleared when any of the following occurs:

- A write to the PTMR register

- A write to the PTCON register

- Any device Reset

The PTMR register is not cleared when PTCON is written.

#### 15.1.6 PWM TIME BASE POSTSCALER

The match output of PTMR can optionally be postscaled through a 4-bit postscaler (which gives a 1:1 to 1:16 scaling).

The postscaler counter is cleared when any of the following occurs:

- A write to the PTMR register

- A write to the PTCON register

- Any device Reset

The PTMR register is not cleared when the PTCON register is written.

### 15.2 PWM Period

PTPER is a 15-bit register and is used to set the counting period for the PWM time base. PTPER is a double- buffered register. The PTPER buffer contents are loaded into the PTPER register at the following instances:

- <u>Free-Running and Single-Shot modes:</u> When the PTMR register is reset to zero after a match with the PTPER register.

- <u>Continuous Up/Down Count modes:</u> When the PTMR register is zero.

The value held in the PTPER buffer is automatically loaded into the PTPER register when the PWM time base is disabled (PTEN = 0).

The PWM period can be determined using Equation 15-1:

#### EQUATION 15-1: PWM PERIOD (FREE-RUNNING MODE)

$$T_{PWM} = T_{CY} \bullet (PTPER + 1) \bullet PTMR Prescale Value$$

If the PWM time base is configured for one of the Continuous Up/Down Count modes, the PWM period is given by Equation 15-2.

#### EQUATION 15-2: PWM PERIOD (UP/DOWN COUNTING MODE)

$$T_{PWM} = T_{CY} \bullet 2 \bullet (PTPER + 1) \bullet PTMR Prescale Value$$

The maximum resolution (in bits) for a given device oscillator and PWM frequency can be determined using Equation 15-3:

#### EQUATION 15-3: PWM RESOLUTION

$$Resolution = \frac{\log (2 \bullet T_{PWM} / T_{CY})}{\log (2)}$$

## 17.2 I<sup>2</sup>C Module Addresses

The I2CADD register contains the Slave mode addresses. The register is a 10-bit register.

If the A10M bit (I2CCON<10>) is '0', the address is interpreted by the module as a 7-bit address. When an address is received, it is compared to the 7 LSbs of the I2CADD register.

If the A10M bit is '1', the address is assumed to be a 10-bit address. When an address is received, it will be compared with the binary value, '11110 A9 A8' (where A9 and A8 are two Most Significant bits of I2CADD). If that value matches, the next address will be compared with the Least Significant 8 bits of I2CADD, as specified in the 10-bit addressing protocol.

The 7-bit  $I^2C$  slave addresses supported by the dsPIC30F are shown in Table 17-1.

# TABLE 17-1:7-BIT I²C™ SLAVEADDRESSES

| Address   | Description                           |

|-----------|---------------------------------------|

| 0x00      | General Call Address or Start Byte    |

| 0x01-0x03 | Reserved                              |

| 0x04-0x07 | HS mode Master Codes                  |

| 0x08-0x77 | Valid 7-Bit Addresses                 |

| 0x78-0x7B | Valid 10-Bit Addresses (lower 7 bits) |

| 0x7C-0x7F | Reserved                              |

## 17.3 I<sup>2</sup>C 7-Bit Slave Mode Operation

Once enabled (I2CEN = 1), the slave module will wait for a Start bit to occur (i.e., the I<sup>2</sup>C module is 'Idle'). Following the detection of a Start bit, 8 bits are shifted into I2CRSR and the address is compared against I2CADD. In 7-bit mode (A10M = 0), bits I2CADD<6:0> are compared against I2CRSR<7:1> and I2CRSR<0> is the R\_W bit. All incoming bits are sampled on the rising edge of SCL.

If an address match occurs, an Acknowledgement will be sent, and the Slave Event Interrupt Flag (SI2CIF) is set on the falling edge of the ninth (ACK) bit. The address match does not affect the contents of the I2CRCV buffer or the RBF bit.

## 17.3.1 SLAVE TRANSMISSION

If the R\_W bit received is a '1', then the serial port will go into Transmit mode. It will send an ACK on the ninth bit and then hold SCL to '0' until the CPU responds by writing to I2CTRN. SCL is released by setting the SCLREL bit, and 8 bits of data are shifted out. Data bits are shifted out on the falling edge of SCL, such that SDA is valid during SCL high. The interrupt pulse is sent on the falling edge of the ninth clock pulse, regardless of the status of the ACK received from the master.

## 17.3.2 SLAVE RECEPTION

If the R\_W bit received is a '0' during an address match, then Receive mode is initiated. Incoming bits are sampled on the rising edge of SCL. After 8 bits are received, if I2CRCV is not full or I2COV is not set, I2CRSR is transferred to I2CRCV. ACK is sent on the ninth clock.

If the RBF flag is set, indicating that I2CRCV is still holding data from a previous operation (RBF = 1), then ACK is not sent; however, the interrupt pulse is generated. In the case of an overflow, the contents of the I2CRSR are not loaded into the I2CRCV.

## 17.4 I<sup>2</sup>C 10-Bit Slave Mode Operation

In 10-bit mode, the basic receive and transmit operations are the same as in the 7-bit mode. However, the criteria for address match is more complex.

The I<sup>2</sup>C specification dictates that a slave must be addressed for a write operation, with two address bytes following a Start bit.

The A10M bit is a control bit that signifies that the address in I2CADD is a 10-bit address rather than a 7-bit address. The address detection protocol for the first byte of a message address is identical for 7-bit and 10-bit messages, but the bits being compared are different.

I2CADD holds the entire 10-bit address. Upon receiving an address following a Start bit, I2CRSR<7:3> is compared against a literal '11110' (the default 10-bit address) and I2CRSR<2:1> are compared against I2CADD<9:8>. If a match occurs and if  $R_W = 0$ , the interrupt pulse is sent. The ADD10 bit will be cleared to indicate a partial address match. If a match fails or  $R_W = 1$ , the ADD10 bit is cleared and the module returns to the Idle state.

The low byte of the address is then received and compared with I2CADD<7:0>. If an address match occurs, the interrupt pulse is generated and the ADD10 bit is set, indicating a complete 10-bit address match. If an address match did not occur, the ADD10 bit is cleared and the module returns to the Idle state.

Note: The I2CRCV will be loaded if the I2COV bit = 1 and the RBF flag = 0. In this case, a read of the I2CRCV was performed, but the user did not clear the state of the I2COV bit before the next receive occurred. The Acknowledgement is not sent ( $\overline{ACK} = 1$ ) and the I2CRCV is updated.

## TABLE 18-1: UART1 REGISTER MAP<sup>(1)</sup>

| SFR Name                                 | Addr. | Bit 15  | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 Bit 6 Bit 5 Bit 4 |                     |       | Bit 4     | Bit 3   | Bit 2  | Bit 1  | Bit 0 | Reset State         |  |  |

|------------------------------------------|-------|---------|--------|--------|--------|--------|--------|-------|-------|-------------------------|---------------------|-------|-----------|---------|--------|--------|-------|---------------------|--|--|

| U1MODE                                   | 020C  | UARTEN  | —      | USIDL  | —      | —      | ALTIO  | —     | —     | WAKE                    | LPBACK              | ABAUD | —         | —       | PDSEL1 | PDSEL0 | STSEL | 0000 0000 0000 0000 |  |  |

| U1STA                                    | 020E  | UTXISEL | —      | —      | —      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISEL1                | URXISEL0            | ADDEN | RIDLE     | PERR    | FERR   | OERR   | URXDA | 0000 0001 0001 0000 |  |  |

| U1TXREG                                  | 0210  | _       | —      | —      | —      | —      | —      | —     | UTX8  |                         |                     | Tr    | ansmit Re | egister |        |        |       | 0000 000u uuuu uuuu |  |  |

| U1RXREG                                  | 0212  | Ι       | —      | —      | —      |        | —      |       | URX8  | Receive Register        |                     |       |           |         |        |        |       | 0000 0000 0000 0000 |  |  |

| U1BRG 0214 Baud Rate Generator Prescaler |       |         |        |        |        |        |        |       |       |                         | 0000 0000 0000 0000 |       |           |         |        |        |       |                     |  |  |

Legend: u = uninitialized bit; — = unimplemented bit, read as '0'

Note 1: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

## TABLE 18-2: UART2 REGISTER MAP<sup>(1)</sup> (NOT AVAILABLE ON dsPIC30F3010)

| SFR<br>Name | Addr.                                    | Bit 15  | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7            | Bit 6               | Bit 5 | Bit 4      | Bit 3   | Bit 2  | Bit 1  | Bit 0               | Reset State         |

|-------------|------------------------------------------|---------|--------|--------|--------|--------|--------|-------|-------|------------------|---------------------|-------|------------|---------|--------|--------|---------------------|---------------------|

| U2MODE      | 0216                                     | UARTEN  | —      | USIDL  | —      | _      | —      | _     | _     | WAKE             | LPBACK              | ABAUD | —          | -       | PDSEL1 | PDSEL0 | STSEL               | 0000 0000 0000 0000 |

| U2STA       | 0218                                     | UTXISEL | —      | _      | —      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISEL1         | URXISEL0            | ADDEN | RIDLE      | PERR    | FERR   | OERR   | URXDA               | 0000 0001 0001 0000 |

| U2TXREG     | 021A                                     | -       | —      | _      | —      |        |        |       | UTX8  |                  |                     | Ti    | ransmit Re | egister |        |        |                     | 0000 000u uuuu uuuu |

| U2RXREG     | 021C                                     | -       | —      | _      | —      |        |        |       | URX8  | Receive Register |                     |       |            |         |        |        | 0000 0000 0000 0000 |                     |

| U2BRG       | U2BRG 021E Baud Rate Generator Prescaler |         |        |        |        |        |        |       |       |                  | 0000 0000 0000 0000 |       |            |         |        |        |                     |                     |

Legend: u = uninitialized bit; - = unimplemented bit, read as '0'

Note 1: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

# 20.3.1.1 POR with Long Crystal Start-up Time (with FSCM Enabled)

The oscillator start-up circuitry is not linked to the POR circuitry. Some crystal circuits (especially low-frequency crystals) will have a relatively long start-up time. Therefore, one or more of the following conditions is possible after the POR timer and the PWRT have expired:

- The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has NOT expired (if a crystal oscillator is used).

- The PLL has not achieved a LOCK (if PLL is used).

If the FSCM is enabled and one of the above conditions is true, then a clock failure trap will occur. The device will automatically switch to the FRC oscillator and the user can switch to the desired crystal oscillator in the trap ISR.

## 20.3.1.2 Operating without FSCM and PWRT

If the FSCM is disabled and the Power-up Timer (PWRT) is also disabled, then the device will exit rapidly from Reset on power-up. If the clock source is FRC, LPRC, EXTRC or EC, it will be active immediately.

If the FSCM is disabled and the system clock has not started, the device will be in a frozen state at the Reset vector until the system clock starts. From the user's perspective, the device will appear to be in Reset until a system clock is available.

#### 20.3.2 BOR: PROGRAMMABLE BROWN-OUT RESET

The BOR (Brown-out Reset) module is based on an internal voltage reference circuit. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (i.e., missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

The BOR module allows selection of one of the following voltage trip points:

- 2.6V-2.71V

- 4.1V-4.4V

- 4.58V-4.73V

**Note:** The BOR voltage trip points indicated here are nominal values provided for design guidance only.

A BOR will generate a Reset pulse which will reset the device. The BOR will select the clock source, based on the device Configuration bit values (FOS<1:0> and FPR<3:0>). Furthermore, if an oscillator mode is selected, the BOR will activate the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, then the clock will be held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the POR time-out (TPOR) and the PWRT time-out (TPWRT) will be applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100  $\mu$ s is applied. The total delay in this case is (TPOR + TFSCM).

The BOR status bit (RCON<1>) will be set to indicate that a BOR has occurred. The BOR circuit, if enabled, will continue to operate while in Sleep or Idle modes and will reset the device should VDD fall below the BOR threshold voltage.

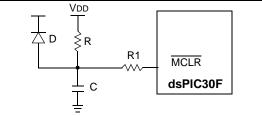

#### EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

- Note 1: External Power-on Reset circuit is required only if the VDD power-up slope is too slow. The diode D helps discharge the capacitor quickly when VDD powers down.

- 2: R should be suitably chosen so as to make sure that the voltage drop across R does not violate the device's electrical specification.

- 3: R1 should be suitably chosen so as to limit any current flowing into MCLR from external capacitor C, in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

- Note: Dedicated supervisory devices, such as the MCP1XX and MCP8XX, may also be used as an external Power-on Reset circuit.

Table 20-5 shows the Reset conditions for the RCON register. Since the control bits within the RCON register are R/W, the information in the table implies that all the bits are negated prior to the action specified in the condition column.

| Condition                                 | Program<br>Counter    | TRAPR | IOPUWR | EXTR | SWR | WDTO | IDLE | SLEEP | POR | BOR |

|-------------------------------------------|-----------------------|-------|--------|------|-----|------|------|-------|-----|-----|

| Power-on Reset                            | 0x000000              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 1   | 1   |

| Brown-out Reset                           | 0x000000              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 1   |

| MCLR Reset during Normal Operation        | 0x000000              | 0     | 0      | 1    | 0   | 0    | 0    | 0     | 0   | 0   |

| Software Reset during<br>Normal Operation | 0x000000              | 0     | 0      | 0    | 1   | 0    | 0    | 0     | 0   | 0   |

| MCLR Reset during Sleep                   | 0x000000              | 0     | 0      | 1    | 0   | 0    | 0    | 1     | 0   | 0   |

| MCLR Reset during Idle                    | 0x000000              | 0     | 0      | 1    | 0   | 0    | 1    | 0     | 0   | 0   |

| WDT Time-out Reset                        | 0x000000              | 0     | 0      | 0    | 0   | 1    | 0    | 0     | 0   | 0   |

| WDT Wake-up                               | PC + 2                | 0     | 0      | 0    | 0   | 1    | 0    | 1     | 0   | 0   |

| Interrupt Wake-up from Sleep              | PC + 2 <sup>(1)</sup> | 0     | 0      | 0    | 0   | 0    | 0    | 1     | 0   | 0   |

| Clock Failure Trap                        | 0x000004              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

| Trap Reset                                | 0x000000              | 1     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

| Illegal Operation Trap                    | 0x000000              | 0     | 1      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

### TABLE 20-5: INITIALIZATION CONDITION FOR RCON REGISTER CASE 1

**Legend:** u = unchanged, x = unknown

Note 1: When the wake-up is due to an enabled interrupt, the PC is loaded with the corresponding interrupt vector.

Table 20-6 shows a second example of the bit conditions for the RCON register. In this case, it is not assumed the user has set/cleared specific bits prior to action specified in the condition column.

#### TABLE 20-6: INITIALIZATION CONDITION FOR RCON REGISTER CASE 2

| Condition                                 | Program<br>Counter    | TRAPR | IOPUWR | EXTR | SWR | WDTO | IDLE | SLEEP | POR | BOR |

|-------------------------------------------|-----------------------|-------|--------|------|-----|------|------|-------|-----|-----|

| Power-on Reset                            | 0x000000              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 1   | 1   |

| Brown-out Reset                           | 0x000000              | u     | u      | u    | u   | u    | u    | u     | 0   | 1   |

| MCLR Reset during Normal<br>Operation     | 0x000000              | u     | u      | 1    | 0   | 0    | 0    | 0     | u   | u   |

| Software Reset during<br>Normal Operation | 0x000000              | u     | u      | 0    | 1   | 0    | 0    | 0     | u   | u   |

| MCLR Reset during Sleep                   | 0x000000              | u     | u      | 1    | u   | 0    | 0    | 1     | u   | u   |

| MCLR Reset during Idle                    | 0x000000              | u     | u      | 1    | u   | 0    | 1    | 0     | u   | u   |

| WDT Time-out Reset                        | 0x000000              | u     | u      | 0    | 0   | 1    | 0    | 0     | u   | u   |

| WDT Wake-up                               | PC + 2                | u     | u      | u    | u   | 1    | u    | 1     | u   | u   |

| Interrupt Wake-up from<br>Sleep           | PC + 2 <sup>(1)</sup> | u     | u      | u    | u   | u    | u    | 1     | u   | u   |

| Clock Failure Trap                        | 0x000004              | u     | u      | u    | u   | u    | u    | u     | u   | u   |

| Trap Reset                                | 0x000000              | 1     | u      | u    | u   | u    | u    | u     | u   | u   |

| Illegal Operation Reset                   | 0x000000              | u     | 1      | u    | u   | u    | u    | u     | u   | u   |

**Legend:** u = unchanged, x = unknown

Note 1: When the wake-up is due to an enabled interrupt, the PC is loaded with the corresponding interrupt vector.

## 20.7 In-Circuit Debugger

When MPLAB<sup>®</sup> ICD 2 is selected as a debugger, the in-circuit debugging functionality is enabled. This function allows simple debugging functions when used with MPLAB IDE. When the device has this feature enabled, some of the resources are not available for general use. These resources include the first 80 bytes of data RAM and two I/O pins.

One of four pairs of debug I/O pins may be selected by the user using configuration options in MPLAB IDE. These pin pairs are named EMUD/EMUC, EMUD1/ EMUC1, EMUD2/EMUC2 and EMUD3/EMUC3. In each case, the selected EMUD pin is the Emulation/ Debug Data line, and the EMUC pin is the Emulation/ Debug Clock line. These pins will interface to the MPLAB ICD 2 module available from Microchip. The selected pair of debug I/O pins is used by MPLAB ICD 2 to send commands and receive responses, as well as to send and receive data. To use the in-circuit debugger function of the device, the design must implement ICSP connections to MCLR, VDD, VSS, PGC, PGD and the selected EMUDx/EMUCx pin pair.

This gives rise to two possibilities:

- If EMUD/EMUC is selected as the debug I/O pin pair, then only a 5-pin interface is required, as the EMUD and EMUC pin functions are multiplexed with the PGD and PGC pin functions in all dsPIC30F devices.

- If EMUD1/EMUC1, EMUD2/EMUC2 or EMUD3/ EMUC3 is selected as the debug I/O pin pair, then a 7-pin interface is required, as the EMUDx/EMUCx pin functions (x = 1, 2 or 3) are not multiplexed with the PGD and PGC pin functions.

# dsPIC30F3010/3011

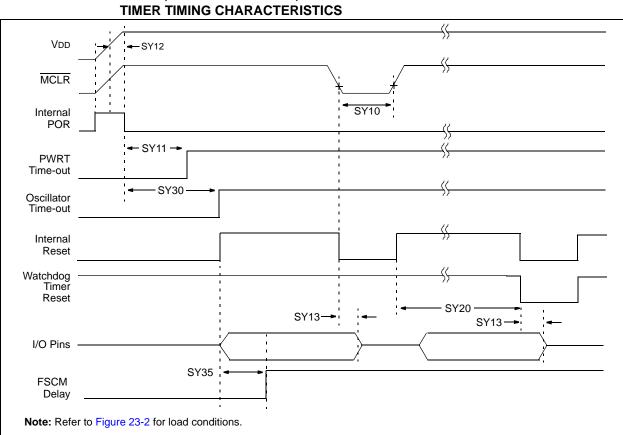

## FIGURE 23-5: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING CHARACTERISTICS

# TABLE 23-20:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET TIMING REQUIREMENTS

|              |                         |                                                             |                   | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                   |                |                                                  |  |  |  |  |

|--------------|-------------------------|-------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|--------------------------------------------------|--|--|--|--|

| Param<br>No. | Symbol                  | Characteristic <sup>(1)</sup>                               | Min               | Тур <sup>(2)</sup>                                                                                                                                                                                                                                                                  | Max               | Units          | Conditions                                       |  |  |  |  |

| SY10         | TmcL                    | MCLR Pulse Width (low)                                      | 2                 | —                                                                                                                                                                                                                                                                                   | _                 | μS             | -40°C to +85°C                                   |  |  |  |  |

| SY11         | TPWRT                   | Power-up Timer Period                                       | 2<br>10<br>43     | 4<br>16<br>64                                                                                                                                                                                                                                                                       | 8<br>32<br>128    | ms             | -40°C to +85°C,<br>VDD = 5V<br>User programmable |  |  |  |  |

| SY12         | TPOR                    | Power-on Reset Delay                                        | 3                 | 10                                                                                                                                                                                                                                                                                  | 30                | μS             | -40°C to +85°C                                   |  |  |  |  |

| SY13         | Tioz                    | I/O High-impedance from MCLR<br>Low or Watchdog Timer Reset | —                 | 0.8                                                                                                                                                                                                                                                                                 | 1.0               | μS             |                                                  |  |  |  |  |

| SY20         | Twdt1<br>Twdt2<br>Twdt3 | Watchdog Timer Time-out Period<br>(no prescaler)            | 1.1<br>1.2<br>1.3 | 2.0<br>2.0<br>2.0                                                                                                                                                                                                                                                                   | 6.6<br>5.0<br>4.0 | ms<br>ms<br>ms | VDD = 2.5V<br>VDD = 3.3V, ±10%<br>VDD = 5V, ±10% |  |  |  |  |

| SY25         | TBOR                    | Brown-out Reset Pulse Width <sup>(3)</sup>                  | 100               | —                                                                                                                                                                                                                                                                                   | _                 | μS             | $VDD \le VBOR (D034)$                            |  |  |  |  |

| SY30         | Tost                    | Oscillator Start-up Timer Period                            |                   | 1024 Tosc                                                                                                                                                                                                                                                                           | _                 | _              | Tosc = OSC1 period                               |  |  |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**2:** Data in "Typ" column is at 5V, 25°C unless otherwise stated.

**3:** Refer to Figure 23-1 and Table 23-10 for BOR.

## INDEX

## Numerics

| 10-Bit HighBSpeed A/D                                    |    |

|----------------------------------------------------------|----|

| Connection Considerations13                              | 32 |

| 10-Bit High-Speed A/D                                    |    |

| A/D Acquisition Requirements                             | 30 |

| Aborting a Conversion12                                  |    |

| ADCHS                                                    |    |

| ADCON1 12                                                |    |

| ADCON2                                                   | 23 |

| ADCON3 12                                                | 23 |

| ADCSSL12                                                 | 23 |

| ADPCFG                                                   | 23 |

| Configuring Analog Port Pins13                           | 32 |

| Conversion Operation12                                   | 25 |

| Effects of a Reset13                                     | 31 |

| Operation During CPU Idle Mode13                         | 31 |

| Operation During CPU Sleep Mode                          | 31 |

| Output Formats                                           |    |

| Power-Down Modes13                                       | 31 |

| Programming the Start of Conversion Trigger 12           | 26 |

| Register Map13                                           |    |

| Result Buffer 12                                         | 25 |

| Sampling Requirements13                                  |    |

| Selecting the Conversion Sequence                        |    |

| 10-Bit High-Speed Analog-to-Digital Converter (ADC) Modu |    |

| 123                                                      |    |

| 16-Bit Up/Down Position Counter Mode                     | 38 |

| Count Direction Status                                   |    |

| Error Checking                                           |    |

## **A**

| A/D                                       |     |

|-------------------------------------------|-----|

| 1 Msps Configuration Guideline            | 128 |

| 600 ksps Configuration Guideline          | 129 |

| Conversion Rate Parameters                | 127 |

| Selecting the Conversion Clock            | 126 |

| Voltage Reference Schematic               | 128 |

| AC Characteristics                        | 172 |

| Load Conditions                           |     |

| AC Temperature and Voltage Specifications | 172 |

| ADC                                       |     |

| 750 ksps Configuration Guideline          |     |

| Conversion Speeds                         | 127 |

| Address Generator Units                   | 37  |

| Alternate 16-Bit Timer/Counter            | 89  |

| Alternate Vector Table                    | 47  |

| Assembler                                 |     |

| MPASM Assembler                           |     |

| Automatic Clock Stretch                   |     |

| During 10-Bit Addressing (STREN = 1)      | 110 |

| During 7-Bit Addressing (STREN = 1)       |     |

| Receive Mode                              |     |

| Transmit Mode                             | 110 |

|                                           |     |

## В

| Band Gap Start-up Time  |     |

|-------------------------|-----|

| Requirements            | 179 |

| Timing Characteristics  | 179 |

| Barrel Shifter          | 24  |

| Bit-Reversed Addressing |     |

| Example                 |     |

| Implementation          |     |

| Modifier Values (table) |     |

|                         |     |

| Sequence Table (16-Entry) 41         |

|--------------------------------------|

| Block Diagrams                       |

| 10-Bit High-Speed ADC Functional 124 |

| 16-Bit Timer1 Module 66              |

| 16-Bit Timer4                        |

| 16-Bit Timer577                      |

| 32-Bit Timer4/575                    |

| Dedicated Port Structure 59          |

| DSP Engine                           |

| dsPIC30F301011                       |

| dsPIC30F3011 10                      |

| External Power-on Reset Circuit 143  |

| I <sup>2</sup> C                     |

| Input Capture Mode79                 |

| Oscillator System                    |

| Output Compare Mode 83               |

| PWM Module                           |

| Quadrature Encoder Interface         |

| Reset System 141                     |

| Shared Port Structure 60             |

| SPI                                  |

| SPI Master/Slave Connection 104      |

| UART Receiver 116                    |

| UART Transmitter 115                 |

| BOR Characteristics 171              |

| BOR. See Brown-out Reset.            |

| Brown-out Reset                      |

| Timing Requirements 178              |

| Brown-out Reset (BOR) 135            |

## С

| C Compilers                          |       |

|--------------------------------------|-------|

| MPLAB C18                            | . 160 |

| Center-Aligned PWM                   | 97    |

| CLKOUT and I/O Timing                |       |

| Characteristics                      | . 177 |

| Requirements                         | . 177 |

| Code Examples                        |       |

| Data EEPROM Block Erase              | 56    |

| Data EEPROM Block Write              | 58    |

| Data EEPROM Read                     |       |

| Data EEPROM Word Erase               | 56    |

| Data EEPROM Word Write               | 57    |

| Erasing a Row of Program Memory      | 51    |

| Initiating a Programming Sequence    | 52    |

| Loading Write Latches                | 52    |

| Code Protection                      | . 135 |

| Complementary PWM Operation          | 98    |

| Configuring Analog Port Pins         |       |

| Control Registers                    |       |

| NVMADR                               | 50    |

| NVMADRU                              | 50    |

| NVMCON                               | 50    |

| NVMKEY                               | 50    |

| Core Overview                        | 17    |

| Core Register Map                    | 33    |

| Customer Change Notification Service | . 219 |

| Customer Notification Service        | . 219 |

| Customer Support                     | . 219 |

| D                                    |       |

| Data Access from Program Memory        |    |

|----------------------------------------|----|

| Using Program Space Visibility         | 28 |

| Data Accumulators and Adder/Subtracter | 22 |