#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                        |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                         |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 20 MIPS                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                 |

| Number of I/O              | 30                                                                            |

| Program Memory Size        | 24KB (8K x 24)                                                                |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | 1K x 8                                                                        |

| RAM Size                   | 1K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 44-TQFP                                                                       |

| Supplier Device Package    | 44-TQFP (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3011-20i-pt |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

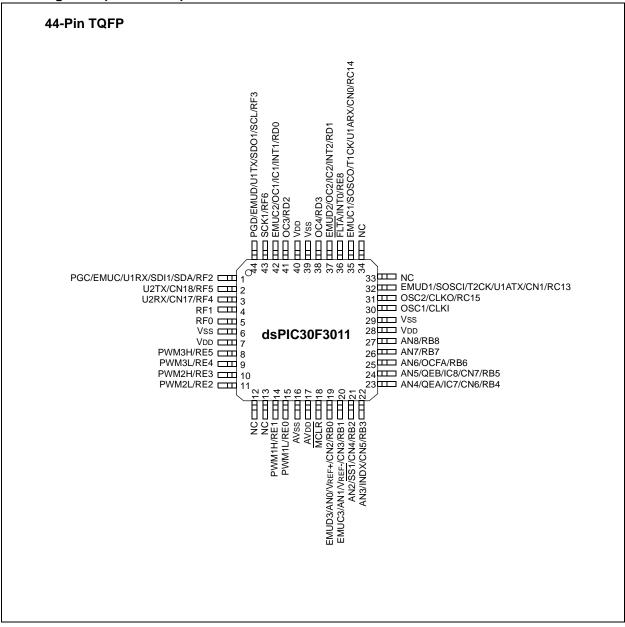

# **Pin Diagrams (Continued)**

| Pin Name                                       | Pin<br>Type               | Buffer<br>Type                | Description                                                                                                                                                                                                                 |

|------------------------------------------------|---------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1<br>OSC2                                   | I<br>I/O                  | ST/CMOS                       | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. |

| PGD<br>PGC                                     | I/O<br>I                  | ST<br>ST                      | In-Circuit Serial Programming data input/output pin.<br>In-Circuit Serial Programming clock input pin.                                                                                                                      |

| RB0-RB8                                        | I/O                       | ST                            | PORTB is a bidirectional I/O port.                                                                                                                                                                                          |

| RC13-RC15                                      | 5 I/O                     | ST                            | PORTC is a bidirectional I/O port.                                                                                                                                                                                          |

| RD0-RD3                                        | I/O                       | ST                            | PORTD is a bidirectional I/O port.                                                                                                                                                                                          |

| RE0-RE5,<br>RE8                                | I/O                       | ST                            | PORTE is a bidirectional I/O port.                                                                                                                                                                                          |

| RF0-RF6                                        | I/O                       | ST                            | PORTF is a bidirectional I/O port.                                                                                                                                                                                          |

| SCK1<br>SDI1<br>SDO1<br>SS1                    | I/O<br>I<br>O<br>I        | ST<br>ST<br>—<br>ST           | Synchronous serial clock input/output for SPI1.<br>SPI1 Data In.<br>SPI1 Data Out.<br>SPI1 Slave Synchronization.                                                                                                           |

| SCL<br>SDA                                     | I/O<br>I/O                | ST<br>ST                      | Synchronous serial clock input/output for $I^2C$ .<br>Synchronous serial data input/output for $I^2C$ .                                                                                                                     |

| SOSCO<br>SOSCI                                 | 0<br>                     |                               | 32 kHz low-power oscillator crystal output.<br>32 kHz low-power oscillator crystal input. ST buffer when configured in RC<br>mode; CMOS otherwise.                                                                          |

| T1CK<br>T2CK                                   |                           | ST<br>ST                      | Timer1 external clock input.<br>Timer2 external clock input.                                                                                                                                                                |

| U1RX<br>U1TX<br>U1ARX<br>U1ATX<br>U2RX<br>U2TX | <br>0<br> <br>0<br> <br>0 | ST<br>—<br>ST<br>—<br>ST<br>— | UART1 Receive.<br>UART1 Transmit.<br>UART1 Alternate Receive.<br>UART1 Alternate Transmit.<br>UART2 Receive.<br>UART2 Transmit.                                                                                             |

| Vdd                                            | Р                         | _                             | Positive supply for logic and I/O pins.                                                                                                                                                                                     |

| Vss                                            | Р                         | —                             | Ground reference for logic and I/O pins.                                                                                                                                                                                    |

| Vref+                                          | I                         | Analog                        | Analog Voltage Reference (High) input.                                                                                                                                                                                      |

| Vref-                                          |                           | Analog                        | Analog Voltage Reference (Low) input.                                                                                                                                                                                       |

| Legend: C<br>S                                 | ST = So                   |                               | r input with CMOS levels Analog = Analog input<br>P = Power                                                                                                                                                                 |

TABLE 1-1: dsPIC30F3011 I/O PIN DESCRIPTIONS (CONTINUED)

| IADLE | 4-2. | DII-NE | VERSEI           | D ADDRESS SEQU |    |    | <b>NI</b> ) |                     |         |

|-------|------|--------|------------------|----------------|----|----|-------------|---------------------|---------|

|       |      |        | lormal<br>ddress |                |    |    |             | -Reverse<br>Address |         |

| A3    | A2   | A1     | A0               | Decimal        | A3 | A2 | A1          | A0                  | Decimal |

| 0     | 0    | 0      | 0                | 0              | 0  | 0  | 0           | 0                   | 0       |

| 0     | 0    | 0      | 1                | 1              | 1  | 0  | 0           | 0                   | 8       |

| 0     | 0    | 1      | 0                | 2              | 0  | 1  | 0           | 0                   | 4       |

| 0     | 0    | 1      | 1                | 3              | 1  | 1  | 0           | 0                   | 12      |

| 0     | 1    | 0      | 0                | 4              | 0  | 0  | 1           | 0                   | 2       |

| 0     | 1    | 0      | 1                | 5              | 1  | 0  | 1           | 0                   | 10      |

| 0     | 1    | 1      | 0                | 6              | 0  | 1  | 1           | 0                   | 6       |

| 0     | 1    | 1      | 1                | 7              | 1  | 1  | 1           | 0                   | 14      |

| 1     | 0    | 0      | 0                | 8              | 0  | 0  | 0           | 1                   | 1       |

| 1     | 0    | 0      | 1                | 9              | 1  | 0  | 0           | 1                   | 9       |

| 1     | 0    | 1      | 0                | 10             | 0  | 1  | 0           | 1                   | 5       |

| 1     | 0    | 1      | 1                | 11             | 1  | 1  | 0           | 1                   | 13      |

| 1     | 1    | 0      | 0                | 12             | 0  | 0  | 1           | 1                   | 3       |

| 1     | 1    | 0      | 1                | 13             | 1  | 0  | 1           | 1                   | 11      |

| 1     | 1    | 1      | 0                | 14             | 0  | 1  | 1           | 1                   | 7       |

| 1     | 1    | 1      | 1                | 15             | 1  | 1  | 1           | 1                   | 15      |

## TABLE 4-2: BIT-REVERSED ADDRESS SEQUENCE (16-ENTRY)

## TABLE 4-3: BIT-REVERSED ADDRESS MODIFIER VALUES FOR XBREV REGISTER

| Buffer Size (Words) | XB<14:0> Bit-Reversed Address Modifier Value |

|---------------------|----------------------------------------------|

| 512                 | 0x0100                                       |

| 256                 | 0x0080                                       |

| 128                 | 0x0040                                       |

| 64                  | 0x0020                                       |

| 32                  | 0x0010                                       |

| 16                  | 0x0008                                       |

| 8                   | 0x0004                                       |

| 4                   | 0x0002                                       |

| 2                   | 0x0001                                       |

# 6.4 RTSP Operation

The dsPIC30F Flash program memory is organized into rows and panels. Each row consists of 32 instructions or 96 bytes. Each panel consists of 128 rows or  $4K \times 24$  instructions. RTSP allows the user to erase one row (32 instructions) at a time and to program 32 instructions at one time.

Each panel of program memory contains write latches that hold 32 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the panel write latches. The data to be programmed into the panel is loaded in sequential order into the write latches; instruction 0, instruction 1, etc. The addresses loaded must always be from an even group of 32 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the write latches. Programming is performed by setting the special bits in the NVMCON register. 32 TBLWTL and four TBLWTH instructions are required to load the 32 instructions.

All of the table write operations are single-word writes (2 instruction cycles), because only the table latches are written.

After the latches are written, a programming operation needs to be initiated to program the data.

The Flash program memory is readable, writable and erasable during normal operation over the entire VDD range.

# 6.5 RTSP Control Registers

The four SFRs used to read and write the program Flash memory are:

- NVMCON

- NVMADR

- NVMADRU

- NVMKEY

### 6.5.1 NVMCON REGISTER

The NVMCON register controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

### 6.5.2 NVMADR REGISTER

The NVMADR register is used to hold the lower two bytes of the effective address. The NVMADR register captures the EA<15:0> of the last table instruction that has been executed and selects the row to write.

#### 6.5.3 NVMADRU REGISTER

The NVMADRU register is used to hold the upper byte of the effective address. The NVMADRU register captures the EA<23:16> of the last table instruction that has been executed.

### 6.5.4 NVMKEY REGISTER

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 0x55 and 0xAA to the NVMKEY register. Refer to **Section 6.6 "Programming Operations"** for further details.

**Note:** The user can also directly write to the NVMADR and NVMADRU registers to specify a program memory address for erasing or programming.

NOTES:

# TABLE 8-2: dsPIC30F3010 PORT REGISTER MAP<sup>(1)</sup>

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset State         |

|-------------|-------|---------|---------|---------|--------|--------|--------|-------|--------|-------|-------|--------|--------|--------|--------|--------|--------|---------------------|

| TRISB       | 02C6  | _       | _       | _       | _      | _      | _      | _     | _      | _     | -     | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 0000 0000 0011 1111 |

| PORTB       | 02C8  | _       | _       | _       | _      | _      | _      | _     | _      | _     | _     | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | 0000 0000 0000 0000 |

| LATB        | 02CB  | _       | —       | —       | _      | _      | _      |       | _      | —     | _     | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | 0000 0000 0000 0000 |

| TRISC       | 02CC  | TRISC15 | TRISC14 | TRISC13 | _      | _      | _      |       | _      | —     | _     | _      | _      | —      | _      | _      | —      | 1110 0000 0000 0000 |

| PORTC       | 02CE  | RC15    | RC14    | RC13    | —      | —      |        |       | —      | —     |       | —      |        | _      |        |        | —      | 0000 0000 0000 0000 |

| LATC        | 02D0  | LATC15  | LATC14  | LATC13  | —      | —      |        |       | —      | —     |       | —      |        | _      |        |        | —      | 0000 0000 0000 0000 |

| TRISD       | 02D2  | _       | _       | —       | _      | _      | _      | _     | —      | —     | _     | —      | _      | —      | _      | TRISD1 | TRISD0 | 0000 0000 0000 0011 |

| PORTD       | 02D4  | _       | —       | —       | _      | _      | —      | —     | —      | —     | —     | —      | —      | —      | —      | RD1    | RD0    | 0000 0000 0000 0000 |

| LATD        | 02D6  | _       | _       | _       | _      | _      | _      | —     | —      | —     | _     | —      | _      | —      | _      | LATD1  | LATD0  | 0000 0000 0000 0000 |

| TRISE       | 02D8  |         | -       | -       | -      |        | —      | —     | TRISE8 | _     | —     | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 0000 0001 0011 1111 |

| PORTE       | 02DA  | _       | —       | —       | _      | _      | —      | —     | RE8    | —     | —     | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | 0000 0000 0000 0000 |

| LATE        | 02DC  | _       | _       | _       | _      | _      | _      | —     | LATE8  | —     | _     | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | 0000 0000 0000 0000 |

| TRISF       | 02EE  | —       | —       | _       | —      | —      | —      | —     | —      | —     | —     | —      | _      | TRISF3 | TRISF2 | —      | —      | 0000 0000 0000 1100 |

| PORTF       | 02E0  | _       | _       | _       | _      | _      | _      | —     | —      | —     | _     | —      | _      | RF3    | RF2    | —      | —      | 0000 0000 0000 0000 |

| LATF        | 02E2  |         | _       | _       |        |        |        |       | _      | _     |       | _      |        | LATF3  | LATF2  |        | _      | 0000 0000 0000 0000 |

**Legend:** — = unimplemented bit, read as '0'

Note 1: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields. Not all peripherals, and therefore their bit positions, are available on this device.

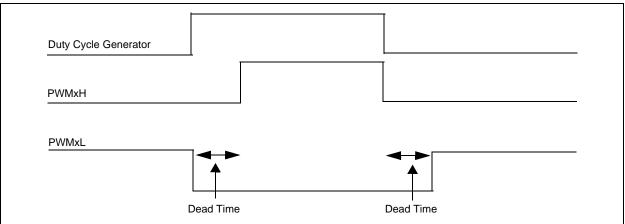

FIGURE 15-4: DEAD-TIME TIMING DIAGRAM

# 15.8 Independent PWM Output

An Independent PWM Output mode is required for driving certain types of loads. A particular PWM output pair is in the Independent Output mode when the corresponding PMOD bit in the PWMCON1 register is set. No dead-time control is implemented between adjacent PWM I/O pins when the module is operating in the Independent mode and both I/O pins are allowed to be active simultaneously.

In the Independent mode, each duty cycle generator is connected to both of the PWM I/O pins in an output pair. By using the associated Duty Cycle register and the appropriate bits in the OVDCON register, the user may select the following signal output options for each PWM I/O pin operating in the Independent mode:

- I/O pin outputs PWM signal

- I/O pin inactive

- I/O pin active

# 15.9 Single Pulse PWM Operation

The PWM module produces single pulse outputs when the PTCON control bits, PTMOD<1:0> = 10. Only edge-aligned outputs may be produced in the Single Pulse mode. In Single Pulse mode, the PWM I/O pin(s) are driven to the active state when the PTEN bit is set. When a match with a Duty Cycle register occurs, the PWM I/O pin is driven to the inactive state. When a match with the PTPER register occurs, the PTMR register is cleared, all active PWM I/O pins are driven to the inactive state, the PTEN bit is cleared and an interrupt is generated.

# 15.10 PWM Output Override

The PWM output override bits allow the user to manually drive the PWM I/O pins to specified logic states, independent of the duty cycle comparison units.

All control bits associated with the PWM output override function are contained in the OVDCON register. The upper half of the OVDCON register contains six bits, POVDxH<3:1> and POVDxL<3:1>, that determine which PWM I/O pins will be overridden. The lower half of the OVDCON register contains six bits, POUTxH<3:1> and POUTxL<3:1>, that determine the state of the PWM I/O pins when a particular output is overridden via the POVD bits.

## 15.10.1 COMPLEMENTARY OUTPUT MODE

When a PWMxL pin is driven active via the OVDCON register, the output signal is forced to be the complement of the corresponding PWMxH pin in the pair. Dead-time insertion is still performed when PWM channels are overridden manually.

## 15.10.2 OVERRIDE SYNCHRONIZATION

If the OSYNC bit in the PWMCON2 register is set, all output overrides performed via the OVDCON register are synchronized to the PWM time base. Synchronous output overrides occur at the following times:

- Edge-Aligned mode, when PTMR is zero.

- Center-Aligned modes, when PTMR is zero and when the value of PTMR matches PTPER.

# 16.3 Slave Select Synchronization

The SS1 pin allows a Synchronous Slave mode. The SPI must be configured in SPI Slave mode with SS1 pin control enabled (SSEN = 1). When the SS1 pin is low, transmission and reception are enabled and the SD01 pin is driven. When the SS1 pin goes high, the SD01 pin is no longer driven. Also, the SPI module is resynchronized and all counters/control circuitry are reset. Therefore, when the SS1 pin is asserted low again, transmission/reception will begin at the MSb, even if SS1 has been deasserted in the middle of a transmit/receive.

## 16.4 SPI Operation During CPU Sleep Mode

During Sleep mode, the SPI module is shut down. If the CPU enters Sleep mode while an SPI transaction is in progress, then the transmission and reception is aborted.

The transmitter and receiver will stop in Sleep mode. However, register contents are not affected by entering or exiting Sleep mode.

# 16.5 SPI Operation During CPU Idle Mode

When the device enters Idle mode, all clock sources remain functional. The SPISIDL bit (SPI1STAT<13>) selects if the SPI module will stop or continue on Idle. If SPISIDL = 0, the module will continue to operate when the CPU enters Idle mode. If SPISIDL = 1, the module will stop when the CPU enters Idle mode.

# TABLE 17-2: I<sup>2</sup>C<sup>™</sup> REGISTER MAP<sup>(1)</sup>

| SFR Name | Addr. | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7            | Bit 6 | Bit 5  | Bit 4      | Bit 3    | Bit 2 | Bit 1 | Bit 0               | Reset State         |

|----------|-------|---------|--------|---------|--------|--------|--------|--------|-------|------------------|-------|--------|------------|----------|-------|-------|---------------------|---------------------|

| I2CRCV   | 0200  | _       | —      | —       | —      | —      | _      | —      | —     |                  |       |        | Receive R  | legister |       |       |                     | 0000 0000 0000 0000 |

| I2CTRN   | 0202  | -       |        | —       | -      | —      |        | _      | —     |                  |       |        | Transmit F | Register |       |       |                     | 0000 0000 1111 1111 |

| I2CBRG   | 0204  | _       | —      | —       | _      | —      | _      | _      |       |                  |       | Baud F | Rate Gener | rator    |       |       |                     | 0000 0000 0000 0000 |

| I2CCON   | 0206  | I2CEN   | —      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN             | STREN | ACKDT  | ACKEN      | RCEN     | PEN   | RSEN  | SEN                 | 0001 0000 0000 0000 |

| 12CSTAT  | 0208  | ACKSTAT | TRSTAT | —       | —      | —      | BCL    | GCSTAT | ADD10 | IWCOL            | I2COV | D_A    | Р          | S        | R_W   | RBF   | TBF                 | 0000 0000 0000 0000 |

| I2CADD   | 020A  | —       |        | _       |        | _      |        |        |       | Address Register |       |        |            |          |       |       | 0000 0000 0000 0000 |                     |

Legend: — = unimplemented bit, read as '0'

Note 1: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

# 19.1 ADC Result Buffer

The module contains a 16-word, dual port, read-only buffer, called ADCBUF0...ADCBUFF, to buffer the ADC results. The RAM is 10 bits wide, but is read into different format 16-bit words. The contents of the sixteen ADC Conversion Result Buffer registers, ADCBUF0 through ADCBUFF, cannot be written by user software.

# 19.2 Conversion Operation

After the ADC module has been configured, the sample acquisition is started by setting the SAMP bit. Various sources, such as a programmable bit, timer time-outs and external events, will terminate acquisition and start a conversion. When the A/D conversion is complete, the result is loaded into ADCBUF0...ADCBUFF, and the A/D Interrupt Flag, ADIF, and the DONE bit are set after the number of samples specified by the SMPI bit.

The following steps should be followed for doing an A/D conversion:

- Configure the ADC module:

- Configure analog pins, voltage reference and digital I/O

- Select A/D input channels

- Select A/D conversion clock

- Select A/D conversion trigger

- Turn on A/D module

- Configure A/D interrupt (if required):

- Clear ADIF bit

- Select A/D interrupt priority

- Start sampling

- Wait the required acquisition time

- Trigger acquisition end; start conversion

- Wait for A/D conversion to complete, by either:

- Waiting for the A/D interrupt

- Waiting for the DONE bit to be set

- Read A/D result buffer; clear ADIF if required

# 19.3 Selecting the Conversion Sequence

Several groups of control bits select the sequence in which the A/D connects inputs to the sample/hold channels, converts channels, writes the buffer memory and generates interrupts. The sequence is controlled by the sampling clocks.

The SIMSAM bit controls the acquire/convert sequence for multiple channels. If the SIMSAM bit is '0', the two or four selected channels are acquired and converted sequentially, with two or four sample clocks. If the SIMSAM bit is '1', two or four selected channels are acquired simultaneously, with one sample clock. The channels are then converted sequentially. Obviously, if there is only 1 channel selected, the SIMSAM bit is not applicable.

The CHPS bits select how many channels are sampled. This can vary from 1, 2 or 4 channels. If the CHPS bits select 1 channel, the CH0 channel will be sampled at the sample clock and converted. The result is stored in the buffer. If the CHPS bits select 2 channels, the CH0 and CH1 channels will be sampled and converted. If the CHPS bits select 4 channels, the CH0, CH1, CH2 and CH3 channels will be sampled and converted.

The SMPI bits select the number of acquisition/ conversion sequences that would be performed before an interrupt occurs. This can vary from 1 sample per interrupt to 16 samples per interrupt.

The user cannot program a combination of CHPS and SMPI bits that specifies more than 16 conversions per interrupt, or 8 conversions per interrupt, depending on the BUFM bit. The BUFM bit, when set, will split the 16-word results buffer (ADCBUF0...ADCBUFF) into two 8-word groups. Writing to the 8-word buffers will be alternated on each interrupt event. Use of the BUFM bit will depend on how much time is available for moving data out of the buffers after the interrupt, as determined by the application.

If the processor can quickly unload a full buffer within the time it takes to acquire and convert one channel, the BUFM bit can be '0' and up to 16 conversions may be done per interrupt. The processor will have one sample and conversion time to move the sixteen conversions.

If the processor cannot unload the buffer within the acquisition and conversion time, the BUFM bit should be '1'. For example, if SMPI<3:0> (ADCON2<5:2>) = 0111, then eight conversions will be loaded into 1/2 of the buffer, following which an interrupt occurs. The next eight conversions will be loaded into the other 1/2 of the buffer. The processor will have the entire time between interrupts to move the eight conversions.

The ALTS bit can be used to alternate the inputs selected during the sampling sequence. The input multiplexer has two sets of sample inputs: MUX A and MUX B. If the ALTS bit is '0', only the MUX A inputs are selected for sampling. If the ALTS bit is '1' and SMPI<3:0> = 0000, on the first sample/convert sequence, the MUX A inputs are selected, and on the next acquire/convert sequence, the MUX B inputs are selected.

The CSCNA bit (ADCON2<10>) will allow the CH0 channel inputs to be alternately scanned across a selected number of analog inputs for the MUX A group. The inputs are selected by the ADCSSL register. If a particular bit in the ADCSSL register is '1', the corresponding input is selected. The inputs are always scanned from lower to higher numbered inputs, starting after each interrupt. If the number of inputs selected is greater than the number of samples taken per interrupt, the higher numbered inputs are unused.

## 20.2.3 LP OSCILLATOR CONTROL

Enabling the LP oscillator is controlled with two elements:

- The current oscillator group bits, COSC<2:0>

- The LPOSCEN bit (OSCON register)

The LP oscillator is on (even during Sleep mode) if LPOSCEN = 1. The LP oscillator is the device clock if:

- COSC<1:0> = 00 (LP selected as main osc.) and

- LPOSCEN = 1

Keeping the LP oscillator on at all times allows for a fast switch to the 32 kHz system clock for lower power operation. Returning to the faster main oscillator will still require a start-up time.

### 20.2.4 PHASE LOCKED LOOP (PLL)

The PLL multiplies the clock which is generated by the primary oscillator. The PLL is selectable to have either gains of x4, x8 and x16. Input and output frequency ranges are summarized in Table 20-3.

TABLE 20-3: PLL FREQUENCY RANGE

| Fin           | PLL<br>Multiplier | Fout           |

|---------------|-------------------|----------------|

| 4 MHz-10 MHz  | x4                | 16 MHz-40 MHz  |

| 4 MHz-10 MHz  | x8                | 32 MHz-80 MHz  |

| 4 MHz-7.5 MHz | x16               | 64 MHz-120 MHz |

The PLL features a lock output, which is asserted when the PLL enters a phase locked state. Should the loop fall out of lock (e.g., due to noise), the lock signal will be rescinded. The state of this signal is reflected in the read-only LOCK bit in the OSCCON register.

## 20.2.5 FAST RC OSCILLATOR (FRC)

The FRC oscillator is a fast (7.37 MHz +/- 2% nominal) internal RC oscillator. This oscillator is intended to provide reasonable device operating speeds without the use of an external crystal, ceramic resonator or RC network. The FRC oscillator can be used with the PLL to obtain higher clock frequencies.

The dsPIC30F operates from the FRC oscillator whenever the current oscillator selection control bits in the OSCCON register (OSCCON<13:12>) are set to '01'.

The four-bit field specified by TUN<3:0> (OSCTUN<3:0>) allows the user to tune the internal fast RC oscillator (nominal 7.37 MHz). The user can tune the FRC oscillator within a range of +10.5%

(840 kHz) and -12% (960 kHz) in steps of 1.50% around the factory calibrated setting, as shown in Table 20-4.

Note: OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation and is neither characterized nor tested.

If OSCCON<14:12> are set to '111' and FPR<4:0> are set to '00101', '00110' or '00111', then a PLL multiplier of 4, 8 or 16 (respectively) is applied

**Note:** When a 16x PLL is used, the FRC frequency must not be tuned to a frequency greater than 7.5 MHz.

### TABLE 20-4: FRC TUNING

| TUN<3:0><br>Bits | FRC Frequency                                                       |

|------------------|---------------------------------------------------------------------|

| 0111             | +10.5%                                                              |

| 0110             | +9.0%                                                               |

| 0101             | +7.5%                                                               |

| 0100             | +6.0%                                                               |

| 0011             | +4.5%                                                               |

| 0010             | +3.0%                                                               |

| 0001             | +1.5%                                                               |

| 0000             | Center Frequency (oscillator is<br>running at calibrated frequency) |

| 1111             | -1.5%                                                               |

| 1110             | -3.0%                                                               |

| 1101             | -4.5%                                                               |

| 1100             | -6.0%                                                               |

| 1011             | -7.5%                                                               |

| 1010             | -9.0%                                                               |

| 1001             | -10.5%                                                              |

| 1000             | -12.0%                                                              |

## 20.2.6 LOW-POWER RC OSCILLATOR (LPRC)

The LPRC oscillator is a component of the Watchdog Timer (WDT) and oscillates at a nominal frequency of 512 kHz. The LPRC oscillator is the clock source for the Power-up Timer (PWRT) circuit, WDT and clock monitor circuits. It may also be used to provide a lowfrequency clock source option for applications where power consumption is critical and timing accuracy is not required.

The LPRC oscillator is always enabled at a Power-on Reset, because it is the clock source for the PWRT. After the PWRT expires, the LPRC oscillator will remain ON if one of the following is true:

- The Fail-Safe Clock Monitor is enabled

- The WDT is enabled

- The LPRC oscillator is selected as the system clock via the COSC<1:0> control bits in the OSCCON register

If one of the above conditions is not true, the LPRC will shut-off after the PWRT expires.

- Note 1: OSC2 pin function is determined by the Primary Oscillator mode selection (FPR<3:0>).

- OSC1 pin cannot be used as an I/O pin, even if the secondary oscillator or an internal clock source is selected at all times.

# 20.2.7 FAIL-SAFE CLOCK MONITOR

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by appropriately programming the FCKSM Configuration bits (Clock Switch and Monitor Selection bits) in the FOSC Configuration register. If the FSCM function is enabled, the LPRC internal oscillator will run at all times (except during Sleep mode) and will not be subject to control by the SWDTEN bit.

In the event of an oscillator failure, the FSCM will generate a clock failure trap event and will switch the system clock over to the FRC oscillator. The user will then have the option to either attempt to restart the oscillator or execute a controlled shut down. The user may decide to treat the trap as a warm Reset by simply loading the Reset address into the oscillator fail trap vector. In this event, the CF (Clock Fail) status bit (OSCCON<3>) is also set whenever a clock failure is recognized.

In the event of a clock failure, the WDT is unaffected and continues to run on the LPRC clock.

If the oscillator has a very slow start-up time coming out of POR, BOR or Sleep, it is possible that the PWRT timer will expire before the oscillator has started. In such cases, the FSCM will be activated and the FSCM will initiate a clock failure trap, and the COSC<1:0> bits are loaded with FRC oscillator selection. This will effectively shut-off the original oscillator that was trying to start.

The user may detect this situation and restart the oscillator in the clock fail trap ISR.

Upon a clock failure detection, the FSCM module will initiate a clock switch to the FRC oscillator as follows:

- 1. The COSC bits (OSCCON<13:12>) are loaded with the FRC Oscillator selection value.

- 2. CF bit is set (OSCCON<3>).

- 3. OSWEN control bit (OSCCON<0>) is cleared.

For the purpose of clock switching, the clock sources are sectioned into four groups:

- Primary

- · Secondary

- Internal FRC

- Internal LPRC

The user can switch between these functional groups, but cannot switch between options within a group. If the primary group is selected, then the choice within the group is always determined by the FPR<3:0> Configuration bits. The OSCCON register holds the control and status bits related to clock switching.

- COSC<1:0>: Read-only status bits always reflect the current oscillator group in effect.

- NOSC<1:0>: Control bits which are written to indicate the new oscillator group of choice.

- On POR and BOR, COSC<1:0> and NOSC<1:0> are both loaded with the Configuration bit values, FOS<1:0>.

- LOCK: The LOCK status bit indicates a PLL lock.

- CF: Read-only status bit indicating if a clock fail detect has occurred.

- OSWEN: Control bit changes from a '0' to a '1' when a clock transition sequence is initiated. Clearing the OSWEN control bit will abort a clock transition in progress (used for hang-up situations).

If Configuration bits, FCKSM<1:0> = lx, then the clock switching and Fail-Safe Clock Monitor functions are disabled. This is the default Configuration bit setting.

If clock switching is disabled, then the FOS<1:0> and FPR<3:0> bits directly control the oscillator selection and the COSC<1:0> bits do not control the clock selection. However, these bits will reflect the clock source selection.

**Note:** The application should not attempt to switch to a clock of frequency lower than 100 kHz when the Fail-Safe Clock Monitor is enabled. If such clock switching is performed, the device may generate an oscillator fail trap and switch to the fast RC oscillator.

Table 20-5 shows the Reset conditions for the RCON register. Since the control bits within the RCON register are R/W, the information in the table implies that all the bits are negated prior to the action specified in the condition column.

| Condition                                 | Program<br>Counter    | TRAPR | IOPUWR | EXTR | SWR | WDTO | IDLE | SLEEP | POR | BOR |

|-------------------------------------------|-----------------------|-------|--------|------|-----|------|------|-------|-----|-----|

| Power-on Reset                            | 0x000000              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 1   | 1   |

| Brown-out Reset                           | 0x000000              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 1   |

| MCLR Reset during Normal Operation        | 0x000000              | 0     | 0      | 1    | 0   | 0    | 0    | 0     | 0   | 0   |

| Software Reset during<br>Normal Operation | 0x000000              | 0     | 0      | 0    | 1   | 0    | 0    | 0     | 0   | 0   |

| MCLR Reset during Sleep                   | 0x000000              | 0     | 0      | 1    | 0   | 0    | 0    | 1     | 0   | 0   |

| MCLR Reset during Idle                    | 0x000000              | 0     | 0      | 1    | 0   | 0    | 1    | 0     | 0   | 0   |

| WDT Time-out Reset                        | 0x000000              | 0     | 0      | 0    | 0   | 1    | 0    | 0     | 0   | 0   |

| WDT Wake-up                               | PC + 2                | 0     | 0      | 0    | 0   | 1    | 0    | 1     | 0   | 0   |

| Interrupt Wake-up from Sleep              | PC + 2 <sup>(1)</sup> | 0     | 0      | 0    | 0   | 0    | 0    | 1     | 0   | 0   |

| Clock Failure Trap                        | 0x000004              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

| Trap Reset                                | 0x000000              | 1     | 0      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

| Illegal Operation Trap                    | 0x000000              | 0     | 1      | 0    | 0   | 0    | 0    | 0     | 0   | 0   |

# TABLE 20-5: INITIALIZATION CONDITION FOR RCON REGISTER CASE 1

**Legend:** u = unchanged, x = unknown

Note 1: When the wake-up is due to an enabled interrupt, the PC is loaded with the corresponding interrupt vector.

Table 20-6 shows a second example of the bit conditions for the RCON register. In this case, it is not assumed the user has set/cleared specific bits prior to action specified in the condition column.

## TABLE 20-6: INITIALIZATION CONDITION FOR RCON REGISTER CASE 2

| Condition                                 | Program<br>Counter    | TRAPR | IOPUWR | EXTR | SWR | WDTO | IDLE | SLEEP | POR | BOR |

|-------------------------------------------|-----------------------|-------|--------|------|-----|------|------|-------|-----|-----|

| Power-on Reset                            | 0x000000              | 0     | 0      | 0    | 0   | 0    | 0    | 0     | 1   | 1   |

| Brown-out Reset                           | 0x000000              | u     | u      | u    | u   | u    | u    | u     | 0   | 1   |

| MCLR Reset during Normal<br>Operation     | 0x000000              | u     | u      | 1    | 0   | 0    | 0    | 0     | u   | u   |

| Software Reset during<br>Normal Operation | 0x000000              | u     | u      | 0    | 1   | 0    | 0    | 0     | u   | u   |

| MCLR Reset during Sleep                   | 0x000000              | u     | u      | 1    | u   | 0    | 0    | 1     | u   | u   |

| MCLR Reset during Idle                    | 0x000000              | u     | u      | 1    | u   | 0    | 1    | 0     | u   | u   |

| WDT Time-out Reset                        | 0x000000              | u     | u      | 0    | 0   | 1    | 0    | 0     | u   | u   |

| WDT Wake-up                               | PC + 2                | u     | u      | u    | u   | 1    | u    | 1     | u   | u   |

| Interrupt Wake-up from<br>Sleep           | PC + 2 <sup>(1)</sup> | u     | u      | u    | u   | u    | u    | 1     | u   | u   |

| Clock Failure Trap                        | 0x000004              | u     | u      | u    | u   | u    | u    | u     | u   | u   |

| Trap Reset                                | 0x000000              | 1     | u      | u    | u   | u    | u    | u     | u   | u   |

| Illegal Operation Reset                   | 0x000000              | u     | 1      | u    | u   | u    | u    | u     | u   | u   |

**Legend:** u = unchanged, x = unknown

Note 1: When the wake-up is due to an enabled interrupt, the PC is loaded with the corresponding interrupt vector.

| AC CH4       | ARACTER       | ISTICS                                                       | Standard C<br>(unless oth<br>Operating t | nerwise sta | a <b>ted)</b><br>∋ -40°C | ≤ TA ≤ +8 | <b>5.5V</b><br>5°C for Industrial<br>25°C for Extended |

|--------------|---------------|--------------------------------------------------------------|------------------------------------------|-------------|--------------------------|-----------|--------------------------------------------------------|

| Param<br>No. | Symbol        | Characteristic                                               | Conditions                               |             |                          |           |                                                        |

| OS10         | Fosc          | External CLKI Frequency <sup>(2)</sup>                       | DC                                       | _           | 40                       | MHz       | EC                                                     |

|              |               | (External clocks allowed                                     | 4                                        | _           | 10                       | MHz       | EC with 4x PLL                                         |

|              |               | only in EC mode)                                             | 4                                        | _           | 10                       | MHz       | EC with 8x PLL                                         |

|              |               |                                                              | 4                                        | _           | 7.5                      | MHz       | EC with 16x PLL                                        |

|              |               | Oscillator Frequency <sup>(2)</sup>                          | DC                                       | _           | 4                        | MHz       | RC                                                     |

|              |               |                                                              | 0.4                                      | _           | 4                        | MHz       | XTL                                                    |

|              |               |                                                              | 4                                        | _           | 10                       | MHz       | ХТ                                                     |

|              |               |                                                              | 4                                        | _           | 10                       | MHz       | XT with 4x PLL                                         |

|              |               |                                                              | 4                                        | —           | 10                       | MHz       | XT with 8x PLL                                         |

|              |               |                                                              | 4                                        | —           | 7.5                      | MHz       | XT with 16x PLL                                        |

|              |               |                                                              | 10                                       | —           | 25                       | MHz       | HS                                                     |

|              |               |                                                              | 31                                       | —           | 33                       | kHz       | LP                                                     |

|              |               |                                                              | —                                        | 7.37        | —                        | MHz       | FRC internal                                           |

|              |               |                                                              | —                                        | 512         | —                        | kHz       | LPRC internal                                          |

| OS20         | Tosc          | Tosc = 1/Fosc                                                | —                                        | —           | —                        | —         | See parameter OS10                                     |

|              |               |                                                              |                                          |             |                          |           | for Fosc value                                         |

| OS25         | TCY           | Instruction Cycle Time <sup>(2,3)</sup>                      | 33                                       | _           | DC                       | ns        | See Table 23-16                                        |

| OS30         | TosL,         | External Clock in (OSC1)                                     | .45 x Tosc                               |             | —                        | ns        | EC                                                     |

|              | TosH          | High or Low Time <sup>(2)</sup>                              |                                          |             |                          |           |                                                        |

| OS31         | TosR,<br>TosF | External Clock in (OSC1)<br>Rise or Fall Time <sup>(2)</sup> | —                                        | —           | 20                       | ns        | EC                                                     |

| OS40         | TckR          | CLKO Rise Time <sup>(2,4)</sup>                              | —                                        | _           | —                        | ns        | See parameter DO31                                     |

| OS41         | TckF          | CLKO Fall Time <sup>(2,4)</sup>                              | _                                        | _           | —                        | ns        | See parameter DO32                                     |

#### TABLE 23-13: EXTERNAL CLOCK TIMING REQUIREMENTS

**Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized but not tested in manufacturing.

- 3: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "Min." values with an external clock applied to the OSC1/CLKI pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

- 4: Measurements are taken in EC or ERC modes. The CLKO signal is measured on the OSC2 pin. CLKO is low for the Q1-Q2 period (1/2 TcY) and high for the Q3-Q4 period (1/2 TcY).

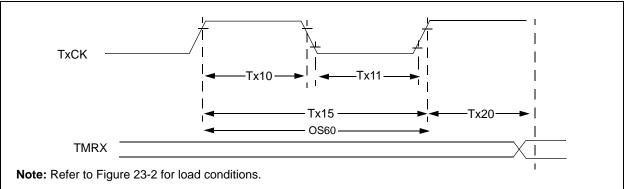

# FIGURE 23-7: TIMER1, 2, 3, 4 AND 5 EXTERNAL CLOCK TIMING CHARACTERISTICS

# TABLE 23-22: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS

| АС СНА       | RACTERIST | ICS                                                                       |                      | (unles | ard Operating<br>s otherwise st<br>ing temperatur | <b>ated)</b><br>e -40 | )°C ≤ Ta   | ≤ +85°0 | 5V<br>C for Industrial<br>℃ for Extended |

|--------------|-----------|---------------------------------------------------------------------------|----------------------|--------|---------------------------------------------------|-----------------------|------------|---------|------------------------------------------|

| Param<br>No. | Symbol    | Characte                                                                  | eristic              |        | Min                                               | Тур                   | Max        | Units   | Conditions                               |

| TA10         | ТтхН      | TxCK High Time                                                            | Synchro<br>no preso  | ,      | 0.5 TCY + 20                                      |                       |            | ns      | Must also meet parameter TA15            |

|              |           |                                                                           | Synchro<br>with pres |        | 10                                                |                       |            | ns      |                                          |

|              |           |                                                                           | Asynchr              | onous  | 10                                                | _                     | _          | ns      |                                          |

| TA11         | TTXL      | TxCK Low Time                                                             | Synchro<br>no preso  |        | 0.5 Tcy + 20                                      | _                     | _          | ns      | Must also meet parameter TA15            |

|              |           |                                                                           | Synchro<br>with pres |        | 10                                                |                       |            | ns      |                                          |

|              |           |                                                                           | Asynchr              | onous  | 10                                                |                       |            | ns      |                                          |

| TA15         | ΤτχΡ      | TxCK Input Period                                                         | Synchro<br>no preso  |        | Tcy + 10                                          | _                     |            | ns      |                                          |

|              |           |                                                                           | Synchro<br>with pres |        | Greater of:<br>20 ns or<br>(TCY + 40)/N           |                       | _          | —       | N = prescale value<br>(1, 8, 64, 256)    |

|              |           |                                                                           | Asynchr              | onous  | 20                                                | _                     | —          | ns      |                                          |

| OS60         | Ft1       | SOSC1/T1CK Osci<br>Frequency Range (<br>enabled by setting<br>(T1CON<1>)) | oscillator           |        | DC                                                | _                     | 50         | kHz     |                                          |

| TA20         | TCKEXTMRL | Delay from Externa<br>Edge to Timer Incre                                 |                      | lock   | 0.5 TCY                                           |                       | 1.5<br>Тсү | _       |                                          |

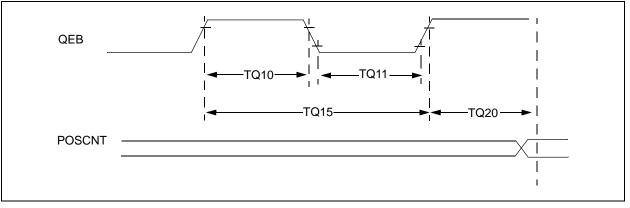

## FIGURE 23-8: TIMERQ (QEI MODULE) EXTERNAL CLOCK TIMING CHARACTERISTICS

#### TABLE 23-25: QEI MODULE EXTERNAL CLOCK TIMING REQUIREMENTS

AC CHARACTERISTICS

Standard Operating Conditions: 2.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$  for Industrial

-40°C  $\leq$  TA  $\leq$  +125°C for Extended

| Param<br>No. | Symbol    | Characteristic <sup>(1)</sup>                             |                             | Min          | Тур | Max     | Units | Conditions                       |

|--------------|-----------|-----------------------------------------------------------|-----------------------------|--------------|-----|---------|-------|----------------------------------|

| TQ10         | TtQH      | •                                                         | Synchronous, with prescaler | Tcy + 20     |     | _       | ns    | Must also meet parameter TQ15    |

| TQ11         | TtQL      |                                                           | Synchronous, with prescaler | Tcy + 20     |     | —       | ns    | Must also meet<br>parameter TQ15 |

| TQ15         | TtQP      |                                                           | Synchronous, with prescaler | 2 * TCY + 40 | _   | —       | ns    |                                  |

| TQ20         | TCKEXTMRL | Delay from External TQCK Clock<br>Edge to Timer Increment |                             | 0.5 TCY      |     | 1.5 TCY |       |                                  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

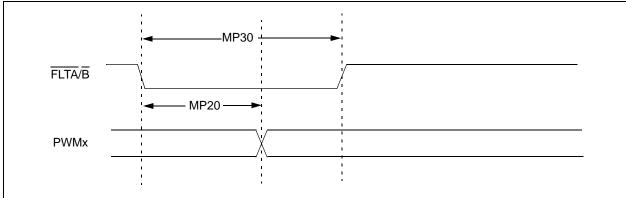

## FIGURE 23-12: MOTOR CONTROL PWM MODULE FAULT TIMING CHARACTERISTICS

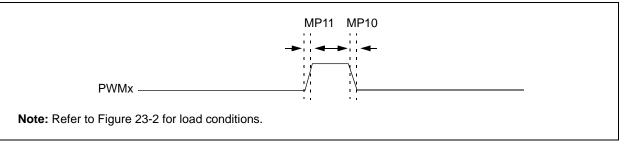

### FIGURE 23-13: MOTOR CONTROL PWM MODULE TIMING CHARACTERISTICS

### TABLE 23-29: MOTOR CONTROL PWM MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |     |       |                    |  |

|--------------------|--------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|--------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>      | Min                                                                                                                                                                                                                                                                                     | Тур | Max | Units | Conditions         |  |

| MP10               | TFPWM  | PWM Output Fall Time               | _                                                                                                                                                                                                                                                                                       | _   |     | ns    | See parameter DO32 |  |

| MP11               | TRPWM  | PWM Output Rise<br>Time            | —                                                                                                                                                                                                                                                                                       | —   | —   | ns    | See parameter DO31 |  |

| MP20               | Tfd    | Fault Input ↓ to PWM<br>I/O Change | —                                                                                                                                                                                                                                                                                       | —   | 50  | ns    |                    |  |

| MP30               | Tfh    | Minimum Pulse Width                | 50                                                                                                                                                                                                                                                                                      |     |     | ns    |                    |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

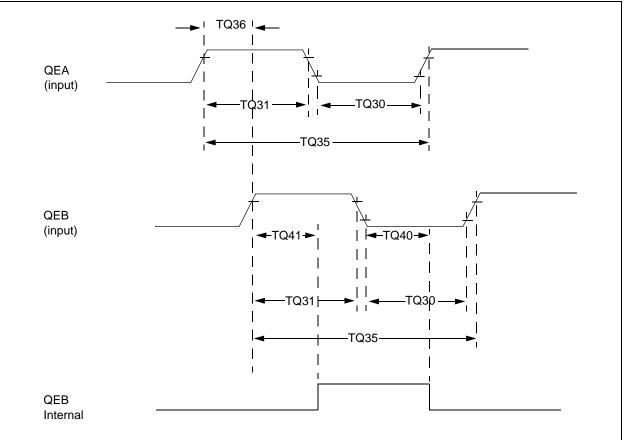

# FIGURE 23-14: QEA/QEB INPUT CHARACTERISTICS

## TABLE 23-30: QUADRATURE DECODER TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                    | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                    |     |       |                                                         |  |

|--------------------|--------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|---------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                      |                                                                                                                                                                                                                                                                                     | Тур <sup>(2)</sup> | Max | Units | Conditions                                              |  |

| TQ30               | TQUL   | Quadrature Input Low Time                          |                                                                                                                                                                                                                                                                                     | 6 TCY              | _   | ns    |                                                         |  |

| TQ31               | ΤουΗ   | Quadrature Input High Time                         |                                                                                                                                                                                                                                                                                     | 6 Tcy              | —   | ns    |                                                         |  |

| TQ35               | TQUIN  | Quadrature Input Period                            |                                                                                                                                                                                                                                                                                     | 12 Tcy             | —   | ns    |                                                         |  |

| TQ36               | ΤουΡ   | Quadrature Phase Period                            |                                                                                                                                                                                                                                                                                     | 3 TCY              | —   | ns    |                                                         |  |

| TQ40               | TQUFL  | Filter Time to Recognize Low, with Digital Filter  |                                                                                                                                                                                                                                                                                     | 3 * N * Tcy        | —   | ns    | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 2)</b> |  |

| TQ41               | TQUFH  | Filter Time to Recognize High, with Digital Filter |                                                                                                                                                                                                                                                                                     | 3 * N * Tcy        | —   | ns    | N = 1, 2, 4, 16, 32, 64,<br>128 and 256 <b>(Note 2)</b> |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: N = Index Channel Digital Filter Clock Divide Select bits. Refer to Section 16. "Quadrature Encoder Interface (QEI)" in the "dsPIC30F Family Reference Manual" (DS70046).

### FIGURE 23-19: SPI MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS