#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                        |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 30 MIPs                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                            |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                |

| Number of I/O              | 30                                                                           |

| Program Memory Size        | 24KB (8K x 24)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 1K x 8                                                                       |

| RAM Size                   | 1K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | A/D 9x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Through Hole                                                                 |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                     |

| Supplier Device Package    | 40-PDIP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3011-30i-p |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                            | 11  |

|-------|------------------------------------------------------------|-----|

| 2.0   | CPU Architecture Overview                                  | 19  |

| 3.0   | Memory Organization                                        | 27  |

| 4.0   | Address Generator Units                                    | 39  |

| 5.0   | Interrupts                                                 | 45  |

| 6.0   | Flash Program Memory                                       | 51  |

| 7.0   | Data EEPROM Memory                                         | 57  |

| 8.0   | I/O Ports                                                  | 61  |

| 9.0   | Timer1 Module                                              | 67  |

| 10.0  | Timer2/3 Module                                            | 71  |

| 11.0  | Timer4/5 Module                                            |     |

| 12.0  | Input Capture Module                                       | 81  |

| 13.0  | Output Compare Module                                      | 85  |

| 14.0  | Quadrature Encoder Interface (QEI) Module                  | 91  |

| 15.0  | Motor Control PWM Module                                   | 97  |

| 16.0  | SPI Module                                                 | 107 |

| 17.0  | I2C™ Module                                                |     |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART) Module  |     |

| 19.0  | 10-bit High-Speed Analog-to-Digital Converter (ADC) Module | 127 |

| 20.0  | System Integration                                         | 139 |

| 21.0  | Instruction Set Summary                                    | 155 |

| 22.0  | Development Support                                        | 165 |

| 23.0  | Electrical Characteristics                                 |     |

| 24.0  | Packaging Information                                      | 209 |

| Index | (                                                          | 219 |

|       | Aicrochip Web Site                                         |     |

|       | omer Change Notification Service                           |     |

|       | omer Support                                               |     |

| Read  | er Response                                                | 226 |

| Produ | uct Identification System                                  | 227 |

|       |                                                            |     |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| Pin Name              | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                        |  |  |  |  |  |  |  |

|-----------------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| OSC1                  | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                    |  |  |  |  |  |  |  |

| OSC2                  | I/O         | —              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.           |  |  |  |  |  |  |  |

| PGD                   | I/O         | ST             | In-Circuit Serial Programming data input/output pin.                                                                                               |  |  |  |  |  |  |  |

| PGC                   | I           | ST             | In-Circuit Serial Programming clock input pin.                                                                                                     |  |  |  |  |  |  |  |

| RB0-RB5               | I/O         | ST             | PORTB is a bidirectional I/O port.                                                                                                                 |  |  |  |  |  |  |  |

| RC13-RC15             | I/O         | ST             | PORTC is a bidirectional I/O port.                                                                                                                 |  |  |  |  |  |  |  |

| RD0-RD1               | I/O         | ST             | PORTD is a bidirectional I/O port.                                                                                                                 |  |  |  |  |  |  |  |

| RE0-RE5,<br>RE8       | I/O         | ST             | PORTE is a bidirectional I/O port.                                                                                                                 |  |  |  |  |  |  |  |

| RF2-RF3               | I/O         | ST             | PORTF is a bidirectional I/O port.                                                                                                                 |  |  |  |  |  |  |  |

| SCK1                  | I/O         | ST             | Synchronous serial clock input/output for SPI1.                                                                                                    |  |  |  |  |  |  |  |

| SDI1                  | I           | ST             | SPI1 Data In.                                                                                                                                      |  |  |  |  |  |  |  |

| SDO1                  | 0           | —              | SPI1 Data Out.                                                                                                                                     |  |  |  |  |  |  |  |

| SCL                   | I/O         | ST             | Synchronous serial clock input/output for I <sup>2</sup> C.                                                                                        |  |  |  |  |  |  |  |

| SDA                   | I/O         | ST             | Synchronous serial data input/output for I <sup>2</sup> C.                                                                                         |  |  |  |  |  |  |  |

| SOSCO<br>SOSCI        | 0           | ST/CMOS        | 32 kHz low-power oscillator crystal output.<br>32 kHz low-power oscillator crystal input. ST buffer when configured in RC<br>mode; CMOS otherwise. |  |  |  |  |  |  |  |

| T1CK                  | I           | ST             | Timer1 external clock input.                                                                                                                       |  |  |  |  |  |  |  |

| T2CK                  | I           | ST             | Timer2 external clock input.                                                                                                                       |  |  |  |  |  |  |  |

| U1RX                  | I           | ST             | UART1 Receive.                                                                                                                                     |  |  |  |  |  |  |  |

| U1TX                  | 0           | —              | UART1 Transmit.                                                                                                                                    |  |  |  |  |  |  |  |

| U1ARX                 |             | ST             | UART1 Alternate Receive.                                                                                                                           |  |  |  |  |  |  |  |

| U1ATX                 | 0           |                | UART1 Alternate Transmit.                                                                                                                          |  |  |  |  |  |  |  |

| VDD                   | P           | —              | Positive supply for logic and I/O pins.                                                                                                            |  |  |  |  |  |  |  |

| Vss                   | P           |                | Ground reference for logic and I/O pins.                                                                                                           |  |  |  |  |  |  |  |

| VREF+                 | I           | Analog         | Analog Voltage Reference (High) input.                                                                                                             |  |  |  |  |  |  |  |

| Vref-                 | I           | Analog         |                                                                                                                                                    |  |  |  |  |  |  |  |

| Legend: CM<br>ST<br>I | = Sc        |                | ible input or outputAnalog =Analog inputr input with CMOS levelsO=OutputP=Power                                                                    |  |  |  |  |  |  |  |

TABLE 1-2: dsPIC30F3010 I/O PIN DESCRIPTIONS (CONTINUED)

## 5.0 INTERRUPTS

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

The dsPIC30F3010/3011 has 29 interrupt sources and 4 processor exceptions (traps), which must be arbitrated based on a priority scheme.

The CPU is responsible for reading the Interrupt Vector Table (IVT) and transferring the address contained in the interrupt vector to the program counter. The interrupt vector is transferred from the program data bus into the program counter through a 24-bit wide multiplexer on the input of the program counter.

The Interrupt Vector Table (IVT) and Alternate Interrupt Vector Table (AIVT) are placed near the beginning of program memory (0x000004). The IVT and AIVT are shown in Figure 5-1.

The interrupt controller is responsible for preprocessing the interrupts and processor exceptions, prior to their being presented to the processor core. The peripheral interrupts and traps are enabled, prioritized and controlled using centralized Special Function Registers (SFR):

- IFS0<15:0>, IFS1<15:0>, IFS2<15:0> All interrupt request flags are maintained in these three registers. The flags are set by their respective peripherals or external signals, and they are cleared via software.

- IEC0<15:0>, IEC1<15:0>, IEC2<15:0> All interrupt enable control bits are maintained in these three registers. These control bits are used to individually enable interrupts from the peripherals or external signals.

- IPC0<15:0>... IPC11<7:0> The user-assignable priority level associated with each of these interrupts is held centrally in these twelve registers.

- IPL<3:0> The current CPU priority level is explicitly stored in the IPL bits. IPL<3> is present in the CORCON register, whereas IPL<2:0> are present in the STATUS Register (SR) in the processor core.

- INTCON1<15:0>, INTCON2<15:0> Global interrupt control functions are derived from these two registers. INTCON1 contains the control and status flags for the processor exceptions. The INTCON2 register controls the external interrupt request signal behavior and the use of the alternate vector table.

- Note: Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit. User software should ensure the appropriate Interrupt flag bits are clear prior to enabling an interrupt.

All interrupt sources can be user-assigned to one of 7 priority levels, 1 through 7, through the IPCx registers. Each interrupt source is associated with an interrupt vector, as shown in Table 5-1. Levels 7 and 1 represent the highest and lowest maskable priorities, respectively.

**Note:** Assigning a priority level of 0 to an interrupt source is equivalent to disabling that interrupt.

If the NSTDIS bit (INTCON1<15>) is set, nesting of interrupts is prevented. Thus, if an interrupt is currently being serviced, processing of a new interrupt is prevented, even if the new interrupt is of higher priority than the one currently being serviced.

Note: The IPL bits become read-only whenever the NSTDIS bit has been set to '1'.

Certain interrupts have specialized control bits for features like edge or level triggered interrupts, interrupt-on-change, etc. Control of these features remains within the peripheral module which generates the interrupt.

The DISI instruction can be used to disable the processing of interrupts of priorities 6 and lower for a certain number of instructions, during which the DISI bit (INTCON2<14>) remains set.

When an interrupt is serviced, the PC is loaded with the address stored in the vector location in program memory that corresponds to the interrupt. There are 63 different vectors within the IVT (refer to Figure 5-2). These vectors are contained in locations 0x000004 through 0x0000FE of program memory (refer to Figure 5-2). These locations contain 24-bit addresses, and in order to preserve robustness, an address error trap will take place should the PC attempt to fetch any of these words during normal execution. This prevents execution of random data as a result of accidentally decrementing a PC into vector space, accidentally mapping a data space address into vector space or the PC rolling over to 0x000000 after reaching the end of implemented program memory space. Execution of a GOTO instruction to this vector space will also generate an address error trap.

## 5.1 Interrupt Priority

The user-assignable Interrupt Priority (IP<2:0>) bits for each individual interrupt source are located in the 3 LSbs of each nibble, within the IPCx register(s). Bit 3 of each nibble is not used and is read as a '0'. These bits define the priority level assigned to a particular interrupt by the user.

| Note: | The user-assignable priority levels start at |

|-------|----------------------------------------------|

|       | 0, as the lowest priority, and Level 7, as   |

|       | the highest priority.                        |

Since more than one interrupt request source may be assigned to a specific user-assigned priority level, a means is provided to assign priority within a given level. This method is called "Natural Order Priority".

Natural Order Priority is determined by the position of an interrupt in the vector table, and only affects interrupt operation when multiple interrupts with the same user-assigned priority become pending at the same time.

Table 5-1 lists the interrupt numbers and interrupt sources for the dsPIC DSC devices and their associated vector numbers.

- **Note 1:** The natural order priority scheme has 0 as the highest priority and 53 as the lowest priority.

- **2:**The natural order priority number is the same as the INT number.

The ability for the user to assign every interrupt to one of seven priority levels implies that the user can assign a very high overall priority level to an interrupt with a low natural order priority. For example, the PWM Fault A Interrupt can be given a priority of 7. The INTO (external interrupt 0) may be assigned to priority Level 1, thus giving it a very low effective priority.

#### TABLE 5-1:INTERRUPT VECTOR TABLE

| Interrupt | Vector | Interrupt Source                         |  |  |  |  |  |

|-----------|--------|------------------------------------------|--|--|--|--|--|

| Number    | Number |                                          |  |  |  |  |  |

| •         | -      | Natural Order Priority                   |  |  |  |  |  |

| 0         | 8      | INT0 – External Interrupt 0              |  |  |  |  |  |

| 1         | 9      | IC1 – Input Capture 1                    |  |  |  |  |  |

| 2         | 10     | OC1 – Output Compare 1                   |  |  |  |  |  |

| 3         | 11     | T1 – Timer1                              |  |  |  |  |  |

| 4         | 12     | IC2 – Input Capture 2                    |  |  |  |  |  |

| 5         | 13     | OC2 – Output Compare 2                   |  |  |  |  |  |

| 6         | 14     | T2 – Timer2                              |  |  |  |  |  |

| 7         | 15     | T3 – Timer3                              |  |  |  |  |  |

| 8         | 16     | SPI1                                     |  |  |  |  |  |

| 9         | 17     | U1RX – UART1 Receiver                    |  |  |  |  |  |

| 10        | 18     | U1TX – UART1 Transmitter                 |  |  |  |  |  |

| 11        | 19     | ADC – ADC Convert Done                   |  |  |  |  |  |

| 12        | 20     | NVM – NVM Write Complete                 |  |  |  |  |  |

| 13        | 21     | SI2C – I <sup>2</sup> C Slave Interrupt  |  |  |  |  |  |

| 14        | 22     | MI2C – I <sup>2</sup> C Master Interrupt |  |  |  |  |  |

| 15        | 23     | Input Change Interrupt                   |  |  |  |  |  |

| 16        | 24     | INT1 – External Interrupt 1              |  |  |  |  |  |

| 17        | 25     | IC7 – Input Capture 7                    |  |  |  |  |  |

| 18        | 26     | IC8 – Input Capture 8                    |  |  |  |  |  |

| 19        | 27     | OC3 – Output Compare 3 <sup>(1)</sup>    |  |  |  |  |  |

| 20        | 28     | OC4 – Output Compare 4 <sup>(1)</sup>    |  |  |  |  |  |

| 21        | 29     | T4 – Timer4                              |  |  |  |  |  |

| 22        | 30     | T5 – Timer5                              |  |  |  |  |  |

| 23        | 31     | INT2 – External Interrupt 2              |  |  |  |  |  |

| 24        | 32     | U2RX – UART2 Receiver <sup>(1)</sup>     |  |  |  |  |  |

| 25        | 33     | U2TX – UART2 Transmitter <sup>(1)</sup>  |  |  |  |  |  |

| 26        | 34     | Reserved                                 |  |  |  |  |  |

| 27        | 35     | Reserved                                 |  |  |  |  |  |

| 28        | 36     | Reserved                                 |  |  |  |  |  |

| 29        | 37     | Reserved                                 |  |  |  |  |  |

| 30        | 38     | Reserved                                 |  |  |  |  |  |

| 31        | 39     | Reserved                                 |  |  |  |  |  |

| 32        | 40     | Reserved                                 |  |  |  |  |  |

| 33        | 41     | Reserved                                 |  |  |  |  |  |

| 34        | 42     | Reserved                                 |  |  |  |  |  |

| 35        | 43     | Reserved                                 |  |  |  |  |  |

| 36        | 44     | Reserved                                 |  |  |  |  |  |

| 37        | 45     | Reserved                                 |  |  |  |  |  |

| 38        | 46     | Reserved                                 |  |  |  |  |  |

| 39        | 47     | PWM – PWM Period Match                   |  |  |  |  |  |

| 40        | 48     | QEI – QEI Interrupt                      |  |  |  |  |  |

| 41        | 49     | Reserved                                 |  |  |  |  |  |

| 42        | 50     | Reserved                                 |  |  |  |  |  |

| 43        | 51     | FLTA – PWM Fault A                       |  |  |  |  |  |

| 44        | 52     | Reserved                                 |  |  |  |  |  |

| 45-53     | 53-61  | Reserved                                 |  |  |  |  |  |

|           | Lowest | Natural Order Priority                   |  |  |  |  |  |

Note 1: Available on dsPIC30F3011 only

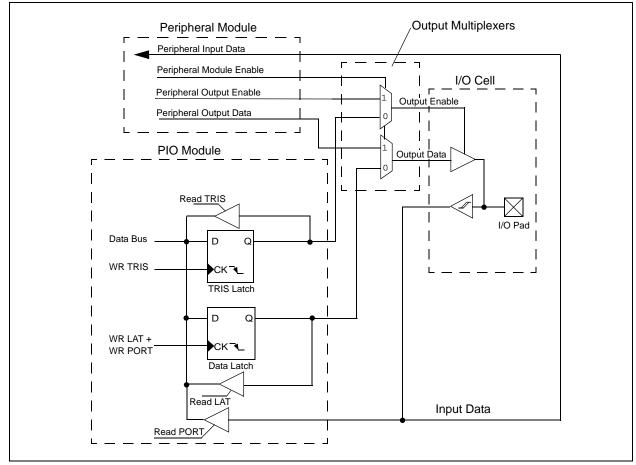

### FIGURE 8-2: BLOCK DIAGRAM OF A SHARED PORT STRUCTURE

## 8.2 Configuring Analog Port Pins

The use of the ADPCFG and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

When reading the PORT register, all pins configured as analog input channel will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins), may cause the input buffer to consume current that exceeds the device specifications.

### 8.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP.

#### EXAMPLE 8-1: PORT WRITE/READ EXAMPLE

| MOV  | 0xFF00, W0 | ; Configure PORTB<15:8><br>; as inputs |

|------|------------|----------------------------------------|

| MOV  | W0, TRISBB | ; and PORTB<7:0> as outputs            |

| NOP  |            | ; Delay 1 cycle                        |

| BTSS | PORTB, #13 | ; Next Instruction                     |

## 9.0 TIMER1 MODULE

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046).

This section describes the 16-bit general purpose Timer1 module and associated operational modes. Figure 9-1 depicts the simplified block diagram of the 16-bit Timer1 module.

| Note: | Timer1                                       | is   | а   | 'Type | A'     | timer. | Refer | to |  |  |  |

|-------|----------------------------------------------|------|-----|-------|--------|--------|-------|----|--|--|--|

|       | Sectio                                       | on : | 23. | "El   | ectric | al     |       |    |  |  |  |

|       | Characteristics", for the specifications for |      |     |       |        |        |       |    |  |  |  |

|       | a Type A timer.                              |      |     |       |        |        |       |    |  |  |  |

The following sections provide a detailed description, including setup and control registers along with associated block diagrams for the operational modes of the timers.

The Timer1 module is a 16-bit timer which can serve as the time counter for the Real-time Clock (RTC), or operate as a free-running interval timer/counter. The 16-bit timer has the following modes:

- 16-bit Timer

- 16-bit Synchronous Counter

- 16-bit Asynchronous Counter

Further, the following operational characteristics are supported:

- Timer gate operation

- Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

These operating modes are determined by setting the appropriate bit(s) in the 16-bit SFR, T1CON. Figure 9-1 presents a block diagram of the 16-bit timer module.

**16-Bit Timer Mode:** In the 16-Bit Timer mode, the timer increments on every instruction cycle up to a match value, preloaded into the Period register, PR1, then resets to '0' and continues to count.

When the CPU goes into the Idle mode, the timer will stop incrementing unless the TSIDL bit (T1CON<13>) = 0. If TSIDL = 1, the timer module logic will resume the incrementing sequence upon termination of the CPU Idle mode.

**16-bit Synchronous Counter Mode:** In the 16-bit Synchronous Counter mode, the timer increments on the rising edge of the applied external clock signal, which is synchronized with the internal phase clocks. The timer counts up to a match value preloaded in PR1, then resets to '0' and continues.

When the CPU goes into the Idle mode, the timer will stop incrementing, unless the respective TSIDL bit = 0. If TSIDL = 1, the timer module logic will resume the incrementing sequence upon termination of the CPU Idle mode.

**16-Bit Asynchronous Counter Mode:** In the 16-Bit Asynchronous Counter mode, the timer increments on every rising edge of the applied external clock signal. The timer counts up to a match value preloaded in PR1, then resets to '0' and continues.

When the timer is configured for the Asynchronous mode of operation and the CPU goes into the Idle mode, the timer will stop incrementing if TSIDL = 1.

# TABLE 11-1: TIMER4/5 REGISTER MAP<sup>(1)</sup>

| SFR Name                  | Addr. | Bit 15 | Bit 14                                               | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7       | Bit 6 | Bit 5  | Bit 4               | Bit 3               | Bit 2 | Bit 1 | Bit 0 | Reset State         |

|---------------------------|-------|--------|------------------------------------------------------|--------|--------|--------|--------|-------|-------|-------------|-------|--------|---------------------|---------------------|-------|-------|-------|---------------------|

| TMR4 0114 Timer4 Register |       |        |                                                      |        |        |        |        |       |       |             |       |        | uuuu uuuu uuuu uuuu |                     |       |       |       |                     |

| TMR5HLD                   | 0116  |        | Timer5 Holding Register (For 32-bit operations only) |        |        |        |        |       |       |             |       |        |                     | uuuu uuuu uuuu uuuu |       |       |       |                     |

| TMR5                      | 0118  |        | Timer5 Register                                      |        |        |        |        |       |       |             |       |        |                     | uuuu uuuu uuuu uuuu |       |       |       |                     |

| PR4                       | 011A  |        |                                                      |        |        |        |        |       | Pe    | riod Regist | er 4  |        |                     |                     |       |       |       | 1111 1111 1111 1111 |

| PR5                       | 011C  |        |                                                      |        |        |        |        |       | Pe    | riod Regist | er 5  |        |                     |                     |       |       |       | 1111 1111 1111 1111 |

| T4CON                     | 011E  | TON    | —                                                    | TSIDL  | —      | _      | —      | —     | —     | —           | TGATE | TCKPS1 | TCKPS0              | T45                 | —     | TCS   | _     | 0000 0000 0000 0000 |

| T5CON                     | 0120  | TON    | —                                                    | TSIDL  | —      | —      | —      | —     | —     | —           | TGATE | TCKPS1 | TCKPS0              | —                   | —     | TCS   | —     | 0000 0000 0000 0000 |

Legend: u = uninitialized bit; — = unimplemented bit, read as '0'

Note 1: Refer to "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields.

NOTES:

#### 18.5.2 FRAMING ERROR (FERR)

The FERR bit (UxSTA<2>) is set if a '0' is detected instead of a Stop bit. If two Stop bits are selected, both Stop bits must be '1'; otherwise, FERR will be set. The read-only FERR bit is buffered along with the received data; it is cleared on any Reset.

#### 18.5.3 PARITY ERROR (PERR)

The PERR bit (UxSTA<3>) is set if the parity of the received word is incorrect. This error bit is applicable only if a Parity mode (odd or even) is selected. The read-only PERR bit is buffered along with the received data bytes; it is cleared on any Reset.

#### 18.5.4 IDLE STATUS

When the receiver is active (i.e., between the initial detection of the Start bit and the completion of the Stop bit), the RIDLE bit (UxSTA<4>) is '0'. Between the completion of the Stop bit and detection of the next Start bit, the RIDLE bit is '1', indicating that the UART is Idle.

#### 18.5.5 RECEIVE BREAK

The receiver will count and expect a certain number of bit times based on the values programmed in the PDSEL (UxMODE<2:1>) and STSEL (UxMODE<0>) bits.

If the break is longer than 13 bit times, the reception is considered complete after the number of bit times specified by PDSEL and STSEL. The URXDA bit is set, FERR is set, zeros are loaded into the receive FIFO, interrupts are generated, if appropriate and the RIDLE bit is set.

When the module receives a long Break signal and the receiver has detected the Start bit, the data bits and the invalid Stop bit (which sets the FERR), the receiver must wait for a valid Stop bit before looking for the next Start bit. It cannot assume that the Break condition on the line is the next Start bit.

Break is regarded as a character containing all 0's, with the FERR bit set. The Break character is loaded into the buffer. No further reception can occur until a Stop bit is received. Note that RIDLE goes high when the Stop bit has not been received yet.

#### 18.6 Address Detect Mode

Setting the ADDEN bit (UxSTA<5>) enables the Address Detect mode, in which a 9th bit (URX8) value of '1' identifies the received word as an address rather than data. This mode is only applicable for 9-bit data communication. The URXISEL control bit does not have any impact on interrupt generation in this mode, since an interrupt (if enabled) will be generated every time the received word has the 9th bit set.

### 18.7 Loopback Mode

Setting the LPBACK bit enables this special mode in which the UxTX pin is internally connected to the UxRX pin. When configured for the Loopback mode, the UxRX pin is disconnected from the internal UART receive logic. However, the UxTX pin still functions as in a normal operation.

To select this mode:

- a) Configure UART for desired mode of operation.

- b) Set LPBACK = 1 to enable Loopback mode.

- c) Enable transmission as defined in **Section 18.3** "**Transmitting Data**".

### 18.8 Baud Rate Generator

The UART has a 16-bit Baud Rate Generator to allow maximum flexibility in baud rate generation. The Baud Rate Generator register (UxBRG) is readable and writable. The baud rate is computed as follows:

- BRG = 16-bit value held in UxBRG register (0 through 65535)

- FCY = Instruction Clock Rate (1/Tcy)

The baud rate is given by Equation 18-1.

## EQUATION 18-1: BAUD RATE

Baud Rate = FCY / (16\*(BRG+1))

Therefore, maximum baud rate possible is

FCY / 16 (if BRG = 0),

and the minimum baud rate possible is

FCY / (16 \* 65536).

With a full 16-bit Baud Rate Generator, at 30 MIPs operation, the minimum baud rate achievable is 28.5 bps.

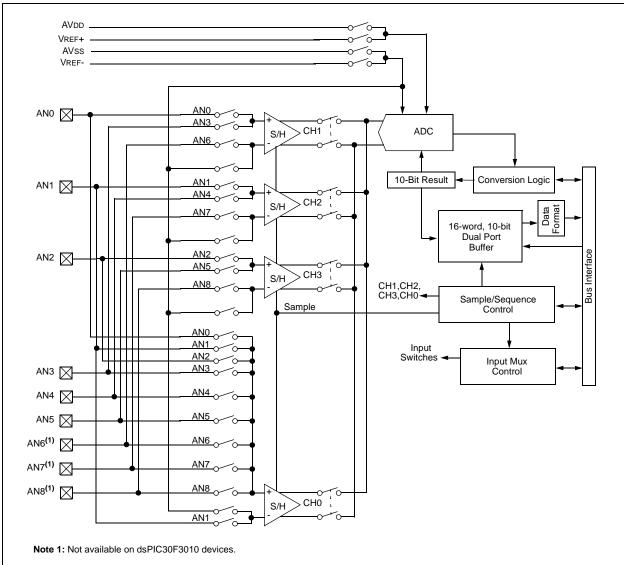

#### FIGURE 19-1: 10-BIT HIGH-SPEED ADC FUNCTIONAL BLOCK DIAGRAM

### 19.4 Programming the Start of Conversion Trigger

The conversion trigger will terminate acquisition and start the requested conversions.

The SSRC<2:0> bits select the source of the conversion trigger.

The SSRC bits provide for up to five alternate sources of conversion trigger.

When SSRC<2:0> = 000, the conversion trigger is under software control. Clearing the SAMP bit will cause the conversion trigger.

When SSRC<2:0> = 111 (Auto-Start mode), the conversion trigger is under A/D clock control. The SAMC bits select the number of A/D clocks between the start of acquisition and the start of conversion. This provides the fastest conversion rates on multiple channels. The SAMC bits must always be at least one clock cycle.

Other trigger sources can come from timer modules, motor control PWM module or external interrupts.

Note: To operate the A/D at the maximum specified conversion speed, the autoconvert trigger option should be selected (SSRC = 111) and the auto-sample time bits should be set to 1 TAD (SAMC = 00001). This configuration will give a total conversion period (sample + convert) of 13 TAD.

The use of any other conversion trigger will result in additional TAD cycles to synchronize the external event to the A/D.

## 19.5 Aborting a Conversion

Clearing the ADON bit during a conversion will abort the current conversion and stop the sampling sequencing. The ADCBUF will not be updated with the partially completed A/D conversion sample. That is, the ADCBUF will continue to contain the value of the last completed conversion (or the last value written to the ADCBUF register).

If the clearing of the ADON bit coincides with an auto-start, the clearing has a higher priority.

After the A/D conversion is aborted, a 2 TAD wait is required before the next sampling may be started by setting the SAMP bit.

If sequential sampling is specified, the A/D will continue at the next sample pulse which corresponds with the next channel converted. If simultaneous sampling is specified, the A/D will continue with the next multi-channel group conversion sequence.

## 19.6 Selecting the A/D Conversion Clock

The A/D conversion requires 12 TAD. The source of the A/D conversion clock is software selected using a 6-bit counter. There are 64 possible options for TAD.

#### EQUATION 19-1: A/D CONVERSION CLOCK

$$TAD = TCY \bullet (0.5 \bullet (ADCS < 5:0 > + 1))$$

$$ADCS < 5:0 > = 2 \quad \frac{TAD}{TCY} - 1$$

The internal RC oscillator is selected by setting the ADRC bit.

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 83.33 nsec (for VDD = 5V). Refer to **Section 23.0 "Electrical Characteristics"** for minimum TAD under other operating conditions.

Example 19-1 shows a sample calculation for the ADCS<5:0> bits, assuming a device operating speed of 30 MIPS.

#### EXAMPLE 19-1: A/D CONVERSION CLOCK CALCULATION

TAD = 154 nsec

TCY = 33 nsec (30 MIPS)

ADCS<5:0> = 2

$$\frac{TAD}{TCY} - 1$$

= 2  $\cdot \frac{154 \text{ nsec}}{33 \text{ nsec}} - 1$

= 8.33

Therefore,

Set ADCS<5:0> = 9

Actual TAD =  $\frac{TCY}{2}$  (ADCS<5:0> + 1)

=  $\frac{33 \text{ nsec}}{2}$  (9 + 1)

= 165 nsec

## TABLE 20-1: OSCILLATOR OPERATING MODES

| Oscillator Mode | Description                                                                        |

|-----------------|------------------------------------------------------------------------------------|

| XTL             | 200 kHz-4 MHz crystal on OSC1:OSC2.                                                |

| хт              | 4 MHz-10 MHz crystal on OSC1:OSC2.                                                 |

| XT w/PLL 4x     | 4 MHz-10 MHz crystal on OSC1:OSC2, 4x PLL enabled.                                 |

| XT w/PLL 8x     | 4 MHz-10 MHz crystal on OSC1:OSC2, 8x PLL enabled.                                 |

| XT w/PLL 16x    | 4 MHz-10 MHz crystal on OSC1:OSC2, 16x PLL enabled <sup>(1)</sup> .                |

| LP              | 32 kHz crystal on SOSCO:SOSCI <sup>(2)</sup> .                                     |

| HS              | 10 MHz-25 MHz crystal.                                                             |

| HS/2 w/PLL 4x   | 10 MHz-25 MHz crystal, divide by 2, 4x PLL enabled.                                |

| HS/2 w/PLL 8x   | 10 MHz-25MHz crystal, divide by 2, 8x PLL enabled.                                 |

| HS/2 w/PLL 16x  | 10 MHz-25MHz crystal, divide by 2, 16x PLL enabled <sup>(1)</sup> .                |

| HS/3 w/PLL 4x   | 10 MHz-25 MHz crystal, divide by 3, 4x PLL enabled.                                |

| HS/3 w/PLL 8x   | 10 MHz-25MHz crystal, divide by 3, 8x PLL enabled.                                 |

| HS/3 w/PLL 16x  | 10 MHz-25MHz crystal, divide by 3, 16x PLL enabled <sup>(1)</sup> .                |

| EC              | External clock input (0-40 MHz).                                                   |

| ECIO            | External clock input (0-40 MHz), OSC2 pin is I/O.                                  |

| EC w/PLL 4x     | External clock input (4-10 MHz), OSC2 pin is I/O, 4x PLL enabled <sup>(1)</sup> .  |

| EC w/PLL 8x     | External clock input (4-10 MHz), OSC2 pin is I/O, 8x PLL enabled <sup>(1)</sup> .  |

| EC w/PLL 16x    | External clock input (4-10 MHz), OSC2 pin is I/O, 16x PLL enabled <sup>(1)</sup> . |

| ERC             | External RC oscillator, OSC2 pin is Fosc/4 output <sup>(3)</sup> .                 |

| ERCIO           | External RC oscillator, OSC2 pin is I/O <sup>(3)</sup> .                           |

| FRC             | 8 MHz internal RC oscillator.                                                      |

| FRC w/PLL 4x    | 7.37 MHz Internal RC oscillator, 4x PLL enabled.                                   |

| FRC w/PLL 8x    | 7.37 MHz Internal RC oscillator, 8x PLL enabled.                                   |

| FRC w/PLL 16x   | 7.37 MHz Internal RC oscillator, 16x PLL enabled.                                  |

| LPRC            | 512 kHz internal RC oscillator.                                                    |

**Note 1:** dsPIC30F maximum operating frequency of 120 MHz must be met.

2: LP oscillator can be conveniently shared as system clock, as well as real-time clock for Timer1.

3: Requires external R and C. Frequency operation up to 4 MHz.

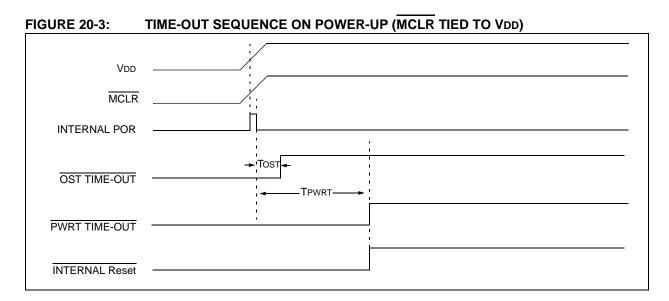

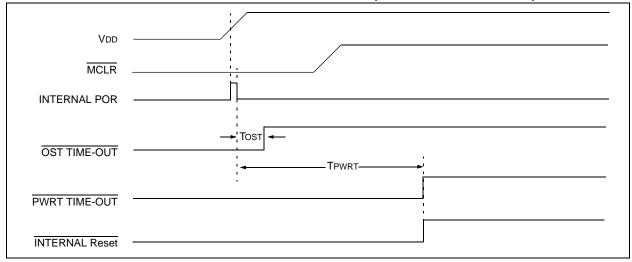

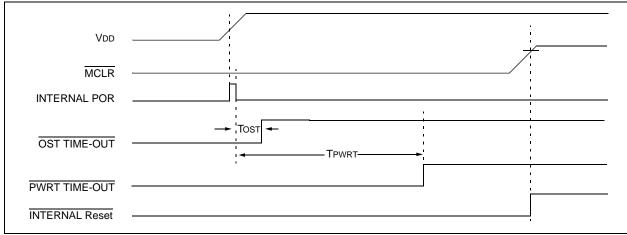

FIGURE 20-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

FIGURE 20-5: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

| Field                                                                                                                                                                                                                                                                                                                                                                                                                       | Description                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Wb                                                                                                                                                                                                                                                                                                                                                                                                                          | Base W register ∈ {W0W15}                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| Wd                                                                                                                                                                                                                                                                                                                                                                                                                          | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                                                                                                                                              |  |  |  |  |  |  |  |  |

| Wdo                                                                                                                                                                                                                                                                                                                                                                                                                         | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] }                                                                                                                           |  |  |  |  |  |  |  |  |

| Wm,Wn                                                                                                                                                                                                                                                                                                                                                                                                                       | Dividend, Divisor Working register pair (direct addressing)                                                                                                                                                    |  |  |  |  |  |  |  |  |

| Wm*Wm                                                                                                                                                                                                                                                                                                                                                                                                                       | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4*W4,W5*W5,W6*W6,W7*W7}                                                                                                          |  |  |  |  |  |  |  |  |

| Wm*Wn       Multiplicand and Multiplier working register pair for DSP instructions ∈         {W4*W5,W4*W6,W4*W7,W5*W6,W5*W7,W6*W7}                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| Wn                                                                                                                                                                                                                                                                                                                                                                                                                          | One of 16 working registers ∈ {W0W15}                                                                                                                                                                          |  |  |  |  |  |  |  |  |

| Wnd                                                                                                                                                                                                                                                                                                                                                                                                                         | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                              |  |  |  |  |  |  |  |  |

| Wns                                                                                                                                                                                                                                                                                                                                                                                                                         | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| WREG                                                                                                                                                                                                                                                                                                                                                                                                                        | W0 (working register used in File register instructions)                                                                                                                                                       |  |  |  |  |  |  |  |  |

| Ws                                                                                                                                                                                                                                                                                                                                                                                                                          | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Wso                                                                                                                                                                                                                                                                                                                                                                                                                         | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                |  |  |  |  |  |  |  |  |

| Wx                                                                                                                                                                                                                                                                                                                                                                                                                          | X data space Prefetch Address register for DSP instructions<br>∈ {[W8]+=6, [W8]+=4, [W8]+=2, [W8], [W8]-=6, [W8]-=4, [W8]-=2,<br>[W9]+=6, [W9]+=4, [W9]+=2, [W9], [W9]-=6, [W9]-=4, [W9]-=2,<br>[W9+W12],none} |  |  |  |  |  |  |  |  |

| Wxd                                                                                                                                                                                                                                                                                                                                                                                                                         | X data space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                       |  |  |  |  |  |  |  |  |

| $ \begin{array}{c} \mathbb{W}_{Y} \\ \mathbb{W}_{Y} \\ \in \{[\mathbb{W}10] + =6, [\mathbb{W}10] + =4, [\mathbb{W}10] + =2, [\mathbb{W}10], [\mathbb{W}10] - =6, [\mathbb{W}10] - =4, [\mathbb{W}10] - =2, \\ [\mathbb{W}11] + =6, [\mathbb{W}11] + =4, [\mathbb{W}11] + =2, [\mathbb{W}11], [\mathbb{W}11] - =6, [\mathbb{W}11] - =4, [\mathbb{W}11] - =2, \\ [\mathbb{W}11 + \mathbb{W}12], \text{ none} \} \end{array} $ |                                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| Wyd                                                                                                                                                                                                                                                                                                                                                                                                                         | Y data space Prefetch Destination register for DSP instructions ∈ {W4W7}                                                                                                                                       |  |  |  |  |  |  |  |  |

## TABLE 21-1: SYMBOLS USED IN OPCODE DESCRIPTIONS (CONTINUED)

### TABLE 21-2: INSTRUCTION SET OVERVIEW

| Base<br>Instr<br># | Assembly<br>Mnemonic |       | Assembly Syntax | Description                              | # of<br>words | # of<br>cycle<br>s | Status Flags<br>Affected |

|--------------------|----------------------|-------|-----------------|------------------------------------------|---------------|--------------------|--------------------------|

| 1                  | ADD                  | ADD   | Acc             | Add Accumulators                         | 1             | 1                  | OA,OB,SA,SB              |

|                    |                      | ADD   | f               | f = f + WREG                             | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | f,WREG          | WREG = f + WREG                          | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | #lit10,Wn       | Wd = lit10 + Wd                          | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,Ws,Wd        | Wd = Wb + Ws                             | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wb,#lit5,Wd     | Wd = Wb + lit5                           | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADD   | Wso,#Slit4,Acc  | 16-bit Signed Add to Accumulator         | 1             | 1                  | OA,OB,SA,SB              |

| 2                  | ADDC                 | ADDC  | f               | f = f + WREG + (C)                       | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADDC  | f,WREG          | WREG = f + WREG + (C)                    | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADDC  | #lit10,Wn       | Wd = Iit10 + Wd + (C)                    | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,Ws,Wd        | Wd = Wb + Ws + (C)                       | 1             | 1                  | C,DC,N,OV,Z              |

|                    |                      | ADDC  | Wb,#lit5,Wd     | Wd = Wb + lit5 + (C)                     | 1             | 1                  | C,DC,N,OV,Z              |

| 3                  | AND                  | AND   | f               | f = f .AND. WREG                         | 1             | 1                  | N,Z                      |

|                    |                      | AND   | f,WREG          | WREG = f .AND. WREG                      | 1             | 1                  | N,Z                      |

|                    |                      | AND   | #lit10,Wn       | Wd = lit10 .AND. Wd                      | 1             | 1                  | N,Z                      |

|                    |                      | AND   | Wb,Ws,Wd        | Wd = Wb .AND. Ws                         | 1             | 1                  | N,Z                      |

|                    |                      | AND   | Wb,#lit5,Wd     | Wd = Wb .AND. lit5                       | 1             | 1                  | N,Z                      |

| 4                  | ASR                  | ASR   | f               | f = Arithmetic Right Shift f             | 1             | 1                  | C,N,OV,Z                 |

|                    |                      | ASR   | f,WREG          | WREG = Arithmetic Right Shift f          | 1             | 1                  | C,N,OV,Z                 |

|                    |                      | ASR   | Ws,Wd           | Wd = Arithmetic Right Shift Ws           | 1             | 1                  | C,N,OV,Z                 |

|                    |                      | ASR   | Wb,Wns,Wnd      | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1                  | N,Z                      |

|                    |                      | ASR   | Wb,#lit5,Wnd    | Wnd = Arithmetic Right Shift Wb by lit5  | 1             | 1                  | N,Z                      |

| 5                  | BCLR                 | BCLR  | f,#bit4         | Bit Clear f                              | 1             | 1                  | None                     |

|                    |                      | BCLR  | Ws,#bit4        | Bit Clear Ws                             | 1             | 1                  | None                     |

| 6                  | BRA                  | BRA   | C,Expr          | Branch if Carry                          | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | GE, Expr        | Branch if Greater than or Equal          | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | GEU, Expr       | Branch if Unsigned Greater than or Equal | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | GT,Expr         | Branch if Greater than                   | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | GTU, Expr       | Branch if Unsigned Greater than          | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | LE,Expr         | Branch if Less than or Equal             | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | LEU, Expr       | Branch if Unsigned Less than or Equal    | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | LT,Expr         | Branch if Less than                      | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | LTU, Expr       | Branch if Unsigned Less than             | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | N,Expr          | Branch if Negative                       | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | NC,Expr         | Branch if Not Carry                      | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | NN,Expr         | Branch if Not Negative                   | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | NOV,Expr        | Branch if Not Overflow                   | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | NZ,Expr         | Branch if Not Zero                       | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | OA,Expr         | Branch if Accumulator A Overflow         | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | OB,Expr         | Branch if Accumulator B Overflow         | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | OV,Expr         | Branch if Overflow                       | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | SA,Expr         | Branch if Accumulator A Saturated        | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | SB,Expr         | Branch if Accumulator B Saturated        | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | Expr            | Branch Unconditionally                   | 1             | 2                  | None                     |

|                    |                      | BRA   | Z,Expr          | Branch if Zero                           | 1             | 1 (2)              | None                     |

|                    |                      | BRA   | Wn              | Computed Branch                          | 1             | 2                  | None                     |

| 7                  | BSET                 | BSET  | f,#bit4         | Bit Set f                                | 1             | 1                  | None                     |

|                    |                      | BSET  | Ws,#bit4        | Bit Set Ws                               | 1             | 1                  | None                     |

| 8                  | BSW                  | BSW.C | Ws,Wb           | Write C bit to Ws <wb></wb>              | 1             | 1                  | None                     |

|                    |                      | BSW.Z | Ws,Wb           | Write Z bit to Ws <wb></wb>              | 1             | 1                  | None                     |

### TABLE 23-14: PLL CLOCK TIMING SPECIFICATIONS (VDD = 2.5 TO 5.5 V)

| AC CHA       | RACTERI | STICS                 | Standard Operating Conditions: 2.5V to 5.5V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                  |                    |                     |       |                                   |  |  |

|--------------|---------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------|---------------------|-------|-----------------------------------|--|--|

| Param<br>No. | Symbol  | Characterist          | ic <sup>(1)</sup>                                                                                                                                                                                    | Min              | Тур <sup>(2)</sup> | Max                 | Units | Conditions                        |  |  |

| OS50         | Fplli   | PLL Input Frequency   | Range <sup>(2)</sup>                                                                                                                                                                                 | 4                | _                  | 10                  | MHz   | EC with 4x PLL                    |  |  |

|              |         |                       | -                                                                                                                                                                                                    | 4                | —                  | 10                  | MHz   | EC with 8x PLL                    |  |  |

|              |         |                       |                                                                                                                                                                                                      | 4                | _                  | 7.5 <sup>(4)</sup>  | MHz   | EC with 16x PLL                   |  |  |

|              |         |                       |                                                                                                                                                                                                      | 4                | —                  | 10                  | MHz   | XT with 4x PLL                    |  |  |

|              |         |                       |                                                                                                                                                                                                      | 4                | _                  | 10                  | MHz   | XT with 8x PLL                    |  |  |

|              |         |                       |                                                                                                                                                                                                      | 4                | —                  | 7.5 <sup>(4)</sup>  | MHz   | XT with 16x PLL                   |  |  |

|              |         |                       |                                                                                                                                                                                                      | 5 <b>(3)</b>     | —                  | 10                  | MHz   | HS/2 with 4x PLL                  |  |  |

|              |         |                       |                                                                                                                                                                                                      | 5 <sup>(3)</sup> | —                  | 10                  | MHz   | HS/2 with 8x PLL                  |  |  |

|              |         |                       |                                                                                                                                                                                                      | 5 <sup>(3)</sup> | —                  | 7.5 <sup>(4)</sup>  | MHz   | HS/2 with 16x PLL                 |  |  |

|              |         |                       |                                                                                                                                                                                                      | 4                | —                  | 8.33 <sup>(3)</sup> | MHz   | HS/3 with 4x PLL                  |  |  |

|              |         |                       |                                                                                                                                                                                                      | 4                | _                  | 8.33 <sup>(3)</sup> | MHz   | HS/3 with 8x PLL                  |  |  |

|              |         |                       |                                                                                                                                                                                                      | 4                | —                  | 7.5 <sup>(4)</sup>  | MHz   | HS/3 with 16x PLL                 |  |  |

| OS51         | Fsys    | On-Chip PLL Output    | (2)                                                                                                                                                                                                  | 16               | _                  | 120                 | MHz   | EC, XT, HS/2, HS/3 modes with PLL |  |  |

| OS52         | TLOC    | PLL Start-up Time (Ic | ock time)                                                                                                                                                                                            | _                | 20                 | 50                  | μS    |                                   |  |  |

$\label{eq:Note 1: These parameters are characterized but not tested in manufacturing.$

2: Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** Limited by oscillator frequency range.

4: Limited by device operating frequency range.

### TABLE 23-15: PLL JITTER

| AC CHA       | RACTERISTICS   |     |                    |       |       |                                                                      |                   |  |

|--------------|----------------|-----|--------------------|-------|-------|----------------------------------------------------------------------|-------------------|--|

| Param<br>No. | Characteristic | Min | Typ <sup>(1)</sup> | Max   | Units | Conditions                                                           |                   |  |

| OS61         | x4 PLL         | _   | 0.251              | 0.413 | %     | $\text{-40°C} \leq \text{TA} \leq \text{+85°C}$                      | VDD = 3.0 to 3.6V |  |

|              |                | —   | 0.251              | 0.413 | %     | $-40^{\circ}C \le TA \le +125^{\circ}C$                              | VDD = 3.0 to 3.6V |  |

|              |                | —   | 0.256              | 0.47  | %     | $\textbf{-40^{\circ}C} \leq \textbf{TA} \leq \textbf{+85^{\circ}C}$  | VDD = 4.5 to 5.5V |  |

|              |                | —   | 0.256              | 0.47  | %     | $\text{-40°C} \leq \text{TA} \leq \text{+125°C}$                     | VDD = 4.5 to 5.5V |  |

|              | x8 PLL         | —   | 0.355              | 0.584 | %     | $\textbf{-40^{\circ}C} \leq \textbf{TA} \leq \textbf{+85^{\circ}C}$  | VDD = 3.0 to 3.6V |  |

|              |                | —   | 0.355              | 0.584 | %     | $\textbf{-40^{\circ}C} \leq \textbf{TA} \leq \textbf{+125^{\circ}C}$ | VDD = 3.0 to 3.6V |  |

|              |                | —   | 0.362              | 0.664 | %     | $\textbf{-40^{\circ}C} \leq \textbf{TA} \leq \textbf{+85^{\circ}C}$  | VDD = 4.5 to 5.5V |  |

|              |                | —   | 0.362              | 0.664 | %     | $-40^{\circ}C \leq TA \leq +125^{\circ}C$                            | VDD = 4.5 to 5.5V |  |

|              | x16 PLL        | —   | 0.67               | 0.92  | %     | $\textbf{-40^{\circ}C} \leq \textbf{TA} \leq \textbf{+85^{\circ}C}$  | VDD = 3.0 to 3.6V |  |

|              |                | _   | 0.632              | 0.956 | %     | $\textbf{-40^{\circ}C} \leq \textbf{TA} \leq \textbf{+85^{\circ}C}$  | VDD = 4.5 to 5.5V |  |

|              |                | _   | 0.632              | 0.956 | %     | $-40^{\circ}C \leq TA \leq +125^{\circ}C$                            | VDD = 4.5 to 5.5V |  |

Note 1: These parameters are characterized but not tested in manufacturing.

| Clock<br>Oscillator<br>Mode | Fosc<br>(MHz) <sup>(1)</sup> | Τ <b>CY (μsec)<sup>(2)</sup></b> | MIPS <sup>(3)</sup><br>w/o PLL | MIPS <sup>(3)</sup><br>w PLL x4 | MIPS <sup>(3)</sup><br>w PLL x8 | MIPS <sup>(3)</sup><br>w PLL x16 |

|-----------------------------|------------------------------|----------------------------------|--------------------------------|---------------------------------|---------------------------------|----------------------------------|

| EC                          | 0.200                        | 20.0                             | 0.05                           | _                               | _                               | —                                |

|                             | 4                            | 1.0                              | 1.0                            | 4.0                             | 8.0                             | 16.0                             |

|                             | 10                           | 0.4                              | 2.5                            | 10.0                            | 20.0                            | —                                |

|                             | 25                           | 0.16                             | 6.25                           | _                               | _                               | —                                |

| XT                          | 4                            | 1.0                              | 1.0                            | 4.0                             | 8.0                             | 16.0                             |

|                             | 10                           | 0.4                              | 2.5                            | 10.0                            | 20.0                            | —                                |

TABLE 23-16: INTERNAL CLOCK TIMING EXAMPLES

**Note 1:** Assumption: Oscillator Postscaler is divide by 1.

**2:** Instruction Execution Cycle Time: TCY = 1/MIPS.

3: Instruction Execution Frequency: MIPS = (Fosc \* PLLx)/4 since there are 4 Q clocks per instruction cycle.

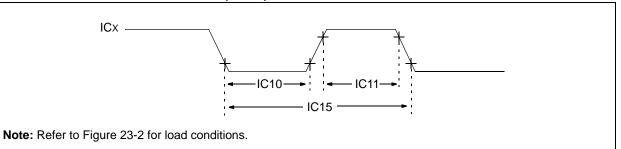

#### FIGURE 23-9: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

#### TABLE 23-26: INPUT CAPTURE TIMING REQUIREMENTS

| AC CHARACTERISTICS            |                               |                  | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.5V to 5.5V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |                                   |   |    |                                  |  |

|-------------------------------|-------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---|----|----------------------------------|--|

| Param<br>No. Symbol Character |                               |                  | ristic <sup>(1)</sup>                                                                                                                                                                                                                                                             | stic <sup>(1)</sup> Min Max Units |   |    |                                  |  |

| IC10                          | IC10 TccL ICx Input Low Time  |                  | No prescaler                                                                                                                                                                                                                                                                      | 0.5 TCY + 20                      |   | ns |                                  |  |

|                               |                               |                  | With prescaler                                                                                                                                                                                                                                                                    | 10                                | _ | ns |                                  |  |

| IC11                          | IC11 TccH ICx Input High Time |                  | No prescaler                                                                                                                                                                                                                                                                      | 0.5 TCY + 20                      | _ | ns |                                  |  |

|                               |                               |                  | With prescaler                                                                                                                                                                                                                                                                    | 10                                | _ | ns |                                  |  |