Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 20 MIPS                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, Motor Control PWM, QEI, POR, PWM, WDT                  |

| Number of I/O              | 30                                                                             |

| Program Memory Size        | 24KB (8K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | 1K x 8                                                                         |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                    |

| Data Converters            | A/D 9x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic30f3011t-20e-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                            | 11  |

|-------|------------------------------------------------------------|-----|

| 2.0   | CPU Architecture Overview                                  | 19  |

| 3.0   | Memory Organization                                        | 27  |

| 4.0   | Address Generator Units                                    | 39  |

| 5.0   | Interrupts                                                 | 45  |

| 6.0   | Flash Program Memory                                       | 51  |

| 7.0   | Data EEPROM Memory                                         | 57  |

| 8.0   | I/O Ports                                                  | 61  |

| 9.0   | Timer1 Module                                              | 67  |

| 10.0  | Timer2/3 Module                                            | 71  |

| 11.0  | Timer4/5 Module                                            |     |

| 12.0  | Input Capture Module                                       | 81  |

| 13.0  | Output Compare Module                                      | 85  |

| 14.0  | Quadrature Encoder Interface (QEI) Module                  | 91  |

| 15.0  | Motor Control PWM Module                                   | 97  |

| 16.0  | SPI Module                                                 | 107 |

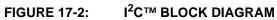

| 17.0  | I2C™ Module                                                |     |

| 18.0  | Universal Asynchronous Receiver Transmitter (UART) Module  |     |

| 19.0  | 10-bit High-Speed Analog-to-Digital Converter (ADC) Module | 127 |

| 20.0  | System Integration                                         | 139 |

| 21.0  | Instruction Set Summary                                    | 155 |

| 22.0  | Development Support                                        | 165 |

| 23.0  | Electrical Characteristics                                 |     |

| 24.0  | Packaging Information                                      | 209 |

| Index | (                                                          | 219 |

|       | Aicrochip Web Site                                         |     |

|       | omer Change Notification Service                           |     |

|       | omer Support                                               |     |

| Read  | er Response                                                | 226 |

| Prod  | uct Identification System                                  | 227 |

|       |                                                            |     |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

• Microchip's Worldwide Web site; http://www.microchip.com

Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

This document contains device-specific information for the dsPIC30F3010/3011 device. The dsPIC30F devices contain extensive Digital Signal Processor (DSP) functionality within a high-performance 16-bit microcontroller (MCU) architecture. Figure 1-1 and Figure 1-2 illustrate device block diagrams for the dsPIC30F3011 and dsPIC30F3010 devices.

| Pin Name                                       | Pin<br>Type                                                                                                                    | Buffer<br>Type                | Description                                                                                                                                                                                                                 |  |  |  |  |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| OSC1<br>OSC2                                   | I<br>I/O                                                                                                                       | ST/CMOS                       | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. |  |  |  |  |  |  |

| PGD<br>PGC                                     | I/O<br>I                                                                                                                       | ST<br>ST                      | n-Circuit Serial Programming data input/output pin.<br>n-Circuit Serial Programming clock input pin.                                                                                                                        |  |  |  |  |  |  |

| RB0-RB8                                        | I/O                                                                                                                            | ST                            | PORTB is a bidirectional I/O port.                                                                                                                                                                                          |  |  |  |  |  |  |

| RC13-RC15                                      | 5 I/O                                                                                                                          | ST                            | PORTC is a bidirectional I/O port.                                                                                                                                                                                          |  |  |  |  |  |  |

| RD0-RD3                                        | I/O                                                                                                                            | ST                            | PORTD is a bidirectional I/O port.                                                                                                                                                                                          |  |  |  |  |  |  |

| RE0-RE5,<br>RE8                                | I/O                                                                                                                            | ST                            | PORTE is a bidirectional I/O port.                                                                                                                                                                                          |  |  |  |  |  |  |

| RF0-RF6                                        | I/O                                                                                                                            | ST                            | PORTF is a bidirectional I/O port.                                                                                                                                                                                          |  |  |  |  |  |  |

| SCK1<br>SDI1<br>SDO1<br>SS1                    | I/O<br>I<br>O<br>I                                                                                                             | ST<br>ST<br>—<br>ST           | Synchronous serial clock input/output for SPI1.<br>SPI1 Data In.<br>SPI1 Data Out.<br>SPI1 Slave Synchronization.                                                                                                           |  |  |  |  |  |  |

| SCL<br>SDA                                     | I/O<br>I/O                                                                                                                     | ST<br>ST                      | Synchronous serial clock input/output for I <sup>2</sup> C.<br>Synchronous serial data input/output for I <sup>2</sup> C.                                                                                                   |  |  |  |  |  |  |

| SOSCO<br>SOSCI                                 | 0<br>                                                                                                                          |                               | 32 kHz low-power oscillator crystal output.<br>32 kHz low-power oscillator crystal input. ST buffer when configured in RC<br>mode; CMOS otherwise.                                                                          |  |  |  |  |  |  |

| T1CK<br>T2CK                                   |                                                                                                                                | ST<br>ST                      | Timer1 external clock input.<br>Timer2 external clock input.                                                                                                                                                                |  |  |  |  |  |  |

| U1RX<br>U1TX<br>U1ARX<br>U1ATX<br>U2RX<br>U2TX | <br>0<br> <br>0<br> <br>0                                                                                                      | ST<br>—<br>ST<br>—<br>ST<br>— | UART1 Receive.<br>UART1 Transmit.<br>UART1 Alternate Receive.<br>UART1 Alternate Transmit.<br>UART2 Receive.<br>UART2 Transmit.                                                                                             |  |  |  |  |  |  |

| Vdd                                            | Р                                                                                                                              | _                             | Positive supply for logic and I/O pins.                                                                                                                                                                                     |  |  |  |  |  |  |

| Vss                                            | Р                                                                                                                              | _                             | Ground reference for logic and I/O pins.                                                                                                                                                                                    |  |  |  |  |  |  |

| Vref+                                          | I                                                                                                                              | Analog                        | Analog Voltage Reference (High) input.                                                                                                                                                                                      |  |  |  |  |  |  |

| Vref-                                          | I                                                                                                                              | Analog                        | Analog Voltage Reference (Low) input.                                                                                                                                                                                       |  |  |  |  |  |  |

|                                                | egend:CMOS =CMOS compatible input or outputAnalog =Analog inputST=Schmitt Trigger input with CMOS levelsO=OutputI=InputP=Power |                               |                                                                                                                                                                                                                             |  |  |  |  |  |  |

TABLE 1-1: dsPIC30F3011 I/O PIN DESCRIPTIONS (CONTINUED)

Table 1-2 provides a brief description of the device I/O pinout and the functions that are multiplexed to a port pin. Multiple functions may exist on one port pin. When multiplexing occurs, the peripheral module's functional requirements may force an override of the data direction of the port pin.

| Pin Name                                                           | Pin<br>Type                                          | Buffer<br>Type                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

|--------------------------------------------------------------------|------------------------------------------------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| AN0-AN5                                                            | I                                                    | Analog                                 | Analog input channels.<br>AN0 and AN1 are also used for device programming data and clock inputs,<br>respectively.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| AVdd                                                               | Р                                                    | Р                                      | Positive supply for analog module. This pin must be connected at all times.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| AVss                                                               | Р                                                    | Р                                      | Ground reference for analog module. This pin must be connected at all times.                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| CLKI<br>CLKO                                                       | і<br>0                                               | ST/CMOS                                | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                                                                                                                                                                                                |  |  |  |  |  |  |

| CN0-CN7                                                            | I                                                    | ST                                     | Always associated with OSC2 pin function.<br>Input change notification inputs.<br>Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| EMUD<br>EMUC<br>EMUD1<br>EMUC1<br>EMUD2<br>EMUC2<br>EMUD3<br>EMUC3 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | ST<br>ST<br>ST<br>ST<br>ST<br>ST<br>ST | CD Primary Communication Channel data input/output pin.<br>CD Primary Communication Channel clock input/output pin.<br>CD Secondary Communication Channel data input/output pin.<br>CD Secondary Communication Channel clock input/output pin.<br>CD Tertiary Communication Channel data input/output pin.<br>CD Tertiary Communication Channel clock input/output pin.<br>CD Tertiary Communication Channel clock input/output pin. |  |  |  |  |  |  |

| IC1, IC2, IC7,<br>IC8                                              | I                                                    | ST                                     | ICD Quaternary Communication Channel clock input/output pin.<br>Capture inputs 1, 2, 7 and 8.                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| INDX<br>QEA<br>QEB                                                 | <br>                                                 | ST<br>ST<br>ST                         | Quadrature Encoder Index Pulse input.<br>Quadrature Encoder Phase A input in QEI mode.<br>Auxiliary Timer External Clock/Gate input in Timer mode.<br>Quadrature Encoder Phase B input in QEI mode.                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| INT0<br>INT1<br>INT2                                               |                                                      | ST<br>ST<br>ST                         | Auxiliary Timer External Clock/Gate input in Timer mode.<br>External interrupt 0.<br>External interrupt 1.<br>External interrupt 2.                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| FLTA<br>PWM1L<br>PWM1H<br>PWM2L<br>PWM2H<br>PWM3L<br>PWM3H         | <br>0<br>0<br>0<br>0<br>0                            | ST<br>—<br>—<br>—<br>—<br>—<br>—       | PWM Fault A input.         PWM1 Low output.         PWM1 High output.         PWM2 Low output.         PWM2 High output.         PWM3 Low output.         PWM3 High output.         PWM3 High output.                                                                                                                                                                                                                                |  |  |  |  |  |  |

| MCLR                                                               | I/P                                                  | ST                                     | Master Clear (Reset) input or programming voltage input. This pin is an active low Reset to the device.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| OCFA<br>OC1, OC2                                                   |                                                      |                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Legend: CM<br>ST<br>I                                              | = Sc                                                 |                                        | tible input or outputAnalog =Analog inputr input with CMOS levelsO=OutputP=Power                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

TABLE 1-2: dsPIC30F3010 I/O PIN DESCRIPTIONS

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A sign-extend (SE) instruction is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions, including the DSP instructions, operate only on words.

#### 3.2.5 NEAR DATA SPACE

An 8 Kbyte 'near' data space is reserved in X address memory space between 0x0000 and 0x1FFF, which is directly addressable via a 13-bit absolute address field within all memory direct instructions. The remaining X address space and all of the Y address space is addressable indirectly. Additionally, the whole of X data space is addressable using MOV instructions, which support memory direct addressing with a 16-bit address field.

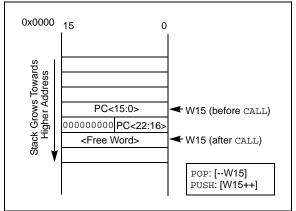

#### 3.2.6 SOFTWARE STACK

The dsPIC DSC device contains a software stack. W15 is used as the Stack Pointer.

The Stack Pointer always points to the first available free word and grows from lower addresses towards higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 3-9. Note that for a PC push during any CALL instruction, the MSB of the PC is zero-extended before the push, ensuring that the MSB is always clear.

Note: A PC push during exception processing will concatenate the SRL register to the MSB of the PC prior to the push. There is a Stack Pointer Limit register (SPLIM) associated with the Stack Pointer. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0', because all stack operations must be word-aligned. Whenever an Effective Address (EA) is generated using W15 as a source or destination pointer, the address thus generated is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value, 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800, thus preventing the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### FIGURE 3-9: CALL STACK FRAME

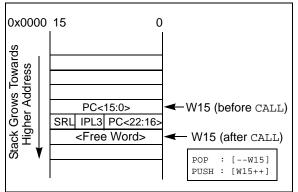

## 5.4 Interrupt Sequence

All interrupt event flags are sampled in the beginning of each instruction cycle by the IFSx registers. A pending Interrupt Request (IRQ) is indicated by the flag bit being equal to a '1' in an IFSx register. The IRQ will cause an interrupt to occur if the corresponding bit in the Interrupt Enable (IECx) register is set. For the remainder of the instruction cycle, the priorities of all pending interrupt requests are evaluated.

If there is a pending IRQ with a priority level greater than the current processor priority level in the IPL bits, the processor will be interrupted.

The processor then stacks the current program counter and the low byte of the processor STATUS register (SRL), as shown in Figure 5-2. The low byte of the STATUS register contains the processor priority level at the time, prior to the beginning of the interrupt cycle. The processor then loads the priority level for this interrupt into the STATUS register. This action will disable all lower priority interrupts until the completion of the Interrupt Service Routine (ISR).

FIGURE 5-2: INTERRUPT STACK FRAME

- Note 1: The user can always lower the priority level by writing a new value into SR. The Interrupt Service Routine must clear the interrupt flag bits in the IFSx register before lowering the processor interrupt priority, in order to avoid recursive interrupts.

- 2: The IPL3 bit (CORCON<3>) is always clear when interrupts are being processed. It is set only during execution of traps.

The RETFIE (Return from Interrupt) instruction will unstack the program counter and STATUS registers to return the processor to its state prior to the interrupt sequence.

#### 5.5 Alternate Vector Table

In program memory, the Interrupt Vector Table (IVT) is followed by the Alternate Interrupt Vector Table (AIVT), as shown in Figure 5-1. Access to the Alternate Vector Table is provided by the ALTIVT bit in the INTCON2 register. If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized the same as the default vectors. The AIVT supports emulation and debugging efforts by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time.

If the AIVT is not required, the program memory allocated to the AIVT may be used for other purposes. AIVT is not a protected section and may be freely programmed by the user.

## 5.6 Fast Context Saving

A context saving option is available using Shadow registers. Shadow registers are provided for the DC, N, OV, Z and C bits in SR, and the registers, W0 through W3. The shadows are only one level deep. The Shadow registers are accessible using the PUSH.S and POP.S instructions only. When the processor vectors to an interrupt, the PUSH.S instruction can be used to store the current value of the aforementioned registers into their respective Shadow registers.

If an ISR of a certain priority uses the PUSH.S and POP.S instructions for fast context saving, then a higher priority ISR should not include the same instructions. Users must save the key registers in software during a lower priority interrupt if the higher priority ISR uses fast context saving.

## 5.7 External Interrupt Requests

The dsPIC30F3010/3011 interrupt controller supports three external interrupt request signals, INT0-INT2. These inputs are edge sensitive; they require a low-tohigh or a high-to-low transition to generate an interrupt request. The INTCON2 register has five bits, INT0EP-INT4EP, that select the polarity of the edge detection circuitry.

## 5.8 Wake-up from Sleep and Idle

The interrupt controller may be used to wake-up the processor from either Sleep or Idle modes if Sleep or Idle mode is active when the interrupt is generated.

If an enabled interrupt request of sufficient priority is received by the interrupt controller, then the standard interrupt request is presented to the processor. At the same time, the processor will wake-up from Sleep or Idle and begin execution of the Interrupt Service Routine needed to process the interrupt request.

## 6.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "dsPIC30F Family Reference Manual" (DS70046). For more information on the device instruction set and programming, refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157).

The dsPIC30F family of devices contains internal program Flash memory for executing user code. There are two methods by which the user can program this memory:

- 1. In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) capabilities

- 2. Run-Time Self-Programming (RTSP)

# 6.1 In-Circuit Serial Programming (ICSP)

dsPIC30F devices can be serially programmed while in the end application circuit. This is simply done with two lines for Programming Clock and Programming Data (which are named PGC and PGD, respectively), and three other lines for Power (VDD), Ground (Vss) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

# 6.2 Run-Time Self-Programming (RTSP)

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions.

With RTSP, the user may erase program memory, 32 instructions (96 bytes) at a time and can write program memory data, 32 instructions (96 bytes) at a time.

## 6.3 Table Instruction Operation Summary

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in Word or Byte mode.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can access program memory in Word or Byte mode.

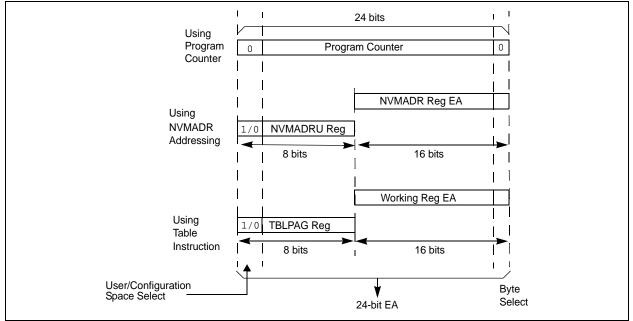

A 24-bit program memory address is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 6-1.

#### FIGURE 6-1: ADDRESSING FOR TABLE AND NVM REGISTERS

# TABLE 8-1: dsPIC30F3011 PORT REGISTER MAP<sup>(1)</sup>

| SFR<br>Name | Addr. | Bit 15  | Bit 14  | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset State         |

|-------------|-------|---------|---------|---------|--------|--------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| TRISB       | 02C6  | _       | _       | _       | -      | —      | _      | _     | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 0000 0001 1111 1111 |

| PORTB       | 02C8  | —       | —       | —       | —      | —      | —      | —     | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | 0000 0000 0000 0000 |

| LATB        | 02CA  | —       | —       | —       | —      | —      | —      | —     | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | 0000 0000 0000 0000 |

| TRISC       | 02CC  | TRISC15 | TRISC14 | TRISC13 | —      | —      | —      | —     | —      | —      | _      | —      | —      | —      | —      | —      | —      | 1110 0000 0000 0000 |

| PORTC       | 02CE  | RC15    | RC14    | RC13    | —      | —      | —      | _     | —      | —      | _      | —      | —      | —      | _      | _      | —      | 0000 0000 0000 0000 |

| LATC        | 02D0  | LATC15  | LATC14  | LATC13  | —      | —      | —      | —     | —      | —      | _      | —      | —      | —      | -      | -      | —      | 0000 0000 0000 0000 |

| TRISD       | 02D2  | —       | —       | —       | —      | —      | —      | —     | —      | —      | _      | —      | —      | TRISD3 | TRISD2 | TRISD1 | TRISD0 | 0000 0000 0000 1111 |

| PORTD       | 02D4  | -       | -       | -       | —      | —      | —      | _     | —      | —      | _      | —      | —      | RD3    | RD2    | RD1    | RD0    | 0000 0000 0000 0000 |

| LATD        | 02D6  | _       | _       | _       | _      | —      | —      | —     | _      | _      | _      | —      | _      | LATD3  | LATD2  | LATD1  | LATD0  | 0000 0000 0000 0000 |

| TRISE       | 02D8  |         |         |         | -      | —      | -      | _     | TRISE8 | _      | _      | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 0000 0001 0011 1111 |

| PORTE       | 02DA  | _       | _       | _       | _      | —      | _      | _     | RE8    | _      | -      | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | 0000 0000 0000 0000 |

| LATE        | 02DC  | _       | _       | _       | _      | —      | —      | —     | LATE8  | _      | _      | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | 0000 0000 0000 0000 |

| TRISF       | 02DE  | _       | _       | _       | _      | —      | -      | _     | _      | _      | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 0000 0000 0111 1111 |

| PORTF       | 02E0  | —       | —       | —       | —      | —      | _      | —     | _      | _      | RF6    | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | 0000 0000 0000 0000 |

| LATF        | 02E2  | —       | -       | -       |        | —      | _      | _     | _      |        | LATF6  | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | 0000 0000 0000 0000 |

**Legend:** — = unimplemented bit, read as '0'

Note 1: Refer to the "dsPIC30F Family Reference Manual" (DS70046) for descriptions of register bit fields. Not all peripherals, and therefore their bit positions, are available on this device.

# dsPIC30F3010/3011

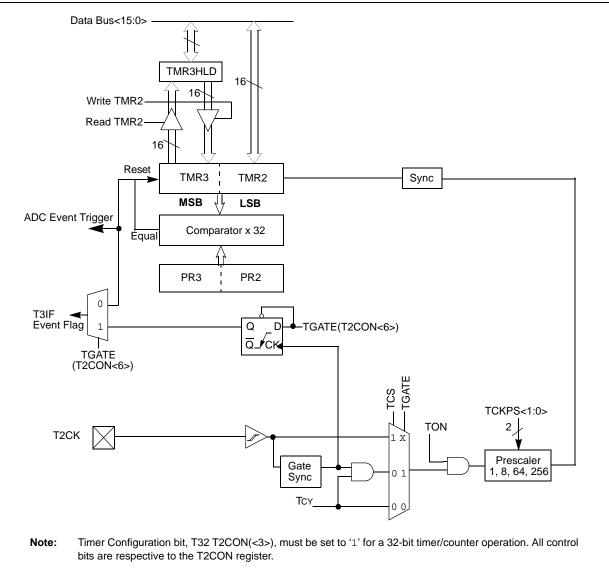

#### FIGURE 10-1: 32-BIT TIMER2/3 BLOCK DIAGRAM

When the PWM time base is in the Continuous Up/ Down Count mode with double updates, new duty cycle values are updated when the value of the PTMR register is zero, and when the value of the PTMR register matches the value in the PTPER register. The contents of the duty cycle buffers are automatically loaded into the Duty Cycle registers when the PWM time base is disabled (PTEN = 0).

# 15.6 Complementary PWM Operation

In the Complementary mode of operation, each pair of PWM outputs is obtained by a complementary PWM signal. A dead time may be optionally inserted during device switching, when both outputs are inactive for a short period (Refer to **Section 15.7 "Dead-Time Generators"**).

In Complementary mode, the duty cycle comparison units are assigned to the PWM outputs as follows:

- PDC1 register controls PWM1H/PWM1L outputs

- PDC2 register controls PWM2H/PWM2L outputs

- PDC3 register controls PWM3H/PWM3L outputs

The Complementary mode is selected for each PWM I/O pin pair by clearing the appropriate PMODx bit in the PWMCON1 SFR. The PWM I/O pins are set to Complementary mode by default upon a device Reset.

## 15.7 Dead-Time Generators

Dead-time generation may be provided when any of the PWM I/O pin pairs are operating in the Complementary Output mode. The PWM outputs use push-pull drive circuits. Due to the inability of the power output devices to switch instantaneously, some amount of time must be provided between the turn-off event of one PWM output in a complementary pair and the turn-on event of the other transistor.

The PWM module allows two different dead times to be programmed. These two dead times may be used in one of two methods described below to increase user flexibility:

- The PWM output signals can be optimized for different turn-off times in the high side and low side transistors in a complementary pair of transistors. The first dead time is inserted between the turn-off event of the lower transistor of the complementary pair and the turn-on event of the upper transistor. The second dead time is inserted between the turn-off event of the upper transistor and the turn-on event of the lower transistor.

- The two dead times can be assigned to individual PWM I/O pin pairs. This operating mode allows the PWM module to drive different transistor/load combinations with each complementary PWM I/O pin pair.

#### 15.7.1 DEAD-TIME GENERATORS

Each complementary output pair for the PWM module has a 6-bit down counter that is used to produce the dead-time insertion. As shown in Figure 15-4, each dead-time unit has a rising and falling edge detector connected to the duty cycle comparison output.

#### 15.7.2 DEAD-TIME RANGES

The amount of dead time provided by the dead-time unit is selected by specifying the input clock prescaler value and a 6-bit unsigned value.

Four input clock prescaler selections have been provided to allow a suitable range of dead time, based on the device operating frequency. The dead-time clock prescaler values are selected using the DTAPS<1:0> control bits in the DTCON1 SFR. One of four clock prescaler options (TCY, 2 TCY, 4 TCY or 8 TCY) may be selected.

After the prescaler value is selected, the dead time is adjusted by loading 6-bit unsigned values into the DTCON1 SFR.

The dead-time unit prescaler is cleared on the following events:

- On a load of the down timer due to a duty cycle comparison edge event.

- On a write to the DTCON1 register.

- On any device Reset.

- Note: The user should not modify the DTCON1 value while the PWM module is operating (PTEN = 1). Unexpected results may occur.

## 15.13 PWM Update Lockout

For a complex PWM application, the user may need to write up to three Duty Cycle registers and the Time Base Period register, PTPER, at a given time. In some applications, it is important that all buffer registers be written before the new duty cycle and period values are loaded for use by the module.

The PWM update lockout feature is enabled by setting the UDIS control bit in the PWMCON2 SFR. The UDIS bit affects all Duty Cycle Buffer registers and the PWM Time Base Period buffer, PTPER. No duty cycle changes or period value changes will have effect while UDIS = 1.

## 15.14 PWM Special Event Trigger

The PWM module has a Special Event Trigger that allows A/D conversions to be synchronized to the PWM time base. The A/D sampling and conversion time may be programmed to occur at any point within the PWM period. The Special Event Trigger allows the user to minimize the delay between the time when A/D conversion results are acquired and the time when the duty cycle value is updated.

The PWM Special Event Trigger has an SFR named SEVTCMP, and five control bits to control its operation. The PTMR value for which a Special Event Trigger should occur is loaded into the SEVTCMP register. When the PWM time base is in a Continuous Up/Down Count mode, an additional control bit is required to specify the counting phase for the Special Event Trigger. The count phase is selected using the SEVTDIR control bit in the SEVTCMP SFR. If the SEVTDIR bit is cleared, the Special Event Trigger will occur on the upward counting cycle of the PWM time base. If the SEVTDIR bit is set, the Special Event Trigger will occur on the downward count cycle of the PWM time base. The SEVTDIR control bit has no effect unless the PWM time base is configured for a Continuous Up/Down Count mode.

#### 15.14.1 SPECIAL EVENT TRIGGER POSTSCALER

The PWM Special Event Trigger has a postscaler that allows a 1:1 to 1:16 postscale ratio. The postscaler is configured by writing the SEVOPS<3:0> control bits in the PWMCON2 SFR.

The special event output postscaler is cleared on the following events:

- Any write to the SEVTCMP register

- Any device Reset

#### 15.15 PWM Operation During CPU Sleep Mode

The Fault A input pin has the ability to wake the CPU from Sleep mode. The PWM module generates an interrupt if the Fault pin is driven low while in Sleep.

#### 15.16 PWM Operation During CPU Idle Mode

The PTCON SFR contains a PTSIDL control bit. This bit determines if the PWM module will continue to operate or stop when the device enters Idle mode. If PTSIDL = 0, the module will continue to operate. If PTSIDL = 1, the module will stop operation as long as the CPU remains in Idle mode.

#### 16.3 Slave Select Synchronization

The SS1 pin allows a Synchronous Slave mode. The SPI must be configured in SPI Slave mode with SS1 pin control enabled (SSEN = 1). When the SS1 pin is low, transmission and reception are enabled and the SD01 pin is driven. When the SS1 pin goes high, the SD01 pin is no longer driven. Also, the SPI module is resynchronized and all counters/control circuitry are reset. Therefore, when the SS1 pin is asserted low again, transmission/reception will begin at the MSb, even if SS1 has been deasserted in the middle of a transmit/receive.

#### 16.4 SPI Operation During CPU Sleep Mode

During Sleep mode, the SPI module is shut down. If the CPU enters Sleep mode while an SPI transaction is in progress, then the transmission and reception is aborted.

The transmitter and receiver will stop in Sleep mode. However, register contents are not affected by entering or exiting Sleep mode.

#### 16.5 SPI Operation During CPU Idle Mode

When the device enters Idle mode, all clock sources remain functional. The SPISIDL bit (SPI1STAT<13>) selects if the SPI module will stop or continue on Idle. If SPISIDL = 0, the module will continue to operate when the CPU enters Idle mode. If SPISIDL = 1, the module will stop when the CPU enters Idle mode.

# dsPIC30F3010/3011

# 19.0 10-BIT HIGH-SPEED ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

**Note:** This data sheet summarizes features of this group of dsPIC30F devices and is not intended to be a complete reference source. For more information on the CPU, peripherals, register descriptions and general device functionality, refer to the "*dsPIC30F Family Reference Manual*" (DS70046).

The 10-bit high-speed Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit digital number. This module is based on a Successive Approximation Register (SAR) architecture, and provides a maximum sampling rate of 1 Msps. The ADC module has 16 analog inputs which are multiplexed into four sample and hold amplifiers. The output of the sample and hold is the input into the converter, which generates the result. The analog reference voltages are software selectable to either the device supply voltage (AVDD/AVSS) or the voltage level on the (VREF+/VREF-) pin. The ADC has a unique feature of being able to operate while the device is in Sleep mode.

The ADC module has six 16-bit registers:

- A/D Control Register 1 (ADCON1)

- A/D Control Register 2 (ADCON2)

- A/D Control Register 3 (ADCON3)

- A/D Input Select register (ADCHS)

- A/D Port Configuration register (ADPCFG)

- A/D Input Scan Selection register (ADCSSL)

The ADCON1, ADCON2 and ADCON3 registers control the operation of the ADC module. The ADCHS register selects the input channels to be converted. The ADPCFG register configures the port pins as analog inputs or as digital I/O. The ADCSSL register selects inputs for scanning.

Note: The SSRC<2:0>, ASAM, SIMSAM, SMPI<3:0>, BUFM and ALTS bits, as well as the ADCON3 and ADCSSL registers, must not be written to while ADON = 1. This would lead to indeterminate results.

The block diagram of the ADC module is shown in Figure 19-1.

#### 19.4 Programming the Start of Conversion Trigger

The conversion trigger will terminate acquisition and start the requested conversions.

The SSRC<2:0> bits select the source of the conversion trigger.

The SSRC bits provide for up to five alternate sources of conversion trigger.

When SSRC<2:0> = 000, the conversion trigger is under software control. Clearing the SAMP bit will cause the conversion trigger.

When SSRC<2:0> = 111 (Auto-Start mode), the conversion trigger is under A/D clock control. The SAMC bits select the number of A/D clocks between the start of acquisition and the start of conversion. This provides the fastest conversion rates on multiple channels. The SAMC bits must always be at least one clock cycle.

Other trigger sources can come from timer modules, motor control PWM module or external interrupts.

Note: To operate the A/D at the maximum specified conversion speed, the autoconvert trigger option should be selected (SSRC = 111) and the auto-sample time bits should be set to 1 TAD (SAMC = 00001). This configuration will give a total conversion period (sample + convert) of 13 TAD.

The use of any other conversion trigger will result in additional TAD cycles to synchronize the external event to the A/D.

## 19.5 Aborting a Conversion

Clearing the ADON bit during a conversion will abort the current conversion and stop the sampling sequencing. The ADCBUF will not be updated with the partially completed A/D conversion sample. That is, the ADCBUF will continue to contain the value of the last completed conversion (or the last value written to the ADCBUF register).

If the clearing of the ADON bit coincides with an auto-start, the clearing has a higher priority.

After the A/D conversion is aborted, a 2 TAD wait is required before the next sampling may be started by setting the SAMP bit.

If sequential sampling is specified, the A/D will continue at the next sample pulse which corresponds with the next channel converted. If simultaneous sampling is specified, the A/D will continue with the next multi-channel group conversion sequence.

#### 19.6 Selecting the A/D Conversion Clock

The A/D conversion requires 12 TAD. The source of the A/D conversion clock is software selected using a 6-bit counter. There are 64 possible options for TAD.

#### EQUATION 19-1: A/D CONVERSION CLOCK

$$TAD = TCY \bullet (0.5 \bullet (ADCS < 5:0 > + 1))$$

$$ADCS < 5:0 > = 2 \quad \frac{TAD}{TCY} - 1$$

The internal RC oscillator is selected by setting the ADRC bit.

For correct A/D conversions, the A/D conversion clock (TAD) must be selected to ensure a minimum TAD time of 83.33 nsec (for VDD = 5V). Refer to **Section 23.0 "Electrical Characteristics"** for minimum TAD under other operating conditions.

Example 19-1 shows a sample calculation for the ADCS<5:0> bits, assuming a device operating speed of 30 MIPS.

#### EXAMPLE 19-1: A/D CONVERSION CLOCK CALCULATION

TAD = 154 nsec

TCY = 33 nsec (30 MIPS)

ADCS<5:0> = 2

$$\frac{TAD}{TCY} - 1$$

= 2  $\cdot \frac{154 \text{ nsec}}{33 \text{ nsec}} - 1$

= 8.33

Therefore,

Set ADCS<5:0> = 9

Actual TAD =  $\frac{TCY}{2}$  (ADCS<5:0> + 1)

=  $\frac{33 \text{ nsec}}{2}$  (9 + 1)

= 165 nsec

## **19.8** A/D Acquisition Requirements

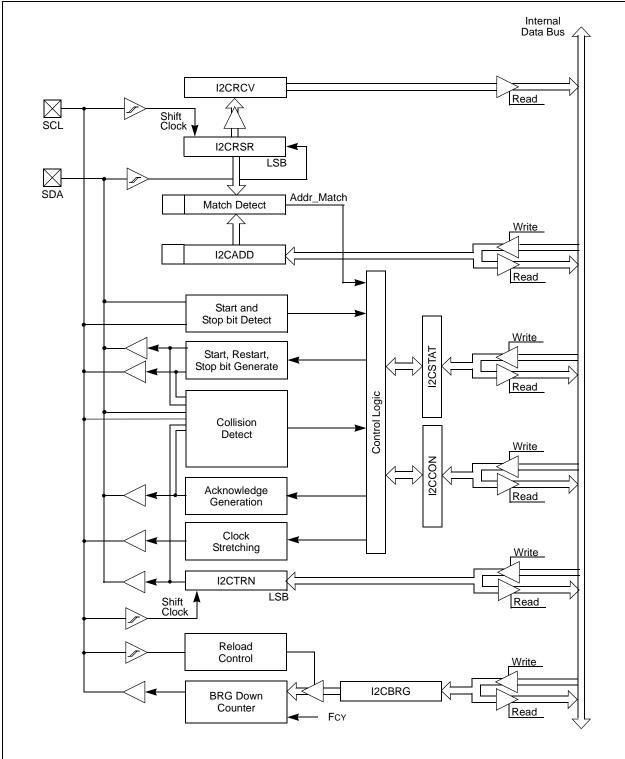

The analog input model of the 10-bit ADC is shown in Figure 19-3. The total sampling time for the ADC is a function of the internal amplifier settling time, device VDD and the holding capacitor charge time.

For the ADC to meet its specified accuracy, the Charge Holding Capacitor (CHOLD) must be allowed to fully charge to the voltage level on the analog input pin. The Source Impedance (Rs), the Interconnect Impedance (RIC) and the Internal Sampling Switch (RSS) Impedance combine to directly affect the time required to charge the capacitor, CHOLD. The combined impedance of the analog sources must therefore be small enough to fully charge the holding capacitor within the chosen sample time. To minimize the effects of pin leakage currents on the accuracy of the A/D converter, the maximum recommended source impedance, Rs, is 5 k $\Omega$ . After the analog input channel is selected (changed), this sampling function must be completed prior to starting the conversion. The internal holding capacitor will be in a discharged state prior to each sample operation.

The user must allow at least 1 TAD period of sampling time, TSAMP, between conversions to allow each sample to be acquired. This sample time may be controlled manually in software by setting/clearing the SAMP bit, or it may be automatically controlled by the ADC. In an automatic configuration, the user must allow enough time between conversion triggers so that the minimum sample time can be satisfied. Refer to the **Section 23.0 "Electrical Characteristics"** for TAD and sample time requirements.

#### FIGURE 19-3: ADC ANALOG INPUT MODEL

#### TABLE 20-1: OSCILLATOR OPERATING MODES

| Oscillator Mode | Description                                                                        |

|-----------------|------------------------------------------------------------------------------------|

| XTL             | 200 kHz-4 MHz crystal on OSC1:OSC2.                                                |

| хт              | 4 MHz-10 MHz crystal on OSC1:OSC2.                                                 |

| XT w/PLL 4x     | 4 MHz-10 MHz crystal on OSC1:OSC2, 4x PLL enabled.                                 |

| XT w/PLL 8x     | 4 MHz-10 MHz crystal on OSC1:OSC2, 8x PLL enabled.                                 |

| XT w/PLL 16x    | 4 MHz-10 MHz crystal on OSC1:OSC2, 16x PLL enabled <sup>(1)</sup> .                |

| LP              | 32 kHz crystal on SOSCO:SOSCI <sup>(2)</sup> .                                     |

| HS              | 10 MHz-25 MHz crystal.                                                             |

| HS/2 w/PLL 4x   | 10 MHz-25 MHz crystal, divide by 2, 4x PLL enabled.                                |

| HS/2 w/PLL 8x   | 10 MHz-25MHz crystal, divide by 2, 8x PLL enabled.                                 |

| HS/2 w/PLL 16x  | 10 MHz-25MHz crystal, divide by 2, 16x PLL enabled <sup>(1)</sup> .                |

| HS/3 w/PLL 4x   | 10 MHz-25 MHz crystal, divide by 3, 4x PLL enabled.                                |

| HS/3 w/PLL 8x   | 10 MHz-25MHz crystal, divide by 3, 8x PLL enabled.                                 |

| HS/3 w/PLL 16x  | 10 MHz-25MHz crystal, divide by 3, 16x PLL enabled <sup>(1)</sup> .                |

| EC              | External clock input (0-40 MHz).                                                   |

| ECIO            | External clock input (0-40 MHz), OSC2 pin is I/O.                                  |

| EC w/PLL 4x     | External clock input (4-10 MHz), OSC2 pin is I/O, 4x PLL enabled <sup>(1)</sup> .  |

| EC w/PLL 8x     | External clock input (4-10 MHz), OSC2 pin is I/O, 8x PLL enabled <sup>(1)</sup> .  |

| EC w/PLL 16x    | External clock input (4-10 MHz), OSC2 pin is I/O, 16x PLL enabled <sup>(1)</sup> . |

| ERC             | External RC oscillator, OSC2 pin is Fosc/4 output <sup>(3)</sup> .                 |

| ERCIO           | External RC oscillator, OSC2 pin is I/O <sup>(3)</sup> .                           |

| FRC             | 8 MHz internal RC oscillator.                                                      |

| FRC w/PLL 4x    | 7.37 MHz Internal RC oscillator, 4x PLL enabled.                                   |

| FRC w/PLL 8x    | 7.37 MHz Internal RC oscillator, 8x PLL enabled.                                   |

| FRC w/PLL 16x   | 7.37 MHz Internal RC oscillator, 16x PLL enabled.                                  |

| LPRC            | 512 kHz internal RC oscillator.                                                    |

**Note 1:** dsPIC30F maximum operating frequency of 120 MHz must be met.

2: LP oscillator can be conveniently shared as system clock, as well as real-time clock for Timer1.

3: Requires external R and C. Frequency operation up to 4 MHz.

If one of the above conditions is not true, the LPRC will shut-off after the PWRT expires.

- Note 1: OSC2 pin function is determined by the Primary Oscillator mode selection (FPR<3:0>).

- OSC1 pin cannot be used as an I/O pin, even if the secondary oscillator or an internal clock source is selected at all times.

## 20.2.7 FAIL-SAFE CLOCK MONITOR

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by appropriately programming the FCKSM Configuration bits (Clock Switch and Monitor Selection bits) in the FOSC Configuration register. If the FSCM function is enabled, the LPRC internal oscillator will run at all times (except during Sleep mode) and will not be subject to control by the SWDTEN bit.

In the event of an oscillator failure, the FSCM will generate a clock failure trap event and will switch the system clock over to the FRC oscillator. The user will then have the option to either attempt to restart the oscillator or execute a controlled shut down. The user may decide to treat the trap as a warm Reset by simply loading the Reset address into the oscillator fail trap vector. In this event, the CF (Clock Fail) status bit (OSCCON<3>) is also set whenever a clock failure is recognized.

In the event of a clock failure, the WDT is unaffected and continues to run on the LPRC clock.

If the oscillator has a very slow start-up time coming out of POR, BOR or Sleep, it is possible that the PWRT timer will expire before the oscillator has started. In such cases, the FSCM will be activated and the FSCM will initiate a clock failure trap, and the COSC<1:0> bits are loaded with FRC oscillator selection. This will effectively shut-off the original oscillator that was trying to start.

The user may detect this situation and restart the oscillator in the clock fail trap ISR.

Upon a clock failure detection, the FSCM module will initiate a clock switch to the FRC oscillator as follows:

- 1. The COSC bits (OSCCON<13:12>) are loaded with the FRC Oscillator selection value.

- 2. CF bit is set (OSCCON<3>).

- 3. OSWEN control bit (OSCCON<0>) is cleared.

For the purpose of clock switching, the clock sources are sectioned into four groups:

- Primary

- · Secondary

- Internal FRC

- Internal LPRC

The user can switch between these functional groups, but cannot switch between options within a group. If the primary group is selected, then the choice within the group is always determined by the FPR<3:0> Configuration bits. The OSCCON register holds the control and status bits related to clock switching.

- COSC<1:0>: Read-only status bits always reflect the current oscillator group in effect.

- NOSC<1:0>: Control bits which are written to indicate the new oscillator group of choice.

- On POR and BOR, COSC<1:0> and NOSC<1:0> are both loaded with the Configuration bit values, FOS<1:0>.

- LOCK: The LOCK status bit indicates a PLL lock.

- CF: Read-only status bit indicating if a clock fail detect has occurred.

- OSWEN: Control bit changes from a '0' to a '1' when a clock transition sequence is initiated. Clearing the OSWEN control bit will abort a clock transition in progress (used for hang-up situations).

If Configuration bits, FCKSM<1:0> = lx, then the clock switching and Fail-Safe Clock Monitor functions are disabled. This is the default Configuration bit setting.

If clock switching is disabled, then the FOS<1:0> and FPR<3:0> bits directly control the oscillator selection and the COSC<1:0> bits do not control the clock selection. However, these bits will reflect the clock source selection.

**Note:** The application should not attempt to switch to a clock of frequency lower than 100 kHz when the Fail-Safe Clock Monitor is enabled. If such clock switching is performed, the device may generate an oscillator fail trap and switch to the fast RC oscillator.

| DC CHA       | RACTERI    | STICS                                                            | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                    |     |       |                                  |  |  |

|--------------|------------|------------------------------------------------------------------|-------------------------------------------------------|--------------------|-----|-------|----------------------------------|--|--|

| Param<br>No. | Symbol     | Characteristic                                                   | Min                                                   | Typ <sup>(1)</sup> | Max | Units | Conditions                       |  |  |

| Operatir     | ng Voltage | (2)                                                              |                                                       |                    |     |       |                                  |  |  |

| DC10         | Vdd        | Supply Voltage                                                   | 2.5                                                   | _                  | 5.5 | V     | Industrial temperature           |  |  |

| DC11         | Vdd        | Supply Voltage                                                   | 3.0                                                   |                    | 5.5 | V     | Extended temperature             |  |  |

| DC12         | Vdr        | RAM Data Retention Voltage <sup>(3)</sup>                        | 1.75                                                  | —                  | _   | V     |                                  |  |  |

| DC16         | VPOR       | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal | —                                                     | _                  | Vss | V     |                                  |  |  |

| DC17         | SVDD       | VDD Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal     | 0.05                                                  | —                  |     | V/ms  | 0-5V in 0.1 sec<br>0-3V in 60 ms |  |  |

#### TABLE 23-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

**Note 1:** Data in "Typ" column is at 5V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized but not tested in manufacturing.

**3:** This is the limit to which VDD can be lowered without losing RAM data.

# **Revision F (November 2010)**

This revision includes minor typographical and formatting changes throughout the data sheet text.

The major changes are referenced by their respective section in Table A-1.

#### TABLE A-1: MAJOR SECTION UPDATES

| Section Name                                             | Update Description                                                                                                                                                        |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High Performance, 16-Bit<br>Digital Signal Controllers" | Added Note 1 to all QFN pin diagrams (see "Pin Diagrams").                                                                                                                |

| Section 1.0 "Device Overview"                            | Updated the Pinout I/O Descriptions for AVDD and AVSS (see Table 1-1 and Table 1-2).                                                                                      |

| Section 15.0 "Motor Control<br>PWM Module"               | Added the IUE bit (PWMCON2<2>) to the PWM Register Map (see Table 15-1).<br>Updated the PWM Period equations (see Equation 15-1 and Equation 15-2).                       |

| Section 20.0 "System<br>Integration"                     | Added a shaded note on OSCTUN functionality in Section 20.2.5 "Fast RC Oscillator (FRC)".                                                                                 |

|                                                          | Updated Notes 1 and 2 in the Configuration Bit Values for Clock Selection (see Table 20-2).                                                                               |

| Section 24.0 "Packaging<br>Information"                  | Removed the 44-Lead QFN package definitions.                                                                                                                              |

| Section 23.0 "Electrical<br>Characteristics"             | Updated the typical and maximum values for parameter DC16 in the DC Temperature and Voltage Specifications (see Table 23-4).                                              |

|                                                          | Updated the maximum value for parameter DI19 and the minimum value for parameter DI29 in the I/O Pin Input Specifications (see Table 23-8).                               |

|                                                          | Removed parameter D136 and updated the minimum, typical, maximum, and conditions for parameters D122 and D134 in the Program and EEPROM specifications (see Table 23-11). |

|                                                          | Updated Note 1 in the Internal FRC Accuracy specifications (see Table 23-17).                                                                                             |

| "Product Identification System"                          | Updated the "ML" package definition.                                                                                                                                      |