Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, SPI, UART/USART                                                 |

| Peripherals                | PWM, WDT                                                                         |

| Number of I/O              | 47                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 8K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.35V ~ 2.7V                                                                     |

| Data Converters            | A/D 14x8/10b                                                                     |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP                                                                          |

| Supplier Device Package    | PG-LQFP-64-4                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/saf-xc164gm-16f40f-ba |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| XC164G<br>Revisior                 | M<br>n History: V1.2, 2007-03                          |

|------------------------------------|--------------------------------------------------------|

| Previous<br>V1.1, 200<br>V1.0, 200 |                                                        |

| Page                               | Subjects (major changes since last revision)           |

| 6                                  | Design steps of the derivatives differentiated.        |

| <b>52</b>                          | Power consumption of the derivatives differentiated.   |

| <b>53</b>                          | Figure 10 adapted.                                     |

| 54                                 | Figure 12 adapted.                                     |

| 64                                 | Packages of the derivatives differentiated.            |

| 65                                 | Thermal resistances of the derivatives differentiated. |

| all                                | "Preliminary" removed                                  |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

# 16-Bit Single-Chip Microcontroller with C166SV2 Core XC166 Family

## XC164GM

# **1** Summary of Features

For a quick overview or reference, the XC164GM's properties are listed here in a condensed way.

- High Performance 16-bit CPU with 5-Stage Pipeline

- 25 ns Instruction Cycle Time at 40 MHz CPU Clock (Single-Cycle Execution)

- 1-Cycle Multiplication (16 × 16 bit), Background Division (32 / 16 bit) in 21 Cycles

- 1-Cycle Multiply-and-Accumulate (MAC) Instructions

- Enhanced Boolean Bit Manipulation Facilities

- Zero-Cycle Jump Execution

- Additional Instructions to Support HLL and Operating Systems

- Register-Based Design with Multiple Variable Register Banks

- Fast Context Switching Support with Two Additional Local Register Banks

- 16 Mbytes Total Linear Address Space for Code and Data

- 1024 Bytes On-Chip Special Function Register Area (C166 Family Compatible)

- 16-Priority-Level Interrupt System with up to 63 Sources, Sample-Rate down to 50 ns

- 8-Channel Interrupt-Driven Single-Cycle Data Transfer Facilities via Peripheral Event Controller (PEC), 24-Bit Pointers Cover Total Address Space

- Clock Generation via on-chip PLL (factors 1:0.15 ... 1:10), or

- via Prescaler (factors 1:1 ... 60:1)

- On-Chip Memory Modules

- 2 Kbytes On-Chip Dual-Port RAM (DPRAM)

- 0/2/4 Kbytes<sup>1)</sup> On-Chip Data SRAM (DSRAM)

- 2 Kbytes On-Chip Program/Data SRAM (PSRAM)

- 32/64/128<sup>1)</sup> Kbytes On-Chip Program Memory (Flash Memory)

- On-Chip Peripheral Modules

- 14-Channel A/D Converter with Programmable Resolution (10-bit or 8-bit) and Conversion Time (down to 2.55 μs or 2.15 μs)

- 16-Channel General Purpose Capture/Compare Unit (CAPCOM2)

- Multi-Functional General Purpose Timer Unit with 5 Timers

- Two Synchronous/Asynchronous Serial Channels (USARTs)

- Two High-Speed-Synchronous Serial Channels

- On-Chip TwinCAN Interface (Rev. 2.0B active) with 32 Message Objects (Full CAN/Basic CAN) on Two CAN Nodes, and Gateway Functionality

- On-Chip Real Time Clock, Driven by the Main Oscillator

- Idle, Sleep, and Power Down Modes with Flexible Power Management

<sup>1)</sup> Depends on the respective derivative. See Table 1 "XC164GM Derivative Synopsis" on Page 6.

#### Summary of Features

- Programmable Watchdog Timer and Oscillator Watchdog

- Up to 47 General Purpose I/O Lines, partly with Selectable Input Thresholds and Hysteresis

- On-Chip Bootstrap Loader

- On-Chip Debug Support via JTAG Interface

- 64-Pin Green LQFP Package for the -16F derivatives, 0.5 mm (19.7 mil) pitch (RoHS compliant)

- 64-Pin TQFP Package for the -4F/8F derivatives, 0.5 mm (19.7 mil) pitch (RoHS compliant)

#### **Ordering Information**

The ordering code for Infineon microcontrollers provides an exact reference to the required product. This ordering code identifies:

- the derivative itself, i.e. its function set, the temperature range, and the supply voltage

- the package and the type of delivery.

For the available ordering codes for the XC164GM please refer to your responsible sales representative or your local distributor.

This document describes several derivatives of the XC164GM group. **Table 1** enumerates these derivatives and summarizes the differences. As this document refers to all of these derivatives, some descriptions may not apply to a specific product.

For simplicity all versions are referred to by the term **XC164GM** throughout this document.

#### **General Device Information**

| Table 2     | Pi          | Pin Definitions and Functions (cont'd) |                                                                 |  |  |  |  |

|-------------|-------------|----------------------------------------|-----------------------------------------------------------------|--|--|--|--|

| Sym-<br>bol | Pin<br>Num. | Input<br>Outp.                         | Function                                                        |  |  |  |  |

|             | -           | -                                      |                                                                 |  |  |  |  |

| Port 5      | 9-18,       | I                                      | Port 5 is a 14-bit input-only port.                             |  |  |  |  |

|             | 21-24       |                                        | The pins of Port 5 also serve as analog input channels for the  |  |  |  |  |

|             |             |                                        | A/D converter, or they serve as timer inputs:                   |  |  |  |  |

| P5.0        | 9           | I                                      | ANO                                                             |  |  |  |  |

| P5.1        | 10          | I                                      | AN1                                                             |  |  |  |  |

| P5.2        | 11          | I                                      | AN2                                                             |  |  |  |  |

| P5.3        | 12          | 1                                      | AN3                                                             |  |  |  |  |

| P5.4        | 13          | 1                                      | AN4                                                             |  |  |  |  |

| P5.5        | 14          | 1                                      | AN5                                                             |  |  |  |  |

| P5.10       | 15          | 1                                      | AN10 (T6EUD): GPT2 Timer T6 Ext. Up/Down Ctrl. Inp.             |  |  |  |  |

| P5.11       | 16          | 1                                      | AN11 (T5EUD): GPT2 Timer T5 Ext. Up/Down Ctrl. Inp.             |  |  |  |  |

| P5.6        | 17          | I                                      | AN6                                                             |  |  |  |  |

| P5.7        | 18          | I                                      | AN7                                                             |  |  |  |  |

| P5.12       | 21          | 1                                      | AN12 (T6IN): GPT2 Timer T6 Count/Gate Input                     |  |  |  |  |

| P5.13       | 22          | 1                                      | AN13 (T5IN): GPT2 Timer T5 Count/Gate Input                     |  |  |  |  |

| P5.14       | 23          | 1                                      | AN14 (T4EUD): GPT1 Timer T4 Ext. Up/Down Ctrl. Inp.             |  |  |  |  |

| P5.15       | 24          | 1                                      | AN15 (T2EUD): GPT1 Timer T2 Ext. Up/Down Ctrl. Inp.             |  |  |  |  |

| TRST        | 62          | I                                      | Test-System Reset Input. For normal system operation, pin       |  |  |  |  |

|             |             |                                        | TRST should be held low. A high level at this pin at the rising |  |  |  |  |

|             |             |                                        | edge of RSTIN enables the hardware configuration and            |  |  |  |  |

|             |             |                                        | activates the XC164GM's debug system. In this case, pin         |  |  |  |  |

|             |             |                                        | TRST must be driven low once to reset the debug system.         |  |  |  |  |

## **General Device Information**

| Table 2          | Piı           | n Defini        | tions and Functions (cont'd)                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------|---------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sym-<br>bol      | Pin<br>Num.   | Input<br>Outp.  | Function                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PORT1            | 1-6,<br>49-56 | IO              | PORT1 consists of one 8-bit and one 6-bit bidirectional I/O<br>port P1L and P1H. Each pin can be programmed for input<br>(output driver in high-impedance state) or output.<br>The following PORT1 pins also serve for alt. functions:                                                                                                                                                                                       |

| P1L.7<br>P1H.0   | 56<br>1       | I/O<br>I<br>I/O | CC22IO: [CAPCOM2] CC22 Capture Inp./Compare Outp.<br>EX0IN: [Fast External Interrupt 0] Input (default pin),<br>CC23IO: [CAPCOM2] CC23 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                            |

| P1H.1            | 2             | I<br>I/O        | EX1IN: [Fast External Interrupt 1] Input (default pin),<br>MRST1: [SSC1] Master-Receive/Slave-Transmit In/Out.                                                                                                                                                                                                                                                                                                               |

| P1H.2            | 3             | I<br>I/O        | EX2IN: [Fast External Interrupt 2] Input (default pin),<br>MTSR1: [SSC1] Master-Transmit/Slave-Receive Out/Inp.                                                                                                                                                                                                                                                                                                              |

| P1H.3            | 3             | <br> /O<br>     | T7IN: [CAPCOM2] Timer T7 Count Input,<br>SCLK1: [SSC1] Master Clock Output / Slave Clock Input,<br>EX3IN: [Fast External Interrupt 3] Input (default pin),                                                                                                                                                                                                                                                                   |

| P1H.4            | 5             | I/O<br>I        | CC24IO: [CAPCOM2] CC24 Capture Inp./Compare Outp.,<br>EX4IN: [Fast External Interrupt 4] Input (default pin)                                                                                                                                                                                                                                                                                                                 |

| P1H.5            | 6             | I/O<br>I        | CC25IO: [CAPCOM2] CC25 Capture Inp./Compare Outp.,<br>EX5IN: [Fast External Interrupt 5] Input (default pin)                                                                                                                                                                                                                                                                                                                 |

|                  |               |                 | Note: At the end of an external reset P1H.4 and P1H.5 also<br>may input startup configuration values                                                                                                                                                                                                                                                                                                                         |

| XTAL2<br>XTAL1   | 61<br>60      | O<br>I          | XTAL2: Output of the oscillator amplifier circuit<br>XTAL1: Input to the oscillator amplifier and input to the<br>internal clock generator<br>To clock the device from an external source, drive XTAL1,<br>while leaving XTAL2 unconnected. Minimum and maximum<br>high/low and rise/fall times specified in the AC Characteristics<br>must be observed.<br><i>Note: Input pin XTAL1 belongs to the core voltage domain.</i> |

|                  |               |                 | Therefore, input voltages must be within the range defined for $V_{\rm DDI}$ .                                                                                                                                                                                                                                                                                                                                               |

| $V_{AREF}$       | 19            | -               | Reference voltage for the A/D converter                                                                                                                                                                                                                                                                                                                                                                                      |

| $V_{AGND}$       | 20            | -               | Reference ground for the A/D converter                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>DDI</sub> | 26, 58        | _               | Digital Core Supply Voltage (On-Chip Modules):<br>+2.5 V during normal operation and idle mode.<br>Please refer to the <b>Operating Condition Parameters</b>                                                                                                                                                                                                                                                                 |

# 3 Functional Description

The architecture of the XC164GM combines advantages of RISC, CISC, and DSP processors with an advanced peripheral subsystem in a very well-balanced way. In addition, the on-chip memory blocks allow the design of compact systems-on-silicon with maximum performance (computing, control, communication).

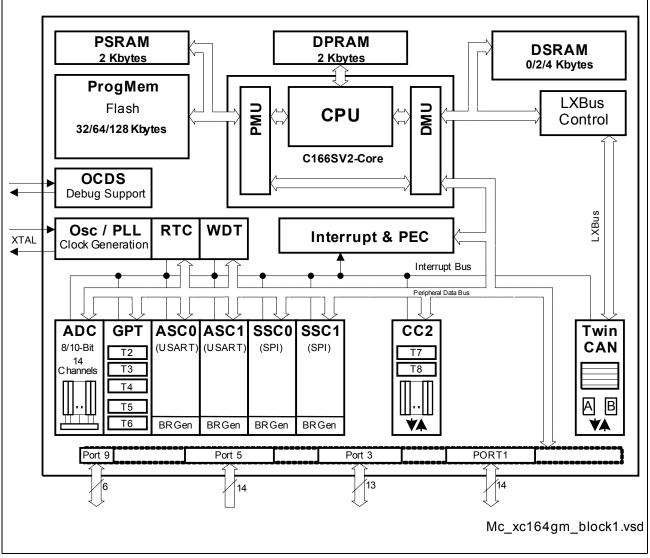

The on-chip memory blocks (program code-memory and SRAM, dual-port RAM, data SRAM) and the set of generic peripherals are connected to the CPU via separate buses. Another bus, the LXBus, connects additional on-chip resources (see **Figure 3**).

This bus structure enhances the overall system performance by enabling the concurrent operation of several subsystems of the XC164GM.

The following block diagram gives an overview of the different on-chip components and of the advanced, high bandwidth internal bus structure of the XC164GM.

Figure 3 Block Diagram

**2 Kbytes of on-chip Dual-Port RAM (DPRAM)** are provided as a storage for user defined variables, for the system stack, general purpose register banks. A register bank can consist of up to 16 word wide (R0 to R15) and/or byte wide (RL0, RH0, ..., RL7, RH7) so-called General Purpose Registers (GPRs).

The upper 256 bytes of the DPRAM are directly bit addressable. When used by a GPR, any location in the DPRAM is bit addressable.

**1024 bytes (2**  $\times$  **512 bytes)** of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are word wide registers which are used for controlling and monitoring functions of the different on-chip units. Unused SFR addresses are reserved for future members of the XC166 Family. Therefore, they should either not be accessed, or written with zeros, to ensure upward compatibility.

| Address Area          | Start Loc.           | End Loc.             | Area Size <sup>1)</sup> | Notes            |

|-----------------------|----------------------|----------------------|-------------------------|------------------|

| Flash register space  | FF'F000 <sub>H</sub> | FF'FFFF <sub>H</sub> | 4 Kbytes                | 2)               |

| Reserved (Acc. trap)  | F8'0000 <sub>H</sub> | FF'FFFF <sub>H</sub> | 508 Kbytes              | -                |

| Reserved for PSRAM    | E0'0800 <sub>H</sub> | F7'FFFF <sub>H</sub> | < 1.5 Mbytes            | Minus PSRAM      |

| Program SRAM          | E0'0000 <sub>H</sub> | E0'07FF <sub>H</sub> | 2 Kbytes                | -                |

| Reserved for pr. mem. | C2'0000 <sub>H</sub> | DF'FFFF <sub>H</sub> | < 2 Mbytes              | Minus Flash      |

| Program Flash         | C0'0000 <sub>H</sub> | C1'FFFF <sub>H</sub> | 128 Kbytes              | XC164GM-16F      |

|                       | C0'0000 <sub>H</sub> | C0'FFFF <sub>H</sub> | 64 Kbytes               | XC164GM-8F       |

|                       | C0'0000 <sub>H</sub> | C0'7FFF <sub>H</sub> | 32 Kbytes               | XC164GM-4F       |

| Reserved              | 20'0800 <sub>H</sub> | BF'FFFF <sub>H</sub> | < 10 Mbytes             | Minus TwinCAN    |

| TwinCAN registers     | 20'0000 <sub>H</sub> | 20'07FF <sub>H</sub> | 2 Kbytes                | Accessed via EBC |

| Reserved              | 01'0000 <sub>H</sub> | 1F'FFFF <sub>H</sub> | < 2 Mbytes              | Minus segment 0  |

| SFR area              | 00'FE00 <sub>H</sub> | 00'FFFF <sub>H</sub> | 0.5 Kbyte               | -                |

| Dual-Port RAM         | 00'F600 <sub>H</sub> | 00'FDFF <sub>H</sub> | 2 Kbytes                | -                |

| Reserved for DPRAM    | 00'F200 <sub>H</sub> | 00'F5FF <sub>H</sub> | 1 Kbyte                 | -                |

| ESFR area             | 00'F000 <sub>H</sub> | 00'F1FF <sub>H</sub> | 0.5 Kbyte               | -                |

| XSFR area             | 00'E000 <sub>H</sub> | 00'EFFF <sub>H</sub> | 4 Kbytes                | -                |

| Reserved              | 00'D000 <sub>H</sub> | 00'DFFF <sub>H</sub> | 6 Kbytes                | -                |

| Data SRAM             | 00'C000 <sub>H</sub> | 00'CFFF <sub>H</sub> | 4 Kbytes                | 3)               |

| Reserved for DSRAM    | 00'8000 <sub>H</sub> | 00'BFFF <sub>H</sub> | 16 Kbytes               | -                |

| Reserved              | 00'0000 <sub>H</sub> | 00'7FFF <sub>H</sub> | 32 Kbytes               | -                |

#### Table 3 XC164GM Memory Map

1) The areas marked with "<" are slightly smaller than indicated, see column "Notes".

- 2) Not defined register locations return a trap code ( $1E9B_H$ ).

- 3) Depends on the respective derivative. See Table 1 "XC164GM Derivative Synopsis" on Page 6.

#### Table 4XC164GM Interrupt Nodes (cont'd)

| Source of Interrupt or PEC<br>Service Request | Control<br>Register | Vector<br>Location <sup>1)</sup> | Trap<br>Number                    |  |

|-----------------------------------------------|---------------------|----------------------------------|-----------------------------------|--|

| Unassigned node                               | _                   | xx'0040 <sub>H</sub>             | 10 <sub>H</sub> / 16 <sub>D</sub> |  |

| Unassigned node                               | _                   | xx'0044 <sub>H</sub>             | 11 <sub>H</sub> / 17 <sub>D</sub> |  |

| Unassigned node                               | _                   | xx'0048 <sub>H</sub>             | 12 <sub>H</sub> / 18 <sub>D</sub> |  |

| Unassigned node                               | -                   | xx'004C <sub>H</sub>             | 13 <sub>H</sub> / 19 <sub>D</sub> |  |

| Unassigned node                               | -                   | xx'0050 <sub>H</sub>             | 14 <sub>H</sub> / 20 <sub>D</sub> |  |

| Unassigned node                               | -                   | xx'0054 <sub>H</sub>             | 15 <sub>H</sub> / 21 <sub>D</sub> |  |

| Unassigned node                               | _                   | xx'0058 <sub>H</sub>             | 16 <sub>H</sub> / 22 <sub>D</sub> |  |

| Unassigned node                               | -                   | xx'005C <sub>H</sub>             | 17 <sub>H</sub> / 23 <sub>D</sub> |  |

| Unassigned node                               | -                   | xx'0078 <sub>H</sub>             | 1E <sub>H</sub> / 30 <sub>D</sub> |  |

| Unassigned node                               | -                   | xx'007C <sub>H</sub>             | 1F <sub>H</sub> / 31 <sub>D</sub> |  |

| Unassigned node                               | -                   | xx'0080 <sub>H</sub>             | 20 <sub>H</sub> / 32 <sub>D</sub> |  |

| Unassigned node                               | -                   | xx'0084 <sub>H</sub>             | 21 <sub>H</sub> / 33 <sub>D</sub> |  |

| Unassigned node                               | -                   | xx'00FC <sub>H</sub>             | 3F <sub>H</sub> / 63 <sub>D</sub> |  |

| Unassigned node                               | -                   | xx'0100 <sub>H</sub>             | 40 <sub>H</sub> / 64 <sub>D</sub> |  |

| Unassigned node                               | _                   | xx'0104 <sub>H</sub>             | 41 <sub>H</sub> / 65 <sub>D</sub> |  |

| Unassigned node                               | _                   | xx'012C <sub>H</sub>             | 4B <sub>H</sub> / 75 <sub>D</sub> |  |

| Unassigned node                               | -                   | xx'0134 <sub>H</sub>             | 4D <sub>H</sub> / 77 <sub>D</sub> |  |

| Unassigned node                               | -                   | xx'0138 <sub>H</sub>             | 4E <sub>H</sub> / 78 <sub>D</sub> |  |

| Unassigned node                               | -                   | xx'013C <sub>H</sub>             | 4F <sub>H</sub> / 79 <sub>D</sub> |  |

| Unassigned node                               | _                   | xx'0140 <sub>H</sub>             | 50 <sub>H</sub> / 80 <sub>D</sub> |  |

| Unassigned node                               | _                   | xx'0160 <sub>H</sub>             | 58 <sub>H</sub> / 88 <sub>D</sub> |  |

1) Register VECSEG defines the segment where the vector table is located to.

Bitfield VECSC in register CPUCON1 defines the distance between two adjacent vectors. This table represents the default setting, with a distance of 4 (two words) between two vectors.

## 3.5 Capture/Compare Unit (CAPCOM2)

The CAPCOM unit supports generation and control of timing sequences on up to 16 channels with a maximum resolution of 1 system clock cycle (8 cycles in staggered mode). The CAPCOM unit is typically used to handle high speed I/O tasks such as pulse and waveform generation, pulse width modulation (PWM), Digital to Analog (D/A) conversion, software timing, or time recording relative to external events.

Two 16-bit timers (T7/T8) with reload registers provide two independent time bases for the capture/compare register array.

The input clock for the timers is programmable to several prescaled values of the internal system clock, or may be derived from an overflow/underflow of timer T6 in module GPT2. This provides a wide range of variation for the timer period and resolution and allows precise adjustments to the application specific requirements. In addition, an external count input for CAPCOM timer T7 allows event scheduling for the capture/compare registers relative to external events.

The capture/compare register array contains 16 dual purpose capture/compare registers, each of which may be individually allocated to either CAPCOM timer (T7 or T8, respectively), and programmed for capture or compare function.

10 registers of the CAPCOM2 module have each one port pin associated with it which serves as an input pin for triggering the capture function, or as an output pin to indicate the occurrence of a compare event.

| Compare Modes           | Function                                                                                                                        |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Mode 0                  | Interrupt-only compare mode;<br>Several compare interrupts per timer period are possible                                        |

| Mode 1                  | Pin toggles on each compare match;<br>Several compare events per timer period are possible                                      |

| Mode 2                  | Interrupt-only compare mode;<br>Only one compare interrupt per timer period is generated                                        |

| Mode 3                  | Pin set '1' on match; pin reset '0' on compare timer overflow;<br>Only one compare event per timer period is generated          |

| Double Register<br>Mode | Two registers operate on one pin;<br>Pin toggles on each compare match;<br>Several compare events per timer period are possible |

| Single Event Mode       | Generates single edges or pulses;<br>Can be used with any compare mode                                                          |

| Table 6Compare Modes (CAPCOM2) |

|--------------------------------|

|--------------------------------|

When a capture/compare register has been selected for capture mode, the current contents of the allocated timer will be latched ('captured') into the capture/compare

The RTC module can be used for different purposes:

- System clock to determine the current time and date, optionally during idle mode, sleep mode, and power down mode

- Cyclic time based interrupt, to provide a system time tick independent of CPU frequency and other resources, e.g. to wake up regularly from idle mode

- 48-bit timer for long term measurements (maximum timespan is > 100 years)

- Alarm interrupt for wake-up on a defined time

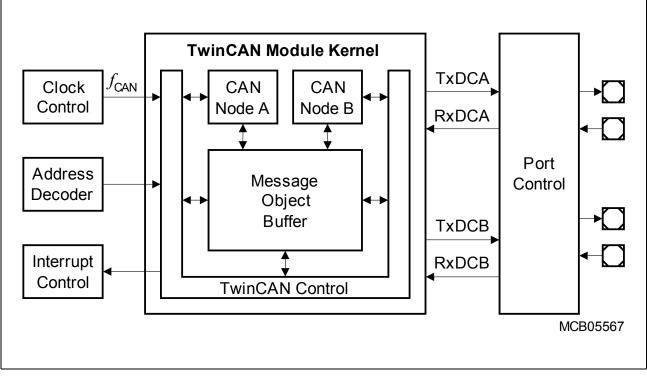

## 3.11 TwinCAN Module

The integrated TwinCAN module handles the completely autonomous transmission and reception of CAN frames in accordance with the CAN specification V2.0 part B (active), i.e. the on-chip TwinCAN module can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

Two Full-CAN nodes share the TwinCAN module's resources to optimize the CAN bus traffic handling and to minimize the CPU load. The module provides up to 32 message objects, which can be assigned to one of the CAN nodes and can be combined to FIFO-structures. Each object provides separate masks for acceptance filtering.

The flexible combination of Full-CAN functionality and FIFO architecture reduces the efforts to fulfill the real-time requirements of complex embedded control applications. Improved CAN bus monitoring functionality as well as the number of message objects permit precise and comfortable CAN bus traffic handling.

Gateway functionality allows automatic data exchange between two separate CAN bus systems, which reduces CPU load and improves the real time behavior of the entire system.

The bit timing for both CAN nodes is derived from the master clock and is programmable up to a data rate of 1 Mbit/s. Each CAN node uses two pins of Port 9 to interface to an external bus transceiver. The interface pins are assigned via software.

Figure 9 TwinCAN Module Block Diagram

#### 3.16 **Power Management**

The XC164GM provides several means to control the power it consumes either at a given time or averaged over a certain timespan. Three mechanisms can be used (partly in parallel):

• **Power Saving Modes** switch the XC164GM into a special operating mode (control via instructions).

Idle Mode stops the CPU while the peripherals can continue to operate.

Sleep Mode and Power Down Mode stop all clock signals and all operation (RTC may optionally continue running). Sleep Mode can be terminated by external interrupt signals.

• Clock Generation Management controls the distribution and the frequency of internal and external clock signals. While the clock signals for currently inactive parts of logic are disabled automatically, the user can reduce the XC164GM's CPU clock frequency which drastically reduces the consumed power.

External circuitry can be controlled via the programmable frequency output FOUT.

• **Peripheral Management** permits temporary disabling of peripheral modules (control via register SYSCON3). Each peripheral can separately be disabled/enabled.

The on-chip RTC supports intermittent operation of the XC164GM by generating cyclic wake-up signals. This offers full performance to quickly react on action requests while the intermittent sleep phases greatly reduce the average power consumption of the system.

## 4 Electrical Parameters

The operating range for the XC164GM is defined by its electrical parameters. For proper operation the indicated limitations must be respected when designing a system.

#### 4.1 General Parameters

These parameters are valid for all subsequent descriptions, unless otherwise noted.

| Parameter                                                                   | Symbol           | Limit Values |                        | Unit | Notes      |

|-----------------------------------------------------------------------------|------------------|--------------|------------------------|------|------------|

|                                                                             |                  | Min.         | Max.                   |      |            |

| Storage temperature                                                         | T <sub>ST</sub>  | -65          | 150                    | °C   | 1)         |

| Junction temperature                                                        | TJ               | -40          | 150                    | °C   | Under bias |

| Voltage on $V_{\text{DDI}}$ pins with respect to ground ( $V_{\text{SS}}$ ) | V <sub>DDI</sub> | -0.5         | 3.25                   | V    | -          |

| Voltage on $V_{\text{DDP}}$ pins with respect to ground ( $V_{\text{SS}}$ ) | V <sub>DDP</sub> | -0.5         | 6.2                    | V    | -          |

| Voltage on any pin with respect to ground ( $V_{SS}$ )                      | V <sub>IN</sub>  | -0.5         | V <sub>DDP</sub> + 0.5 | V    | 2)         |

| Input current on any pin during overload condition                          | -                | -10          | 10                     | mA   | -          |

| Absolute sum of all input<br>currents during overload<br>condition          | -                | -            | 100                    | mA   | -          |

#### Table 9Absolute Maximum Ratings

1) Moisture Sensitivity Level (MSL) 3, conforming to Jedec J-STD-020C for 260 °C.

2) Input pin XTAL1 belongs to the core voltage domain. Therefore, input voltages must be within the range defined for VDDI.

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

| Parameter                                                  | Symbol          |    | Limit Values |      | Unit | Test Condition           |

|------------------------------------------------------------|-----------------|----|--------------|------|------|--------------------------|

|                                                            |                 |    | Min.         | Max. |      |                          |

| XTAL1 input current                                        | I <sub>IL</sub> | CC | -            | ±20  | μA   | $0 V < V_{IN} < V_{DDI}$ |

| Pin capacitance <sup>12)</sup><br>(digital inputs/outputs) | C <sub>IO</sub> | CC | _            | 10   | pF   | -                        |

#### Table 11 DC Characteristics (Operating Conditions apply)<sup>1)</sup> (cont'd)

1) Keeping signal levels within the limits specified in this table, ensures operation without overload conditions. For signal levels outside these specifications, also refer to the specification of the overload current  $I_{OV}$ .

- 2) If XTAL1 is driven by a crystal, reaching an amplitude (peak to peak) of  $0.4 \times V_{DDI}$  is sufficient.

- 3) This parameter is tested for P3, P9.

4) The maximum deliverable output current of a port driver depends on the selected output driver mode, see Table 12, Current Limits for Port Output Drivers. The limit for pin groups must be respected.

- 5) As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL} \rightarrow V_{SS}$ ,  $V_{OH} \rightarrow V_{DDP}$ ). However, only the levels for nominal output currents are guaranteed.

- 6) This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage results from the external circuitry.

- 7) An additional error current ( $I_{INJ}$ ) will flow if an overload current flows through an adjacent pin. Please refer to the definition of the overload coupling factor  $K_{OV}$ .

- The driver of P3.15 is designed for faster switching, because this pin can deliver the system clock (CLKOUT). The maximum leakage current for P3.15 is, therefore, increased to 1 μA.

- 9) During a hardware reset this specification is valid for configuration on P1H.4, P1H.5, P9.4 and P9.5. After a hardware reset this specification is valid for NMI.

- 10) The maximum current may be drawn while the respective signal line remains inactive.

- 11) The minimum current must be drawn to drive the respective signal line active.

- 12) Not subject to production test verified by design/characterization.

| Port Output Driver<br>Mode | Maximum Output Current $(I_{OLmax}, -I_{OHmax})^{1)}$ | Nominal Output Current<br>( <i>I</i> <sub>OLnom</sub> , - <i>I</i> <sub>OHnom</sub> ) |

|----------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------|

| Strong driver              | 10 mA                                                 | 2.5 mA                                                                                |

| Medium driver              | 4.0 mA                                                | 1.0 mA                                                                                |

| Weak driver                | 0.5 mA                                                | 0.1 mA                                                                                |

#### Table 12Current Limits for Port Output Drivers

An output current above |I<sub>OXnom</sub>| may be drawn from up to three pins at the same time. For any group of 16 neighboring port output pins the total output current in each direction (ΣI<sub>OL</sub> and Σ-I<sub>OH</sub>) must remain below 50 mA.

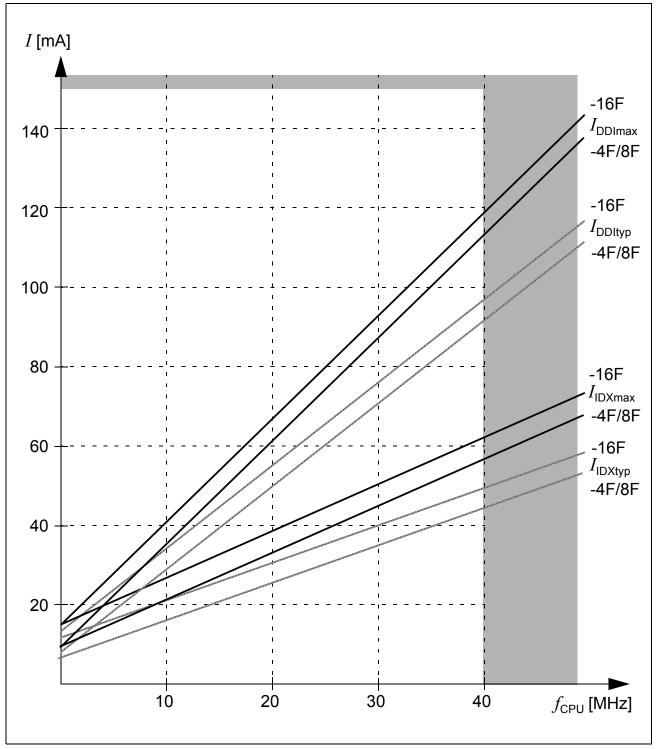

Figure 10 Supply/Idle Current as a Function of Operating Frequency

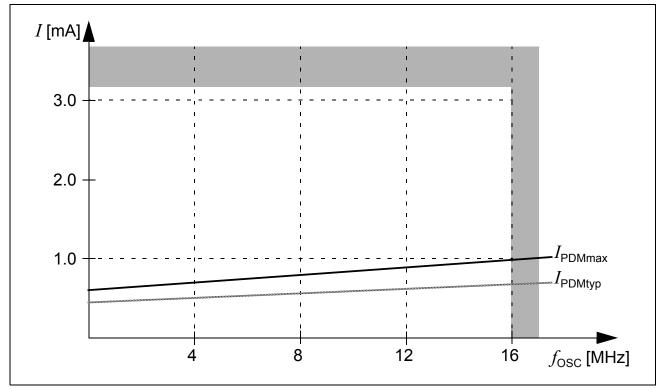

Figure 11 Sleep and Power Down Supply Current due to RTC and Oscillator Running, as a Function of Oscillator Frequency

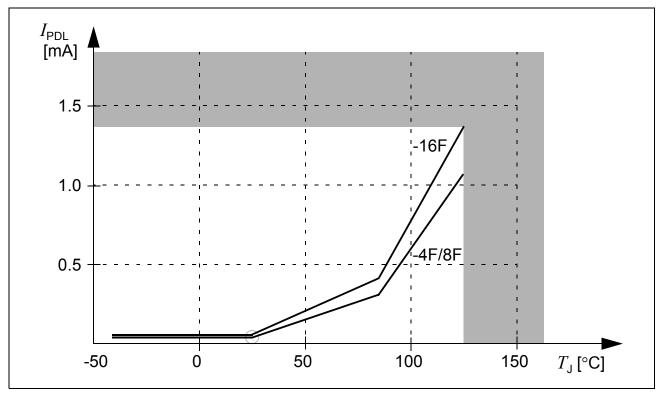

Figure 12 Sleep and Power Down Leakage Supply Current as a Function of Temperature

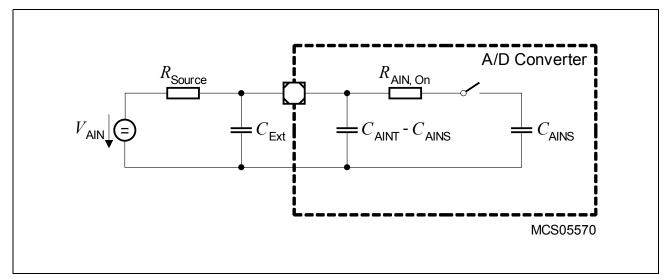

- V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

- 3) The limit values for  $f_{BC}$  must not be exceeded when selecting the peripheral frequency and the ADCTC setting.

- 4) This parameter includes the sample time t<sub>S</sub>, the time for determining the digital result and the time to load the result register with the conversion result (t<sub>SYS</sub> = 1/f<sub>SYS</sub>). Values for the basic clock t<sub>BC</sub> depend on programming and can be taken from Table 15.

- When the post-calibration is switched off, the conversion time is reduced by  $12 \times t_{BC}$ .

- 5) The actual duration of the reset calibration depends on the noise on the reference signal. Conversions executed during the reset calibration increase the calibration time. The TUE for those conversions may be increased.

- 6) Not subject to production test verified by design/characterization. The given parameter values cover the complete operating range. Under relaxed operating conditions (temperature, supply voltage) reduced values can be used for calculations. At room temperature and nominal supply voltage the following typical values can be used:

$C_{\text{AINTtyp}}$  = 12 pF,  $C_{\text{AINStyp}}$  = 7 pF,  $R_{\text{AINtyp}}$  = 1.5 kΩ,  $C_{\text{AREFTtyp}}$  = 15 pF,  $C_{\text{AREFStyp}}$  = 13 pF,  $R_{\text{AREFtyp}}$  = 0.7 kΩ.

Figure 13 Equivalent Circuitry for Analog Inputs

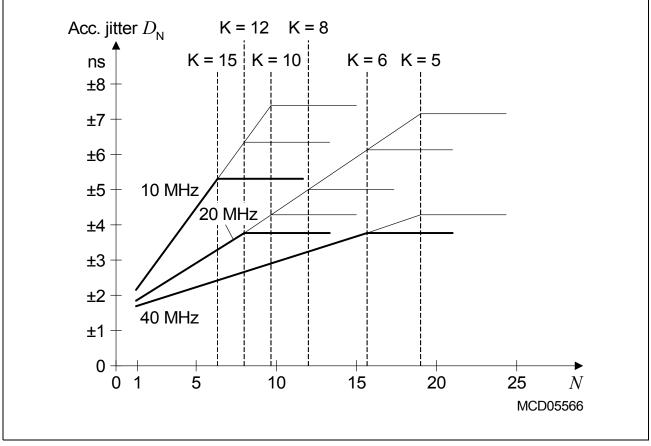

This is especially important for bus cycles using waitstates and e.g. for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train generation or measurement, lower baudrates, etc.) the deviation caused by the PLL jitter is negligible.

The value of the accumulated PLL jitter depends on the number of consecutive VCO output cycles within the respective timeframe. The VCO output clock is divided by the output prescaler (K = PLLODIV+1) to generate the master clock signal  $f_{MC}$ . Therefore, the number of VCO cycles can be represented as K × N, where N is the number of consecutive  $f_{MC}$  cycles (TCM).

For a period of  $\mathbf{N} \times \text{TCM}$  the accumulated PLL jitter is defined by the deviation  $D_{\text{N}}$ :

$D_N$  [ns] = ±(1.5 + 6.32 × N /  $f_{MC}$ );  $f_{MC}$  in [MHz], N = number of consecutive TCMs.

So, for a period of 3 TCMs @ 20 MHz and K = 12:  $D_3 = \pm(1.5 + 6.32 \times 3 / 20) = 2.448$  ns. This formula is applicable for K × N < 95. For longer periods the K × N = 95 value can be

used. This steady value can be approximated by:  $D_{Nmax}$  [ns] = ±(1.5 + 600 / (K ×  $f_{MC}$ )).

Figure 15 Approximated Accumulated PLL Jitter

Note: The bold lines indicate the minimum accumulated jitter which can be achieved by selecting the maximum possible output prescaler factor K.

Different frequency bands can be selected for the VCO, so the operation of the PLL can be adjusted to a wide range of input and output frequencies:

| Table 16 | VCO Bands for PLL Operation <sup>1)</sup> |

|----------|-------------------------------------------|

|----------|-------------------------------------------|

| PLLCON.PLLVB | VCO Frequency Range | Base Frequency Range |

|--------------|---------------------|----------------------|

| 00           | 100 150 MHz         | 20 80 MHz            |

| 01           | 150 200 MHz         | 40 130 MHz           |

| 10           | 200 250 MHz         | 60 180 MHz           |

| 11           | Reserved            |                      |

1) Not subject to production test - verified by design/characterization.